May 2004

# FAIRCHILD

SEMICONDUCTOR®

# RMBA09501

## Cellular 2 Watt Linear GaAs MMIC Power Amplifier

#### **General Description**

Features

The RMBA09501 is a highly linear Power Amplifier. The two stage circuit uses our pHEMT process. It is designed for use as a driver stage for Cellular base stations, or as the output stage for Micro- and Pico-Cell base stations. The amplifier has been optimized for high linearity requirements for CDMA operation.

# 2 Watt Linear output power at 36dBc ACPR1 for CDMA operation

- Small Signal Gain of > 30dB

- Small outline SMD package

## **Absolute Ratings**

| Symbol                             | Parameter                         | Min | Max  | Units |

|------------------------------------|-----------------------------------|-----|------|-------|

| V <sub>DD</sub>                    | Drain Supply Voltage <sup>1</sup> |     | +10  | V     |

| V <sub>GS</sub><br>P <sub>RF</sub> | Gate Supply Voltage               |     | -5   | V     |

| P <sub>RF</sub>                    | RF Input Power (from 50Ω source)  |     | +5   | dBm   |

| т <sub>с</sub>                     | Case Operating Temperature        | -30 | +85  | °C    |

| T <sub>S</sub>                     | Storage Temperature               | -40 | +100 | °C    |

Note:

1. Only under quiescent conditions-no RF applied.

©2004 Fairchild Semiconductor Corporation

# **RMBA09501**

# **Electrical Characteristics**<sup>2</sup>

| Parameter                                                       | Min | Тур      | Max   | Units |

|-----------------------------------------------------------------|-----|----------|-------|-------|

| Frequency Range                                                 | 869 |          | 894   | MHz   |

| Gain (Small Signal)                                             |     | 35       |       | dB    |

| Gain Variation:                                                 |     |          |       |       |

| Over Frequency Range                                            |     | ±1.5     |       | dB    |

| Over Temperature Range                                          |     | ±2.5     |       | dB    |

| Noise Figure                                                    |     | 6        |       | dB    |

| Linear Output Power: for CDMA <sup>3</sup>                      | 33  |          |       | dBm   |

| OIP3 <sup>5</sup>                                               |     | 43       |       | dBm   |

| Idd @ 33dBm Pout – 7V                                           |     | 1.0      |       | A     |

| PAE @ 33dBm Pout                                                |     | 28.5     |       | %     |

| Input VSWR (50Ω)                                                |     | 2:1      |       |       |

| RF Input Power                                                  |     | +1       |       | dBm   |

| Drain Voltage (V <sub>DD</sub> )                                |     | 7.0      |       | V     |

| Gate Voltages (VG <sub>1</sub> , VG <sub>2</sub> ) <sup>4</sup> | -2  |          | -0.25 | V     |

| Quiescent Currents (IDQ1, IDQ2) <sup>4</sup>                    |     | 150, 400 |       | mA    |

| Thermal Resistance (Channel to Case) Ric                        |     | 11       |       | °C/W  |

Notes:

Notes:

2. V<sub>DD</sub> = 7.0V, T<sub>C</sub> = 25°C. Part mounted on evaluation board with input and output matching to 50Ω.

3. 9 Channel Forward Link QPSK Source; 1.23Mbps modulation rate. CDMA ACPR1 is measured using the ratio of the average power within the 1.23MHz channel at band center to the average power within a 30KHz bandwidth at an 885KHz offset. Minimum CDMA output power is met with ACPR1 > 36dBc.

4. VG1 and VG2 must be individually adjusted to achieve IDQ1 and IDQ2. A single VGG bias supply adjusted to achieve IDQ1OTAL = 550mA can be used with nearly equivalent performance. Values for IDQ1 and IDQ2 shown have been optimized for CDMA operation. IDQ1 and IDQ2 (or IDQ1OTAL) can be adjusted to optimize the linearity of the amplifier for other modulation systems.

5. OIP3 specifications are achieved for power output levels of 27 and 30 dBm per tone with tone spacing of 1.25MHz at bandcenter.

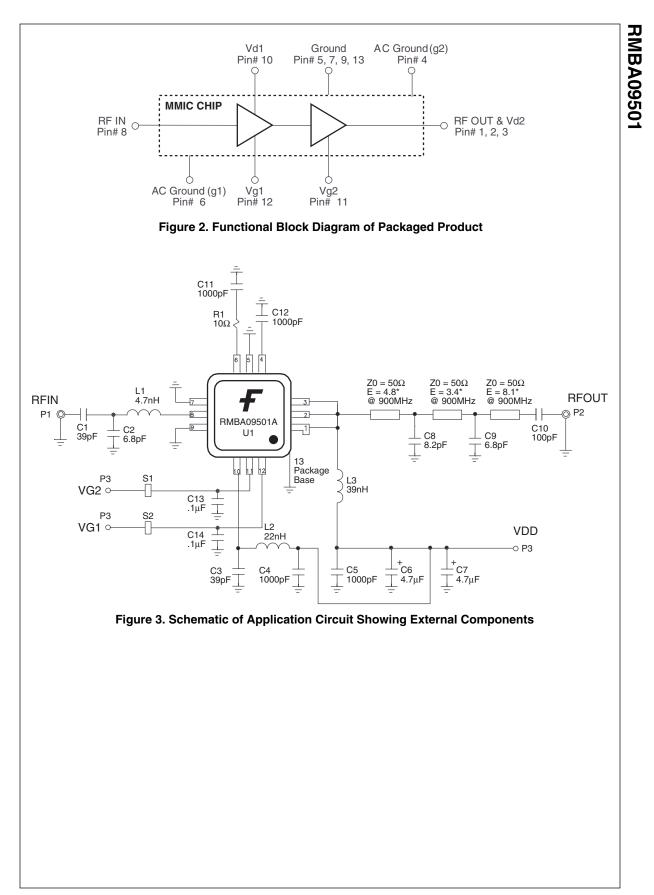

The device requires external input and output matching to  $50\Omega$  as shown in Figure 3 and the Parts List.

# **Application Information**

#### CAUTION: THIS IS AN ESD SENSITIVE DEVICE

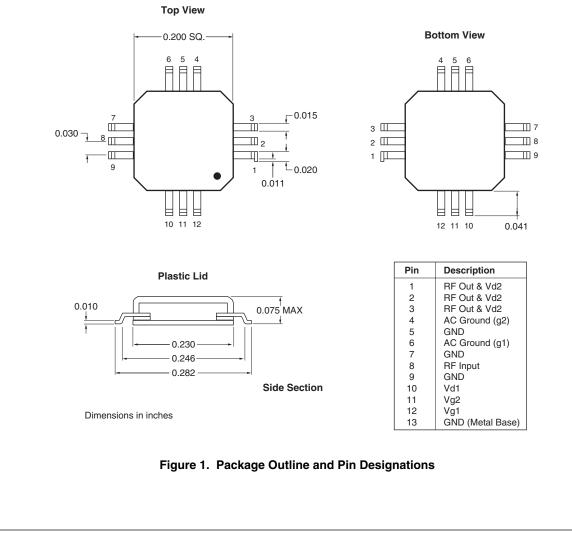

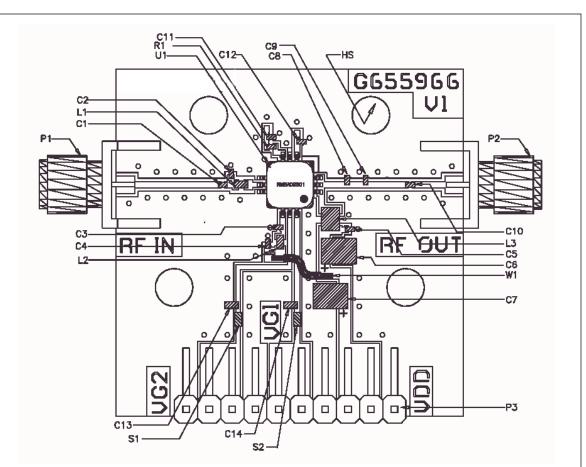

The following describes a procedure for evaluating the RMBA09501, a monolithic high efficiency power amplifier, in a surface mount package, designed for use as a driver stage for Cellular Base stations, or as the final output stage for Microand Pico-Cell base stations. Figure 1 shows the package outline and the pin designations. Figure 2 shows the functional block diagram of the packaged product. The RMBA09501 requires external passive components for DC bias and RF input and output matching circuits as shown in Figure 3 and the Part List. A recommended schematic circuit is shown in Figure 3. The gate biases for the two stages of the amplifier may be set by simple resistive voltage dividers. Figure 4 shows a typical layout of an evaluation board, corresponding to the schematic circuits of Figure 3. The following designations should be noted:

- (1) Pin designations are as shown in Figure 2.

- (2) Vg1 and Vg2 are the Gate Voltages (negative) applied at the pins of the package.

- (3) Vgg1 and Vgg2 are the negative supply voltages at the evaluation board terminals.

- (4) Vd1 and Vd2 are the Drain Voltages (positive) applied at the pins of the package.

- (5) Vdd1 and Vdd2 are the positive supply voltages at the evaluation board terminals.

Note: The 2 terminals of Vdd1 and Vdd2 may be tied together. The base of the package must be soldered on to a heat sink for proper operation.

RMBA09501

Figure 4. Layout of Test Evaluation Board (RMBA09501-TD, G657471)

## Test Procedure for the Evaluation Board (RMBA09501-TB)

#### CAUTION: LOSS OF GATE VOLTAGES (VG1, VG2) WHILE CORRESPONDING DRAIN VOLTAGES (Vdd) ARE PRESENT CAN DAMAGE THE AMPLIFIER.

The following sequence must be followed to properly test the amplifier. (It is necessary to add a fan to provide air cooling across the heat sink of RMBA09501.) Note: Vdd1, 2 are tied together.

Step 1: Turn off RF input power.

**Step 2:** Use GND terminal of the evaluation board for the ground of the DC supplies. Slowly apply gate supply voltages as specified on results sheet supplied with test board to the board terminals Vgg1 and Vgg2.

**Step 3:** Slowly apply drain supply voltages of +7.0V to the board terminals Vdd1, 2. Adjust Vgg to set the total quiescent current Idq1 and Idq2 (with no RF applied) Idq as per supplied result sheet. Gate supply voltages (Vgg i.e., Vgg1, Vgg2) may be adjusted, only if quiescent current (Idq1 and Idq2) values desired are different from those noted on the data summary supplied with product samples.

**Step 4:** After the bias condition is established, RF input signal may now be applied at the appropriate frequency band and appropriate power level.

Step 5: Follow turn-off sequence of:

- (i) Turn off RF Input Power

- (ii) Turn down and off drain voltages Vdd1, 2.

- (iii) Turn down and off gate voltages Vgg1 and Vgg2.

**RMBA09501**

| Part             | Value                   | Size (EIA) | Vendor(s)                       |

|------------------|-------------------------|------------|---------------------------------|

| C1, C3           | 39pF                    | 0402       | Murata, GRM36COG390J050         |

| C2, C9           | 6.8pF                   | 0402       | Murata, GRM36COG6R8B050         |

| C8               | 8.2pF                   | 0402       | Murata, GRM36COG8R2B50          |

| C4, C5, C11, C12 | 1000pF                  | 0402       | Murata, GRM36X7R102K050         |

| C6, C7           | 4.7µF                   | 3528       | TDK, C3216X7R102K050            |

| L1               | 4.7nH                   | 0603       | Toko, LL1608-FH4N7S             |

| L2               | 22nH                    | 0603       | Toko, LL1608-FH22NK             |

| L3               | 39nH                    | 1008       | Coilcraft, 1008HQ-39NTKBC       |

| R1               | 10Ω                     | 0402       | IMS, RCI-0402-10R0J             |

| S1, S2           |                         |            | Bar or Ni Ribbon Short          |

| W1               | 26AWG (0.015" dia) Wire |            | Alpha, 2853/1                   |

| U1               | RMBA09501 PA            |            | Fairchild Semiconductor         |

| P3               | Right angle Pin Header  |            | 3M 2340-5211TN                  |

| P1, P2           | Brass SMA Connectors    |            | Johnson Components 142-0701-841 |

| Board            | FR4                     |            | Raytheon Dwg# G654626, V1       |

| C10              | 100pF                   | 0603       | Murata, GRM36COG101J50          |

| C13, C14         | 1.0µF                   | 0805       | Murata, GRM39Y5V104Z50          |

0054040

## **Thermal Considerations for Heat Sinking the RMBA09501**

The PWB must be prepared with either an embedded copper slug in the board where the package is to be mounted or a heat sink should be attached to the backside of the PWB where the package is to be mounted on the front side. The slug or the heat sink should be made of a highly electrically and thermally conductive material such as copper or aluminum. The slug should be at least the same thickness as the PWB. In the case of the heat sink, a small pedestal should protrude through a hole in the PWB where the package bottom is directly soldered. In either configuration, the top surface of the slug or the pedestal should be made coplanar with the package lead mounting plane i.e., the top surface of the PWB. Use Sn96 solder (96.5% Sn and 3.5% Ag) at 220°C for 20 seconds or less to attach the heat sink to the backside of the PWB. Then, using Sn63, the package bottom should be firmly soldered to the slug or the pedestal while the pins are soldered to the respective pads on the front side of the PWB without causing any stress on the pins. Remove flux completely if used for soldering.

©2004 Fairchild Semiconductor Corporation

#### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

| ACEx™                                | FAST®                          | ISOPLANAR™                   | Power247™                       | SuperFET™                |

|--------------------------------------|--------------------------------|------------------------------|---------------------------------|--------------------------|

| ActiveArray™                         | FASTr™                         | LittleFET™                   | PowerSaver™                     | SuperSOT™-3              |

| Bottomless™                          | FPS™                           | MICROCOUPLER™                | PowerTrench <sup>®</sup>        | SuperSOT™-6              |

| CoolFET™                             | FRFET™                         | MicroFET™                    | QFET <sup>®</sup>               | SuperSOT <sup>™</sup> -8 |

| CROSSVOLT™                           | GlobalOptoisolator™            | MicroPak™                    | QS™                             | SyncFET™                 |

| DOME™                                | GTO™່                          | MICROWIRE™                   | QT Optoelectronics <sup>™</sup> | TinyLogic®               |

| EcoSPARK™                            | HiSeC™                         | MSX™                         | Quiet Series <sup>™</sup>       | TINYOPTO™                |

| E <sup>2</sup> CMOS <sup>™</sup>     | I²C™                           | MSXPro™                      | RapidConfigure™                 | TruTranslation™          |

| EnSigna™                             | <i>i-Lo</i> ™                  | OCX™                         | RapidConnect™                   | UHC™                     |

| FACT™                                | ImpliedDisconnect <sup>™</sup> | OCXPro™                      | µSerDes™                        | UltraFET <sup>®</sup>    |

| FACT Quiet Seri                      |                                | <b>OPTOLOGIC<sup>®</sup></b> | SILENT SWITCHER <sup>®</sup>    | VCX™                     |

| Across the board. Around the world.™ |                                | OPTOPLANAR™                  | SMART START™                    |                          |

| The Power Franchise <sup>®</sup>     |                                | PACMAN™                      | SPM™                            |                          |

| Programmable Active Droop™           |                                | POP™                         | Stealth™                        |                          |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                                        |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for<br>product development. Specifications may change in<br>any manner without notice.                                                                                          |

| Preliminary              | First Production          | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |

Rev. I11