###

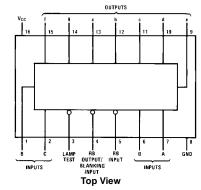

## MM74C48 BCD-to-7 Segment Decoder

#### **General Description**

The MM74C48 BCD-to-7 segment decoder is a monolithic complementary MOS (CMOS) integrated circuit constructed with N- and P-channel enhancement transistors. Seven NAND gates and one driver are connected in pairs to make binary-coded decimal (BCD) data and its complement available to the seven decoding AND-OR-INVERT gates. The remaining NAND gate and three input buffers provide test-blanking input/ripple-blanking output, and ripple-blanking inputs.

#### Features

- Wide supply voltage range: 3.0V to 15V

- Guaranteed noise margin: 1.0V

- High noise immunity: 0.45 V<sub>CC</sub> (typ.)

- Low power TTL compatibility: fan out of 2 driving 74L

- High current sourcing output (up to 50 mA)

- Ripple blanking for leading or trailing zeros (optional)

- Lamp test provision

#### **Ordering Code:**

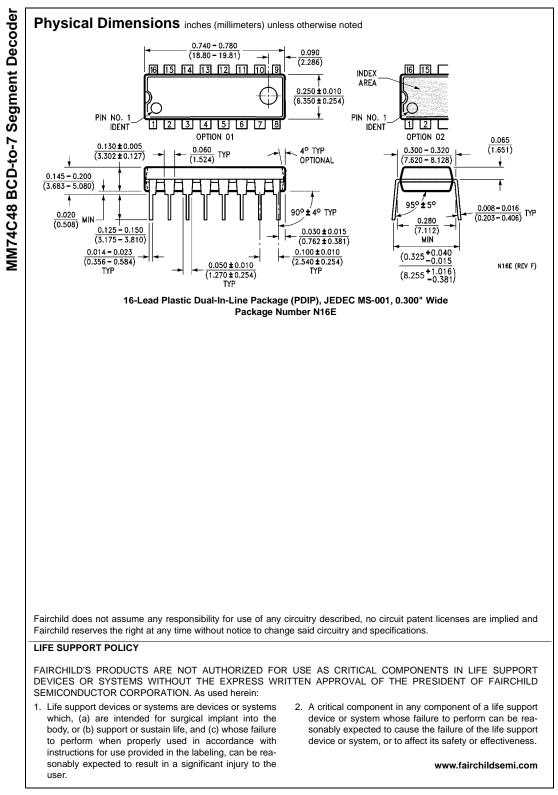

| Order Number | Package Number | Package Description                                                    |

|--------------|----------------|------------------------------------------------------------------------|

| MM74C48N     | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide |

## **Connection Diagrams**

#### © 2002 Fairchild Semiconductor Corporation DS005883

# **MM74C48**

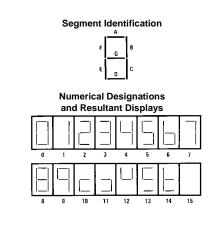

## Truth Table

| Decimal        |    |     | Inp | uts |   |   |                    |   |   | C | Dutput | s |   |   | Nata      |

|----------------|----|-----|-----|-----|---|---|--------------------|---|---|---|--------|---|---|---|-----------|

| or<br>Function | LT | RBI | D   | С   | В | Α | BI/RBO<br>(Note 1) | а | b | с | d      | е | f |   | Note      |

|                |    |     |     |     |   |   | . ,                |   |   | - | -      | - |   | g | (Nists O) |

| 0              | Н  | Н   | L   | L   | L | L | Н                  | Н | Н | Н | Н      | Н | Н | L | (Note 2)  |

| 1              | н  | Х   | L   | L   | L | н | Н                  | L | н | н | L      | L | L | L | (Note 2)  |

| 2              | н  | Х   | L   | L   | н | L | Н                  | н | Н | L | Н      | Н | L | н |           |

| 3              | н  | Х   | L   | L   | н | н | Н                  | н | н | н | н      | L | L | н |           |

| 4              | Н  | Х   | L   | Н   | L | L | Н                  | L | Н | Н | L      | L | Н | Н |           |

| 5              | н  | Х   | L   | н   | L | н | Н                  | н | L | н | н      | L | н | н |           |

| 6              | н  | Х   | L   | н   | н | L | н                  | L | L | н | н      | н | н | н |           |

| 7              | н  | Х   | L   | н   | н | н | н                  | н | н | н | L      | L | L | L |           |

| 8              | Н  | Х   | Н   | L   | L | L | Н                  | Н | Н | Н | Н      | Н | Н | Н |           |

| 9              | н  | Х   | н   | L   | L | н | н                  | н | н | н | L      | L | н | н |           |

| 10             | н  | Х   | н   | L   | н | L | н                  | L | L | L | н      | н | L | н |           |

| 11             | н  | х   | Н   | L   | н | н | н                  | L | L | н | н      | L | L | н |           |

| 12             | Н  | Х   | Н   | Н   | L | L | Н                  | L | Н | L | L      | L | Н | Н |           |

| 13             | н  | Х   | н   | н   | L | н | н                  | н | L | L | н      | L | н | н |           |

| 14             | н  | Х   | н   | н   | н | L | н                  | L | L | L | н      | н | н | н |           |

| 15             | н  | х   | н   | н   | н | н | н                  | L | L | L | L      | L | L | L |           |

| BI             | Х  | Х   | Х   | Х   | Х | Х | L                  | L | L | L | L      | L | L | L | (Note 3)  |

| RBI            | н  | L   | L   | L   | L | L | L                  | L | L | L | L      | L | L | L | (Note 4)  |

| LT             | L  | х   | Х   | Х   | Х | х | н                  | н | н | н | н      | н | н | н | (Note 5)  |

H = HIGH Level

L = LOW Level X = Irrelevant

Note 1: One BI/RBO is wire-AND logic serving as blanking input (BI) and/or ripple-blanking output (RBO).

Note 2: The blanking input (BI) must be open when output functions 0–15 are desired. The ripple-blanking input (RBI) must be HIGH, if blanking of a decimal zero is not desired.

Note 3: When a LOW logic level is applied directly to the blanking input (BI), all segment outputs are LOW regardless of the level of any other input.

Note 4: When ripple-blanking input (RBI) and inputs A, B, C, and D are at a LOW level with the lamp-test input HIGH, all segment outputs go LOW and the ripple-blanking output (RBO) goes to a LOW level (response condition).

Note 5: When the blanking input/ripple-blanking output (BI/RBO) is open and a LOW is applied to the lamp-test input, all segment outputs are HIGH.

## Absolute Maximum Ratings(Note 6)

| Voltage at Any Pin               | –0.3V to V <sub>CC</sub> + 0.3V   |

|----------------------------------|-----------------------------------|

| Operating Temperature Range      | -55°C to +125°C                   |

| Storage Temperature Range        | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Power Dissipation                |                                   |

| Dual-In-Line                     | 700 mW                            |

| Small Outline                    | 500 mW                            |

| Operating V <sub>CC</sub> Range  | 3.0V to 15V                       |

| Absolute Maximum V <sub>CC</sub> | 18V                               |

| Lead Temperature                 |                                   |

| (Soldering, 10 seconds)          | 260°C                             |

MM74C48

**Note 6:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The Electrical Characteristics table provides conditions for actual device operation.

## **DC Electrical Characteristics**

|                     | Parameter                           | Conditions                                                        | Min                   | Тур        | Max   | Units |

|---------------------|-------------------------------------|-------------------------------------------------------------------|-----------------------|------------|-------|-------|

| CMOS to C           | MOS                                 |                                                                   |                       |            |       |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage           | $V_{CC} = 5.0V$                                                   | 3.5                   |            |       | v     |

|                     |                                     | $V_{CC} = 10V$                                                    | 8.0                   |            |       | v     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage           | $V_{CC} = 5.0V$                                                   |                       |            | 1.5   | V     |

|                     |                                     | $V_{CC} = 10V$                                                    |                       |            | 2.0   | v     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | $V_{CC} = 5.0V, I_{O} = -10 \ \mu A$                              | 4.5                   |            |       | v     |

|                     | (RB Output Only)                    | $V_{CC} = 10V, I_{O} = -10 \ \mu A$                               | 9.0                   |            |       | v     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | $V_{CC} = 5.0V, I_{O} = 10 \ \mu A$                               |                       |            | 0.5   | v     |

|                     |                                     | $V_{CC} = 10V, I_{O} = 10 \ \mu A$                                |                       |            | 1.0   | v     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current           | V <sub>CC</sub> = 15.0V, V <sub>IN</sub> = 15V                    |                       | 0.005      | 1.0   | μΑ    |

| I <sub>IN(0)</sub>  | Logical "0" Input Current           | $V_{CC} = 15.0V, V_{IN} = 0V$                                     | -1.0                  | -0.005     |       | μΑ    |

| I <sub>CC</sub>     | Supply Current                      | V <sub>CC</sub> = 15V                                             |                       | 0.05       | 300   | μΑ    |

| CMOS/LPT            | TL INTERFACE                        |                                                                   | L                     |            |       |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage           | $V_{CC} = 4.75V$                                                  | V <sub>CC</sub> – 1.5 |            |       | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage           | $V_{CC} = 4.75V$                                                  |                       |            | 0.8   | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | $V_{CC} = 4.75 V$ , $I_{O} = -50 \ \mu A$                         | 2.4                   |            |       | V     |

| ( )                 | (RB Output Only)                    |                                                                   |                       |            |       |       |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | $V_{CC} = 4.75 V, I_{O} = 360 \ \mu A$                            |                       |            | 0.4   | V     |

|                     | RIVE (See Family Characteristics Da | ta Sheet)                                                         | I                     |            |       | I     |

| ISOURCE             | Output Source Current               | $V_{CC} = 4.75V, V_{OUT} = 0.4V$                                  |                       |            | -0.80 |       |

|                     | (P-Channel) (RB Output Only)        | $V_{CC} = 10V, V_{OUT} = 0.5V$                                    |                       |            | -4.0  | mA    |

| I <sub>SINK</sub>   | Output Sink Current                 | $V_{CC} = 5.0V, V_{OUT} = V_{CC}$                                 | 1.75                  | 3.6        |       | mA    |

|                     | (N-Channel)                         | $T_A = 25^{\circ}C$                                               |                       |            |       |       |

| I <sub>SINK</sub>   | Output Sink Current                 | $V_{CC} = 10V, V_{OUT} = V_{CC}$                                  | 8.0                   | 16         |       | mA    |

|                     | (N-Channel)                         | $T_A = 25^{\circ}C$                                               |                       |            |       |       |

|                     | Output Source Current               | V <sub>CC</sub> = 5.0V, V <sub>OUT</sub> = 3.4V                   | -20                   | -50        |       |       |

| ISOURCE             |                                     |                                                                   |                       | CE.        |       |       |

| ISOURCE             | (NPN Bipolar)                       | $V_{CC} = 5.0V, V_{OUT} = 3.0V$                                   |                       | -65        |       |       |

| ISOURCE             | (NPN Bipolar)                       | $V_{CC} = 5.0V, V_{OUT} = 3.0V$<br>$V_{CC} = 10V, V_{OUT} = 8.4V$ | -20                   | -65<br>-50 |       | mA    |

|                                    | $C_{L} = 50 \text{ pF}$ , unless otherwise specified |                 |     |     |      |       |  |

|------------------------------------|------------------------------------------------------|-----------------|-----|-----|------|-------|--|

| Symbol                             | Parameter                                            | Conditions      | Min | Тур | Max  | Units |  |

| t <sub>pd0,</sub> t <sub>pd1</sub> | Propagation Delay to a "1" or "0" on                 | $V_{CC} = 5.0V$ |     | 450 | 1500 |       |  |

|                                    | Segment Outputs from Data Inputs                     | $V_{CC} = 10V$  |     | 160 | 500  | ns    |  |

| t <sub>pd0</sub>                   | Propagation Delay to a "0" on                        | $V_{CC} = 5.0V$ |     | 500 | 1600 |       |  |

|                                    | Segment Outputs from RB Input                        | $V_{CC} = 10V$  |     | 180 | 550  | ns    |  |

| t <sub>pd0</sub>                   | Propagation Delay to a "0" on                        | $V_{CC} = 5.0V$ |     | 350 | 1200 |       |  |

|                                    | Segment Outputs from Blanking Input                  | $V_{CC} = 10V$  |     | 140 | 450  | ns    |  |

| t <sub>pd1</sub>                   | Propagation Delay to a "1" on                        | $V_{CC} = 5.0V$ |     | 450 | 1500 |       |  |

|                                    | Segment Outputs from Lamp Test                       | $V_{CC} = 10V$  |     | 160 | 500  | ns    |  |

| t <sub>pd1</sub>                   | Propagation Delay to a "1" on RB                     | $V_{CC} = 5.0V$ |     | 600 | 2000 |       |  |

|                                    | Output from RB Input                                 | $V_{CC} = 10V$  |     | 250 | 800  | ns    |  |

| t <sub>pd0</sub>                   | Propagation Delay to a "0" on RB                     | $V_{CC} = 5.0V$ |     | 140 | 450  |       |  |

| F                                  | Output from RB Input                                 | $V_{CC} = 10V$  |     | 50  | 150  | ns    |  |

Note 7: AC Parameters are guaranteed by DC correlated testing

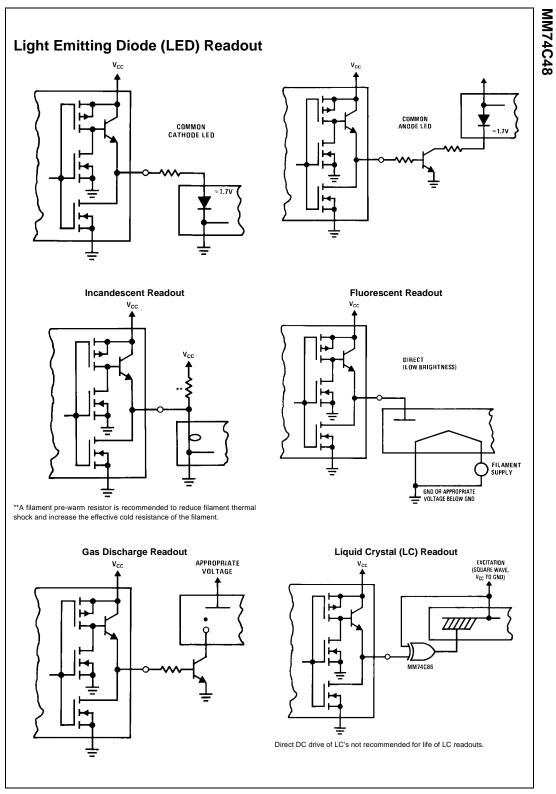

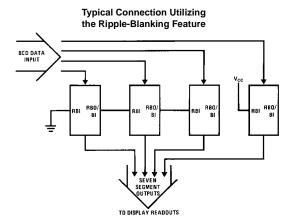

## **Typical Applications**

First three stages will blank leading zeros, the fourth stage will not blank zeros.

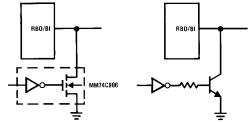

#### Blanking Input Connection Diagram

When RBO/BI is forced LOW, all segment outputs are off regardless of the state of any other input condition.