September 2009

# FXM2IC102 2-Bit I<sup>2</sup>C Bus Interface Voltage Translator / Repeater

#### **Features**

- Bi-Directional Interface between any Two Levels from 1.65V to 5.5V

- Auto-Direction Sensing, Direction Control not Needed

- Buffer Isolates Capacitance and Allows 400pF on Each Port

- Open-Drain Inputs/Outputs

- Schmitt Trigger Data Inputs

- Accommodates Standard-Mode and Fast-Mode I<sup>2</sup>C-bus Devices

- Fully Configurable: Inputs and Outputs Track V<sub>CC</sub> Level

- Non-Preferential Power-up; Either V<sub>CC</sub> May be Powered Up First

- Outputs Remain in 3-State until Active V<sub>CC</sub> Level is Reached

- Power-Off High Impedance

- Active HIGH Output Enable Referenced to V<sub>CCA</sub>

- 5V-Tolerant Output Enable

- Packaged in 8-Terminal Leadless MicroPak™ (1.6mm x 1.6mm)

- **ESD Protection Exceeds:**

- 8kV HBM ESD (per JESD22-A114 & Mil Std 883e 3015.7)

- 15kV HBM I/O to GND ESD (per JESD22-A114 & Mil Std 883e 3015.7)

### Description

The FXM2IC102 is a configurable dual-voltage-supply translator designed for bi-directional voltage translation over a wide range of input and output voltage levels.

The FXM2IC102 is intended for use as a voltage translator in applications using the I<sup>2</sup>C bus interface. Input and output voltage levels are compatible with I<sup>2</sup>C device specification voltage levels.

The device is designed so that the A port tracks the V<sub>CCA</sub> level and the B port tracks the V<sub>CCB</sub> level. This allows for bi-directional voltage translation over voltage ranges: 1.8V, 2.5V, 3.3V, and 5.0V.

The device remains in 3-state until both V<sub>CC</sub>s reach active levels, allowing either V<sub>CC</sub> to be powered up first. Internal power-down control circuits place the device in 3-state if either V<sub>CC</sub> is removed.

The two ports of the device have auto-direction sense capability. Either port may sense an input signal and transfer it as an output signal to the other port.

Schmitt triggers are used on data inputs for signal noise suppression. Typically the inputs have 100 millivolts of hysteresis over the full V<sub>CC</sub> range.

The FXM2IC102 typically consumes only 230nA during "no  $I^2C$  data transactions" when  $V_{CCA} = 1.8V$  and  $V_{CCB} =$ 3.3V. See Figure 4 and Figure 5 for more details.

FXM2IC102 exhibits robust I<sup>2</sup>C repeater performance due to strong current sinking capability in > 400pf bus segments. See Figure 6 and Figure 7 for details.

### Ordering Information

| Part Number  | Operating<br>Temperature Range | Top<br>Mark | © Eco<br>Status | Package                     | Packing<br>Method              |

|--------------|--------------------------------|-------------|-----------------|-----------------------------|--------------------------------|

| FXM2IC102L8X | -40 to +85°C                   | XG          | Green           | 8-Lead MicroPak, 1.6mm Wide | 3000 Units on<br>Tape and Reel |

For Fairchild's definition of Eco Status, please visit: <a href="http://www.fairchildsemi.com/company/green/rohs-green.html">http://www.fairchildsemi.com/company/green/rohs-green.html</a>.

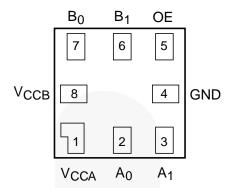

## **Pin Configuration**

Figure 1. Pin Configuration (Top-Through View)

### **Pin Definitions**

| Pin # | Name                            | Description                      |

|-------|---------------------------------|----------------------------------|

| 1     | V <sub>CCA</sub>                | A-Side Power Supply              |

| 2, 3  | A <sub>0</sub> , A <sub>1</sub> | A-Side Inputs or 3-State Outputs |

| 4     | GND                             | Ground                           |

| 5     | OE                              | Output Enable Input              |

| 6, 7  | B <sub>1</sub> , B <sub>0</sub> | B-Side Inputs or 3-State Outputs |

| 8     | V <sub>CCB</sub>                | B-Side Power Supply              |

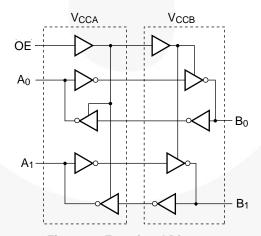

### **Functional Diagram**

Figure 2. Functional Diagram

### **Truth Table**

| Control          | Outputs          |  |  |  |

|------------------|------------------|--|--|--|

| OE               | - Outputs        |  |  |  |

| LOW Logic Level  | 3-State          |  |  |  |

| HIGH Logic Level | Normal Operation |  |  |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                              |                                                       | Min.                                | Max. | Units                   |      |  |

|-------------------------------------|-------------------------------------------------------|-------------------------------------|------|-------------------------|------|--|

| V <sub>CCA</sub> , V <sub>CCB</sub> | Supply Voltage                                        |                                     | -0.5 | 7.0                     |      |  |

|                                     |                                                       | A Port                              | -0.5 | 7.0                     | V    |  |

| $V_{IN}$                            | DC Input Voltage                                      | B Port                              | -0.5 | 7.0                     | V    |  |

|                                     |                                                       | Control Input (OE)                  | -0.5 | 7.0                     |      |  |

|                                     |                                                       | An Outputs 3-State                  | -0.5 | 7.0                     |      |  |

| \/                                  | Vo Output Voltage <sup>(1)</sup>                      | B <sub>n</sub> Outputs 3-State      | -0.5 | 7.0                     | V    |  |

| Vo                                  |                                                       | A <sub>n</sub> Outputs Active       | -0.5 | V <sub>CCA</sub> + 0.5V | V    |  |

|                                     |                                                       | B <sub>n</sub> Outputs Active       | -0.5 | V <sub>CCB</sub> + 0.5V |      |  |

| I <sub>IK</sub>                     | DC Input Diode Current                                | At V <sub>IN</sub> < 0V             |      | -50                     | mA   |  |

|                                     | DC Output Diode Current                               | At V <sub>O</sub> < 0V              |      | -50                     | mA   |  |

| I <sub>OK</sub>                     | DC Output Diode Current                               | At V <sub>O</sub> > V <sub>CC</sub> |      | +50                     | IIIA |  |

| I <sub>OH</sub> / I <sub>OL</sub>   | DC Output Source/Sink Cur                             | rent                                | -50  | +50                     | mA   |  |

| Icc                                 | DC V <sub>CC</sub> or Ground Current per Supply Pin   |                                     |      | ±100                    | mA   |  |

| T <sub>STG</sub>                    | Storage Temperature Range                             | 9                                   | -65  | +150                    | °C   |  |

| ESD                                 | Electrostatic Discharge Human Body Model, JESD22-A114 |                                     |      | 8000                    | V    |  |

| LSD                                 | Capability                                            | Charged Device Model, JESD22-C101   |      | 2000                    | V    |  |

#### Note:

1. Io absolute maximum rating must be observed.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                              |                                | Min.                                    | Max. | Units            |      |

|-------------------------------------|--------------------------------|-----------------------------------------|------|------------------|------|

| V <sub>CCA</sub> , V <sub>CCB</sub> | Power Supply Operating         |                                         | 1.65 | 5.50             | V    |

|                                     |                                | A Port                                  | 0    | 5.5              |      |

| $V_{IN}$                            |                                | B Port                                  | 0    | 5.5              | V    |

|                                     | Control Input (OE)             |                                         | 0    | V <sub>CCA</sub> |      |

| $\Delta_{t}$ / $\Delta_{V}$         | Maximum Input Edge Rate        | $V_{CCA}/_{B} = 1.65V \text{ to } 5.5V$ |      | 200              | ns/V |

| T <sub>A</sub>                      | Free Air Operating Temperature |                                         |      | +85              | °C   |

#### Note:

2. All unused inputs and I/O pins must be held at V<sub>CCI</sub> or GND. V<sub>CCI</sub> is the V<sub>CC</sub> associated with the input side.

### Power-Up/Power-Down Sequencing

FXM translators offer an advantage in that either  $V_{CC}$  may be powered up first. This benefit derives from the chip design. When either  $V_{CC}$  is at 0V, outputs are in a high-impedance state. The control input (OE) is designed to track the  $V_{CCA}$  supply. A pull-down resistor tying OE to GND should be used to ensure that bus contention, excessive currents, or oscillations do not occur during power-up/power-down. The size of the pull-down resistor is based upon the current-sinking capability of the device driving the OE pin.

The recommended power-up sequence is:

- 1. Apply power to the first V<sub>CC</sub>.

- 2. Apply power to the second  $V_{\text{CC}}$ .

- 3. Drive the OE input HIGH to enable the device.

The recommended power-down sequence is:

- 1. Drive OE input LOW to disable the device.

- 2. Remove power from either V<sub>CC</sub>.

- 3. Remove power from other V<sub>CC</sub>.

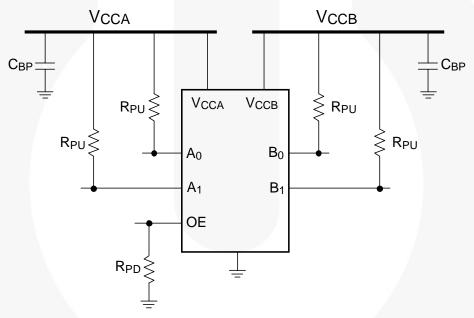

### **Application Circuit**

Figure 3. Application Circuit

### **Application Notes**

The FXM2IC102 has open-drain outputs and requires pull-up resistors on the four data I/O pins, as shown in Figure 3. If a pair of data I/O pins ( $A_n/B_n$ ) is not used, both pins should be tied to GND (or both to  $V_{CC}$ ). In this case, pull-down or pull-up resistors are not required.

The recommended values for the pull-up resistors ( $R_{PU}$ ) are  $1k\Omega$  minimum to  $10k\Omega$  maximum. The recommended value for the bypass capacitors ( $C_{BP}$ ) is  $0.1\mu F$ . The recommended value for the pull-down resistor ( $R_{PD}$ ) on OE is  $1k\Omega$  or higher and may depend upon the current-sinking capability of the device driving the OE pin.

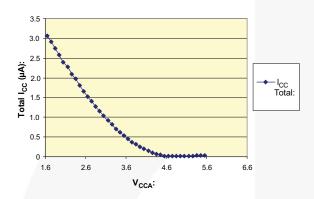

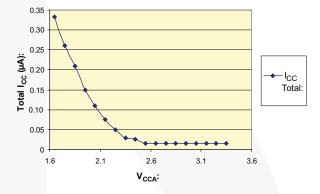

### Low I<sub>CC</sub> During I<sup>2</sup>C Idle

In a typical Mobile Internet Device (MID) application,  $I^2C$  data transactions are idle the vast majority of the time. Therefore, it is critical that the  $I^2C$  translator burns as little current as possible when no data transactions are passing across the  $I^2C$  bus. Figure 4 and Figure 5 plot the typical FXM2IC102  $I_{CC}$  performance across the entire voltage translation range during no  $I^2C$  data

transactions. In Figure 4,  $V_{\text{CCB}}$  = 5.5V and in Figure 5,  $V_{\text{CCB}}$  = 3.3V.

For example, to translate from 1.8V to 3.3V (Figure 5), with no  $I^2C$  data transactions present, the total  $I_{CC}$  of the FXM2IC102 is typically only 230nA. In effect, the FXM2IC102 virtually powers itself down when the  $I^2C$  bus is idle.

Figure 4. FXM2IC102 I<sub>CC</sub> vs. V<sub>CCA</sub> Sweep During no I<sup>2</sup>C Data Transactions (V<sub>CCB</sub> = 5.5V.  $T_A$  = +25°C)

Figure 5. FXM2IC102  $I_{CC}$  vs.  $V_{CCA}$  Sweep During no  $I^2C$  Data Transactions  $(V_{CCB} = 3.3V. T_A = +25^{\circ}C)$

#### Note:

3. Figure 4 depicts the typical  $I_{CC}$  of the FXM2IC102 when translating from 5.5V on the  $V_{CCB}$  supply to a range of 1.65V – 5.5V on the  $V_{CCA}$  supply.

#### Note:

Figure 5 depicts the typical I<sub>CC</sub> of the FXM2IC102 when translating from 3.3V on the V<sub>CCB</sub> supply to a range of 1.65V – 3.3V on the V<sub>CCA</sub> supply.

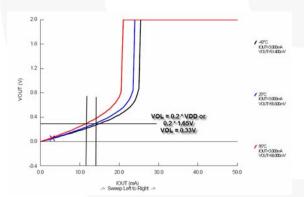

#### What Makes a Good I2C Repeater?

The  $I^2C$  specification identifies the maximum number of devices allowed on an  $I^2C$  segment as 400pf. Therefore, when an  $I^2C$  segment exceeds 400pf, a repeater is required to split the segment into two, whereby each of the individual  $I^2C$  segments does not exceed 400pf.

The question then arises, "What makes a good I<sup>2</sup>C repeater?" The question becomes complicated when considering the following factors:

- Current sinking capability of the outputs

- Output edge rates

- Distributed and lumped capacitances of the I<sup>2</sup>C segment

- Speed of the I<sup>2</sup>C bus: standard mode (100kbits/s), fast mode (400kbit/s), or fast-mode plus (1000kbit/s)

- Pull-up resistor sizing

- System signal delays, including device propagation delay and time of flight vs. meeting critical data setup/hold times

- Multiple master / slave topologies

- Clock stretching

It is possible to simplify this by focusing on the output current sinking capability relative to the bus impedance.

The DC electrical tables of the  $I^2C$  specification, for fast mode, require a maximum  $V_{OL}$  of 0.4V while sinking 3mA of current when  $V_{DD} > 2V$ , and a maximum  $V_{OL}$  of 0.2 \*  $V_{DD}$ , while sinking 3mA when  $V_{DD} < 2V$ . The

Figure 6.  $V_{OL}$  vs.  $I_{OL}$  ( $V_{DD} = 1.65V$ )

minimum  $I_{OL}$  is 3mA for a  $V_{OL}$  of 0.4V and 6mA for a  $V_{OL}$  of 0.6V.

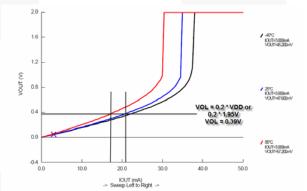

In short, the more a repeater can sink current while maintaining the maximum  $V_{OL}$ , the more capacitance it can drive at a given data rate. The  $I^2C$  specifically benchmarks this by stating: "to drive a full bus load at 400kHz, 6mA  $I_{OL}$  is required at 0.6V  $V_{OL}$ . Parts not meeting this specification can still function, but not at 400kHz and 400pF".

As shown in Figure 6, the FXM2IC102 can typically sink 11mA - 13mA, depending on temperature, while maintaining a  $V_{\text{OL}}$  of 0.33V when  $V_{\text{DD}}$  is only 1.65V. This says the FXM2IC102 delivers conservatively twice the current sinking capability for a 400pF, 1.65V segment running at 400kHz.

If  $V_{DD}=1.95V$ , (Figure 7) the FXM2IC102 can sink 18mA-21mA, depending on temperature, while maintaining a  $V_{OL}$  of 0.39V. This says the FXM2IC102 delivers conservatively 3 times the current sinking capability for a 400pF, 1.95V segment running at 400kHz.

If  $V_{DD}=3.0V$ , the FXM2IC102 can sink 25mA -30mA, depending on temperature, while maintaining a  $V_{OL}$  of 0.4V. This says the FXM2IC102 delivers conservatively 4x the current sinking capability for a 400pF, 3.0V segment running at 400kHz.

Figure 7.  $V_{OL}$  vs.  $I_{OL}$  ( $V_{DD} = 1.95V$ )

### **DC Electrical Characteristics**

$T_A = -40$ °C to +85°C.

| Symbol                          | Parameter                                    | Conditions                         |                                              | V <sub>CCA</sub> (V) | V <sub>CCB</sub> (V) | Min.                   | Max.                   | Units |

|---------------------------------|----------------------------------------------|------------------------------------|----------------------------------------------|----------------------|----------------------|------------------------|------------------------|-------|

| V                               | High Level Input                             | Data                               | nputs A <sub>n</sub>                         | 1.65-5.50            | 1.65-5.50            | 0.7 x V <sub>CCA</sub> |                        | V     |

| $V_{IHA}$                       | Voltage A                                    | Contr                              | ol Input OE                                  | 1.65-5.50            | 1.65-5.50            | 0.9 x V <sub>CCA</sub> |                        | ٧     |

| $V_{IHB}$                       | High Level Input<br>Voltage B                | Data                               | inputs B <sub>n</sub>                        | 1.65-5.50            | 1.65–5.50            | 0.7 x V <sub>CCB</sub> |                        | V     |

| $V_{ILA}$                       | Low Level Input                              | Data                               | nputs A <sub>n</sub>                         | 1.65-5.50            | 1.65-5.50            |                        | $0.3 \times V_{CCA}$   | V     |

| VILA                            | Voltage A                                    | Contr                              | ol Input OE                                  | 1.65-5.50            | 1.65-5.50            |                        | 0.1 x V <sub>CCA</sub> |       |

| $V_{ILB}$                       | Low Level Input<br>Voltage B                 | Data                               | nputs B <sub>n</sub>                         | 1.65–5.50            | 1.65–5.50            |                        | 0.3 x V <sub>CCB</sub> | ٧     |

| $V_{OLA}$                       | Low Level Output                             | Α                                  | I <sub>OL</sub> = 3mA                        | 1.65-2.30            | 1.65-5.50            |                        | 0.1 x V <sub>CCA</sub> | V     |

| VOLA                            | Voltage A <sup>(5)</sup>                     | Port                               | I <sub>OL</sub> = 6mA                        | 3.00-5.50            | 1.65–5.50            |                        | 0.2                    | V     |

| $V_{OLB}$                       | Low Level Output                             | В                                  | $I_{OL} = 3mA$                               | 1.65-5.50            | 1.65-2.30            |                        | 0.1 x V <sub>CCB</sub> | V     |

| ▼ OLB                           | Voltage B <sup>(5)</sup>                     | Port                               | I <sub>OL</sub> = 6mA                        | 1.65-5.50            | 3.00-5.50            |                        | 0.2                    |       |

| I∟                              | Input Leakage<br>Current                     |                                    | ol Input OE,<br>V <sub>CCA</sub> or GND      | 1.65–5.50            | 1.65–5.50            |                        | ±1.0                   | μΑ    |

| 1                               | Power Off                                    | An                                 | $V_{IN}$ or $V_O = 0V$ to 5.5V               | 0                    | 5.50                 |                        | ±2.0                   |       |

| I <sub>OFF</sub>                | Leakage Current                              | B <sub>n</sub>                     | $V_{IN}$ or $V_O = 0V$ to 5.5V               | 5.50                 | 0                    |                        | ±2.0                   | μA    |

|                                 |                                              | A <sub>n</sub> ,<br>B <sub>n</sub> | $V_O = 0V$ to 5.5V,<br>OE = $V_{IL}$         | 5.50                 | 5.50                 |                        | ±2.0                   |       |

| l <sub>OZ</sub>                 | 3-State Output<br>Leakage <sup>(6)</sup>     | An                                 | $V_0 = 0V$ to 5.5V,<br>OE = Don't Care       | 5.50                 | 0                    |                        | ±2.0                   | μA    |

|                                 |                                              | Bn                                 | $V_0 = 0V$ to 5.5V,<br>OE = Don't Care       | 0                    | 5.50                 |                        | ±2.0                   |       |

| I <sub>CCA</sub> / <sub>B</sub> | Quiescent Supply<br>Current <sup>(7,8)</sup> | V <sub>IN</sub> =                  | $V_{CCI}$ or GND, $I_0 = 0$                  | 1.65-5.50            | 1.65–5.50            |                        | 5.0                    | μA    |

| I <sub>CCZ</sub>                | Quiescent Supply<br>Current <sup>(7)</sup>   | V <sub>IN</sub> = OE =             | $V_{CCI}$ or GND, $I_0 = 0$ , $V_{IL}$       | 1.65-5.50            | 1.65–5.50            |                        | 5.0                    | μA    |

|                                 | Quiescent Supply                             | V <sub>IN</sub> =                  | 5.5V or GND, I <sub>O</sub> = 0,             | 0                    | 1.65-5.50            |                        | -2.0                   |       |

| I <sub>CCA</sub>                | Current <sup>(6)</sup>                       | OE =                               | Don't Care, B <sub>n</sub> to A <sub>n</sub> | 1.65-5.50            | 0                    |                        | 2.0                    | μA    |

| lass                            | Quiescent Supply                             | V <sub>IN</sub> =                  | 5.5V or GND, I <sub>O</sub> = 0,             | 1.65-5.50            | 0                    |                        | -2.0                   |       |

| I <sub>CCB</sub>                | Current <sup>(6)</sup>                       | OE =                               | Don't Care, A <sub>n</sub> to B <sub>n</sub> | 0                    | 1.65-5.50            |                        | 2.0                    | μA    |

- This is the output voltage for static conditions. Dynamic drive specifications are given in the Dynamic Output Electrical Characteristics table.

- "Don't Care" indicates any valid logic level.  $V_{\text{CCI}}$  is the  $V_{\text{CC}}$  associated with the input side.

- Reflects current per supply, V<sub>CCA</sub> or V<sub>CCB</sub>.

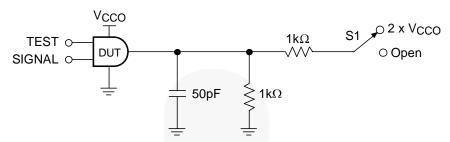

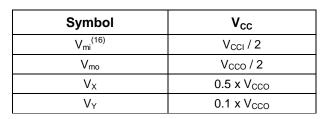

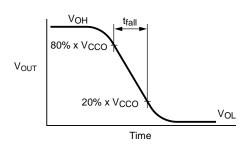

### **Dynamic Output Electrical Characteristics**

Output rise / fall time and dynamic output current<sup>(9)</sup>. Output load:  $C_L = 50 pF$ ,  $R_L = 1 k\Omega$ .  $T_A = -40 °C$  to +85 °C.

|                   |                                                  | V <sub>cco</sub> : <sup>(10)</sup> |      |        |      |        |      |         |       |       |

|-------------------|--------------------------------------------------|------------------------------------|------|--------|------|--------|------|---------|-------|-------|

| Symbol            | Symbol Parameter                                 |                                    | 5.5V | 3.0 to | 3.6V | 2.3 to | 2.7V | 1.65 to | 1.95V | Units |

|                   |                                                  | Тур.                               | Max. | Тур.   | Max. | Тур.   | Max. | Тур.    | Max.  |       |

| t <sub>rise</sub> | Output Rise Time, A Port, B Port <sup>(11)</sup> |                                    | 4    |        | 5    |        | 6    |         | 8     | ns    |

| t <sub>fall</sub> | Output Fall Time, A Port, B Port <sup>(12)</sup> |                                    | 4    |        | 5    |        | 6    |         | 8     | ns    |

| I <sub>OHD</sub>  | Dynamic Output Current HIGH <sup>(11)</sup>      | -45                                |      | -24    |      | -15    |      | -8      |       | mA    |

| I <sub>OLD</sub>  | Dynamic Output Current LOW (12)                  | +45                                |      | +24    |      | +15    |      | +8      |       | mA    |

#### Notes:

- 9. Dynamic output characteristics are guaranteed, but not tested.

- 10.  $V_{\text{CCO}}$  is the  $V_{\text{CC}}$  associated with the output side.

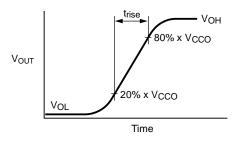

- 11. See Figure 12.12. See Figure 13.

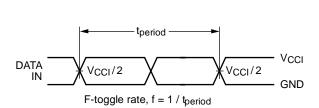

### Maximum Data Rate(13)

Output Load:  $C_L = 50 pF$ ,  $R_L = 1 k\Omega$ .  $T_A = -40 °C$  to +85 °C.

| V <sub>CCA</sub> | 4.5 to 5.5V | 3.0 to 3.6V | 2.3 to 2.7V | 1.65 to 1.95V | Units |

|------------------|-------------|-------------|-------------|---------------|-------|

|                  | Min.        | Min.        | Min.        | Min.          |       |

| 4.5V to 5.5V     | 40          | 35          | 30          | 20            | MHz   |

| 3.0V to 3.6V     | 35          | 35          | 30          | 20            | MHz   |

| 2.3V to 2.7V     | 30          | 30          | 25          | 20            | MHz   |

| 1.65V to 1.95V   | 20          | 20          | 20          | 20            | MHz   |

#### Notes:

13. Maximum data rate is guaranteed, but not tested.

### Capacitance

$T_A = +25$ °C.

| Symbol           | Parameter                          | Conditions                                                           | Typical | Units |

|------------------|------------------------------------|----------------------------------------------------------------------|---------|-------|

| C <sub>IN</sub>  | Input Capacitance Control Pin (OE) | $V_{CCA} = V_{CCB} = GND$                                            | 4       | pF    |

| C <sub>I/O</sub> | Input/Output Capacitance, An, Bn   | $V_{CCA} = V_{CCB} = 5.0V$ , $OE = V_{CCA}$                          | 6       | pF    |

| $C_{pd}$         | Power Dissipation Capacitance      | $V_{CCA} = V_{CCB} = 5.0V$ , $V_{IN} = 0V$ or $V_{CC}$ , $f = 10MHz$ | 40      | pF    |

### **AC Characteristics**

Output Load:  $C_L$  = 50pF,  $R_L$  = 1k $\Omega$ .  $T_A$  = -40°C to +85°C.

|                        |                                | V <sub>CCB</sub> : |      |        |      |        |      |         |       |       |

|------------------------|--------------------------------|--------------------|------|--------|------|--------|------|---------|-------|-------|

| Symbol                 | Parameter                      | 4.5 to             | 5.5V | 3.0 to | 3.6V | 2.3 to | 2.7V | 1.65 to | 1.95V | Units |

|                        |                                | Min.               | Max. | Min.   | Max. | Min.   | Max. | Min.    | Max.  |       |

| V <sub>CCA</sub> = 4.5 | 5 to 5.5V                      |                    |      |        |      |        |      | •       |       |       |

|                        | A to B                         | 1.0                | 4.5  | 1.5    | 5.5  | 2.0    | 7.0  | 3.0     | 11.5  |       |

| t <sub>PLH</sub>       | B to A                         | 1.0                | 4.5  | 1.5    | 5.5  | 1.5    | 6.5  | 2.5     | 9.5   | ns    |

|                        | A to B                         | 2.0                | 6.0  | 2.5    | 6.5  | 3.0    | 8.0  | 4.0     | 12.5  |       |

| t <sub>PHL</sub>       | B to A                         | 2.0                | 6.0  | 2.5    | 7.0  | 3.0    | 8.0  | 3.5     | 12.0  | ns    |

| 4                      | OE to A                        |                    | 9.5  |        | 10.0 |        | 11.5 |         | 18.0  |       |

| $t_{PZL}$              | OE to B                        |                    | 9.0  |        | 11.0 |        | 13.5 |         | 22.0  | ns    |

|                        | OE to A                        |                    | 26.5 |        | 26.5 |        | 26.5 |         | 26.5  |       |

| $t_{PLZ}$              | OE to B                        |                    | 26.0 |        | 26.5 |        | 20.5 |         | 15.5  | ns    |

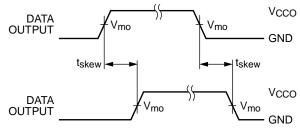

| t <sub>skew</sub>      | A Port, B Port <sup>(14)</sup> |                    | 0.5  |        | 0.5  |        | 0.5  |         | 0.5   | ns    |

| $V_{CCA} = 3.0$        | 0 to 3.6V                      |                    |      |        |      |        |      |         |       |       |

| . /                    | A to B                         | 1.5                | 5.5  | 1.5    | 6.5  | 2.0    | 8.0  | 3.0     | 12.0  | ,     |

| t <sub>PLH</sub>       | B to A                         | 1.5                | 5.5  | 1.5    | 6.5  | 2.0    | 7.5  | 2.5     | 10.5  | ns    |

| 7                      | A to B                         | 2.5                | 7.0  | 2.5    | 7.5  | 3.0    | 9.0  | 4.0     | 13.0  |       |

| t <sub>PHL</sub>       | B to A                         | 2.5                | 6.5  | 2.5    | 7.5  | 3.0    | 9.5  | 4.0     | 13.0  | ns    |

|                        | OE to A                        |                    | 12.5 |        | 13.0 |        | 15.5 |         | 21.0  |       |

| t <sub>PZL</sub>       | OE to B                        |                    | 10.0 |        | 12.5 |        | 14.5 |         | 22.5  | ns    |

|                        | OE to A                        |                    | 27.5 |        | 28.0 |        | 28.0 |         | 28.0  |       |

| t <sub>PLZ</sub>       | OE to B                        |                    | 27.5 |        | 28.0 |        | 28.5 |         | 22.5  | ns    |

| t <sub>skew</sub>      | A Port, B Port <sup>(14)</sup> |                    | 0.5  |        | 0.5  |        | 0.5  |         | 0.5   | ns    |

| V <sub>CCA</sub> = 2.3 | 3 to 2.7V                      | •                  |      | •      | •    |        |      |         |       |       |

|                        | A to B                         | 1.5                | 6.5  | 2.0    | 7.5  | 2.5    | 8.5  | 3.5     | 12.5  |       |

| t <sub>PLH</sub>       | B to A                         | 2.0                | 7.5  | 2.0    | 8.0  | 2.5    | 8.5  | 3.0     | 11.5  | ns    |

|                        | A to B                         | 3.0                | 8.5  | 3.0    | 9.5  | 3.0    | 10.0 | 4.0     | 13.5  |       |

| t <sub>PHL</sub>       | B to A                         | 3.0                | 8.0  | 3.0    | 9.0  | 3.0    | 10.0 | 4.5     | 14.0  | ns    |

|                        | OE to A                        |                    | 16.0 |        | 16.5 |        | 18.0 |         | 23.5  |       |

| t <sub>PZL</sub>       | OE to B                        |                    | 11.0 |        | 14.0 |        | 15.5 |         | 23.5  | ns    |

| . \                    | OE to A                        |                    | 29.0 |        | 29.0 |        | 29.5 |         | 29.5  |       |

| t <sub>PLZ</sub>       | OE to B                        |                    | 29.0 |        | 29.0 |        | 29.5 |         | 29.5  | ns    |

| t <sub>skew</sub>      | A Port, B Port <sup>(14)</sup> |                    | 0.5  |        | 0.5  | -      | 0.5  |         | 0.5   | ns    |

|                        | 65 to 1.95V                    |                    |      |        |      |        |      | 7       |       |       |

|                        | A to B                         | 2.5                | 9.5  | 2.5    | 10.5 | 3.0    | 11.5 | 4.0     | 15.0  |       |

| t <sub>PLH</sub>       | B to A                         | 3.0                | 11.5 | 3.0    | 12.0 | 3.5    | 12.5 | 4.0     | 15.0  | ns    |

|                        | A to B                         | 3.5                | 11.5 | 4.0    | 12.5 | 4.5    | 14.0 | 5.0     | 15.5  |       |

| t <sub>PHL</sub>       | B to A                         | 4.0                | 12.5 | 4.0    | 13.0 | 4.0    | 13.5 | 5.0     | 15.5  | ns    |

|                        | OE to A                        |                    | 27.0 |        | 27.0 |        | 27.0 |         | 30.0  |       |

| t <sub>PZL</sub>       | OE to B                        |                    | 18.0 | 1,1    | 19.5 |        | 22.5 |         | 29.0  | ns    |

|                        | OE to A                        |                    | 34.0 |        | 34.0 |        | 34.5 |         | 35.0  |       |

| t <sub>PLZ</sub>       | OE to B                        |                    | 31.5 |        | 32.5 |        | 33.5 |         | 36.5  | ns    |

| t <sub>skew</sub>      | A Port, B Port <sup>(14)</sup> |                    | 0.5  |        | 0.5  |        | 0.5  |         | 0.5   | ns    |

#### Note:

<sup>14.</sup> Skew is the variation of propagation delay between output signals and applies only to output signals on the same port (A<sub>n</sub> or B<sub>n</sub>) and switching with the same polarity (LOW-to-HIGH or HIGH-to-LOW) (see Figure 15). Skew is guaranteed, but not tested.

## **Applications Test Circuit**

Figure 8. AC Test Circuit

Table 1. Propagation Delay Table

| Test                                                      | Input Signal | Output Enable Control | S1 Position          |

|-----------------------------------------------------------|--------------|-----------------------|----------------------|

| t <sub>PLH</sub> , t <sub>PHL</sub>                       | Data Pulses  | V <sub>CCA</sub>      | Open                 |

| t <sub>PZL</sub> (OE to A <sub>n</sub> , B <sub>n</sub> ) | 0V           | LOW to HIGH Switch    | 2 x V <sub>CCO</sub> |

| $t_{PLZ}$ (OE to $A_n$ , $B_n$ )                          | 0V           | HIGH to LOW Switch    | 2 x V <sub>CCO</sub> |

Table 2. AC Load Table

| V <sub>cco</sub> | C <sub>L</sub> | R <sub>L</sub> |

|------------------|----------------|----------------|

| 1.8 ±0.15V       | 50pF           | 1kΩ            |

| 2.5 ±0.2V        | 50pF           | 1kΩ            |

| 3.3 ±0.3V        | 50pF           | 1kΩ            |

| 5.0 ±0.5V        | 50pF           | 1kΩ            |

### **Timing Diagrams**

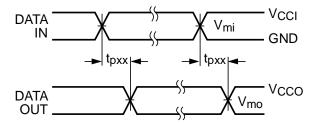

Figure 9. Waveform for Inverting and Non-Inverting Functions (15)

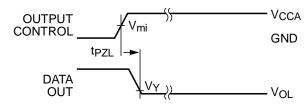

Figure 10. 3-STATE Output Low Enable Time<sup>(15)</sup>

| OUTPUT<br>CONTROL | VCCA Vmi        |

|-------------------|-----------------|

| DATA<br>OUT       | V <sub>OL</sub> |

Figure 11. 3-STATE Output High Enable Time<sup>(15)</sup>

$$I_{OHD} \approx (C_{L} + C_{I/O}) \times \frac{\Delta V_{OUT}}{\Delta t} = (C_{L} + C_{I/O}) \times \frac{(20\% - 80\%) \times V_{CCO}}{t_{PISF}}$$

(80% - 20%) x V<sub>CCO</sub>  $I_{OLD} \approx \, \left( C_{L} + C_{I/O} \right) \, x \, \frac{\Delta V_{OUT}}{\Delta t} = \left( C_{L} \, {}_{+} C_{I/O} \right) \, x \,$

Figure 12. Active Output Rise Time and Dynamic **Output Current High**

Figure 13. Active Output Fall Time and Dynamic **Output Current Low**

tskew = (tpHLmax - tpHLmin) or (tpLHmax - tpLHmin)

Figure 15. Output Skew Time

Figure 14. Maximum Data Rate (or F-Toggle) in MHz

Notes:

- 15. Input  $t_R = t_F = 2.0$ ns, 10% to 90% at  $V_{IN} = 1.65$ V to 1.95V; Input  $t_R = t_F = 2.0$ ns, 10% to 90% at  $V_{IN} = 2.3$  to 2.7V; Input  $t_R = t_F = 2.5 \text{ns}$ , 10% to 90%, at  $V_{IN} = 3.0 \text{V}$  to 3.6V only; Input  $t_R = t_F = 2.5$ ns, 10% to 90%, at  $V_{IN} = 4.5$ V to 5.5 only.

- 16.  $V_{CCI} = V_{CCA}$  for control pin OE or  $V_{mi} = (V_{CCA} / 2)$ .

www.fairchildsemi.com

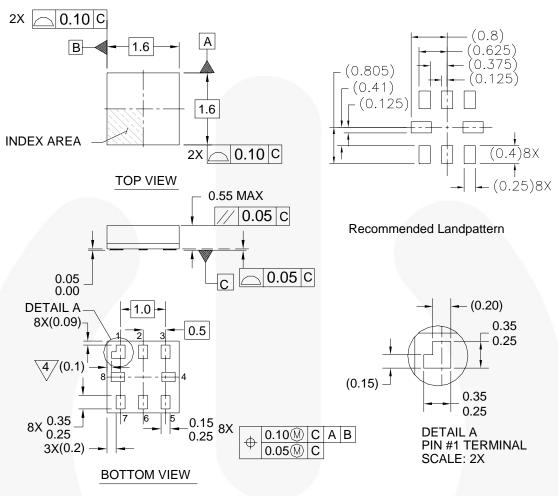

### **Physical Dimensions**

#### Notes:

- 1. PACKAGE CONFORMS TO JEDEC MO-255 VARIATION UAAD

- 2. DIMENSIONS ARE IN MILLIMETERS

- 3. DRAWING CONFORMS TO ASME Y.14M-1994

- 4/PIN 1 FLAG, END OF PACKAGE OFFSET

- 5. DRAWING FILE NAME: MKT-MAC08AREV4

MAC08AREV4

Figure 16. 8-Lead MicroPak™, 1.6mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

#### Tape & Reel Format for MicroPak™

Always visit Fairchild Semiconductor's online packaging area for the most recent tape and reel specifications: <a href="http://www.fairchildsemi.com/products/logic/pdf/micropak\_tr.pdf">http://www.fairchildsemi.com/products/logic/pdf/micropak\_tr.pdf</a>.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ EPST# Auto-SPM™ F-PFS™ Build it Now™ FRFET®

CorePLUS™ CorePOM/ER™ Green FPS™ CROSSVOLT™ Green FPS™ e-Series™

CTL™ Current Transfer Logic™ EcoSPARK® EfficientMax™ EZSWTCH™\*

Fairchild®

Fairchild Semiconductor® FACT Quiet Series™ FACT

FAST® EastvCore™

EETBench™ FlashVVriter®\*

Global Power Resource<sup>SM</sup>

G*тах*™ GTO™ IntelliMAX™

ISOPLANAR™ MegaBuck™ MICROCOUPLER™

MicroFET™ MicroPak™ MillerDrive™ MotionMa×™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR®

PDP SPM™ Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™ QFET®

QS™

Quiet Series™ RapidConfigure™

Saving our world, 1mWWW/kW at a time™ SignalWise™

SmartMax™ SMART START™ SPM®

STEALTH™ SuperFET™ SuperSOT™3 SuperSOT\*\*6 SuperSOT™8 SupreMOS™ SyncFET™ Sync-Lock™

SYSTEM GENERAL

TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>6</sup> TINYOPTO\*\* TinyPower™ TinyPWM™ TinyWire™ TriFault Detect™ TRUECURRENT" μSerDes™

UHC<sup>®</sup> Ultra FRFET™ UniFET™ VCX<sup>TM</sup> VisualMax™ XS™

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- 1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Definition of Terms      |                       |                                                                                                                                                                                                     |  |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |  |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                 |  |

Rev. 142

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.