# **LIMITED DATASHEET**

Email <u>Analog.Switch@fairchildsemi.com</u> to request the full datasheet.

# FUSB2500 USB2.0 High-Speed OTG Transceiver with ULPI Interface

#### **Features**

- Complies with USB 2.0 OTG Rev 1.3 Supplement and ULPI Rev 1.1 Specifications

- Supports 480Mbps, 12Mbps, and 1.5Mbps USB2.0 Speeds

- Integrated Termination Resistors Meet USB2.0 Resistor ECN

- Integrated Serializer and Deserializer

- Insertion and Removal of Stuffed Bits as Appropriate

- USB Clock and Data Recovery to ±150ppm

- Supports USB OTG Rev 1.3 Host Negotiation Protocol (HNP) and Session Request Protocol (SRP)

### **Applications**

- Cell phones, Digital Still Camera, PDA

- DVD Recorder, Scanner, Printer

- Video Camera, Set-Top Box, MP3 Player

#### **IMPORTANT NOTE:**

For additional performance information, please contact <u>analogswitch@fairchildsemi.com</u>.

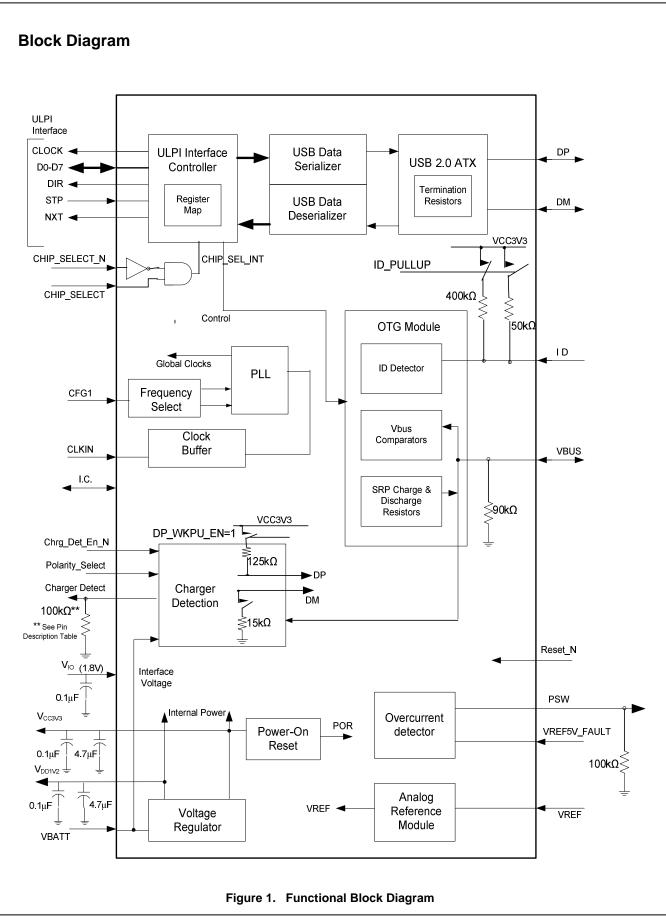

### Description

The FUSB2500 is a UTMI+ Low-Pin Interface (ULPI) USB2.0 On-The-Go (OTG) transceiver. It is compliant with the Universal Serial Bus Specification Rev 2.0 (USB2.0), the ULPI Specification Rev. 1.1, and the OOTG Supplement to USB2.0, Rev. 1.3.

The FUSB2500 is optimized to connect the USB2.0 host, peripheral, or OTG-controller to the USB connector via the ULPI link. Data can be transmitted and received at high speed (480Mbps), full speed (12Mbps), and low speed (1.5Mbps) through a 12-bit (SDR) interface.

The FUSB2500 also includes a charger-detection functional block that enables automatic detection for charging USB2.0 host ports or dedicated chargers. The FUSB2500 is compliant with Battery Charging Specification Rev. 1.0.

#### Related Resources

- UTMI+ Low Pin Interface Specification (ULPI), Revision 1.1, October 20, 2004. http://www.ulpi.org

- UTMI+ Specification, Revision 1.0, February 22, 2004. http://www.ulpi.org

## **Ordering Information**

| Part Number | Top Mark | Operating Temperature Range | Package                                                        |

|-------------|----------|-----------------------------|----------------------------------------------------------------|

| FUSB2500GFX | FUSB2500 | -40 to +85°C                | 36-Ball, Ball Grid Array (BGA), 3.5 x 3.5 x 1.0mm, 0.5mm Pitch |

# **Ball Configuration**

| F | Polarity<br>Select            | Charger<br>Detect | VBATT            | VBUS                  | CLKIN<br>(19.2MHz) | ı.c.   |

|---|-------------------------------|-------------------|------------------|-----------------------|--------------------|--------|

| E | Charger<br>Detect<br>Enable_N | VREF5V_<br>FAULT  | VCC3V3           | GND                   | DIR                | VDD1V2 |

| D | DP                            | GND               | ID               | PSW                   | NXT                | STP    |

| С | DM                            | RREF              | Chip<br>Select_N | Reset_N               | GND                | D7     |

| В | D0                            | VIO (1.8V)        | Chip_Select      | CFG1 (GND<br>19.2MHz) | VIO (1.8V)         | D6     |

| Α | D1                            | D2                | D3               | CLOCK                 | D4                 | D5     |

| • | 1                             | 2                 | 3                | 4                     | 5                  | 6      |

Figure 2. Ball Configuration (Bottom Up View)

# **Pin Definitions**

| Symbol <sup>(1)</sup>      | Ball | Type <sup>(2)</sup> | Description                                                                                                                                                                                                                                                                                                                     |

|----------------------------|------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip_Select                | В3   | I                   | Active HIGH. LOW – ULPI pin three-stated; HIGH – ULPI operates normally. TTL compatible; CMOS input with hysteresis. If either Chip_Select or Chip_Select_N are de-asserted, the FUSB2500 is in power down and the ULPI bus is three-stated. For ULPI to operate, both signals need to be active.                               |

| Chip Select_N              | C3   | I                   | Active LOW. HIGH – ULPI pin three-stated; LOW – ULPI operates normally. TTL compatible; CMOS input with hysteresis. If either Chip_Select or Chip_Select_N are de-asserted, the FUSB2500 is in power down and the ULPI bus is three-stated. For ULPI to operate, both signals need to be active.                                |

| R <sub>REF</sub>           | C2   | AI/O                | Resistor reference. Connect through 12k $\Omega$ ±1% to GND.                                                                                                                                                                                                                                                                    |

| DM                         | C1   | AI/O                | USB D- pin. This pin is 5V tolerant. USB mode: data minus (D-) pin of the USB cable.                                                                                                                                                                                                                                            |

| DP <sup>(3)</sup>          | D1   | AI/O                | USB D+ pin. This pin is 5V tolerant. USB mode: data plus (D+) pin of the USB cable.                                                                                                                                                                                                                                             |

| VREF5V_FAULT               | E2   | I                   | VREF5V_FAULT is used to signal a V <sub>BUS</sub> over-current/over-voltage condition from an external SMPS or power management IC. The link must enable this function via the ExternalVbusFault register bit and the polarity must be set via the ExternalVbusActiveLow register bit.                                          |

| ID                         | D3   | I                   | Identification (ID) pin of the micro-USB cable. TTL, If not used, connect to the $V_{\text{CC3V3}}$ pin.                                                                                                                                                                                                                        |

| Charger Detect             | F2   | 0                   | If polarity is to be active LOW, connect $100 \text{K}\Omega$ to $V_{BATT}$ (in open-drain mode). If polarity is to be active HIGH, $100 \text{K}\Omega$ to GND is needed (open source). This is a 5V-tolerant pin referenced to an internal 3.3V rail generated from $V_{BATT}$ for charger detection when in power-down mode. |

| Polarity Select            | F1   | I                   | When connected to GND, the charger-detect signal is active LOW. When connected to $V_{BATT}$ , the charger detect signal is active HIGH. This is a 5V-tolerant pin referenced to an internal 3.3V rail generated from $V_{BATT}$ for charger detection when in power-down mode.                                                 |

| Charger Detect<br>Enable_N | E1   | I                   | Active LOW. Connect to GND to activate. Connect to $V_{BATT}$ when charger detection is not required. This is a 5V-tolerant pin referenced to an internal 3.3V rail generated from $V_{BATT}$ for charger detection when in power-down mode.                                                                                    |

| V <sub>BATT</sub>          | F3   | Р                   | Input supply voltage or battery source. Nominally 2.7V to 4.5V. Operation of USB should function down to $V_{BATT}$ of 3.0V. Products may stop operating at $V_{BATT}$ of 3.1V. (4)                                                                                                                                             |

| PSW                        | D4   | 0                   | Controls an external, active HIGH, $V_{BUS}$ power switch/charge pump and/or an SMPS charger IC. An external 100K $\Omega$ pull-down resistor is required. Open source, this pin is referenced to $V_{CC3V3}$ .                                                                                                                 |

| V <sub>BUS</sub>           | F4   | AI/O                | Should be connected to the $V_{BUS}$ pin of the USB cable. Leave open circuit if not used. An internal 90K $\Omega$ ±11% pull-down resistor is present on this pin.                                                                                                                                                             |

| V <sub>CC3V3</sub>         | E3   | Р                   | 3.3V regulator output requiring capacitors. Internally powers OTG, analog core, and ATX. External capacitors are 0.1μF and 4.7μF.                                                                                                                                                                                               |

| CLKIN                      | F5   | I                   | Clock input; 1.8V peak input allowed; frequency depends on the CFG1 pin. This is a digital input buffer, not analog for a crystal.                                                                                                                                                                                              |

| I.C.                       | F6   | I/O                 | Internally connected; leave OPEN.                                                                                                                                                                                                                                                                                               |

Continued on the following page...

# Pin Definitions (Continued)

| Symbol <sup>(1)</sup> | Ball         | Type <sup>(2)</sup> | Description                                                                                                               |

|-----------------------|--------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|

| CFG1                  | B4           | 1                   | Configures the clock frequency; 0: input is 19.2MHz. 1: input is 26MHz.                                                   |

| V <sub>DD1V2</sub>    | E6           | Р                   | 1.2V regulator output requiring capacitors. Internally powers the digital core. External capacitors are 0.1µF and 4.7µF.  |

| DIR                   | E5           | 0                   | ULPI direction output signal; slew-rate-controlled output (2ns typical).                                                  |

| STP                   | D6           | -                   | ULPI stop input signal; CMOS input.                                                                                       |

| NXT                   | D5           | 0                   | ULPI next output signal; slew-rate-controlled output (2ns typical).                                                       |

| D7                    | C6           | I/O                 | ULPI data pin 7; three-state output; slew-rate-controlled output (2ns typical); CMOS input.                               |

| D6                    | В6           | I/O                 | ULPI data pin 6; three-state output; slew-rate-controlled output (2ns typical); CMOS input.                               |

| D5                    | A6           | I/O                 | ULPI data pin 5; three-state output; slew-rate-controlled output (2ns typical); CMOS input.                               |

| D4                    | A5           | I/O                 | ULPI data pin 4; three-state output; slew-rate-controlled output (2ns typical); CMOS input.                               |

| D3                    | A3           | I/O                 | ULPI data pin 3; three-state output; slew-rate-controlled output (2ns typical); CMOS input.                               |

| D2                    | A2           | I/O                 | ULPI data pin 2; three-state output; slew-rate-controlled output ( 2ns typical); CMOS input.                              |

| D1                    | A1           | I/O                 | ULPI data pin 1; three-state output; slew-rate-controlled output ( 2ns typical); CMOS input.                              |

| D0                    | B1           | I/O                 | ULPI data pin 0; three-state output; slew-rate-controlled output ( 2ns typical); CMOS input.                              |

| CLOCK                 | A4           | 0                   | 60MHz clock output when digital 19.2MHz (or 26MHz) clock is applied; Push-pull output; slew-rate-controlled output (2ns). |

| V <sub>IO</sub>       | B2, B5       | Р                   | Input I/O supply rail; 1.65V-1.95V; nominally 1.8V. 0.1µF capacitor connected to power input.                             |

| Reset_N               | C4           | I                   | Connect to V <sub>IO</sub> 1.8V when not used. Resets the transceiver; active LOW.                                        |

| GND                   | E4,D2,<br>C5 | Р                   | Connect to ground.                                                                                                        |

#### Notes:

- 1. Symbol names ending with underscore N (for example, NAME\_N) indicate active LOW signals.

- 2. I=input; O=output; I/O=digital input/output; OD=open-drain output; AI/O=analog input/output; P=power or ground pin.

- 3. A 125K $\Omega$  resistor is used for basic charger detection.

- 4. Per the USB2.0 specification, below a supply of 2.97V, USB full-speed and low-speed transactions are not guaranteed; although some devices may continue to function with the FUSB2500 at the lower supply rail.

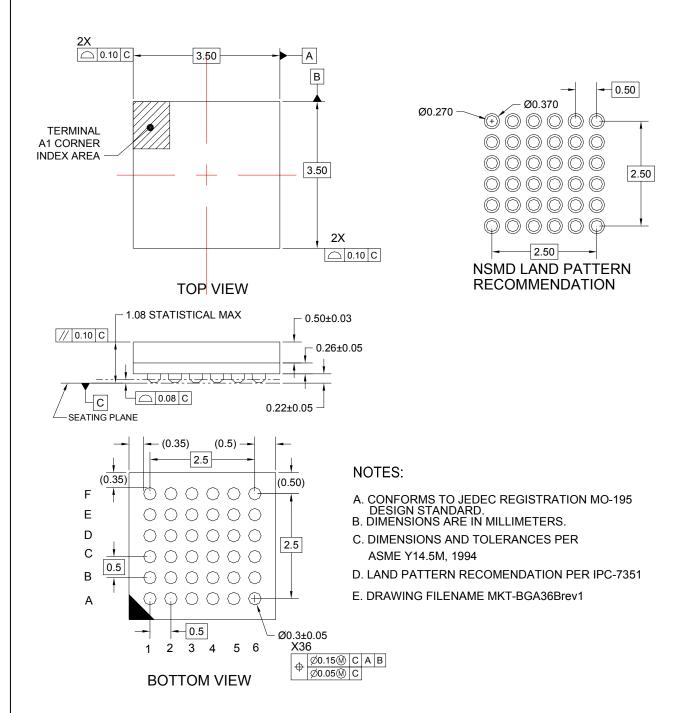

## **Physical Dimensions**

Figure 24. 36-Ball BGA Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

# O

#### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool™

F-PFS™

AccuPower™

FRFET®

AX-CAP™\*

Global Power Resource®™

BitSiC™

GreenBridge™

Build it Now™

Green FPS™

CorePLUS™

Green FPS™ e-Series™

OTE

Current Transfer Logic™

DEUXPEED®

Dual Cool™

SOPLANAR™

Making Small Speakers Sound Louder

and Better™

Dual Cool™ and Better™

EcoSPARK® MegaBuck™

EfficientMax™ MICROCOUPLER™

ESBC™ MicroFET™

MicroPak™

MicroPak2™ Fairchild® MillerDrive™ Fairchild Semiconductor® MotionMax™ FACT Quiet Series™ Motion-SPM™ FACT mWSaver™ FAST® OptoHiT™ FastvCore™ OPTOLOGIC® FFTBench™ **OPTOPLANAR®** FlashWriter®\*

QFĒT®

QS™

Quiet Series™

RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™

SMART START™ Solutions for Your Success™

Programmable Active Droop™

SPM®

STEALTH™

SUPERFET®

SUPERSOT™-3

SUPERSOT™-6

SUPERSOT™-8

SUPERMOS®

SYNCFET™

SYNC-LOCK™

SYSTEM

GENERAL®\*

PowerTrench®

PowerXS™

SmartMax™

The Power Franchise®

Franchise

TinyBoost™

TinyBuck™

TinyCalc™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPWM™

TinyWire™

TranSiC™

TriFault Detect™

TRUECURRENT®\*\*

µSerDes™

VERDES

UHC®

Ultra FRFET™

UniFET™

VCX™

VisualMax™

VoltagePlus™

XS™

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

**FPSTM**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a)

are intended for surgical implant into the body or (b) support or

sustain life, and (c) whose failure to perform when properly used in

accordance with instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. I61