# FAN5033 8-Bit Programmable, 2- to 3-Phase, Synchronous Buck Controller

### Features

- Selectable 2- or 3-phase operation at up to 1MHz per phase

- ±7.7mV worst-case differential sensing error over temperature

- Active current balancing between the output phases

- Power Good and Crowbar blanking supports on-the-fly VID code changes

- 0.5V to 1.6V output

- Fully compliant with the Intel<sup>®</sup> VR10 and VR11 specifications

- Selectable VR10 extended (7-bit) and VR11 (8-bit) VID tables

- Programmable soft-start ramp

- Programmable short-circuit protection and latch-off delay

## Applications

- Desktop PC/Server processor power supplies for existing and next-generation Intel processors

- VRM modules

## Description

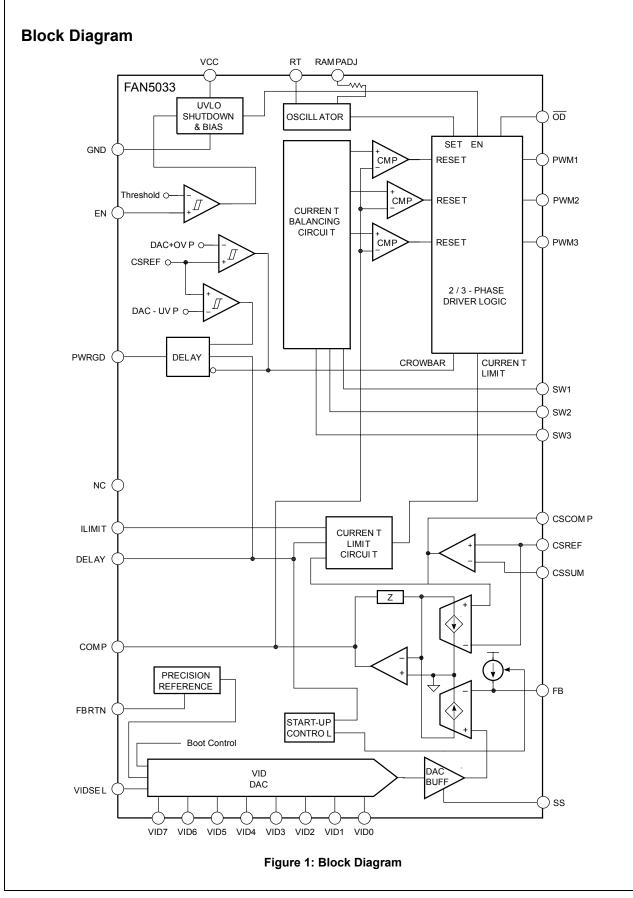

The FAN5033 device is a multi-phase buck switching regulator controller optimized to convert a 12V input supply to the processor core voltage required by high performance Intel<sup>®</sup> processors. It has an internal 8-bit DAC that converts a digital voltage identification (VID) code, sent from the processor, to set the output voltage between 0.5V and 1.6V in 6.25mV steps. It outputs PWM signals to external MOSFET drivers that drive the switching power MOSFETs. The switching frequency of the design is programmable by a single resistor value. The number of phases can be programmed to support two- or three-phase applications.

The FAN5033 also includes programmable no-load offset and droop functions to adjust the output voltage as a function of the load current, as required by the Intel specifications. The FAN5033 provides an accurate and reliable short-circuit protection function with an adjustable over-current set point.

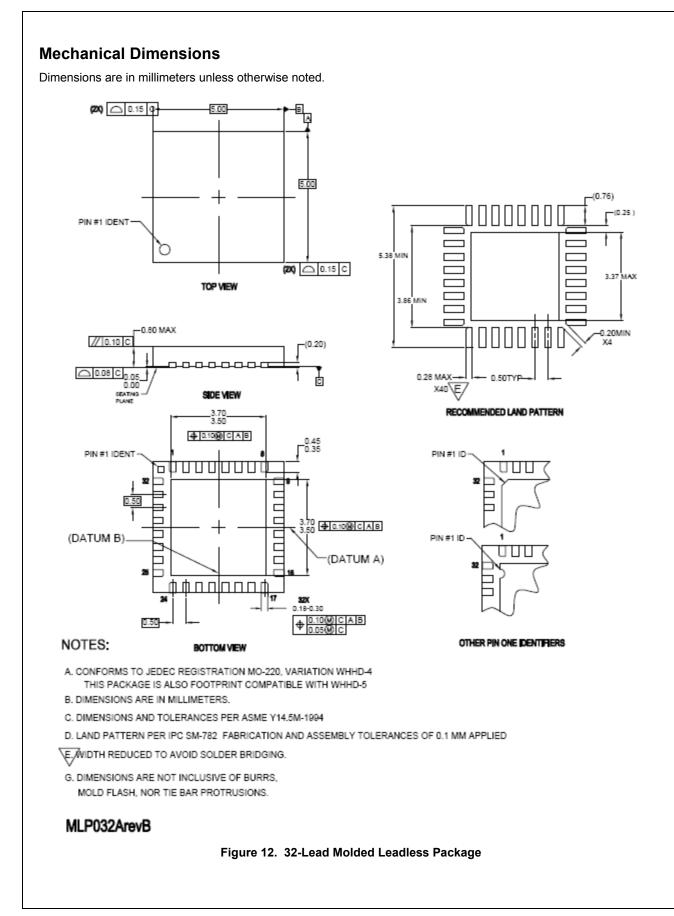

The FAN5033 is specified over the commercial temperature range of 0°C to +85°C and is available in a 32-lead MLP package.

### **Ordering Information**

| Part Number | Temperature Range | Pb-Free | Package Type | Packing Method | Quantity       |

|-------------|-------------------|---------|--------------|----------------|----------------|

| FAN5033MPX  | 0°C to 85°C       | Yes     | MLP-32       | Tape and Reel  | 3,000 per Reel |

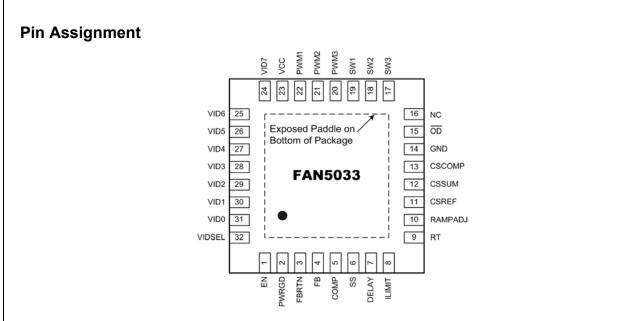

Figure 2: Pin Assignment

# **Pin Definitions**

| Pin # | Name    | Description                                                                                                                                                                                                          |

|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | EN      | <b>Power Supply Enable Input</b> . Analog comparator input with hysteresis. If input voltage is higher than the internal threshold, the controller is enabled. If lower, the controller is disabled.                 |

| 2     | PWRGD   | <b>Power Good Output</b> . Open drain output that pulls to GND when the output voltage is outside the proper operating range.                                                                                        |

| 3     | FBRTN   | Feedback Return. VID DAC and Error Amplifier reference for remote sensing of output voltage.                                                                                                                         |

| 4     | FB      | <b>Feedback Input</b> . Error amplifier input for remote sensing of output voltage. A positive internal current source is connected to this pin to allow the output voltage to be offset lower than the DAC voltage. |

| 5     | COMP    | Error Amplifier Output. For loop compensation.                                                                                                                                                                       |

| 6     | SS      | <b>Soft-Start Input</b> . An external capacitor connected between this pin and GND sets the soft-start ramp-up time.                                                                                                 |

| 7     | DELAY   | <b>Delay Timer Input</b> . An external capacitor connected between this pin and GND sets th over-current latch-off delay time, BOOT voltage hold time, EN delay time, and PWRGD delay time.                          |

| 8     | ILIMIT  | <b>Current Limit Set</b> . An external resistor from this pin to GND sets the current limit threshold of the converter.                                                                                              |

| 9     | RT      | <b>Frequency Set Input</b> . An external resistor connected between this pin and GND sets the oscillator frequency of the device.                                                                                    |

| 10    | RAMPADJ | <b>PWM Ramp Set Input</b> . An external resistor connected between this pin and the converter input voltage sets the internal PWM ramp.                                                                              |

| 11    | CSREF   | <b>Current Sense Amplifier Positive Input</b> . The voltage on this pin is used as the reference for the current sense amplifier. The Power Good and Crowbar functions are also internally connected to this pin.    |

| 12    | CSSUM   | Current Sense Amplifier Negative Input.                                                                                                                                                                              |

| 13    | CSCOMP  | Current Sense Amplifier Compensation Output.                                                                                                                                                                         |

FAN5033 — 8-Bit Programmable 2- to 3-Phase Synchronous Buck Controller

| Pin #    | Name              | Description                                                                                                                                                                                                                                           |

|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14       | GND               | <b>Ground</b> . All internal biasing and logic output signals of the device are referenced to this ground.                                                                                                                                            |

| 15       | OD                | <b>Output Disable</b> . This pin is actively pulled low when the EN input is low or when $V_{CC}$ is below its UVLO threshold to disable the external MOSFET drivers. (Also referred to as OD# in the text of this document.)                         |

| 16       | NC                | No Connection. This pin is not connected internally.                                                                                                                                                                                                  |

| 17 to 19 | SW3 to<br>SW1     | <b>Switching Node Current Balance Inputs</b> . Sense the switching side of the inductor and used to measure the current level in each phase. The SW pins of unused phases should be left open.                                                        |

| 20 to 22 | PWM3 to<br>PWM1   | <b>PWM Outputs</b> . Each output is connected to the input of an external MOSFET driver, such as the FAN5109. Connecting the PWM3 output to VCC disables that phase, allowing the FAN5033 to operate as a two-phase controller.                       |

| 23       | VCC               | Supply Voltage for the Device.                                                                                                                                                                                                                        |

| 24 to 31 | VID7 to<br>VID0   | <b>Voltage Identification Code Inputs</b> . These digital inputs are connected to the internal DAC and used to program the output voltage. These pins have 1µA internal pull-down; so if they are left open, the input state is decoded as logic low. |

| 32       | VIDSEL            | <b>VID Table Select Input</b> . A logic low selects the extended VR10 DAC table and a logic high selects the VR11 DAC table. This pin has a $1\mu$ A internal pull-down; so if left open, the input state is decoded as logic low.                    |

| -        | Exposed<br>Paddle | Internally connected to die ground. May be connected to ground or left floating.<br>Connect to ground for lowest package thermal resistance.                                                                                                          |

## Absolute Maximum Rating

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

Unless otherwise specified, all other voltages are referenced to GND.

| Symbol           | Parameter                                             | Min. | Тур. | Max.                  | Unit |

|------------------|-------------------------------------------------------|------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply Voltage                                        | -0.3 |      | +15                   | V    |

|                  | FBRTN                                                 | -0.3 |      | +0.3                  | V    |

|                  | RAMPADJ, PWM3                                         | -0.3 |      | V <sub>CC</sub> + 0.3 | V    |

|                  | SW1 – SW3                                             | -10  |      | +25                   | V    |

|                  | All Other Inputs and Outputs                          | -0.3 |      | +5.5                  | V    |

| TJ               | Operating Junction Temperature                        | 0    |      | +125                  | °C   |

| T <sub>STG</sub> | Storage Temperature                                   | -65  |      | +150                  | °C   |

| TL               | Lead Soldering Temperature (10 seconds)               |      |      | 300                   | °C   |

| T <sub>LI</sub>  | Lead Infrared Temperature (15 seconds)                |      |      | 260                   | °C   |

| $\theta_{JA}$    | Thermal Resistance Junction-to-Ambient <sup>(1)</sup> |      |      | 45                    | °C/W |

Note:

Junction-to-ambient thermal resistance, θ<sub>JA</sub>, is a strong function of PCB material, board thickness, thickness and number of copper planes, number of via used, diameter of via used, available copper surface, and attached heat sink characteristics.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol          | Parameter                  | Min. | Тур. | Max. | Unit |

|-----------------|----------------------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage, VCC to GND | 9.6  | 12   | 14.4 | V    |

| T <sub>A</sub>  | Ambient Temperature        | 0    |      | +85  | °C   |

# **Electrical Characteristics**

$V_{CC}$  = 12V, FBRTN = GND, and  $T_A$  = +25°C. The • denotes specifications that apply over the full operating temperature range.

| Symbol                      | Parameter                                                                       | Conditions                                                                         |   | Min.  | Тур.  | Max.  | Unit |

|-----------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---|-------|-------|-------|------|

| Error Amp                   | lifier                                                                          |                                                                                    |   |       |       |       |      |

| VCOMP                       | Output Voltage Range                                                            |                                                                                    | • | 0.5   |       | 4.0   | V    |

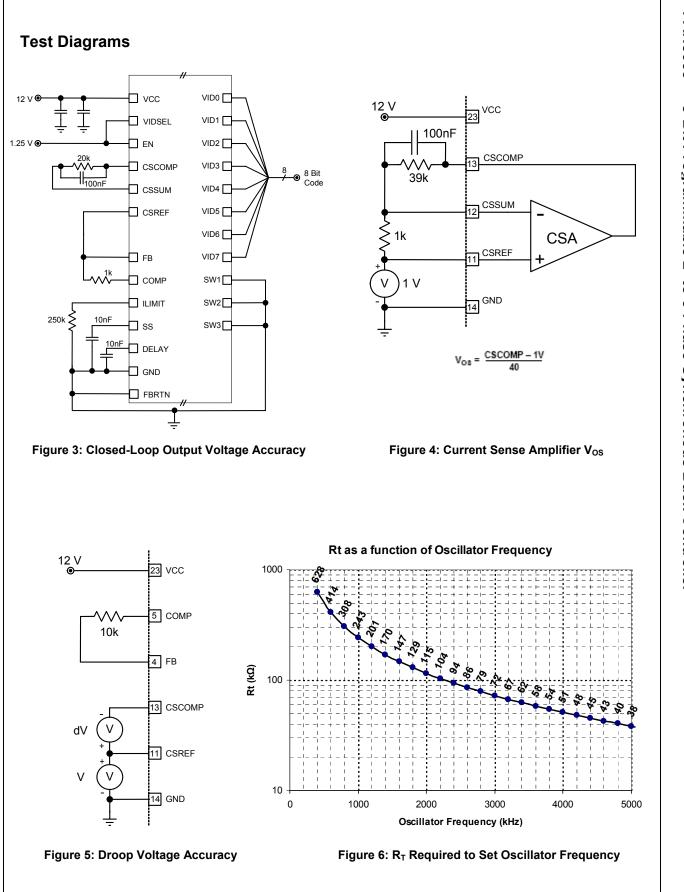

| $V_{\text{FB}}$             | Accuracy<br>Relative to nominal DAC output,<br>referenced to FBRTN.<br>Figure 3 | VRM11 VID Range:<br>1.00625V to 1.60000V                                           | • | -7.7  |       | +7.7  | mV   |

| V <sub>FB(BOOT)</sub>       | Accuracy<br>Relative to nominal DAC output,<br>referenced to FBRTN.<br>Figure 3 | During Start-up                                                                    | • | 1.092 | 1.100 | 1.108 | V    |

|                             | Load Line Droop Accuracy                                                        | CSREF-CSCOMP= 80mV<br>Figure 5                                                     | • | -78   | -80   | -82   | mV   |

|                             | Differential Non-linearity                                                      |                                                                                    | • | -1    |       | +1    | LSB  |

| $\Delta V_{\text{FB}}$      | Line Regulation                                                                 | V <sub>CC</sub> =10V to 14V                                                        |   |       | 0.05  |       | %    |

| I <sub>FB</sub>             | Input Bias Current                                                              |                                                                                    | • | 13.5  | 15.0  | 16.5  | μA   |

| I <sub>FBRTN</sub>          | FBRTN Current                                                                   |                                                                                    | • |       | 70    | 95    | μA   |

| I <sub>O(ERR)</sub>         | Output Current                                                                  | FB forced to V <sub>OUT</sub> -3%                                                  |   |       | 500   |       | μA   |

| GBW <sub>(ERR)</sub>        | Gain Bandwidth Product                                                          | COMP = FB <sup>(2)</sup>                                                           |   |       | 20    |       | MHz  |

|                             | Slew Rate                                                                       | COMP = FB <sup>(2)</sup>                                                           |   |       | 25    |       | V/µs |

| V <sub>CSCOMP</sub>         | CSCOMP Voltage Range                                                            | Relative to CSREF                                                                  | • | -250  |       | +250  | mV   |

| t <sub>BOOT</sub>           | BOOT Voltage Hold Time                                                          | C <sub>DELAY</sub> = 10nF                                                          |   |       | 2     |       | ms   |

| VID Inputs                  | and VIDSEL                                                                      | ·                                                                                  |   |       |       |       |      |

| $V_{\text{IH}(\text{VID})}$ | Input Low Voltage                                                               | VIDx, VIDSEL                                                                       | • |       |       | 0.4   | V    |

| V <sub>IL(VID)</sub>        | Input High Voltage                                                              | VIDx, VIDSEL                                                                       | • | 0.8   |       | 3.3   | V    |

| V <sub>IH(VID)</sub>        | Select VR10 Table                                                               | VIDSEL Logic Low                                                                   |   |       |       | 0.4   | V    |

| I <sub>IN(VID)</sub>        | Select VR11 Table                                                               | VIDSEL Logic High                                                                  |   | 0.8   |       | 3.3   | V    |

|                             | Input Current, VID Low                                                          |                                                                                    |   |       | -1    |       | μA   |

|                             | VID Transition Delay Time                                                       | VID code change to FB change <sup>(2)</sup>                                        | • | 200   |       |       | ns   |

|                             | No CPU Detection Turn-off Delay<br>Time                                         | VID code change to OFF state to PWM going low <sup>(2)</sup>                       | • | 200   |       |       | ns   |

| Oscillator                  |                                                                                 |                                                                                    |   |       |       |       |      |

| f <sub>OSC</sub>            | Frequency                                                                       |                                                                                    | • | 0.25  |       | 4.50  | MHz  |

| f <sub>PHASE</sub>          | Frequency Variation                                                             | $T_A = 25C, R_T = 200K, 3-$ phase                                                  |   | -20%  | 400   | 20%   | kHz  |

| V <sub>RT</sub>             | Output Voltage                                                                  | $R_T = 100 k\Omega$ to GND                                                         | • | 1.9   | 2.0   | 2.1   | V    |

| VRAMPADJ                    | RAMPADJ Output Voltage                                                          | $V_{RAMPADJ} = V_{DAC} + 2k\Omega * (V_{CC} - V_{DAC}) / (R_{RAMPADJ} + 2K\Omega)$ | • | -50   |       | +50   | mV   |

| IRAMPADJ                    | RAMPADJ Input Current Range                                                     |                                                                                    | 1 | 1     |       | 50    | μA   |

## Electrical Characteristics (Continued)

$V_{CC}$  = 12V, FBRTN = GND, and  $T_A$  = +25°C. The • denotes specifications that apply over the full operating temperature range.

| Symbol                     | Parameter                          | Conditions                                                   |   | Min. | Тур. | Max. | Unit  |

|----------------------------|------------------------------------|--------------------------------------------------------------|---|------|------|------|-------|

| Current Se                 | nse Amplifier                      |                                                              | I |      |      |      |       |

| V <sub>OS(CSA)</sub>       | Offset Voltage                     | CSSUM – CSREF<br>Figure 4                                    | • | -1.0 |      | +1.0 | mV    |

| IBIAS(CSSUM)               | Input Bias Current (for CSSUM)     |                                                              | • | -50  |      | +50  | nA    |

| I <sub>BIAS(CSREF)</sub>   | Input Current (for CSREF)          | Current drawn by<br>CSREF Pin                                | • | -3   |      | +3   | μA    |

| $GBW_{(CSA)}$              | Gain Bandwidth Product             | $CSSUM = C_{SCOMP}^{(2)}$                                    |   |      | 10   |      | MHz   |

|                            | Slew Rate                          | $C_{CSCOMP} = 10pF^{(2)}$                                    |   |      | 10   |      | V/µs  |

| V <sub>CSACM</sub>         | Input Common-Mode Range            | CSSUM and CSREF                                              | • | 0    |      | 3.2  | V     |

|                            | Output Voltage Range               |                                                              | • | 0.05 |      | 3.2  | V     |

| I <sub>CSCOMP</sub>        | Output Current                     |                                                              |   |      | 1    |      | mA    |

| $t_{OC(DELAY)}$            | Current Limit Latch-off Delay Time | C <sub>DELAY</sub> = 10nF                                    |   |      | 5    |      | ms    |

| Current Ba                 | lance Circuit                      |                                                              |   |      |      |      |       |

| V <sub>SW(x)CM</sub>       | Common Mode Range <sup>(2)</sup>   |                                                              | • | -600 |      | +200 | mV    |

| R <sub>SW(x)</sub>         | Input Resistance                   | SW(x) = 0V                                                   | • | 35   | 50   | 65   | kΩ    |

| I <sub>SW(x)</sub>         | Input Current                      | SW(x) = 0V                                                   | • | 1.6  | 3.3  | 5.0  | μA    |

| $\Delta I_{SW(x)}$         | Input Current Matching             | SW(x) = 0V                                                   | • | -5   |      | +5   | %     |

| Current Lin                | nit Comparator                     |                                                              |   |      |      |      |       |

| VILIMIT                    | Output Voltage                     | R <sub>ILIMT</sub> = 143kΩ                                   | ٠ | 1.6  | 1.7  | 1.8  | V     |

| I <sub>ILIMIT</sub>        | Output Current                     | R <sub>ILIMT</sub> = 143kΩ                                   |   |      | 12   |      | μA    |

|                            | Maximum Output Current             |                                                              | ٠ | 60   |      |      | μA    |

| V <sub>CL</sub>            | Current Limit Threshold Voltage    | $V_{CSREF} - V_{CSCOMP}, R_{ILIMT}$<br>= 143kΩ               | • | 100  | 120  | 140  | mV    |

|                            | Current Limit Setting Ratio        | V <sub>CL</sub> / I <sub>ILIMT</sub>                         |   |      | 10   |      | mV/μA |

| Delay Time                 | r                                  |                                                              |   |      |      |      |       |

| IDELAY                     | Normal Mode Output Current         |                                                              | • | 12   | 15   | 18   | μA    |

| I <sub>DELAY(CL)</sub>     | Output Current in Current Limit    |                                                              | • | 3.0  | 3.75 | 4.5  | μA    |

| V <sub>DELAY(TH)</sub>     | Threshold Voltage                  |                                                              | • | 1.6  | 1.7  | 1.8  | V     |

| Soft-Start                 | ·                                  | ·                                                            |   |      |      | •    | •     |

| I <sub>(SS)</sub>          | Output Current                     | During Start-up                                              | • | 12   | 15   | 18   | μA    |

| Enable Inp                 | ut                                 |                                                              |   |      |      |      |       |

| $V_{\text{TH}(\text{EN})}$ | Threshold Voltage                  |                                                              | • | 800  | 850  | 900  | mV    |

| V <sub>HYS(EN)</sub>       | Threshold Hysteresis               |                                                              | • | 80   | 100  | 120  | mV    |

| I <sub>IN(EN)</sub>        | Enable Input Current               |                                                              |   |      | 1    |      | μA    |

| t <sub>DELAY(EN)</sub>     | Turn-on Delay                      | Start-up sequence,<br>EN>950mV, C <sub>DELAY</sub> =<br>10nF |   |      | 2    |      | ms    |

## Electrical Characteristics (Continued)

$V_{CC}$  = 12V, FBRTN = GND, and  $T_A$  = +25°C. The • denotes specifications that apply over the full operating temperature range.

| Symbol                 | Parameter                  | Condi                                                                                      | tions                |   | Min.              | Тур. | Max. | Unit     |

|------------------------|----------------------------|--------------------------------------------------------------------------------------------|----------------------|---|-------------------|------|------|----------|

| OD Output              | •                          |                                                                                            |                      |   |                   |      |      | <u> </u> |

| V <sub>OL(ODB)</sub>   | Output Voltage Low         | $I_{PWM(SINK)} = 400 \mu A$                                                                |                      | • |                   | 160  | 400  | mV       |

| V <sub>OH(ODB)</sub>   | Output Voltage High        | I <sub>PWM(SOURCE)</sub> = 400μA                                                           |                      | • | 4                 | 5    |      | V        |

| Power Goo              | d Comparator               | I                                                                                          |                      | I |                   |      |      |          |

| V <sub>PWRGD(UV)</sub> | Under-Voltage<br>Threshold | Relative to Nominal D                                                                      | DAC Output           | • | -300              | -250 | -200 | mV       |

| V <sub>PWRGD(OV)</sub> | Over-Voltage<br>Threshold  | Relative to Nominal D                                                                      | DAC Output           | • | 100               | 150  | 200  | mV       |

| $V_{OL(PWRGD)}$        | Output Low Voltage         | I <sub>PWRGD(SINK)</sub> = -4mA                                                            |                      | • |                   | 200  | 300  | mV       |

|                        | Power Good Delay<br>Time   | C <sub>DELAY</sub> = 10nF<br>Power Good<br>Blanking Time                                   | Start-up<br>sequence | • |                   | 2    |      | ms       |

| t <sub>PWRGD</sub>     |                            |                                                                                            | VID code<br>Changing | • |                   | 250  |      | μs       |

|                        |                            |                                                                                            | VID Code Static      | • | 100               | 200  |      | ns       |

| VCROWBAR               | Crowbar Trip Point         | Relative to Nominal D                                                                      | DAC Output           | • | 100               | 150  | 200  | mV       |

|                        | Crowbar Reset Point        | Relative to FBRTN                                                                          |                      | • | 250               | 300  | 350  | mV       |

| t <sub>CROWBAR</sub>   | Crowbar Delay Time         | Over-voltage to<br>PWM going low                                                           | VID code Change      | • | 100               | 250  |      | μs       |

|                        |                            | Crowbar Blanking<br>Time                                                                   | VID Code Static      | • |                   | 400  |      | ns       |

| PWM Outp               | uts                        | I                                                                                          |                      |   | 1                 |      |      | <u></u>  |

| V <sub>OL(VRTM)</sub>  | Output Voltage Low         | $I_{PWM(SINK)} = 400 \mu A$                                                                |                      | • |                   | 160  | 400  | mV       |

| V <sub>OH(VRTM)</sub>  | Output Voltage High        | $I_{PWM(SOURCE)} = 400 \mu A$                                                              |                      | • | 4                 | 5    |      | V        |

|                        | Phase Disable Voltage      | Applicable to PWM3 pins only. Connect this pin to VCC to disable the phase. <sup>(3)</sup> |                      | • | V <sub>CC</sub> 1 |      |      | V        |

| Input Supp             | ly                         |                                                                                            |                      |   |                   |      |      | L        |

| V <sub>CC</sub>        | DC Supply Current          | EN = Logic HIGH                                                                            |                      | • |                   | 8    | 12   | mA       |

| V <sub>UVLO</sub>      | UVLO Threshold             | V <sub>CC</sub> rising                                                                     |                      | • | 6.5               | 6.9  | 7.3  | V        |

| VULVOLHYS              | UVLO Hysteresis            |                                                                                            |                      | • | 0.7               | 0.9  | 1.1  | V        |

1. All limits at operating temperature extremes are guaranteed by design, characterization, and statistical quality control.

2. AC specifications guaranteed by design and characterization; not production tested.

3. To operate FAN5033 with fewer than three phases, PWM3 should be connected to VCC to disable this phase. See the "Theory of Operation" section for details.

| /ID4 | VID3          | VID2 | VID1   | VID0 | VID5 | VID6   | V <sub>OUT</sub> (V) |

|------|---------------|------|--------|------|------|--------|----------------------|

| 1    | 1             | 1    | 1      | 1    | 1    | 0      | OFF                  |

| 1    | 1             | 1    | 1      | 1    | 1    | 1      | OFF                  |

| 1    | 1             | 1    | 1      | 1    | 0    | 0      | OFF                  |

| 1    | 1             | 1    | 1      | 1    | 0    | 1      | OFF                  |

| 1    | 1             | 1    | 1      | 0    | 1    | 0      | 1.09375              |

| 1    | 1             | 1    | 1      | 0    | 1    | 1      | 1.10000              |

| 1    | 1             | 1    | 1      | 0    | 0    | 0      | 1.10625              |

| 1    | 1             | 1    | 1      | 0    | 0    | 1      | 1.11250              |

| 1    | 1             | 1    | 0      | 1    | 1    | 0      | 1.11875              |

| 1    | 1             | 1    | 0      | 1    | 1    | 1      | 1.12500              |

| 1    | <u>1</u><br>1 | 1    | 0      | 1    | 0    | 0      | 1.13125<br>1.13750   |

| 1    | 1             | 1    | 0      | 0    | 1    | 0      | 1.13750              |

| 1    | 1             | 1    | 0      | 0    | 1    | 1      | 1.14575              |

| 1    | 1             | 1    | 0      | 0    | 0    | 0      | 1.15625              |

| 1    | 1             | 1    | 0      | 0    | 0    | 1      | 1.16250              |

| 1    | 1             | 0    | 1      | 1    | 1    | 0      | 1.16875              |

| 1    | 1             | 0    | 1      | 1    | 1    | 1      | 1.17500              |

| 1    | 1             | 0    | 1      | 1    | 0    | 0      | 1.18125              |

| 1    | 1             | 0    | 1      | 1    | 0    | 1      | 1.18750              |

| 1    | 1             | 0    | 1      | 0    | 1    | 0      | 1.19375              |

| 1    | 1             | 0    | 1      | 0    | 1    | 1      | 1.20000              |

| 1    | 1             | 0    | 1      | 0    | 0    | 0      | 1.20625              |

| 1    | <u>1</u><br>1 | 0    | 1<br>0 | 0    | 0    | 1<br>0 | 1.21250              |

| 1    | 1             | 0    | 0      | 1    | 1    | 1      | 1.21875<br>1.22500   |

| 1    | 1             | 0    | 0      | 1    | 0    | 0      | 1.22300              |

| 1    | 1             | 0    | 0      | 1    | 0    | 1      | 1.23750              |

| 1    | 1             | 0    | 0      | 0    | 1    | 0      | 1.24375              |

| 1    | 1             | 0    | 0      | 0    | 1    | 1      | 1.25000              |

| 1    | 1             | 0    | 0      | 0    | 0    | 0      | 1.25625              |

| 1    | 1             | 0    | 0      | 0    | 0    | 1      | 1.26250              |

| 1    | 0             | 1    | 1      | 1    | 1    | 0      | 1.26875              |

| 1    | 0             | 1    | 1      | 1    | 1    | 1      | 1.27500              |

| 1    | 0             | 1    | 1      | 1    | 0    | 0      | 1.28125              |

| 1    | 0             | 1    | 1      | 1    | 0    | 1      | 1.28750              |

| 1    | 0             | 1    | 1      | 0    | 1    | 0      | 1.29375<br>1.30000   |

| 1    | 0             | 1    | 1      | 0    | 0    | 0      | 1.30625              |

| 1    | 0             | 1    | 1      | 0    | 0    | 1      | 1.31250              |

| 1    | 0             | 1    | 0      | 1    | 1    | 0      | 1.31875              |

| 1    | 0             | 1    | 0      | 1    | 1    | 1      | 1.32500              |

| 1    | 0             | 1    | 0      | 1    | 0    | 0      | 1.33125              |

| 1    | 0             | 1    | 0      | 1    | 0    | 1      | 1.33750              |

| 1    | 0             | 1    | 0      | 0    | 1    | 0      | 1.34375              |

| 1    | 0             | 1    | 0      | 0    | 1    | 1      | 1.35000              |

| 1    | 0             | 1    | 0      | 0    | 0    | 0      | 1.35625              |

| 1    | 0             | 1    | 0      | 0    | 0    | 1      | 1.36250              |

| 1    | 0             | 0    | 1      | 1    | 1    | 0      | 1.36875              |

| 1    | 0             | 0    | 1      | 1    | 1    | 1      | 1.37500              |

| 1    | 0             | 0    | 1      | 1    | 0    | 0      | 1.38125<br>1.38750   |

| 1    | 0             | 0    | 1      | 0    | 1    | 0      | 1.39375              |

| 1    | 0             | 0    | 1      | 0    | 1    | 1      | 1.40000              |

| 1    | 0             | 0    | 1      | 0    | 0    | 0      | 1.40625              |

| 1    | 0             | 0    | 1      | 0    | 0    | 1      | 1.41250              |

| 1    | 0             | 0    | 0      | 1    | 1    | 0      | 1.41875              |

| 1    | 0             | 0    | 0      | 1    | 1    | 1      | 1.42500              |

| 1    | 0             | 0    | 0      | 1    | 0    | 0      | 1.43125              |

| 1    | 0             | 0    | 0      | 1    | 0    | 1      | 1.43750              |

| 1    | 0             | 0    | 0      | 0    | 1    | 0      | 1.44375              |

| 1    | 0             | 0    | 0      | 0    | 1    | 1      | 1.45000              |

| 1    | 0             | 0    | 0      | 0    | 0    | 0      | 1.45625              |

| able 1: Co | ontinued |      |      |      |      |      |                      |

|------------|----------|------|------|------|------|------|----------------------|

| VID4       | VID3     | VID2 | VID1 | VID0 | VID5 | VID6 | V <sub>OUT (V)</sub> |

| 0          | 1        | 1    | 1    | 1    | 1    | 0    | 1.46875              |

| 0          | 1        | 1    | 1    | 1    | 1    | 1    | 1.47500              |

| 0          | 1        | 1    | 1    | 1    | 0    | 0    | 1.48125              |

| 0          | 1        | 1    | 1    | 1    | 0    | 1    | 1.48750              |

| 0          | 1        | 1    | 1    | 0    | 1    | 0    | 1.49375              |

| 0          | 1        | 1    | 1    | 0    | 1    | 1    | 1.50000              |

| 0          | 1        | 1    | 1    | 0    | 0    | 0    | 1.50625              |

| 0          | 1        | 1    | 1    | 0    | 0    | 1    | 1.51250              |

| 0          | 1        | 1    | 0    | 1    | 1    | 0    | 1.51875              |

| 0          | 1        | 1    | 0    | 1    | 1    | 1    | 1.52500              |

| 0          | 1        | 1    | 0    | 1    | 0    | 0    | 1.53125              |

| 0          | 1        | 1    | 0    | 1    | 0    | 1    | 1.53750              |

| 0          | 1        | 1    | 0    | 0    | 1    | 0    | 1.54375              |

| 0          | 1        | 1    | 0    | 0    | 1    | 1    | 1.55000              |

| 0          | 1        | 1    | 0    | 0    | 0    | 0    | 1.55625              |

| 0          | 1        | 1    | 0    | 0    | 0    | 1    | 1.56250              |

| 0          | 1        | 0    | 1    | 1    | 1    | 0    | 1.56875              |

| 0          | 1        | 0    | 1    | 1    | 1    | 1    | 1.57500              |

| 0          | 1        | 0    | 1    | 1    | 0    | 0    | 1.58125              |

| 0          | 1        | 0    | 1    | 1    | 0    | 1    | 1.58750              |

| 0          | 1        | 0    | 1    | 0    | 1    | 0    | 1.59375              |

| 0          | 1        | 0    | 1    | 0    | 1    | 1    | 1.60000              |

| 0          | 1        | 0    | 1    | 0    | 0    | 0    | 0.83125              |

| 0          | 1        | 0    | 1    | 0    | 0    | 1    | 0.83750              |

| 0          | 1        | 0    | 0    | 1    | 1    | 0    | 0.84375              |

| 0          | 1        | 0    | 0    | 1    | 1    | 1    | 0.85000              |

| 0          | 1        | 0    | 0    | 1    | 0    | 0    | 0.85625              |

| 0          | 1        | 0    | 0    | 1    | 0    | 1    | 0.86250              |

| 0          | 1        | 0    | 0    | 0    | 1    | 0    | 0.86875              |

| 0          | 1        | 0    | 0    | 0    | 1    | 1    | 0.87500              |

| 0          | 1        | 0    | 0    | 0    | 0    | 0    | 0.88125              |

| 0          | 1        | 0    | 0    | 0    | 0    | 1    | 0.88750              |

| 0          | 0        | 1    | 1    | 1    | 1    | 0    | 0.89375              |

| 0          | 0        | 1    | 1    | 1    | 1    | 1    | 0.90000              |

| 0          | 0        | 1    | 1    | 1    | 0    | 0    | 0.90625              |

| 0          | 0        | 1    | 1    | 1    | 0    | 1    | 0.91250              |

| 0          | 0        | 1    | 1    | 0    | 1    | 0    | 0.91875              |

| 0          | 0        | 1    | 1    | 0    | 1    | 1    | 0.92500              |

| 0          | 0        | 1    | 1    | 0    | 0    | 0    | 0.93125              |

| 0          | 0        | 1    | 1    | 0    | 0    | 1    | 0.93750              |

| 0          | 0        | 1    | 0    | 1    | 1    | 0    | 0.94375              |

| 0          | 0        | 1    | 0    | 1    | 1    | 1    | 0.95000              |

| 0          | 0        | 1    | 0    | 1    | 0    | 0    | 0.95625              |

| 0          | 0        | 1    | 0    | 1    | 0    | 1    | 0.96250              |

| 0          | 0        | 1    | 0    | 0    | 1    | 0    | 0.96875              |

| 0          | 0        | 1    | 0    | 0    | 1    | 1    | 0.97500              |

| 0          | 0        | 1    | 0    | 0    | 0    | 0    | 0.98125              |

| 0          | 0        | 1    | 0    | 0    | 0    | 1    | 0.98750              |

| 0          | 0        | 0    | 1    | 1    | 1    | 0    | 0.99375              |

| 0          | 0        | 0    | 1    | 1    | 1    | 1    | 1.00000              |

| 0          | 0        | 0    | 1    | 1    | 0    | 0    | 1.00625              |

| 0          | 0        | 0    | 1    | 1    | 0    | 1    | 1.01250              |

| 0          | 0        | 0    | 1    | 0    | 1    | 0    | 1.01875              |

| 0          | 0        | 0    | 1    | 0    | 1    | 1    | 1.02500              |

| 0          | 0        | 0    | 1    | 0    | 0    | 0    | 1.03125              |

| 0          | 0        | 0    | 1    | 0    | 0    | 1    | 1.03750              |

| 0          | 0        | 0    | 0    | 1    | 1    | 0    | 1.04375              |

| 0          | 0        | 0    | 0    | 1    | 1    | 1    | 1.05000              |

| 0          | 0        | 0    | 0    | 1    | 0    | 0    | 1.05625              |

| 0          | 0        | 0    | 0    | 1    | 0    | 1    | 1.06250              |

| 0          | 0        | 0    | 0    | 0    | 1    | 0    | 1.06875              |

| 0          | 0        | 0    | 0    | 0    | 1    | 1    | 1.07500              |

| 0          | 0        | 0    | 0    | 0    | 0    | 0    | 1.08125              |

| 0          | 0        | 0    | 0    | 0    | 0    | 1    | 1.08750              |

| HEX        | Voltage | 1 <sub>h</sub> )<br>Tolerance    | HEX | Voltage | Tolerance                                          | HEX        | Voltage | Tolerance               | HEX | Voltage | Tolerand  |

|------------|---------|----------------------------------|-----|---------|----------------------------------------------------|------------|---------|-------------------------|-----|---------|-----------|

| 0.0        | OFF     | Toloranoo                        | 4 0 | 1.21250 | +-15mV LL (0 - 110A)                               | 80         | 0.81250 | Monotonic               | C 0 | 0.4125  | Don't Car |

| 01         | OFF     |                                  | 4 1 | 1.20625 | +-15mV LL (0 - 110A)                               | 81         | 0.80625 | Monotonic               | C 1 | 0.40625 | Don't Car |

|            | -       | 1 45 m)/11 (0                    |     |         |                                                    |            |         |                         |     |         |           |

| 02         | 1.60000 | +-15mV LL (0 -                   | 42  | 1.20000 | +-15mV LL (0 - 110A)                               | 82         | 0.8     | Monotonic               | C 2 | 0.40000 | Don't Car |

| 03         | 1.59375 | +-15mV LL (0 -                   | 43  | 1.19375 | +-15mV LL (0 - 110A)                               | 83         | 0.79375 | Monotonic               | C 3 | 0.39375 | Don't Car |

| 04         | 1.58750 | +-15mV LL (0 -                   | 44  | 1.18750 | +-15mV LL (0 - 110A)                               | 84         | 0.7875  | Monotonic               | C 4 | 0.38750 | Don't Car |

| 05         | 1.58125 | +-15mV LL (0 -                   | 4 5 | 1.18125 | +-15mV LL (0 - 110A)                               | 85         | 0.78125 | Monotonic               | C 5 | 0.38125 | Don't Car |

| 06         | 1.57500 | +-15mV LL (0 -                   | 46  | 1.17500 | +-15mV LL (0 - 110A)                               | 86         | 0.775   | Monotonic               | C 6 | 0.37500 | Don't Car |

| 07         | 1.56875 | +-15mV LL (0 -                   | 47  | 1.16875 | +-15mV LL (0 - 110A)                               | 87         | 0.76875 | Monotonic               | C 7 | 0.36875 | Don't Car |

| 8 0        | 1.56250 | +-15mV LL (0 -                   | 48  | 1.16250 | +-15mV LL (0 - 110A)                               | 88         | 0.7625  | Monotonic               | C 8 | 0.36250 | Don't Car |

| 09         | 1.55625 | +-15mV LL (0 -                   | 49  | 1.15625 | +-15mV LL (0 - 110A)                               | 89         | 0.75625 | Monotonic               | C 9 | 0.35625 | Don't Car |

| 0 A 0      | 1.55000 | +-15mV LL (0 -                   | 4 A | 1.15000 | +-15mV LL (0 - 110A)                               | 8 A        | 0.75    | Monotonic               | CA  | 0.35000 | Don't Ca  |

| 0 B        | 1.54375 | +-15mV LL (0 -                   | 4 B | 1.14375 | +-15mV LL (0 - 110A)                               | 8 B        | 0.74375 | Monotonic               | СВ  | 0.34375 | Don't Ca  |

| 0 C        | 1.53750 | +-15mV LL (0 -                   | 4 C | 1.13750 | +-15mV LL (0 - 110A)                               | 8 C        | 0.7375  | Monotonic               | CC  | 0.33750 | Don't Ca  |

| 0 D        | 1.53125 | +-15mV LL (0 -                   | 4 D | 1.13125 | +-15mV LL (0 - 110A)                               | 8 D        | 0.73125 | Monotonic               | CD  | 0.33125 | Don't Ca  |

| 0 E        | 1.52500 | +-15mV LL (0 -                   | 4 E | 1.12500 | +-15mV LL (0 - 110A)                               | 8 E        | 0.725   | Monotonic               | CE  | 0.32500 | Don't Ca  |

| 0 F        | 1.51875 | +-15mV LL (0 -                   | 4 F | 1.11875 | +-15mV LL (0 - 110A)                               | 8 F        | 0.71875 | Monotonic               | CF  | 0.31875 | Don't Ca  |

| 10         | 1.51250 | +-15mV LL (0 -                   | 50  | 1.11250 | +-15mV LL (0 - 110A)                               | 90         | 0.7125  | Monotonic               | D 0 | 0.31250 | Don't Ca  |

| 11         | 1.50625 | +-15mV LL (0 -                   | 51  | 1.10625 | +-15mV LL (0 - 110A)                               | 91         | 0.70625 | Monotonic               | D 1 | 0.30625 | Don't Ca  |

| 12         | 1.50000 | +-15mV LL (0 -                   | 52  | 1.10000 | +-15mV LL (0 - 110A)                               | 92         | 0.7     | Monotonic               | D 2 | 0.30000 | Don't Ca  |

| 13         | 1.49375 | +-15mV LL (0 -                   | 53  | 1.09375 | +-15mV LL (0 - 110A)                               | 93         | 0.69375 | Monotonic               | D 3 | 0.29375 | Don't Ca  |

| 14         | 1.48750 | +-15mV LL (0 -                   | 54  | 1.08750 | +-15mV LL (0 - 110A)                               | 94         | 0.6875  | Monotonic               | D 4 | 0.28750 | Don't Ca  |

| 15         | 1.48125 | +-15mV LL (0 -                   | 55  | 1.08125 | +-15mV LL (0 - 110A)                               | 95         | 0.68125 | Monotonic               | D 5 | 0.28125 | Don't Ca  |

| 16         | 1.47500 | +-15mV LL (0 -                   | 56  | 1.07500 | +-15mV LL (0 - 110A)                               | 96         | 0.675   | Monotonic               | D 6 | 0.27500 | Don't Ca  |

| 17         | 1.46875 | +-15mV LL (0 -                   | 57  | 1.06875 | · · · · · · · · · · · · · · · · · · ·              | 97         | 0.66875 |                         | D 7 | 0.27300 |           |

|            |         |                                  |     | 1.06250 | +-15mV LL (0 - 110A)                               | 97         | 0.6625  | Monotonic               |     |         | Don't Ca  |

| 18         | 1.46250 | +-15mV LL (0 -                   | 58  |         | +-15mV LL (0 - 110A)                               |            |         | Monotonic               | D 8 | 0.26250 | Don't Ca  |

| 19         | 1.45625 | +-15mV LL (0 -                   | 59  | 1.05625 | +-15mV LL (0 - 110A)                               | 99         | 0.65625 | Monotonic               | D 9 | 0.25625 | Don't Ca  |

| 1 A        | 1.45000 | +-15mV LL (0 -                   | 5 A | 1.05000 | +-15mV LL (0 - 110A)                               | 9 A        | 0.65    | Monotonic               | DA  | 0.25000 | Don't Ca  |

| 1 B        | 1.44375 | +-15mV LL (0 -                   | 5 B | 1.04375 | +-15mV LL (0 - 110A)                               | 9 B        | 0.64375 | Monotonic               | DB  | 0.24375 | Don't Ca  |

| 1 C        | 1.43750 | +-15mV LL (0 -                   | 5 C | 1.03750 | +-15mV LL (0 - 110A)                               | 9 C        | 0.6375  | Monotonic               | DC  | 0.23750 | Don't Ca  |

| 1 D        | 1.43125 | +-15mV LL (0 -                   | 5 D | 1.03125 | +-15mV LL (0 - 110A)                               | 9 D        | 0.63125 | Monotonic               | DD  | 0.23125 | Don't Ca  |

| 1 E        | 1.42500 | +-15mV LL (0 -                   | 5 E | 1.02500 | +-15mV LL (0 - 110A)                               | 9 E        | 0.625   | Monotonic               | DE  | 0.22500 | Don't Ca  |

| 1 F        | 1.41875 | +-15mV LL (0 -                   | 5 F | 1.01875 | +-15mV LL (0 - 110A)                               | 9 F        | 0.61875 | Monotonic               | DF  | 0.21875 | Don't Ca  |

| 20         | 1.41250 | +-15mV LL (0 -                   | 60  | 1.01250 | +-15mV LL (0 - 110A)                               | A 0        | 0.6125  | Monotonic               | E 0 | 0.21250 | Don't Ca  |

| 21         | 1.40625 | +-15mV LL (0 -                   | 61  | 1.00625 | +-15mV LL (0 - 110A)                               | A 1        | 0.60625 | Monotonic               | E 1 | 0.20625 | Don't Ca  |

| 22         | 1.40000 | +-15mV LL (0 -                   | 62  | 1.00000 | Monotonic DAC (6.25 mV)                            | A 2        | 0.6     | Monotonic               | E 2 | 0.20000 | Don't Ca  |

| 23         | 1.39375 | +-15mV LL (0 -                   | 63  | 0.99375 | Monotonic DAC (6.25 mV)                            | A 3        | 0.59375 | Monotonic               | E 3 | 0.19375 | Don't Ca  |

| 24         | 1.38750 | +-15mV LL (0 -                   | 64  | 0.98750 | Monotonic DAC (6.25 mV)                            | A 4        | 0.5875  | Monotonic               | E 4 | 0.18750 | Don't Ca  |

| 25         | 1.38125 | +-15mV LL (0 -                   | 65  | 0.98125 | Monotonic DAC (6.25 mV)                            | A 5        | 0.58125 | Monotonic               | E 5 | 0.18125 | Don't Ca  |

| 26         | 1.37500 | +-15mV LL (0 -                   | 66  | 0.97500 | Monotonic DAC (6.25 mV)                            | A 6        | 0.575   | Monotonic               | E 6 | 0.17500 | Don't Ca  |

| 27         | 1.36875 | +-15mV LL (0 -                   | 67  | 0.96875 | Monotonic DAC (6.25 mV)                            | Α7         | 0.56875 | Monotonic               | E 7 | 0.16875 | Don't Ca  |

| 28         | 1.36250 | +-15mV LL (0 -                   | 68  | 0.96250 | Monotonic DAC (6.25 mV)                            | A 8        | 0.5625  | Monotonic               | E 8 | 0.16250 | Don't Ca  |

| 29         | 1.35625 | +-15mV LL (0 -                   | 69  | 0.95625 | Monotonic DAC (6.25 mV)                            | A 9        | 0.55625 | Monotonic               | E 9 | 0.15625 | Don't Ca  |

| 2 A        | 1.35000 | +-15mV LL (0 -                   | 6 A | 0.95000 | Monotonic DAC (6.25 mV)                            | AA         | 0.55    | Monotonic               | ΕA  | 0.15000 | Don't Ca  |

| 2 B        | 1.34375 | +-15mV LL (0 -                   | 6 B | 0.94375 | Monotonic DAC (6.25 mV)                            | AB         | 0.54375 | Monotonic               | EB  | 0.14375 | Don't Ca  |

| 2 C        | 1.33750 | +-15mV LL (0 -                   | 6 C | 0.93750 | Monotonic DAC (6.25 mV)                            | AC         | 0.5375  | Monotonic               | EC  | 0.13750 | Don't Ca  |

| 2 D        | 1.33125 | +-15mV LL (0 -                   | 6 D | 0.93125 | Monotonic DAC (6.25 mV)                            | A D        | 0.53125 | Monotonic               | ED  | 0.13125 | Don't Ca  |

| 2 E        | 1.32500 | +-15mV LL (0 -                   | 6 E | 0.92500 | Monotonic DAC (6.25 mV)                            | AE         | 0.525   | Monotonic               | EE  |         | Don't Ca  |

| 2 E<br>2 F | 1.31875 | +-15mV LL (0 -                   | 6 F | 0.92500 | Monotonic DAC (6.25 mV)                            | AF         | 0.51875 | Monotonic               | EF  | 0.12300 | Don't Ca  |

| 30         | 1.31250 | +-15mV LL (0 -                   | 70  | 0.91375 | Monotonic DAC (6.25 mV)                            | BO         | 0.5125  | Monotonic               | FO  | 0.11250 | Don't Ca  |

| 31         | 1.30625 | +-15mV LL (0 -                   | 7 0 | 0.90625 | Monotonic DAC (6.25 mV)                            | B 1        | 0.50625 | Monotonic               | F 1 | 0.11230 | Don't Ca  |

| 32         | 1.30025 | +-15mV LL (0 -                   | 72  | 0.90823 | Monotonic DAC (6.25 mV)                            | B 2        | 0.50625 |                         | F 1 | 0.10025 | Don't Ca  |

| _          | 1.29375 |                                  |     | 0.90000 |                                                    |            |         | Monotonic<br>Don't Care | F 2 |         | Don't Ca  |

| 33         | 1.29375 | +-15mV LL (0 -                   | 73  | 0.89373 | Monotonic DAC (6.25 mV)<br>Monotonic DAC (6.25 mV) | B 3<br>B 4 | 0.49375 |                         |     | 0.09375 |           |

| 34         |         | +-15mV LL (0 -<br>+-15mV LL (0 - |     |         | · · · · · · · · · · · · · · · · · · ·              |            | 0.4875  | Don't Care              | F 4 | 0.08750 | Don't Ca  |

| 35         | 1.28125 |                                  | 75  | 0.88125 | Monotonic DAC (6.25 mV)                            | B 5        | 0.48125 | Don't Care              | F 5 | 0.08125 | Don't Ca  |

| 36         | 1.27500 | +-15mV LL (0 -                   | 76  | 0.87500 | Monotonic DAC (6.25 mV)                            | B 6        | 0.475   | Don't Care              | F 6 | 0.07500 | Don't Ca  |

| 37         | 1.26875 | +-15mV LL (0 -                   | 77  | 0.86875 | Monotonic DAC (6.25 mV)                            | B 7        | 0.46875 | Don't Care              | F 7 | 0.06875 | Don't Ca  |

| 38         | 1.26250 | +-15mV LL (0 -                   | 78  | 0.86250 | Monotonic DAC (6.25 mV)                            | B 8        | 0.4625  | Don't Care              | F 8 | 0.06250 | Don't Ca  |

| 39         | 1.25625 | +-15mV LL (0 -                   | 79  | 0.85625 | Monotonic DAC (6.25 mV)                            | B 9        | 0.45625 | Don't Care              | F 9 | 0.05625 | Don't Ca  |

| 3 A        | 1.25000 | +-15mV LL (0 -                   | 7 A | 0.85000 | Monotonic DAC (6.25 mV)                            | ΒA         | 0.45    | Don't Care              | FA  | 0.05000 | Don't Ca  |

| 3 B        | 1.24375 | +-15mV LL (0 -                   | 7 B | 0.84375 | Monotonic DAC (6.25 mV)                            | BB         | 0.44375 | Don't Care              | FB  | 0.04375 | Don't Ca  |

| 3 C        | 1.23750 | +-15mV LL (0 -                   | 7 C | 0.83750 | Monotonic DAC (6.25 mV)                            | BC         | 0.4375  | Don't Care              | FC  | 0.03750 | Don't Ca  |

| 3 D        | 1.23125 | +-15mV LL (0 -                   | 7 D | 0.83125 | Monotonic DAC (6.25 mV)                            | ΒD         | 0.43125 | Don't Care              | FD  | 0.03125 | Don't Ca  |

| 3 E        | 1.22500 | +-15mV LL (0 -                   | 7 E | 0.82500 | Monotonic DAC (6.25 mV)                            | ΒE         | 0.425   | Don't Care              | FE  | OFF     |           |

|            |         |                                  |     |         |                                                    |            |         |                         |     |         |           |

# Table 2: Output Voltage Programming Codes (8-bit) 0 = logic LOW; 1 = logic HIGH. (MSB: VID7, LSB: VID0; $11110001_{b} = F1_{h}$ )

FAN5033 — 8-Bit Programmable 2- to 3-Phase Synchronous Buck Controller

## Theory of Operation

#### Note: The values shown in this section are for reference only. See the parametric tables for actual values.

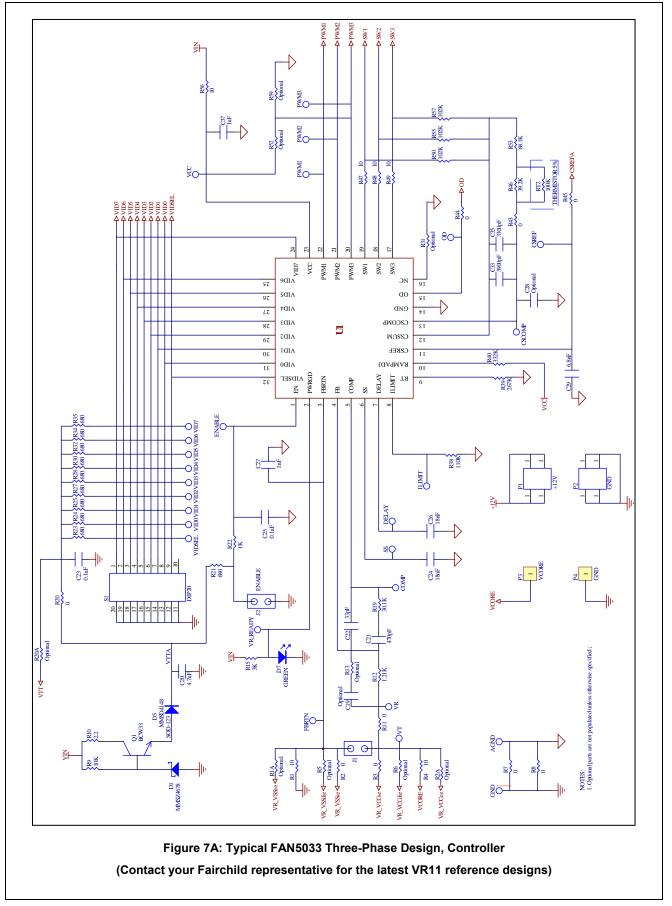

The FAN5033 is a fixed-frequency PWM controller with multi-phase logic outputs for use in two- and three-phase synchronous buck CPU power supplies. It has an internal VID DAC designed to interface directly with Intel's 8-bit VRD/VRM 11 and 7-bit VRD/VRM 10.x-compatible CPUs. Multi-phase operation is required for the high currents and low voltages of today's Intel's microprocessors that can require up to 150A of current.

The integrated features of the FAN5033 ensure a stable, high-performance topology for:

- Balanced currents and thermals between phases

- High-speed response at the lowest possible switching frequency and output decoupling capacitors

- Tight load line regulation and accuracy

- High-current output by allowing up to three-phase designs

- Reduced output ripple due to multi-phase operation

- Good PC board layout noise immunity

- Easily settable and adjustable design parameters with simple component selection

- Two- to three-phase operation allows optimizing designs for cost/performance and support a wide range of applications

#### START-UP SEQUENCE

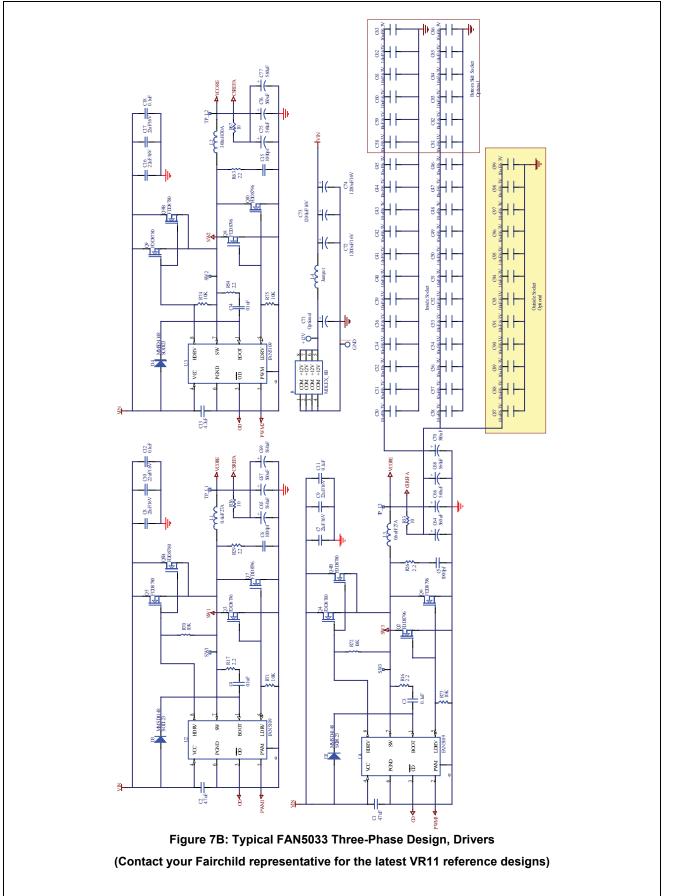

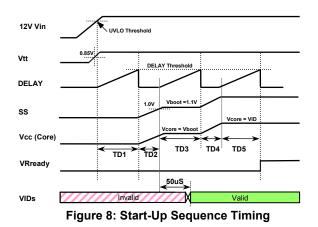

The FAN5033 start-up sequence is shown in Figure 8. Once the EN and UVLO conditions are met, the DELAY pin goes through one cycle (TD1); after which, the internal oscillator starts. The first two clock cycles are used for phase detection. The soft-start ramp is enabled (TD2), raising the output voltage up to the boot voltage of 1.1V. The boot hold time (TD3) allows the processor VID pins settle to the programmed VID code. After TD3 timing is finished, the output soft-starts, either up or down, to the final VID voltage during TD4. TD5 is the time between the output reaching the VID voltage and the PWRGD being presented to the system.

#### PHASE-DETECTION SEQUENCE

During start-up, the number of operational phases and their phase relationship is determined by the internal circuitry that monitors the PWM outputs. Normally, the FAN5033 operates as a three-phase PWM controller. For two-phase operation, connect the PWM3 pin to VCC.

The PWM logic, which is driven by the master oscillator, directs the phase sequencer and channel detectors. Channel detection occurs during the first two clock cycles after the chip is enabled. During the detection period, PWM3 is connected to a 100 $\mu$ A sinking current source and two internal voltage comparators check the pin voltage of PWM3 versus a threshold of 3V typical. If the pin is tied to VIN, the pin voltage is above 3V and that phase is disabled and put in a tri-state mode. Otherwise, the internal 100 $\mu$ A current source pulls PWM pin below the 3V threshold. After channel detection, the 100 $\mu$ A current source is removed.

Shorting PWM3 to VCC configures the system for twophase operation.

After detection time is complete, the PWM outputs that were not sensed as "pulled high" function as normal PWM outputs. PWM outputs that were sensed as "pulled high" are put into a high-impedance state.

The PWM signals are logic-level outputs intended for driving external gate drivers, such as the FAN5109. Since each phase is monitored independently, operation approaching 100% duty cycle is possible. Also, more than one output can be on at the same time to allow overlapping phases.

#### MASTER CLOCK FREQUENCY

The clock frequency of the FAN5033 is set with an external resistor connected from the RT pin to ground. The frequency to resistor relationship is shown in Figure 6. To determine the frequency per phase, divide the clock by the number of enabled phases.

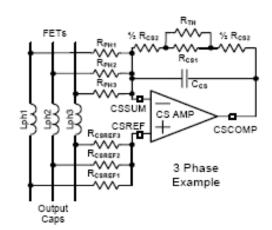

#### **OUTPUT CURRENT SENSING** (See Figure 2)

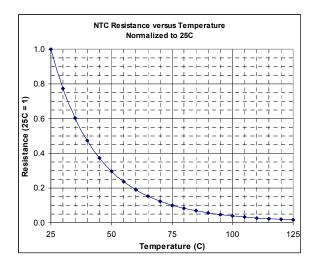

The FAN5033 provides a dedicated current sense amplifier (CSA) to monitor the output current for proper voltage positioning and for current limit detection. It differentially senses the voltage drop across the DCR of the inductors to give the total average current being delivered to the load. This method is inherently more accurate than peak current detection or sampling the voltage across the low-side MOSFETs. The CSA implementation can be configured several ways, depending on the objectives of the system. It can use output inductor DCR sensing without a thermistor, for lowest cost, or output inductor DCR sensing with a thermistor, for improved accuracy with tracking of inductor temperature.

To measure the differential voltage across the output inductors, the positive input of the CSA (CSREF pin) is connected, using equal value resistors, to the output capacitor side of the inductors. The negative input of the CSA (CSSUM pin) is connected, again using equal value resistors, to the MOSFET side of the inductors. The CSA's output (CSCOMP) is a voltage equal to the voltage dropped across the inductors, times the gain of the CSA, and is inversely proportional to the output current.

The gain of the CSA is set by connecting an external feedback resistor between the CSA's CSCOMP and CSSUM pins. A capacitor, connected across the resistor, is used to create a low pass filter to remove high-frequency switching effects and to create a RC pole to cancel the zero created by the L/DCR of the inductor. The end result is that the voltage between the CSCOMP and CSREF pins is inversely proportional to the output current (CSCOMP goes negative relative to CSREF as current increases) and the CSA gain sets the ratio of the CSA output voltage change as a function of output current limit comparator and is also used by the droop amplifier to create the output load line.

The CSA is designed to have a low offset input voltage. The sensing gain is determined by external resistors so that it can be extremely accurate.

#### LOAD LINE IMPEDANCE CONTROL

The FAN5033 has an internal "Droop Amp" that effectively subtracts the voltage applied between the CSCOMP and CSREF pins from the FB pin voltage of the error amplifier, allowing the output voltage to be varied independent of the DAC setting. A positive voltage on CSCOMP (relative to CSREF) increases the output voltage and a negative voltage decreases it. Since the voltage between the CSA's CSCOMP and CSREF pins is inversely proportional to the output, current causes the output voltage to decrease an amount directly proportional to the increase in output, current, creating a droop or "Load Line." The ratio of output voltage decrease to output voltage decrease is the effective  $R_o$  of the power supply and is set by the DC gain of the CSA.

# CURRENT CONTROL MODE AND THERMAL BALANCE

The FAN5033 has individual SW inputs for each phase. They are used to measure the voltage drop across the bottom FETs to determine the current in each phase. This information is combined with an internal ramp to create a current balancing feedback system. This gives good current balance accuracy that takes into account, not only the current, but also the thermal balance between the bottom FETs in each phase.

External resistors  $R_{SW1}$  through  $R_{SW3}$  can be placed in series with individual SW inputs to create an intentional current imbalance if desired, such as in cases where one phase has better cooling and can support higher

currents. It is best to have the ability to add these resistors in the initial design to ensure that placeholders are provided in the layout. To increase the current in a phase, increase  $R_{SW}$  for that phase. Even adding a resistor of a few hundred ohms can make a noticeable increase in current, so use small steps.

The amplitude of the internal ramp is set by a resistor connected between the input voltage and the RAMPADJ pin. This method also implements the Voltage Feed Forward function.

#### OUTPUT VOLTAGE DIFFERENTIAL SENSING

The FAN5033 uses differential sensing in conjunction with a high accuracy DAC and a low offset error amplifier to maintain a worst-case specification of  $\pm$ 7.7mV differential sensing accuracy over its specified operating range.

A high gain-bandwidth error amplifier is used for the voltage control loop. The voltage on the FB pin is compared to the DAC voltage to control the output voltage. The FB voltage is also effectively offset by the CSA output voltage for accurately positioning the output voltage as a function of current. The output of the error amplifier is the COMP pin, which is compared to the internal PWM ramps to create the PWM pulse widths.

The negative input (FB) is tied to the output sense location with a resistor ( $R_B$ ) and is used for sensing and controlling the output voltage at this point. Additionally a current source is connected internally to the FB pin, which causes a fixed DC current to flow through  $R_B$ . This current creates a fixed voltage drop (offset voltage) across  $R_B$ . The offset voltage adds to the sensed output voltage, which causes the error amp to regulate the actual output voltage lower than the programmed VID voltage by this amount. The main loop compensation is incorporated into the feedback by an external network connected between FB and COMP.

#### DELAY TIMER

The delay times for the start-up timing sequence are set with a capacitor from the DELAY pin to ground, as described in the Start-Up Sequence section. In UVLO or when EN is logic low, the DELAY pin is held at ground. Once the UVLO and EN are asserted, a 15 $\mu$ A current flows out of the DELAY pin to charge C<sub>DLY</sub>. A comparator, with a threshold of 1.7V, monitors the DELAY pin voltage. The delay time is therefore set by the 15 $\mu$ A charging the delay capacitor from 0V to 1.7V. This DELAY pin is used for multiple delay timings (TD1, TD3, and TD5) during start-up. DELAY is also used for timing the current limit latch off as explained in the CURRENT LIMIT section.

#### SOFT-START

The soft-start times for the output voltage are set with a capacitor from the SS pin to ground. After TD1 and the phase-detection cycle have been completed, the SS time (TD2 in Figure 8) starts. The SS pin is disconnected from GND and the capacitor is charged up to the 1.1V boot voltage by the SS amplifier, which has a limited output current of  $15\mu$ A. The voltage at the FB pin follows the ramping voltage on the SS pin, limiting

the inrush current during start-up. The soft-start time depends on the value of the boot voltage and  $C_{SS}$ .

Once the SS voltage is within 100mV of the boot voltage, the boot voltage delay time (TD3) is started. The end of the boot voltage delay time signals the beginning of the second soft-start time (TD4). The SS voltage changes from the boot voltage to the programmed VID DAC voltage (either higher or lower) using the SS amplifier with the limited output current of 15 $\mu$ A. The voltage of the FB pin follows the ramping voltage of the SS pin, limiting the inrush current during the transition from the boot voltage to the final DAC voltage. The second soft-start time depends on the boot voltage, the programmed VID DAC voltage, and C<sub>SS</sub>.

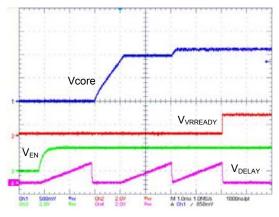

If either EN is taken low or  $V_{\text{CC}}$  drops below UVLO, DELAY and SS are reset to ground to be ready for another soft-start cycle. Figure 9 shows typical start-up waveforms for the FAN5033.

Figure 9: Start-up Waveforms

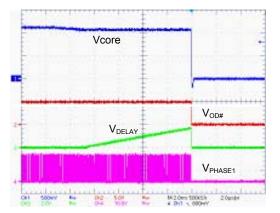

# CURRENT LIMIT, SHORT-CIRCUIT. AND LATCH-OFF PROTECTION

The FAN5033 compares a programmable current limit set point to the voltage from the output of the current sense amplifier. The current limit level is set with the resistor from the ILIMIT pin to ground. During operation, the voltage on ILIMIT is 1.7V. The current through the external resistor is internally scaled to give a current limit threshold of 10mV/ $\mu$ A. If the voltage between CSREF and CSCOMP rises above the current limit threshold, the internal current limit amplifier controls the internal COMP voltage to maintain the average output current at the limit.

After TD5 has completed, an over-current (OC) event starts a latch-off delay timer. The delay timer uses the DELAY pin timing capacitor. During current limit, the DELAY pin current is reduced to  $3.75 \ \mu$ A. When the voltage on the delay pin reaches 1.7V, the controller shuts down and latches off. The current limit latch-off delay time is therefore set by the current of  $3.75 \ \mu$ A charging the delay capacitor 1.7V. This delay is four times longer than the delay time during the start-up sequence. If there is a current limit during start-up, the FAN5033 goes through TD1 to TD5 in current limit and

starts the latch-off timer. Because the controller continues to operate during the latch-off delay time, if the OC is removed before the 1.7V threshold is reached, the controller returns to normal operation and the DELAY capacitor is reset to GND.

The latch-off function can be reset by cycling the supply voltage to the FAN5033 or by toggling the EN pin low for a short time. To disable the short-circuit latch-off function, an external resistor can be placed in parallel with  $C_{DLY}$  to prevent the DELAY capacitor from charging up to the 1.7V threshold. The addition of this resistor causes a slight increase in the delay times.

During start-up, when the output voltage is below 200mV, a secondary current limit is active. This secondary current limit clamps the internal COMP voltage at the PWM comparators to 1.5V. Typical overcurrent latch-off waveforms are shown in Figure 10.

Figure 10: Over-Current Latch-off Waveforms

#### DYNAMIC VID

The FAN5033 has the ability to dynamically change the VID inputs while the controller is running. This allows the output voltage to change while the supply is running and supplying current to the load. This is commonly referred to as VID on-the-fly (OTF). A VID OTF can occur under either light or heavy load conditions. The processor signals the controller by changing the VID inputs in multiple steps from the start code to the finish code. This change can be positive or negative.

When a VID input changes state, the FAN5033 detects the change and ignores the DAC inputs for a minimum of 200ns. This time prevents a false code due to logic skew while the eight VID inputs are changing. Additionally, the first VID change initiates the PWRGD and CROWBAR blanking functions for a minimum of 100µs to prevent a false PWRGD or CROWBAR event. Each VID change resets the internal timer.

#### POWER GOOD MONITORING

The power good comparator monitors the output voltage via the CSREF pin. The PWRGD pin is an open-drain output whose high level (when connected to a pull-up resistor) indicates that the output voltage is within the nominal limits specified based on the VID voltage setting. PWRGD goes low if the output voltage is outside of the specified range, if the VID DAC inputs are in no CPU mode, or whenever the EN pin is pulled low. PWRGD is blanked during a VID OTF event for a period of  $\sim$ 200µs to prevent false signals during the time the output is changing.

The PWRGD circuitry also incorporates an initial turn-on delay time (TD5) based on the DELAY timer. Prior to the SS voltage reaching the programmed VID DAC voltage of -100mV, the PWRGD pin is held low. Once the SS pin is within 100mV of the programmed DAC voltage, the capacitor on the DELAY pin begins to charge up. A comparator monitors the DELAY voltage and enables PWRGD when the voltage reaches 1.7V. The PWRGD delay time is therefore set by a current of 15 $\mu$ A charging a capacitor from 0V to 1.7V.

#### **OUTPUT CROWBAR**

As part of the protection for the load and output components of the supply, the PWM outputs are driven low (turning on the low-side MOSFETs) when the output voltage exceeds the upper crowbar threshold. This crowbar action stops once the output voltage falls below the release threshold of approximately 300mV.

Turning on the low-side MOSFETs pulls down the output as the reverse current builds up in the inductors. If the output over-voltage is due to a short in the high-side MOSFET, this action current-limits the input supply, protecting the microprocessor.

#### OUTPUT ENABLE AND UVLO

For the FAN5033 to begin switching, the input supply ( $V_{CC}$ ) to the controller must be higher than the UVLO threshold and the EN pin must be higher than its 0.85V threshold. This initiates a system start-up sequence. If either UVLO or EN is less than their respective thresholds, the FAN5033 is disabled, which holds the

PWM outputs low, discharges the DELAY and SS capacitors, and forces PWRGD and OD# signals low.

In the application circuit, the OD# pin should be connected to the OD# inputs of the FAN5009 or FAN5109 drivers. Pulling OD# low disables the drivers such that both DRVH and DRVL are driven low. This turns off the bottom MOSFETs to prevent them from discharging the output capacitors through the output inductors. If the bottom MOSFETs were left on, the output capacitors could ring with the output inductors and produce a negative output voltage to the processor.

Figure 11: Typical NTC Resistance vs. Temperature

## **Application Section**

### Instructions

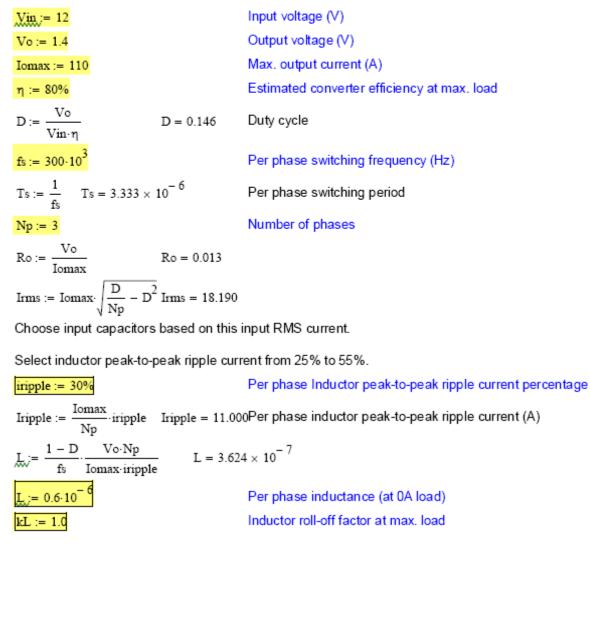

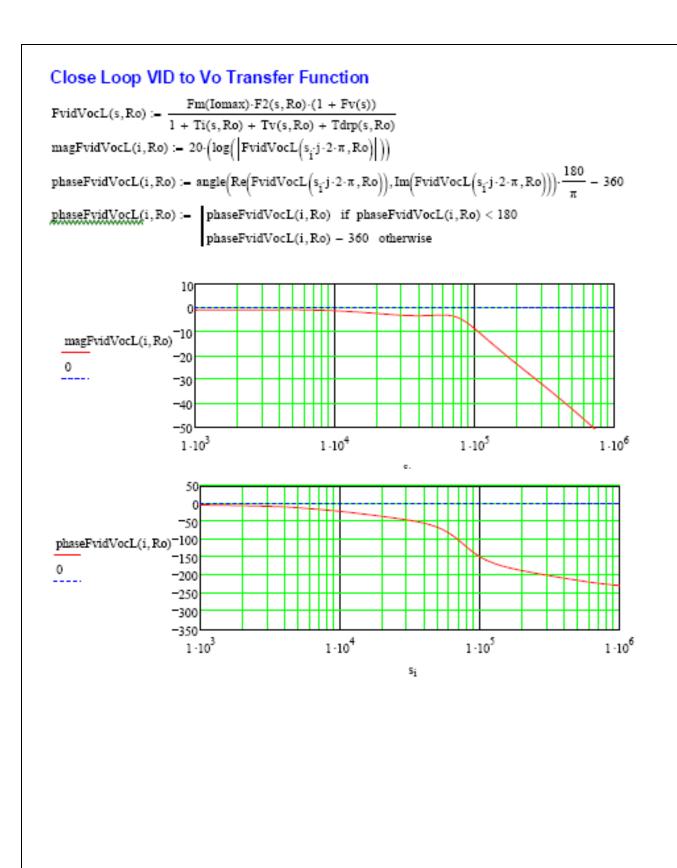

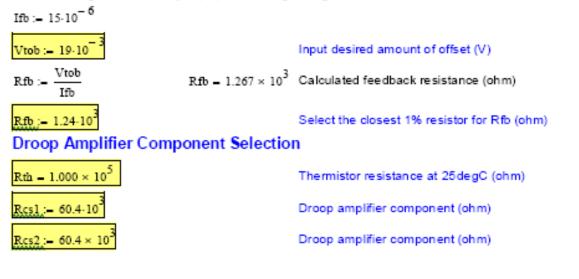

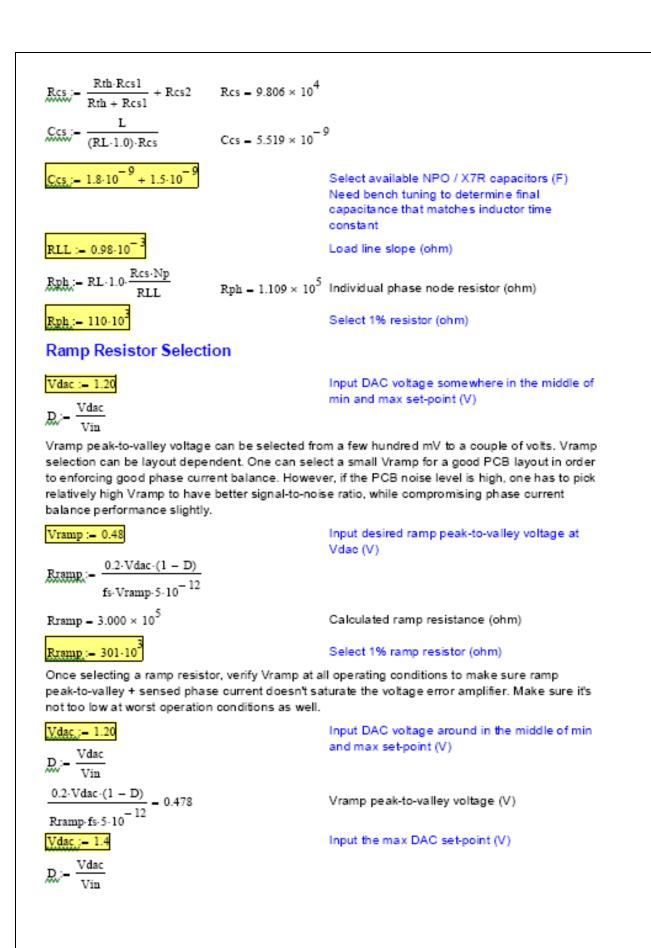

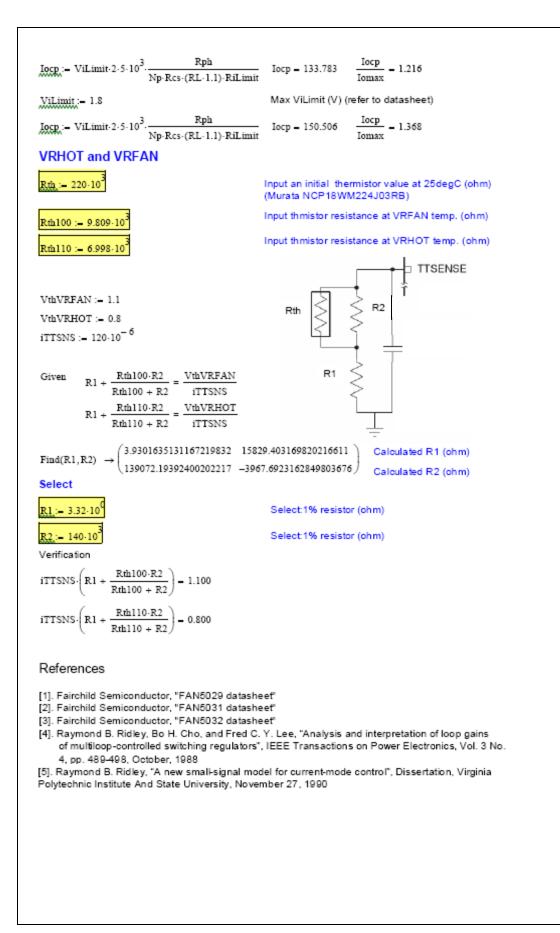

The purpose of this Mathcad program is to cover design and optimization of the control design that is very important for the FAN5029/31/32/33 based multiphase VR design in order to meet critical dynamic performance requirements. This Mathcad program is available from Fairchild upon request, and feel free to contact us should you have any questions.

Highlight regions, such as Vin := 12 are required input fields.

### Input Parameters

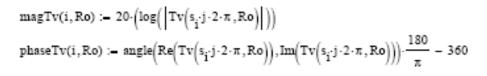

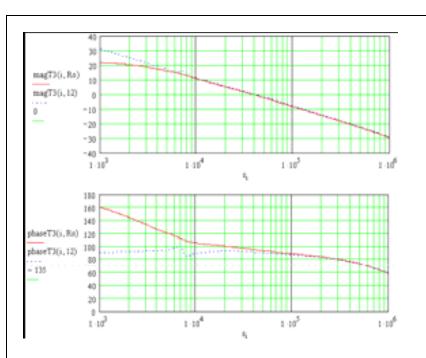

$$\begin{split} & \mathrm{Wn} := \frac{\pi}{\mathrm{Ts}} & \mathrm{Qz} := \frac{-2}{\pi} \\ & \mathrm{He}(s) := 1 + \frac{s}{\mathrm{Wn}\cdot\mathrm{Qz}} + \frac{s^2}{\mathrm{Wn}^2} \\ & \mathrm{Fi}(s) := \mathrm{Ri}\cdot\mathrm{He}(s) & \mathrm{Current\ sense\ gain} \\ & \mathrm{magFi}(i) := 20\cdot \left(\log\left(\left|\mathrm{Fi}\left(s_1^-j\cdot 2\cdot\pi\right)\right|\right)\right) & \mathrm{phaseFi}(i) := \mathrm{angle}\left(\mathrm{Re}\left(\mathrm{Fi}\left(s_1^-j\cdot 2\cdot\pi\right)\right), \mathrm{Im}\left(\mathrm{Fi}\left(s_1^-j\cdot 2\cdot\pi\right)\right)\right) \cdot \frac{180}{\pi}\right) \\ & \mathrm{Open\ Loop\ Transfer\ Function:\ F5(s) = iL/i0} \\ & \mathrm{F5}(s,\mathrm{Ro}) := \frac{1}{\frac{1}{\mathrm{Rc} + \frac{1}{\mathrm{s}\cdot\mathrm{C}}} + \frac{1}{\mathrm{Rc}^2 + \frac{1}{\mathrm{s}\cdot\mathrm{C}^2}} + \frac{1}{\mathrm{Ro}} + \frac{1}{\mathrm{s}\cdot\mathrm{L} + \mathrm{RL}} \cdot \frac{1}{\mathrm{s}\cdot\mathrm{L} + \mathrm{RL}} \\ & \mathrm{magF5}(i,\mathrm{Ro}) := 20\cdot \left(\log\left(\left|\mathrm{F5}\left(s_1^-j\cdot 2\cdot\pi,\mathrm{Ro}\right)\right|\right)\right) \\ & \mathrm{phaseF5}(i,\mathrm{Ro}) := \mathrm{angle}\left(\mathrm{Re}(\mathrm{F5}\left(s_1^-j\cdot 2\cdot\pi,\mathrm{Ro}\right)\right), \mathrm{Im}\left(\mathrm{F5}\left(s_1^-j\cdot 2\cdot\pi,\mathrm{Ro}\right)\right)\right) \cdot \frac{180}{\pi} - 360 \\ & \mathrm{Open\ Loop\ Control\ to\ Inductor\ Current\ Transfer\ Function:\ F4(s) = iL/d \\ & \mathrm{F4}(s,\mathrm{Ro}) := \mathrm{Vin} \cdot \frac{1}{\frac{s\cdot\mathrm{C}}{1+s\cdot\mathrm{Rc}\cdot\mathrm{C}} + \frac{1}{\frac{s\cdot\mathrm{C2}}{1+s\cdot\mathrm{Rc}^2\cdot\mathrm{C2}} + \frac{1}{\mathrm{Ro}} \\ & \mathrm{magF4}(i,\mathrm{Ro}) := 20\cdot \left(\log\left(\left|\mathrm{F4}\left(s_1^-j\cdot 2\cdot\pi,\mathrm{Ro}\right)\right|\right)\right) \\ & \mathrm{phaseF4}(i,\mathrm{Ro}) := \mathrm{angle}\left(\mathrm{Re}(\mathrm{F4}\left(s_1^-j\cdot 2\cdot\pi,\mathrm{Ro}\right)\right), \mathrm{Im}\left(\mathrm{F4}\left(s_1^-j\cdot 2\cdot\pi,\mathrm{Ro}\right)\right)\right) \cdot \frac{180}{\pi} - 0 \end{split}$$

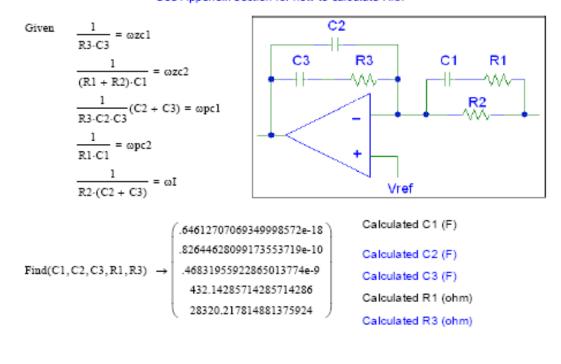

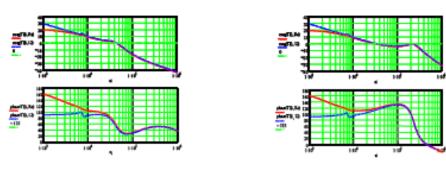

## Voltage Compensator Gain Fv(s)

For most of applications using electrolytic type dominant output capacitors, a 2-pole-1-zero compensator, consisting of R2, R3, C2, and C3 as shown in below, is sufficient to meet the VR dynamic requirements. However a placeholder for a 3-pole-2-zero compensator is always recommended in the PCB layout, in order to have a little flexibility to fine tune the VR performance.

For ceramic types of output capacitor dominant applications, a 3-pole-2-zero compensator is usually mandatory.

In this design example, electrolytic type dominant output capacitors are used.

The compensator design adopts an interactive approach. In such a condition, one can optimize the control design by interactive tuning the compensator parameters through a few iterations.

As a good starting point, select the compensator zero to be around 1.5 ~ 3.5X open loop power stage double poles, and select the high frequency pole to be around 0.8 ~ 2.5X per phase switching frequency. The compensator high frequency pole is placed in order to filter out high frequency switching noise. It's not recommended to place it too close to the control bandwidth. Use the DC gain of  $_{\Theta}$ I to adjust the control bandwidth. It's quite important to note that the

compensator zero and DC gain are critical parameters, and need to be fine tuned in interactive manner through a few iterations of this program.  $f_{zc1 := 12 \cdot 10^3}$ Place the compensator zero to cancel the power stage pole (1.5 ~ 3.5X open loop power stage double poles) (Hz)

To cancel the power stage pole (Hz)

To be placed around 0.8 ~ 2.5X the per phase switching frequency (Hz)

ωpcl := 2·π·fpcl fpc2 := 57·10<sup>13</sup>

To cancel the lower power stage esr zero (Hz)

ωpc2 := 2π-fpc2

fzc2 := 15.10<sup>13</sup>

$\omega zc2 := 2 \cdot \pi \cdot fzc2$

fpc1 := 80.10<sup>2</sup>

ωI:= 1.5·10<sup>6</sup>

Cross over freq. adjustment