November 2010

# FAN4800 Low Startup Current PFC/PWM Controller Combinations

### **Features**

- Low Startup Current (100µA Typical)

- Low Operating Current (2.5mA Typical)

- Low Total Harmonic Distortion, High Power Factor

- Pin-Compatible Upgrade for the ML4800

- Average Current, Continuous or Discontinuous Boost, Leading-Edge PFC

- Slew Rate Enhanced Transconductance Error Amplifier for Ultra-Fast PFC Response

- Internally Synchronized Leading-Edge PFC and Trailing-Edge PWM

- Reduction of Ripple Current in the Storage Capacitor between the PFC and PWM Sections

- PWM Configurable for Current Mode or Voltage Mode

- Additional Folded-Back Current Limit for PWM Section

- 20V BiCMOS Process

- V<sub>IN</sub> OK Guaranteed Turn-on PWM at 2.25V

- V<sub>CC</sub> OVP Comparator, Low-Power Detect Comparator

- Current-Fed Gain Modulator for Improved Noise Immunity

- Brownout Control, Over-Voltage Protection, UVLO, Soft-Start, and Reference OK

- Available in16-DIP Package

## **Applications**

- Desktop PC Power Supply

- Internet Server Power Supply

- Uninterruptible Power Supply (UPS)

- Battery Charger

- DC Motor Power Supply

- Monitor Power Supply

- Telecom System Power Supply

- Distributed Power

## Description

The FAN4800 is a controller for power-factor-corrected, switched-mode power supplies. Power Factor Correction (PFC) allows the use of smaller, lower-cost bulk capacitors, reduces power line loading and stress on the switching FETs, and results in a power supply that fully complies with IEC-1000-3-2 specifications. Intended as a BiCMOS version of the industry-standard ML4800, the FAN4800 includes circuits for the implementation of leading-edge, average-current, boost-type power factor correction and a trailing-edge Pulse Width Modulator (PWM). A gate driver with 1A capabilities minimizes the need for external driver circuits. Low-power requirements improve efficiency and reduce component costs.

An over-voltage comparator shuts down the PFC section in the event of a sudden decrease in load. The PFC section also includes peak current limiting and input voltage brownout protection. The PWM section can be operated in current or voltage mode, at up to 250kHz, and includes an accurate 50% duty cycle limit to prevent transformer saturation.

The FAN4800 includes a folded-back current limit for the PWM section to provide short-circuit protection.

## **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package |      | Marking<br>Code |  |

|-------------|--------------------------------|---------|------|-----------------|--|

| FAN4800IN   | FAN4800IN -40°C to +125°C      |         | Rail | FAN4800         |  |

| FAN4800IN_G | -40°C to +125°C                | 16-PDIP | Rail | FAN4800         |  |

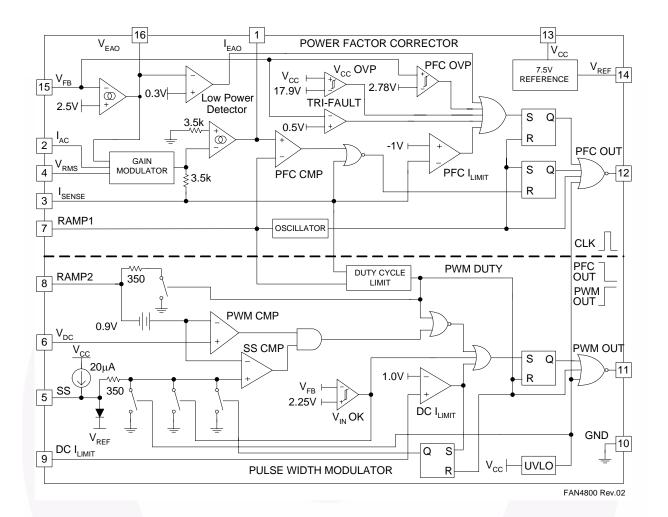

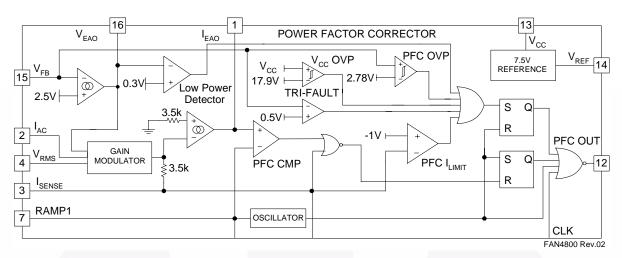

## **Block Diagram**

Figure 1. Internal Block Diagram

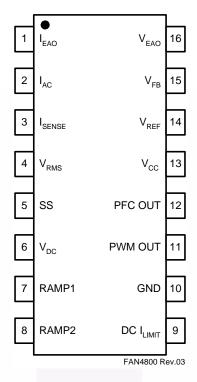

## **Pin Configuration**

Figure 2. Pin Configuration (Top View)

## **Pin Definitions**

| Pin# | Name                  | Description                                                                                                                                  |  |  |

|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | I <sub>EAO</sub>      | PFC transconductance current error amplifier output                                                                                          |  |  |

| 2    | I <sub>AC</sub>       | PFC gain control reference input                                                                                                             |  |  |

| 3    | I <sub>SENSE</sub>    | Current sense input to the PFC current limit comparator                                                                                      |  |  |

| 4    | V <sub>RMS</sub>      | Input for PFC RMS line voltage compensation                                                                                                  |  |  |

| 5    | SS                    | Connection point for the PWM soft-start capacitor                                                                                            |  |  |

| 6    | $V_{DC}$              | PWM voltage feedback input                                                                                                                   |  |  |

| 7    | RAMP1 (RtCt)          | Oscillator timing node; timing set by RT, CT                                                                                                 |  |  |

| 8    | RAMP2 (PWM RAMP)      | In current mode, this pin functions as the current-sense input. In voltage mode it is the PWM input from the PFC output (feed forward ramp). |  |  |

| 9    | DC I <sub>LIMIT</sub> | PWM current-limit comparator input                                                                                                           |  |  |

| 10   | GND                   | Ground                                                                                                                                       |  |  |

| 11   | PWM OUT               | PWM driver output                                                                                                                            |  |  |

| 12   | PFC OUT               | PFC driver output                                                                                                                            |  |  |

| 13   | V <sub>CC</sub>       | Positive supply                                                                                                                              |  |  |

| 14   | $V_{REF}$             | Buffered output for the internal 7.5V reference                                                                                              |  |  |

| 15   | V <sub>FB</sub>       | PFC transconductance voltage error amplifier input                                                                                           |  |  |

| 16   | V <sub>EAO</sub>      | PFC transconductance voltage error amplifier output                                                                                          |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol               | Parameter                                           | Min.    | Max.                 | Unit |

|----------------------|-----------------------------------------------------|---------|----------------------|------|

| V <sub>CC</sub>      | Positive Supply Voltage                             |         | 20                   | V    |

| I <sub>EAO</sub>     | PFC Transconductance Current Error Amplifier Output | 0       | 5.5                  | V    |

| V <sub>ISENSE</sub>  | I <sub>SENSE</sub> Voltage                          | -3.0    | 0.7                  | V    |

|                      | Voltage on Any Other Pin                            | GND-0.3 | V <sub>CC</sub> +0.3 | V    |

| I <sub>REF</sub>     | I <sub>REF</sub> Current                            |         | 10                   | mA   |

| I <sub>AC</sub>      | I <sub>AC</sub> Input Current                       |         | 1                    | mA   |

| I <sub>PFC_OUT</sub> | Peak PFC OUT Current, Source or Sink                |         | 1                    | А    |

| I <sub>PWM_OUT</sub> | Peak PWM OUT Current, Source or Sink                |         | 1                    | А    |

|                      | PFC OUT, PWM OUT Energy per Cycle                   |         | 1.5                  | μJ   |

| T <sub>J</sub>       | Junction Temperature                                |         | +150                 | °C   |

| T <sub>STG</sub>     | Storage Temperature Range                           | -65     | +150                 | °C   |

| T <sub>A</sub>       | Operating Temperature Range                         | -40     | +125                 | °C   |

| TL                   | Lead Temperature (Soldering,10 Seconds)             |         | +260                 | °C   |

| $\theta_{JA}$        | Thermal Resistance                                  |         | 80                   | °C/W |

## **Electrical Characteristics**

Unless otherwise stated, these specifications apply:  $V_{CC}$  = 15V,  $R_T$  = 52.3K $\Omega$ ,  $C_T$  = 470pF, and  $T_A$  = -40°C to 125°C.

| Symbol                             | Parameter Condition                         |                                                                                 | Min.  | Тур.  | Max. | Unit |

|------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------|-------|-------|------|------|

| VOLTAGE E                          | RROR AMPLIFIER                              |                                                                                 | II.   |       | 1    |      |

| V <sub>FB</sub>                    | Input Voltage Range <sup>(1)</sup>          |                                                                                 | 0     |       | 6    | V    |

| gm1                                | Transconductance                            |                                                                                 | 50    | 70    | 90   | µmho |

| V <sub>ref</sub> (PFC)             | Feedback Reference Voltage                  | T <sub>A</sub> = 25°C                                                           | 2.45  | 2.50  | 2.55 | V    |

| I <sub>b</sub> (V <sub>EAO</sub> ) | Input Bias Current <sup>(2)</sup>           |                                                                                 | -1.00 | -0.05 |      | mA   |

| V <sub>EAO</sub> (H)               | Output High-Voltage                         |                                                                                 | 5.8   | 6.0   |      | V    |

| V <sub>EAO</sub> (L)               | Output Low-Voltage                          |                                                                                 |       | 0.1   | 0.4  | V    |

| I <sub>sink</sub> (V)              | Sink Current                                | T <sub>A</sub> = 25°C, V <sub>FB</sub> = 3V,<br>V <sub>EAO</sub> = 6.0V         |       | -35   | -20  | μΑ   |

| I <sub>source</sub> (V)            | Source Current                              | T <sub>A</sub> = 25°C, V <sub>FB</sub> = 1.5V<br>V <sub>EAO</sub> = 1.5V        | 30    | 40    |      | μΑ   |

| G <sub>V</sub>                     | Open-Loop Gain <sup>(1)(3)</sup>            |                                                                                 | 50    | 60    |      | dB   |

| PSRR1                              | Power Supply Rejection Ratio <sup>(1)</sup> | 11V < V <sub>CC</sub> < 16.5V                                                   | 50    | 60    |      | dB   |

| CURRENT E                          | RROR AMPLIFIER                              |                                                                                 | \     | I     |      |      |

| V <sub>IEAO</sub>                  | Input Voltage Range <sup>(1)</sup>          |                                                                                 | -1.5  |       | 0.7  | V    |

| gm2                                | Transconductance                            |                                                                                 | 50    | 85    | 100  | µmho |

| V <sub>offset</sub>                | Input Offset Voltage                        | T <sub>A</sub> = 25°C                                                           |       |       | 25   | mV   |

| I <sub>beao</sub>                  | Input Bias Current <sup>(1)</sup>           |                                                                                 | -1    |       |      | μA   |

| I <sub>EAO</sub> (H)               | Output High-Voltage                         |                                                                                 | 4.00  | 4.25  |      | V    |

| I <sub>EAO</sub> (L)               | Output Low-Voltage                          |                                                                                 |       | 1.0   | 1.2  | V    |

| I <sub>sink</sub> (I)              | Sink Current                                | I <sub>SENSE</sub> = +0.5, I <sub>EAO</sub> = 4.0V                              |       | -65   | -35  | μA   |

| I <sub>source</sub> (I)            | Source Current                              | I <sub>SENSE</sub> = -0.5, I <sub>EAO</sub> = 1.5V                              | 35    | 75    |      | μA   |

| Gi                                 | Open-Loop Gain <sup>(1)</sup>               |                                                                                 | 60    | 70    |      | dB   |

| PSRR2                              | Power Supply Rejection Ratio <sup>(1)</sup> | 11V < V <sub>CC</sub> < 16.5V                                                   | 60    | 75    |      | dB   |

| PFC OVP C                          | OMPARATOR                                   | ,                                                                               |       | I     | II.  |      |

| Vovp                               | Threshold Voltage                           | T <sub>A</sub> = 25°C                                                           | 2.70  | 2.78  | 2.90 | V    |

| HY(ovp)                            | Hysteresis                                  | T <sub>A</sub> = 25°C                                                           | 230   |       | 350  | mV   |

| LOW-POWE                           | R DETECT COMPARATOR                         |                                                                                 | Į.    | Į.    |      | Į.   |

| V <sub>th</sub> (lp)               | Threshold Voltage                           | T <sub>A</sub> = 25°C                                                           | 0.15  | 0.30  | 0.40 | V    |

| VCC OVP C                          | OMPARATOR                                   | ,                                                                               | 1     |       |      |      |

| V <sub>CC_OVP</sub>                | Threshold Voltage                           | T <sub>A</sub> = 25°C                                                           | 17.5  | 17.9  | 18.5 | V    |

| HY(V <sub>CC_OVP</sub> )           | Hysteresis                                  | T <sub>A</sub> = 25°C                                                           | 1.40  | 1.50  | 1.65 | V    |

| TRI-FAULT                          | DETECT                                      | <u>'</u>                                                                        |       | I     |      | 3/   |

| $t_{d(F)}$                         | Time to Fault Detect HIGH <sup>(1)</sup>    | $V_{FB} = V_{Fault}$ Detect LOW to $V_{FB} = Open$ . 470pF from $V_{FB}$ to GND |       | 2     | 4    | ms   |

| F(L)                               | Fault Detect LOW                            |                                                                                 | 0.4   | 0.5   | 0.6  | V    |

## **Electrical Characteristics** (Continued)

Unless otherwise stated, these specifications apply:  $V_{CC}$  = 15V,  $R_T$  = 52.3k $\Omega$ ,  $C_T$  = 470pF, and  $T_A$  = -40°C to 125°C.

| Symbol                               | Parameter                                                               | Condition                                                                | Min.  | Тур.  | Max.  | Unit                  |

|--------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|-------|-------|-------|-----------------------|

| PFC I <sub>LIMIT</sub> C             | OMPARATOR                                                               |                                                                          |       | •     | •     | •                     |

| V <sub>th(cs)</sub>                  | Threshold Voltage                                                       |                                                                          | -1.10 | -1.00 | -0.90 | V                     |

| V <sub>th(cs)</sub> -V <sub>gm</sub> | (PFC I <sub>LIMIT</sub> V <sub>TH</sub> – Gain Modulator Output)        |                                                                          | 5     | 100   |       | mV                    |

| t <sub>d(pfc_off)</sub>              | Delay to Output <sup>(1)</sup>                                          |                                                                          |       | 250   |       | ns                    |

| DC I <sub>LIMIT</sub> CC             | MPARATOR                                                                |                                                                          |       |       |       |                       |

| V <sub>th(DC)</sub>                  | Threshold Voltage                                                       |                                                                          | 0.95  | 1.00  | 1.05  | V                     |

| t <sub>d</sub> (pwm_off)             | Delay to Output <sup>(1)</sup>                                          |                                                                          |       | 250   |       | ns                    |

| VIN OK COM                           | IPARATOR                                                                |                                                                          |       |       |       |                       |

| V <sub>th(OK)</sub>                  | Threshold Voltage                                                       |                                                                          | 2.10  |       | 2.45  | V                     |

| HY(OK)                               | Hysteresis                                                              |                                                                          | 0.8   | 1.0   | 1.2   | V                     |

| GAIN MODU                            | JLATOR                                                                  |                                                                          |       | •     |       |                       |

| G1                                   |                                                                         | $I_{AC} = 100\mu A, V_{RMS} = 0, V_{FB} = 1V, T_A = 25^{\circ}C$         | 0.70  | 0.84  | 0.95  |                       |

| G2                                   | O-: (3)                                                                 | $I_{AC} = 100 \mu A, V_{RMS} = 1.1 V, V_{FB} = 1 V, T_A = 25 ^{\circ} C$ | 1.80  | 2.00  | 2.20  | - Gain <sup>(3)</sup> |

| G3                                   | - Gain <sup>(3)</sup>                                                   | $I_{AC} = 150\mu A, V_{RMS} = 1.8V, V_{FB} = 1V, T_A = 25^{\circ}C$      | 0.90  | 1.00  | 1.10  |                       |

| G4                                   |                                                                         | $I_{AC} = 300 \mu A, V_{RMS} = 3.3 V, V_{FB} = 1 V, T_A = 25 ^{\circ} C$ | 0.25  | 0.32  | 0.40  |                       |

| BW                                   | Band Width <sup>(1)</sup>                                               | $I_{AC} = 100\mu A$                                                      |       | 10    |       | MHz                   |

| Vo(gm)                               | Output Voltage<br>= 3.5kΩ x (I <sub>SENSE</sub> – I <sub>OFFSET</sub> ) | $I_{AC} = 250\mu A, V_{RMS} = 1.1V, V_{FB} = 2V, T_A = 25^{\circ}C$      | 0.80  | 1.00  | 1.20  | V                     |

| OSCILLATO                            | PR                                                                      |                                                                          |       |       |       |                       |

| f <sub>osc1</sub>                    | Initial Accuracy                                                        | T <sub>A</sub> = 25°C                                                    | 68    |       | 81    | kHz                   |

| $\Delta f_{osc1}$                    | Voltage Stability                                                       | 11V < V <sub>CC</sub> < 16.5V                                            | 7     | 1     |       | %                     |

| $\Delta f_{osc2}$                    | Temperature Stability                                                   |                                                                          |       | 2     |       | %                     |

| f <sub>osc2</sub>                    | Total Variation                                                         | Line, Temp                                                               | 66    |       | 84    | kHz                   |

| $V_{ramp}$                           | Ramp Valley to Peak Voltage <sup>(1)</sup>                              |                                                                          |       | 2.75  |       | V                     |

| t <sub>dead</sub>                    | PFC Dead Time                                                           |                                                                          |       | 685   | 7     | ns                    |

| I <sub>dis</sub>                     | CT Discharge Current                                                    | $V_{RAMP2} = 0V$ , $V_{RAMP1} = 2.5V$                                    | 6.5   |       | 15.0  | mA                    |

| REFERENC                             | E                                                                       |                                                                          |       |       |       |                       |

| V <sub>ref1</sub>                    | Output Voltage                                                          | $T_A = 25$ °C, $I(V_{REF}) = 1$ mA                                       | 7.4   | 7.5   | 7.6   | V                     |

| $\Delta V_{ref1}$                    | Line Regulation                                                         | 11V < V <sub>CC</sub> < 16.5V                                            |       | 10    | 25    | mV                    |

| $\Delta V_{ref2}$                    | Load Regulation                                                         | $0mA < I(V_{REF}) < 7mA$                                                 |       | 10    | 20    | mV                    |

| $\Delta V_{ref4}$                    | Temperature Stability                                                   |                                                                          |       | 0.4   |       | %                     |

| V <sub>ref2</sub>                    | Total Variation <sup>(1)</sup>                                          | Line, Load, Temperature                                                  | 7.35  |       | 7.65  | V                     |

| $\Delta V_{ref5}$                    | Long Term Stability <sup>(1)</sup>                                      | $T_J = 125^{\circ}C$ , 1000 hours                                        | 5     |       | 25    | mV                    |

## **Electrical Characteristics** (Continued)

Unless otherwise stated, these specifications apply:  $V_{CC}$  = 15V,  $R_T$  = 52.3k $\Omega$ ,  $C_T$  = 470pF,  $T_A$  = -40°C to 125°C.

| Symbol                  | Parameter                         | Condition                                                                      | Min.  | Тур.  | Max.  | Unit |

|-------------------------|-----------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|------|

| PFC                     |                                   |                                                                                |       | •     |       |      |

| D <sub>min.</sub>       | Minimum Duty Cycle                | V <sub>IEAO</sub> > 4.0V                                                       |       |       | 0     | %    |

| D <sub>max.</sub>       | Maximum Duty Cycle                | V <sub>IEAO</sub> < 1.2V                                                       | 92    | 95    |       | %    |

| R <sub>ON</sub> (low)1  | Output Low P                      | $I_{OUT} = -20$ mA at $T_A = 25$ °C                                            |       |       | 15    | Ω    |

| R <sub>ON</sub> (low)2  | Output Low R <sub>dson</sub>      | $I_{OUT} = -100$ mA at $T_A = 25$ °C                                           |       |       | 15    | Ω    |

| Vol1                    | Output Low Voltage <sup>(1)</sup> | $I_{OUT} = -10 \text{mA}, V_{CC} = 9 \text{V},$<br>$T_A = 25 ^{\circ}\text{C}$ |       | 0.4   | 0.8   | V    |

| R <sub>ON</sub> (high)1 | Output High B                     | I <sub>OUT</sub> = 20mA at T <sub>A</sub> = 25°C                               |       | 15    | 20    | Ω    |

| R <sub>ON</sub> (high)2 | Output High R <sub>dson</sub>     | $I_{OUT} = 100$ mA at $T_A = 25$ °C                                            |       | 15    | 20    | Ω    |

| t <sub>r(pfc)</sub>     | Rise/Fall Time <sup>(1)</sup>     | C <sub>L</sub> = 1000pF                                                        |       | 50    |       | ns   |

| PWM                     |                                   |                                                                                |       | •     |       |      |

| D                       | Duty Cycle Range                  |                                                                                | 0-42  | 0-47  | 0-49  | %    |

| R <sub>ON</sub> (low)3  | Output Low D                      | $I_{OUT} = -20$ mA at $T_A = 25$ °C                                            |       |       | 15    | Ω    |

| R <sub>ON</sub> (low)4  | Output Low R <sub>dson</sub>      | $I_{OUT} = -100$ mA at $T_A = 25$ °C                                           |       |       | 15    | Ω    |

| Vol2                    | Output Low Voltage                | $I_{OUT} = -10 \text{mA}, V_{CC} = 9 \text{V},$<br>$T_A = 25 ^{\circ}\text{C}$ |       | 0.4   | 0.8   | V    |

| R <sub>ON</sub> (high)3 | Output Llich D                    | I <sub>OUT</sub> = 20mA at T <sub>A</sub> = 25°C                               |       | 15    | 20    | Ω    |

| R <sub>ON</sub> (high)4 | Output High R <sub>dson</sub>     | $I_{OUT} = 100$ mA at $T_A = 25$ °C                                            |       | 15    | 20    | Ω    |

| t <sub>r(pwm)</sub>     | Rise/Fall Time                    | $C_L = 1000 pF^{(1)}$                                                          |       | 50    |       | ns   |

| PWM(Is)                 | PWM Comparator Level Shift        |                                                                                | 0.6   | 0.9   | 1.2   | V    |

| SUPPLY                  |                                   |                                                                                |       |       |       |      |

| I <sub>st</sub>         | Startup Current                   | $V_{CC} = 12V, C_L = 0pF$                                                      |       | 100   | 200   | μΑ   |

| I <sub>op</sub>         | Operating Current                 | 14V, C <sub>L</sub> = 0pF                                                      |       | 2.5   | 7.0   | mA   |

| V <sub>th(start)</sub>  | Under-Voltage Lockout Threshold   |                                                                                | 12.74 | 13.00 | 13.26 | V    |

| V <sub>th(hys)</sub>    | Under-Voltage Lockout Hysteresis  |                                                                                | 2.80  | 3.00  | 3.20  | V    |

#### Notes:

- 1. This parameter, although guaranteed by design, is not 100% production tested.

- 2. Includes all bias currents to other circuits connected to the  $\rm V_{FB}$  pin.

- 3. Gain = K × 5.375V; K =  $(I_{SENSE} I_{OFFSET}) \times [I_{AC} \times (V_{EAO} 0.625)]^{-1}$ ;  $V_{EAO \ (MAX.)} = 6V$ .

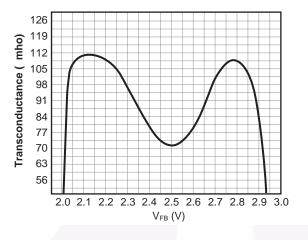

## **Typical Performance Characteristics**

100 90 Fransconductance (mho) 80 70 60 50 40 30 20 10 0 -10 -0.8 -0.6 -0.4 -0.2 0.0 0.2 0.4 0.6 I<sub>SENSE</sub> (V)

Figure 3. Voltage Error Amplifier (gmv)

Transconductance

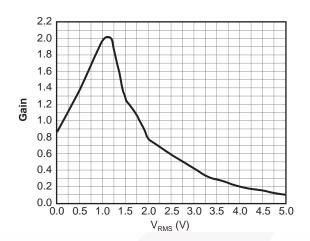

Figure 4. Current Error Amplifier (gmi)

Transconductance

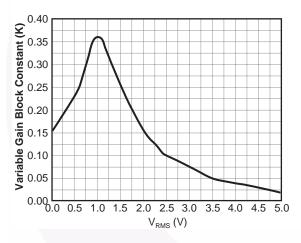

Figure 5. Gain Modulator Transfer Characteristic (K)

Figure 6. Gain vs. V<sub>RMS</sub>

$$K = \frac{I_{GAINMOD} - I_{OFFSET}}{I_{AC} \times (6 - 0.625)} mV^{-1}$$

(1)

$$Gain = \frac{I_{SENSE} - I_{OFFSET}}{I_{AC}}$$

## **Functional Description**

The FAN4800 consists of an average-current controlled, continuous boost Power Factor Correction (PFC) frontend and a synchronized Pulse Width Modulator (PWM) back-end. The PWM can be used in either current or voltage mode. In voltage mode, feed forward from the PFC output bus can be used to improve the PWM's line regulation. In either mode, the PWM stage uses conventional trailing-edge, duty-cycle modulation. This proprietary leading/trailing edge modulation results in a higher usable PFC error amplifier bandwidth and can significantly reduce the size of the PFC DC bus capacitor.

The synchronization of the PWM with the PFC simplifies the PWM compensation due to the controlled ripple on the PFC output capacitor (the PWM input capacitor). The PWM section of the FAN4800 runs at the same frequency as the PFC.

In addition to power factor correction, a number of protection features are built into the FAN4800. These include soft-start, PFC over-voltage protection, peak current limiting, brownout protection, duty-cycle limiting, and under-voltage lockout (UVLO).

#### **Power Factor Correction**

Power Factor Correction treats a nonlinear load like a resistive load to the AC line. For a resistor, the current drawn from the line is in phase with and proportional to the line voltage, so the power factor is unity (one). A common class of nonlinear load is the input of most power supplies, which use a bridge rectifier and capacitive input filter fed from the line.

The peak charging effect, which occurs on the input filter capacitor in these supplies, causes brief high-amplitude pulses of current to flow from the power line, rather than a sinusoidal current in phase with the line voltage. Such supplies present a power factor to the line of less than one (i.e., they cause significant current harmonics of the power line frequency to appear at the input). If the input current drawn by such a supply (or any nonlinear load) can be made to follow the input voltage in instantaneous amplitude, it appears resistive to the supply.

To hold the input current draw of a device drawing power from the AC line in phase with and proportional to the input voltage, that device must be prevented from loading the line except in proportion to the instantaneous line voltage. To accomplish this, the PFC section of the FAN4800 uses a boost mode DC-DC converter. The input to the converter is the full-wave, rectified, AC line voltage. No bulk filtering is applied following the bridge rectifier, so the input voltage to the boost converter ranges (at twice line the frequency) from zero volts to a peak value of the AC input and back to zero. By forcing the boost converter to meet two simultaneous conditions, it is possible to ensure that the current drawn from the power line is proportional to the input line voltage.

One of these conditions is that the output voltage of the boost converter must be set higher than the peak value of the line voltage. A commonly used value is 385V<sub>DC</sub>, to allow for a high line of 270V<sub>AC</sub> rms. The second condition is that the current drawn from the line at any given instant must be proportional to the line voltage. Establishing a suitable voltage control loop for the converter, which in turn drives a current error amplifier and switching output driver, satisfies the first of these requirements. The second requirement is met by using the rectified AC line voltage to modulate the output of the voltage control loop. Such modulation causes the current error amplifier to command a power stage current that varies directly with the input voltage. To prevent ripple, which necessarily appears at the output of boost circuit (typically about 10V<sub>AC</sub> on a 385V<sub>DC</sub> level), from introducing distortion back through the voltage error amplifier, the bandwidth of the voltage loop is deliberately kept low. A final refinement is to adjust the overall gain of the PFC section to be proportional to 1/V<sub>IN</sub><sup>2</sup>, which linearizes the transfer function of the system as the AC input voltage.

Since the boost converter in the FAN4800 PFC is current averaging, no slope compensation is required.

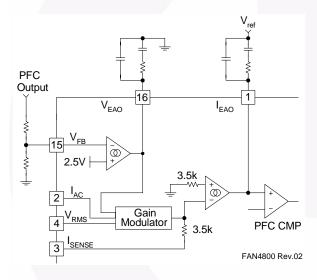

#### 1. PFC Section

### 1.1 Gain Modulator

Figure 1 shows a block diagram of the PFC section of the FAN4800. The gain modulator is the heart of the PFC, as the circuit block controls the response of the current loop to line voltage waveform and frequency, RMS line voltage, and PFC output voltages. There are three inputs to the gain modulator:

- 1. A current representing the instantaneous input voltage (amplitude and wave shape) to the PFC. The rectified AC input sine wave is converted to a proportional current via a resistor and is then fed into the gain modulator at I<sub>AC</sub>. Sampling current in this way minimizes ground noise, required in high-power, switching-power conversion environments. The gain modulator responds linearly to this current.

- 2. A voltage proportional to the long-term RMS AC line voltage, derived from the rectified line voltage after scaling and filtering. This signal is presented to the gain modulator at V<sub>RMS</sub>. The output of the gain modulator is inversely proportional to V<sub>RMS</sub><sup>2</sup> (except at unusually low values of V<sub>RMS</sub>, where special gain contouring takes over to limit power dissipation of the circuit components under heavy brownout conditions). The relationship between V<sub>RMS</sub> and gain is called K and is illustrated in Figure 5.

The output of the voltage error amplifier, V<sub>EAO</sub>. The gain modulator responds linearly to variation in V<sub>EAO</sub>.

The output of the gain modulator is a current signal, in the form of a full wave rectified sinusoid at twice the line frequency. This current is applied to the virtual ground (negative) input of the current error amplifier. In this way, the gain modulator forms the reference for the current error loop and ultimately controls the instantaneous current draw of the PFC from the power line. The general form of the output of the gain modulator is:

$$I_{GAINMOD} = \frac{I_{AC} \times V_{EAO}}{V_{RMS}^2} \times 1V$$

(3)

More precisely, the output current of the gain modulator is given by:

$$I_{GAINMOD} = K \times (V_{EAO} - 0.625) \times I_{AC}$$

(4)

where K is in units of V<sup>-1</sup>.

The output current of the gain modulator is limited around 228.57 $\mu$ A and the maximum output voltage of the gain modulator is limited to 228.57 $\mu$ A x 3.5K = 0.8V.

This 0.8V also determines the maximum input power. However,  $I_{GAINMOD}$  cannot be measured directly from  $I_{SENSE}$ .  $I_{SENSE} = I_{GAINMOD} - I_{OFFSET}$  and  $I_{OFFSET}$  can only be measured when  $V_{EAO}$  is less than 0.5V and  $I_{GAINMOD}$  is 0A. Typical  $I_{OFFSET}$  is around  $60\mu A$ .

## 1.2 Selecting R<sub>AC</sub> for I<sub>AC</sub> pin

$I_{AC}$  pin is the input of the gain modulator.  $I_{AC}$  is also a current mirror input and requires current input. Selecting a proper resistor  $R_{AC}$  provides a good sine wave current derived from the line voltage and helps program the maximum input power and minimum input line voltage.

$R_{AC} = V_{IN}$  peak x 7.9K. For example, if the minimum line voltage is  $80V_{AC}$ , the  $R_{AC} = 80 \times 1.414 \times 7.9K = 894k\Omega$ .

### 1.3 Current Error Amplifier, IEAO

The current error amplifier's output controls the PFC duty cycle to keep the average current through the boost inductor a linear function of the line voltage. At the inverting input to the current error amplifier, the output current of the gain modulator is summed with a current, which results from a negative voltage being impressed upon the I<sub>SENSE</sub> pin.

The negative voltage on I<sub>SENSE</sub> represents the sum of all currents flowing in the PFC circuit and is typically derived from a current sense resistor in series with the negative terminal of the input bridge rectifier.

The inverting input of the current error amplifier is a virtual ground. Given this fact, and the arrangement of the duty cycle modulator polarities internal to the PFC, an increase in positive current from the gain modulator causes the output stage to increase its duty cycle until the voltage on  $I_{\rm SENSE}$  is adequately negative to cancel this increased current. Similarly, if the gain modulator's output decreases, the output duty cycle decreases to achieve a less negative voltage on the  $I_{\rm SENSE}$  pin.

## 1.4 Cycle-By-Cycle Current Limiter and Selecting R<sub>S</sub>

As well as being a part of the current feedback loop, the  $I_{SENSE}$  pin is a direct input to the cycle-by-cycle current limiter for the PFC section. If the input voltage at this pin is ever less than -1V, the output of the PFC is disabled until the protection flip-flop is reset by the clock pulse at the start of the next PFC power cycle.

$\rm R_S$  is the sensing resistor of the PFC boost converter. During the steady state, line input current x  $\rm R_S$  equals  $\rm I_{GAINMOD}$  x 3.5K.

Since the maximum output voltage of the gain modulator is  $I_{GAINMOD}$  maximum x 3.5k = 0.8V during the steady state,  $R_S$  x line input current is limited to below 0.8V as well. Therefore, to choose  $R_S$ , use the following equation:

$$R_{S} = \frac{0.8V \times V_{INPEAK}}{2 \times Line Input Power}$$

(5)

For example, if the minimum input voltage is  $80V_{AC}$  and the maximum input RMS power is 200Watt,  $R_S = (0.8V \times 80V \times 1.414) / (2 \times 200) = 0.226\Omega$ .

### 1.5 PFC OVP

In the FAN4800, the PFC OVP comparator serves to protect the power circuit from being subjected to excessive voltages if the load changes suddenly. A resistor divider from the high-voltage DC output of the PFC is fed to  $V_{FB}$ . When the voltage on  $V_{FB}$  exceeds 2.78V, the PFC output driver is shut down. The PWM section continues to operate. The OVP comparator has 280mV of hysteresis and the PFC does not restart until the voltage at  $V_{FB}$  drops below 2.50V.  $V_{CC}$  OVP can also serve as a redundant PFC OVP protection.  $V_{CC}$  OVP threshold is 17.9V with 1.5V hysteresis.

Figure 7. PFC Section Block Diagram

## 1.6 Error Amplifier Compensation

The PWM loading of the PFC can be modeled as a negative resistor because an increase in the input voltage to the PWM causes a decrease in the input current. This response dictates the proper compensation of the two transconductance error amplifiers.

Figure 8 shows the types of compensation networks most commonly used for the voltage and current error amplifiers, along with their respective return points. The current-loop compensation is returned to  $V_{REF}$  to produce a soft-start characteristic on the PFC: As the reference voltage increases from 0V, it creates a differentiated voltage on  $I_{EAO}$ , which prevents the PFC from immediately demanding a full duty cycle on its boost converter.

## 1.7 PFC Voltage Loop

There are two major concerns when compensating the voltage loop error amplifier (V<sub>FAO</sub>); stability and transient response. Optimizing interaction between transient response and stability requires that the error amplifier's open-loop crossover frequency half that of the line frequency, or 23Hz for a 47Hz line (lowest anticipated international power frequency). The gain vs. input voltage of the FAN4800's voltage error amplifier (V<sub>FAO</sub>) has a specially shaped non-linearity, so that under steady-state operating conditions, the transconductance of the error amplifier is at a local minimum. Rapid perturbation in line or load conditions causes the input to the voltage error amplifier (VFR) to deviate from its 2.5V (nominal) value. If this happens, the transconductance of the voltage error amplifier increases significantly, as shown in the Figure 4. This raises the gain-bandwidth product of the voltage loop, resulting in a much more rapid voltage loop response to such perturbations than would occur with conventional linear gain characteristics.

The voltage loop gain(s) is given by:

$$= \frac{\Delta V_{OUT}}{\Delta V_{EAO}} \times \frac{\Delta V_{FB}}{\Delta V_{OUT}} \times \frac{\Delta V_{EAO}}{\Delta V_{FB}}$$

$$\approx \frac{P_{IN} \times 2.5V}{V_{OUTDC}^2 \times \Delta V_{EAO} \times S \times C_{DC}} \times GM_V \times Z_C$$

(6)

where:

Z<sub>C</sub>: Compensation network for the voltage loop.

$GM_V$ : Transconductance of  $V_{FAO}$ .

P<sub>IN</sub>: Average PFC input power.

V<sup>2</sup><sub>OUTDC</sub>: PFC boost output voltage (typical designed

value is 380V).

C<sub>DC</sub>: PFC boost output capacitor.

### 1.8 PFC Current Loop

The compensation of the current amplifier ( $I_{EAO}$ ) is similar to that of the voltage error amplifier ( $V_{EAO}$ ) with the exception of the choice of crossover frequency. The crossover frequency of the current amplifier should be at least ten times that of the voltage amplifier to prevent interaction with the voltage loop. It should also be limited to less than one sixth of the switching frequency, e.g., 16.7kHz for a 100kHz switching frequency.

The current loop gain(s) is given by:

$$= \frac{\Delta V_{ISENSE}}{\Delta D_{OFF}} \times \frac{\Delta D_{OFF}}{\Delta I_{EAO}} \times \frac{\Delta I_{EAO}}{\Delta V_{ISENSE}}$$

$$\approx \frac{V_{OUTDC} \times R_{S}}{S \times L \times 2.5V} \times GM_{I} \times Z_{CI}$$

(7)

where:

Z<sub>Cl</sub>: Compensation network for the current loop.

GM<sub>I</sub>: Transconductance of I<sub>EAO</sub>.

V<sub>OUTDC</sub>: PFC boost output voltage (typical designed

value is 380V). The equation uses the worst-

case condition to calculate the Z<sub>Cl</sub>.

R<sub>S</sub>: Sensing resistor of the boost converter.

2.5V: Amplitude of the PFC leading modulation

ramp.

L: Boost inductor.

A modest degree of gain contouring is applied to the transfer characteristic of the current error amplifier to increase its response speed to current-loop perturbations. However, the boost inductor is usually the dominant factor in overall current loop response. Therefore, this contouring is significantly less marked than that of the voltage error amplifier. This is illustrated in Figure 8.

Figure 8. Compensation Network Connection for the Voltage and Current Error Amplifiers

There is an RC filter between R<sub>S</sub> and I<sub>SENSE</sub> pin.

There are two reasons to add a filter at the I<sub>SENSE</sub> pin:

- Protection: During startup or in-rush current conditions, there is a large voltage across R<sub>S</sub>, which is the sensing resistor of the PFC boost converter. It requires the I<sub>SENSE</sub> filter to attenuate the energy.

- 2) To reduce L, the boost inductor: The I<sub>SENSE</sub> filter also can reduce the boost inductor value since the I<sub>SENSE</sub> filter behaves like an integrator before the I<sub>SENSE</sub> pin, which is the input of the current error amplifier, I<sub>EAO</sub>.

The I<sub>SENSE</sub> filter is an RC filter. The resistor value of the I<sub>SENSE</sub> filter is between  $100\Omega$  and  $50\Omega$  because I<sub>OFFSET</sub> x R<sub>S</sub> can generate an offset voltage of I<sub>EAO</sub>.

Selecting an  $R_{FILTER}$  equal to  $50\Omega$  keeps the offset of the  $I_{EAO}$  less than 5mV. Design the pole of  $I_{SENSE}$  filter at  $f_{pfc}/6,$  one sixth of the PFC switching frequency, so the boost inductor can be reduced six times without disturbing the stability. The capacitor of the  $I_{SENSE}$  filter,  $C_{FILTER}$ , is approximately 283nF.

Figure 9. External Component Connection to V<sub>CC</sub>

### 1.9 Oscillator (RAMP1)

The oscillator frequency is determined by the values of  $R_T$  and  $C_T$ , which determine the ramp and off-time of the oscillator output clock:

$$f_{\rm OSC} = \frac{1}{t_{RAMP} + t_{DEAD}} \tag{8}$$

The dead time of the oscillator is derived from the following equation:

$$t_{RAMP} = C_T \times R_T \times In \left( \frac{V_{REF} - 1.00}{V_{REF} - 3.75} \right)$$

(9)

at  $V_{REF} = 7.5V$  and  $t_{RAMP} = C_T \times R_T \times 0.55$ .

The dead time of the oscillator may be determined using:

$$t_{DEAD} = \frac{2.75V}{12.11mA} \times C_T = 227 \times C_T \tag{10}$$

The dead time is so small (t<sub>RAMP</sub>>>t<sub>DEAD</sub>) that the operating frequency can typically be approximated by:

$$f_{\rm OSC} = \frac{1}{t_{RAMP}} \tag{11}$$

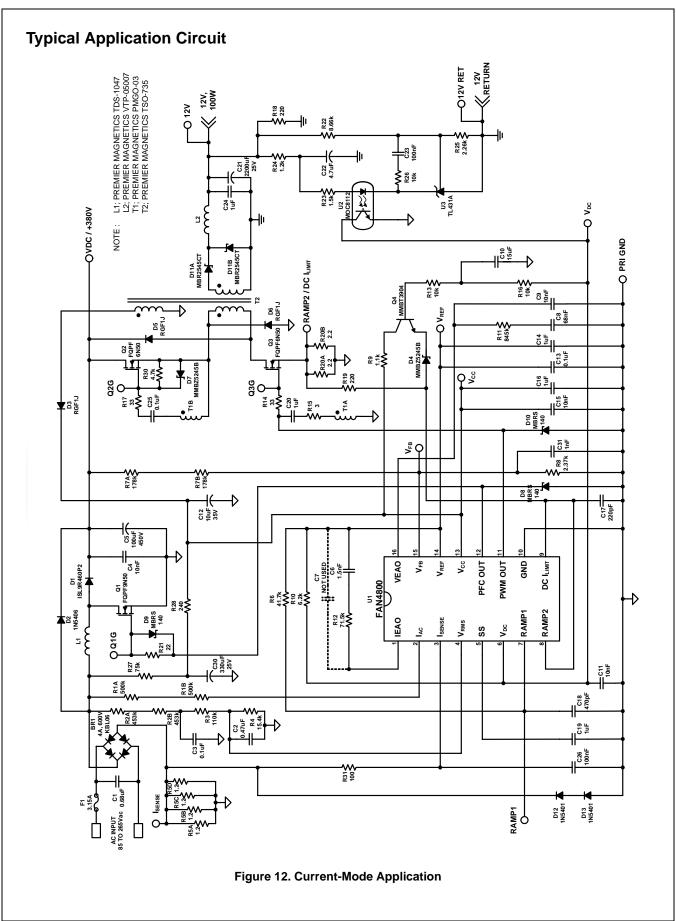

#### 1.10 Example

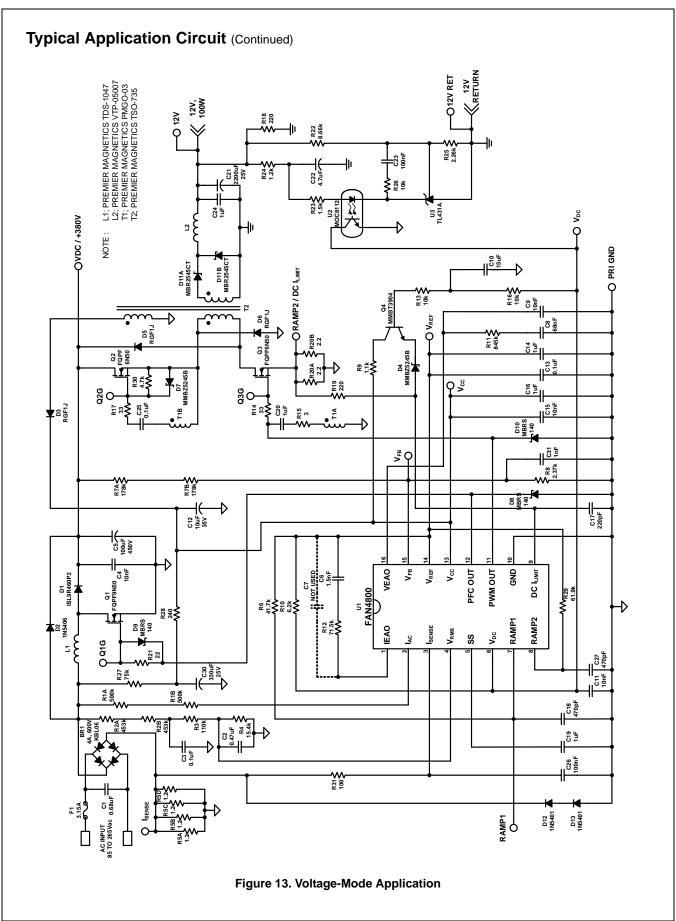

For the application circuit shown in Figures 12 and 13, with the oscillator running at:

$$f_{\rm OSC} = 100kHz = \frac{1}{t_{RAMP}} \tag{12}$$

solving for  $C_T \times R_T$  yields 1.96 x 10<sup>-4</sup>.  $C_T$  is 390pF and  $R_T$  is 51.1k $\Omega$ , selecting standard components values.

The dead time of the oscillator adds to the maximum PWM duty cycle (it is an input to the duty cycle limiter). With zero oscillator dead time, the maximum PWM duty cycle is typically 47%. Take care not to make  $C_T$  too large, which could extend the maximum duty cycle beyond 50%. This can be accomplished by using no greater than a 390pF capacitor for  $C_T$ .

#### 2. PWM Section

### 2.1 Pulse Width Modulator (PWM)

The operation of the PWM section of the FAN4800 is straightforward, but there are several points that should be noted. Foremost among these is the inherent synchronization of PWM with the PFC section of the device, from which it also derives its basic timing. The PWM is capable of current-mode or voltage-mode operation. In current-mode applications, the PWM ramp (RAMP2) is usually derived directly from a current sensing resistor or current transformer in the primary of the output stage. it is thereby representative of the current flowing in the converter's output stage. DC ILIMIT, which provides cycleby-cycle current limiting, is typically connected to RAMP2 in such applications. For voltage-mode operation and certain specialized applications, RAMP2 can be connected to a separate RC timing network to generate a voltage ramp against which V<sub>DC</sub> is compared. Under these conditions, the use of voltage feed-forward from the PFC bus can assist in line regulation accuracy and response. As in current-mode operation, the DC ILIMIT input is used for output stage over-current protection.

No voltage error amplifier is included in the PWM stage of the FAN4800, as this function is generally performed on the output side of the PWM's isolation boundary. To facilitate the design of opto-coupler feedback circuitry, an offset has been built into the PWM's RAMP2 input that allows  $V_{DC}$  to command a 0% duty cycle for input voltages below typical 0.9V.

## 2.2 PWM Current Limit

The DC  $I_{LIMIT}$  pin is a direct input to the cycle-by-cycle current limiter for the PWM section. Should the input voltage at this pin ever exceed 1V, the output flip-flop is reset by the clock pulse at the start of the next PWM power cycle. When the DC  $I_{LIMIT}$  triggers the cycle-by-

cycle current, it also softly discharges the voltage of the soft-start capacitor. It limits the PWM duty cycle mode and the power dissipation is reduced during the dead-short condition.

### 2.3 V<sub>IN</sub> OK Comparator

The  $V_{\text{IN}}$  OK comparator monitors the DC output of the PFC and inhibits the PWM if the voltage on  $V_{\text{FB}}$  is less than its nominal 2.25V. Once the voltage reaches 2.25V, which corresponds to the PFC output capacitor being charged to its rated boost voltage, the soft-start begins.

#### 2.4 PWM Control (RAMP2)

When the PWM section is used in current mode, RAMP2 is generally used as the sampling point for a voltage, representing the current in the primary of the PWM's output transformer. The voltage is derived either from a current sensing resistor or a current transformer. In voltage mode, RAMP2 is the input for a ramp voltage generated by a second set of timing components (R<sub>RAMP2</sub>, C<sub>RAMP2</sub>) that have a minimum value of 0V and a peak value of approximately 5V. In voltage mode, feed forward from the PFC output bus is an excellent way to derive the timing ramp for the PWM stage.

#### 2.5 Soft-Start (SS)

PWM startup is controlled by selection of the external capacitor at soft-start. A current source of 20mA supplies the charging current for the capacitor and startup of the PWM begins at 0.9V. Startup delay can be programmed by the following equation:

$$C_{SS} = t_{DELAY} \times \frac{20\mu A}{0.9V} \tag{13}$$

where  $C_{SS}$  is the required soft-start capacitance and the  $t_{DELAY}$  is the desired startup delay.

It is important that the time constant of the PWM softstart allows the PFC time to generate sufficient output power for the PWM section. The PWM startup delay should be at least 5ms.

Solving for the minimum value of C<sub>SS</sub>:

$$C_{SS} = 5ms \times \frac{20\mu A}{0.9V} = 111nF$$

(14)

Use caution when using this minimum soft-start capacitance value because it can cause premature charging of the SS capacitor and activation of the PWM section if  $V_{FB}$  is in the hysteresis band of the  $V_{IN}$  OK comparator at startup. The magnitude of  $V_{FB}$  at startup is related both to line voltage and nominal PFC output voltage. Typically, a 1.0µF soft-start capacitor allows time for  $V_{FB}$  and PFC<sub>OUT</sub> to reach their nominal values prior to activation of the PWM section at line voltages between 90Vrms and 265Vrms.

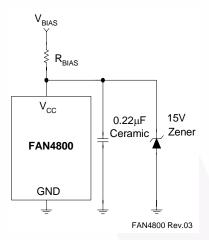

### 2.6 Generating V<sub>CC</sub>

After turning on the FAN4800 at 13V, the operating voltage can vary from 10V to 17.9V. The threshold voltage of the  $V_{CC}$  OVP comparator is 17.9V and its hysteresis is 1.5V. When  $V_{CC}$  reaches 17.9V, PFC OUT is LOW, and the PWM section is not disturbed. There are two ways to generate  $V_{CC}$ : use auxiliary power supply around 15V or use bootstrap winding to self-bias the FAN4800 system. The bootstrap winding can be either taped from the PFC boost choke or from the transformer of the DC-to-DC stage.

The ratio of the bootstrap's winding transformer should be set between 18V and 15V. A filter network is recommended between  $V_{\rm CC}$  (pin 13) and bootstrap winding. The resistor of the filter can be set as:

$$R_{FILTER} \times I_{VCC} \approx 2V,$$

$I_{VCC} = I_{OP} + (Q_{PFCFET} + Q_{PWMFET}) \times f_{SW} I_{OP}$

$= 2.5A \ (typ.)$  (15)

If  $V_{CC}$  goes beyond 17.9V, the PFC gate (pin 12) drive goes LOW and the PWM gate drive (pin 11) remains working. The resistor's value must be chosen to meet the operating current requirement of the FAN4800 itself (5mA, maximum) in addition to the current required by the two gate driver outputs.

#### 2.7 Example

To obtain a desired  $V_{BIAS}$  voltage of 18V, a  $V_{CC}$  of 15V, and the FAN4800 driving a total gate charge of 90nC at 100kHz (e.g. one IRF840 MOSFET and two IRF820 MOSFET), the gate driver current required is:

$$I_{GATEDRIVE} = 100kHz \times 90nC = 9mA \tag{16}$$

$$R_{BIAS} = \frac{V_{BIAS} - V_{CC}}{I_{CC} + I_{G}}$$

$$= \frac{18V - 15V}{5mA + 9mA}$$

(17)

Choose

$$R_{BIAS} = 214\Omega$$

(18)

Bypass the FAN4800 locally with a  $1.0\mu F$  ceramic capacitor. In most applications, an electrolytic capacitor of between  $47\mu F$  and  $220\mu F$  is also required across the part both for filtering and as a part of the startup bootstrap circuitry.

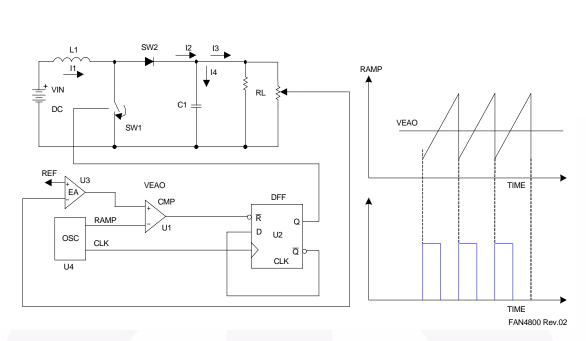

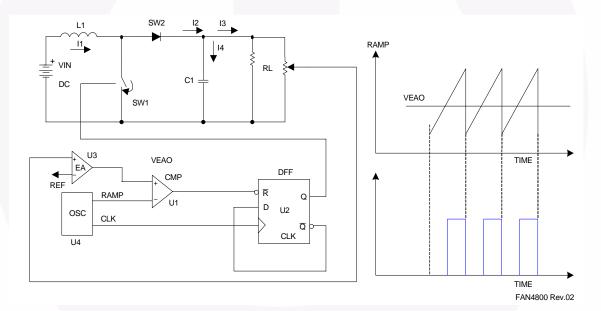

### 2.8 Leading/Trailing Modulation

Conventional PWM techniques employ trailing-edge modulation, in which the switch turns on right after the trailing edge of the system clock. The error amplifier output is then compared with the modulating ramp up. The effective duty cycle of the trailing edge modulation is determined during the on-time of the switch. Figure 10 shows a typical trailing-edge control scheme.

In the case of leading-edge modulation, the switch is turned off exactly at the leading edge of the system clock. When the modulating ramp reaches the level of the error amplifier output voltage, the switch is turned on. The effective duty-cycle of the leading-edge modulation is determined during off-time of the switch. Figure 11 shows a leading-edge control scheme.

One of the advantages of this control technique is that it requires only one system clock. Switch 1 (SW1) turns off and Switch 2 (SW2) turns on at the same instant to minimize the momentary no-load period, thus lowering ripple voltage generated by the switching action. With such synchronized switching, the ripple voltage of the first stage is reduced. Calculation and evaluation have shown that the 120Hz component of the PFC's output ripple voltage can be reduced by as much as 30% using the leading-edge modulation method.

Figure 10. Typical Trailing-Edge Control Scheme

Figure 11. Typical Leading-Edge Control Scheme

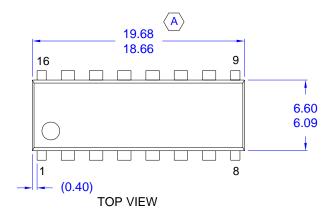

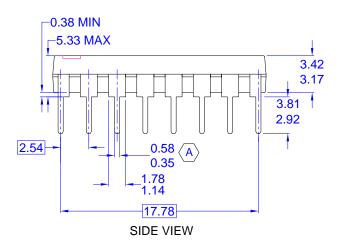

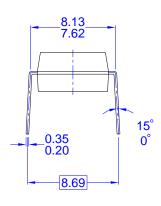

## **Physical Dimensions**

NOTES: UNLESS OTHERWISE SPECIFIED

- A)THIS PACKAGE CONFORMS TO JEDEC MS-001 VARIATION BB

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR PROTRUSIONS

- D) CONFORMS TO ASME Y14.5M-1994

- E) DRAWING FILE NAME: N16EREV1

Figure 14. 16-Lead Plastic Dual In-Line Package (DIP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ Auto-SPM™ Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT\*\* CTL™ Current Transfer Logic™ DEUXPEED<sup>®</sup>

Green FPS™ e-Series™ Gmax™ GTO™ IntelliMAX™ ISOPLANAR™ Dual Cool™ MegaBuck™ EcoSPARK® MICROCOUPLER™ EfficientMa×™ MicmEET™ ESBC™ MicroPak™ MicroPak2™ MillerDri∨e™ Fairchild® MotionMa×™ Fairchild Semiconductor® Motion-SPM™ FACT Quiet Series™ OptoHiT™ FACT OPTOLOGIC® FAST® OPTOPLANAR® Fast∨Core™

E-PES™

Green FPS™

Global Power Resourcesu

FRFFT

PowerTrench<sup>®</sup> PowerXS™ Programmable Active Droop™

QFET QS™

Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™ SPM® STEALTH™ SuperFET<sup>6</sup> SuperSOT\*\*3 SuperSOT™6 SuperSOT™8 SupreMOS® SyncFET™ Sync-Lock™ SYSTEM GENERAL®

The Power Franchise® The Right Technology for Your Success™

TinyBoost™

TinýBuck™ TinyCalc™ TinyLogic<sup>6</sup> TINYOPTO\*\* TinyPower™ TinyPWM™ TinyWire™ TriFault Detect™ TRUECURRENT"\* μSerDes™

LIHO Ultra FRFET™ UniFET™ VCX™ VisualMax™ XSTM

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor

PDP SPM™

Power-SPM™

#### DISCLAIMER

FETBench™

FlashVVriter®\*

**FPST**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HERBIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS, THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS. SPECIFICALLY THE WARRANTY THEREIN. WHICH COVERS THESE PRODUCTS

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit, parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Definition of Terms                                                                                                                                                                    |                   |                                                                                                                                                                                                        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Datasheet Identification                                                                                                                                                               | Product Status    | Definition                                                                                                                                                                                             |  |  |

| Advance Information Formative / In Design Datasheet contains the design specifications for product development. Specifications may any manner without notice.                          |                   | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |  |  |

|                                                                                                                                                                                        |                   | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed Full Production Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make at any time without notice to improve the design. |                   | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                                  |  |  |

| Obsolete                                                                                                                                                                               | Not In Production | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |  |  |

Rev. 151