January 2008

# FAN2013 — 2A Low-Voltage, Current-Mode Synchronous PWM Buck Regulator

# Features

- 95% Efficiency, Synchronous Operation

- Adjustable Output Voltage from 0.8V to V<sub>IN</sub>-1

- 4.5V to 5.5V Input Voltage Range

- Up to 2A Output Current

- Fixed-Frequency 1.3 MHz PWM Operation

- 100% Duty Cycle Low-Dropout Operation (LDO)

- Soft-Start Function

- Excellent Load Transient Response

- Power-Good Flag

- Over-Voltage, Under-Voltage Lockout, Short-Circuit, and Thermal Shutdown Protections

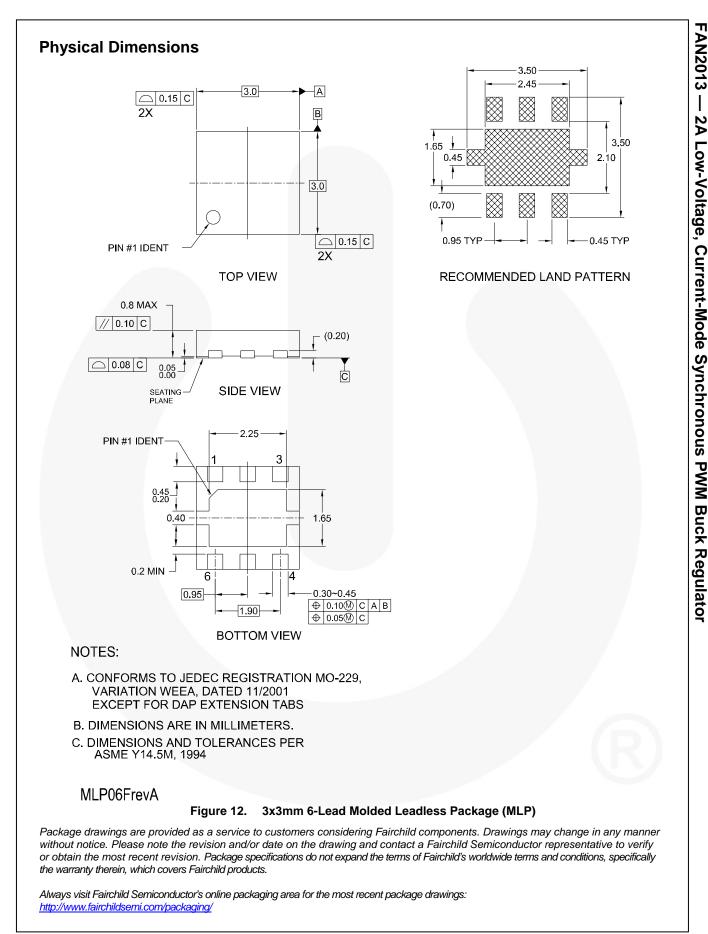

- 3x3mm 6-lead MLP Package

# Applications

- Hard Disk Drive

- Set-Top Box

- Point-of-Load Power

- Notebook Computer

- Communications Equipment

# Description

The FAN2013 is a high-efficiency, low-noise, synchronous Pulse Width Modulated (PWM) currentmode DC-DC converter designed for low-voltage applications. It provides up to 2A continuous-load current from the 4.5V to 5.5V input. The output voltage is adjustable over a wide range by means of an external voltage divider.

The FAN2013 is enabled when the input voltage on the  $V_{\text{IN}}$  pin exceed the UVLO threshold.

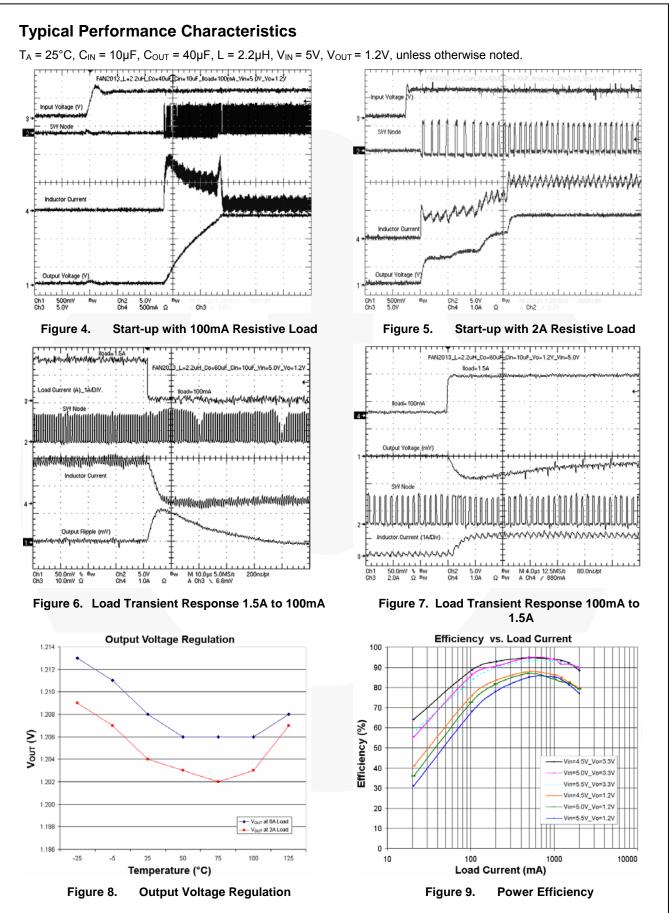

A current-mode control loop with a fast transient response ensures excellent line and load regulation. The fixed 1.3MHz switching frequency enables designers to choose a small, inexpensive external inductor and capacitor. Filtering can be accomplished with small components, reducing space and cost.

Protection features include input under-voltage lockout, short-circuit protection, and thermal shutdown. Soft-start limits inrush current during start-up conditions.

The device is available in a 3x3mm 6-lead MLP.

# **Ordering Information**

| Part Number                                               | Number Output Voltage Package |                                            | Packing Method |  |

|-----------------------------------------------------------|-------------------------------|--------------------------------------------|----------------|--|

| FAN2013MPX                                                | 0.8V to $V_{IN}$ -1V          | 3x3mm 6-Lead Molded Leadless Package (MLP) | Tape and Reel  |  |

| All packages are lead free per JEDEC: J-STD-020B standard |                               |                                            |                |  |

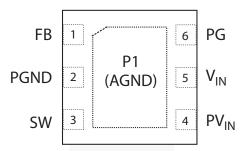

# **Pin Assignments**

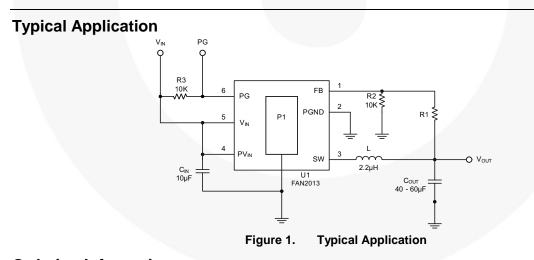

Figure 2. Pin Assignments (Top View)

# **Pin Definitions**

| Pin # | Name | Description                                                                                                                 |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------|

| P1    | AGND | Analog Ground. P1 must be soldered to the PCB ground.                                                                       |

| 1     | FB   | Feedback Input. Adjustable voltage option; connect this pin to the resistor divider.                                        |

| 2     | PGND | <b>Power Ground</b> . This pin is connected to the internal MOSFET switches. This pin must be externally connected to AGND. |

| 3     | SW   | Switching Node. This pin is connected to the internal MOSFET switches.                                                      |

| 4     | PVIN | Supply Voltage Input. This pin is connected to the internal MOSFET switches.                                                |

| 5     | VIN  | Supply Voltage Input.                                                                                                       |

| 6     | PG   | Open Drain Power Good.                                                                                                      |

FAN2013 — 2A Low-Voltage, Current-Mode Synchronous PWM Buck Regulator

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                               |     | Min. | Max.            | Unit |

|------------------|---------------------------------------------------------|-----|------|-----------------|------|

| V <sub>IN</sub>  | Supply Voltage                                          |     | -0.3 | 6.2             | V    |

|                  | Input Voltage on PVIN and Any Other Pin                 |     | -0.3 | V <sub>IN</sub> | V    |

| $\theta_{JC}$    | Thermal Resistance, Junction-to-Tab <sup>(1)</sup>      |     |      | 8               | °C/W |

| TL               | Lead Soldering Temperature (10 Seconds)                 |     |      | 260             | °C   |

| T <sub>STG</sub> | Storage Temperature                                     |     | -65  | 150             | °C   |

| TJ               | Junction Temperature                                    |     | -40  | 150             | °C   |

| ESD              | Electrostatic Discharge Protection Level <sup>(2)</sup> | HBM | 3.5  |                 | kV   |

| L3D              |                                                         | CDM | 2    |                 | ΓV.  |

Notes:

Junction-to-ambient thermal resistance, θ<sub>JA</sub>, is a strong function of PCB material, board thickness, thickness and number of copper planes, number of via used, diameter of via used, available copper surface, and attached heat sink characteristics.

2. Using Mil Std. 883E, method 3015.7 (Human Body Model) and EIA/JESD22C101-A (Charged Device Model).

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbols         | Parameter                                | Min. | Тур. | Max.               | Unit |

|-----------------|------------------------------------------|------|------|--------------------|------|

| V <sub>IN</sub> | Supply Voltage Range                     | 4.5  |      | 5.5                | V    |

| Vout            | Output Voltage Range, Adjustable Version | 0.8  |      | V <sub>IN</sub> -1 | V    |

| IOUT            | Output Current                           |      |      | 2.0                | А    |

| L               | Inductor <sup>(3)</sup>                  |      | 2.2  |                    | μH   |

| CIN             | Input Capacitor <sup>(3)</sup>           | 10   | 20   |                    | μF   |

| COUT            | Output Capacitor <sup>(3)</sup>          | 20   | 40   |                    | μF   |

| T <sub>A</sub>  | Operating Ambient Temperature Range      | -40  |      | +85                | °C   |

Note:

3. Refer to the Applications section for details.

# **Electrical Characteristics**

$V_{IN}$  = 4.5V to 5.5V,  $V_{OUT}$  = 1.2V,  $I_{OUT}$  = 200mA,  $C_{IN}$  = 10µF,  $C_{OUT}$  = 40µF, L = 2.2µH,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = 25°C.

| Symbol                     | Parameter                           | ter Conditions                                                                                                                                                                                                            |      | Тур.                   | Max. | Units |

|----------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|-------|

| VIN                        | Input Voltage                       |                                                                                                                                                                                                                           |      |                        | 5.5  | V     |

| l <sub>Q</sub>             | Quiescent Current                   | I <sub>OUT</sub> = 0mA                                                                                                                                                                                                    |      | 10                     | 16   | mA    |

| N/                         |                                     | V <sub>IN</sub> Rising                                                                                                                                                                                                    | 3.4  | 3.7                    | 4.0  | V     |

| V <sub>UVLO</sub>          | UVLO Threshold                      | Hysteresis                                                                                                                                                                                                                |      | 150                    |      | mV    |

| R <sub>ON_PMOS</sub>       | PMOS On Resistance                  | $V_{IN} = V_{GS} = 5V$                                                                                                                                                                                                    |      | 90                     |      | MΩ    |

| Ron_nmos                   | NMOS On Resistance                  | V <sub>IN</sub> = V <sub>GS</sub> = 5V                                                                                                                                                                                    |      | 90                     |      | mΩ    |

| I <sub>LIMIT</sub>         | P-Channel Current Limit             | 4.5V < V <sub>IN</sub> < 5.5V                                                                                                                                                                                             | 2.8  | 3.5                    | 4.2  | Α     |

| <b>т</b>                   | Quer Terreture Drotestion           | Rising Temperature                                                                                                                                                                                                        |      | 150                    |      | °C    |

| T <sub>OVP</sub>           | Over-Temperature Protection         | Hysteresis                                                                                                                                                                                                                |      | 20                     |      | °C    |

| f <sub>SW</sub>            | Switching Frequency                 |                                                                                                                                                                                                                           | 1000 | 1300                   | 1600 | kHz   |

| R <sub>LINE</sub>          | Line Regulation                     | $V_{IN}$ = 4.5 to 5.5V, $I_{OUT}$ = 100mA                                                                                                                                                                                 |      | 0.16                   |      | %/V   |

| RLOAD                      | Load Regulation                     | $0mA \le I_{OUT} \le 2000mA$                                                                                                                                                                                              |      | 0.2                    | 0.6  | %     |

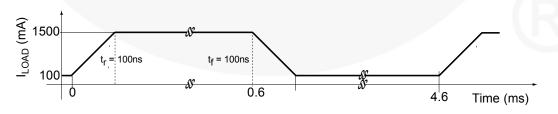

| V <sub>OUT</sub> Ou<br>Tra | Output Voltage During Load          | $I_{OUT}$ from 1500mA to 100mA,<br>$C_{OUT} = 60 \mu F$                                                                                                                                                                   |      |                        | 5    | %     |

|                            | Transition <sup>(4)</sup>           | $I_{OUT}$ from 100mA to 1500mA,<br>$C_{OUT} = 60 \mu F$                                                                                                                                                                   | -5   |                        |      | %     |

| I <sub>LEAK</sub>          | Reverse Leakage Current into Pin SW | $V_{IN}$ = Open, EN = GND, $V_{SW}$ = 5.5V                                                                                                                                                                                |      | 0.1                    | 1.0  | μA    |

| V <sub>REF</sub>           | Reference Voltage                   |                                                                                                                                                                                                                           |      | 0.8                    |      | V     |

|                            |                                     | $\label{eq:VIN} \begin{array}{l} V_{\text{IN}} = 4.5 \text{ to } 5.5 \text{V}, 0 \text{mA} \leq I_{\text{OUT}} \\ \leq 2000 \text{mA}, \ T_{\text{A}} = 0^{\circ} \text{C} \ \text{to} + 85^{\circ} \text{C} \end{array}$ | -2   |                        | 2    | %     |

| V <sub>OUT</sub> Outp      | Output Voltage Accuracy             | $V_{IN}$ = 4.5 to 5.5V, 0mA $\leq I_{OUT}$<br>$\leq$ 2000mA, T <sub>A</sub> = -40°C to +85°C                                                                                                                              | -3   |                        | 3    | %     |

|                            | Power Good Output                   | FB Voltage Rising                                                                                                                                                                                                         |      | 0.85 xV <sub>оит</sub> |      | %     |

|                            | Threshold and Hysteresis            | Hysteresis                                                                                                                                                                                                                |      | 2                      |      | V     |

| t <sub>PG</sub>            | Power Good Output Delay             |                                                                                                                                                                                                                           |      | 100                    |      | μs    |

| V <sub>PG_LOW</sub>        | Power Good Voltage Low              | I <sub>sink</sub> =6mA, Open-Drain Output                                                                                                                                                                                 |      |                        | 0.4  | V     |

| Vara                       | Over-Voltage Protection             | FB Voltage Rising                                                                                                                                                                                                         |      | 1.07 xV <sub>OUT</sub> |      | V     |

|                            | Threshold and Hysteresis            | Hysteresis                                                                                                                                                                                                                |      | 2                      |      | %     |

#### Notes:

4. Please refer to the load transient response test waveform shown in Figure 3.

Figure 3. Load Transient Response Test Waveform

© 2006 Fairchild Semiconductor Corporation FAN2013 Rev. 1.0.3

www.fairchildsemi.com

П

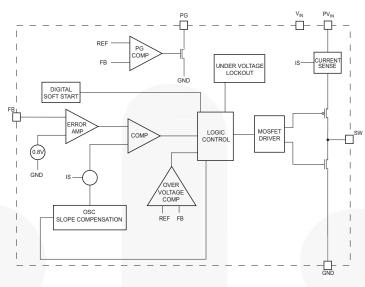

## **Block Diagram**

Figure 10. Block Diagram

# **Detailed Operation Description**

The FAN2013 is a step-down pulse-width modulated (PWM) current mode converter with a fixed switching frequency of 1.3MHz. At the rising edge of each clock cycle, the P-channel transistor is turned on until the PWM comparator trips or the current limit is reached. During the ON time, the inductor current ramps up and is monitored by the internal current-mode control loop. After a minimum dead time, the N-channel transistor is turned ON and the inductor current ramps down. As the clock cycle is completed, the N-channel switch is turned OFF and the next clock cycle starts. The duty cycle is given by the ratio of output voltage and input voltage. The converter runs at minimum duty cycle when output voltage is at minimum and input voltage is at maximum, and at 100% duty cycle when the input voltage approaches the output voltage, as described below.

## 100% Duty Cycle Operation

As the input voltage approaches the output voltage and the duty cycle exceeds the typical 95%, the converter turns the P-channel transistor continuously on. In this mode, the output voltage is equal to the input voltage, minus the voltage drop across the P-channel transistor:

$$V_{OUT} = V_{IN} - I_{LOAD} \times (R_{DS_{ON}} + R_{L})$$

where  $R_{DS_ON}$  = P-channel switch on resistance  $I_{LOAD}$  = Output current

R<sub>L</sub> = Inductor DC resistance

## **UVLO and Soft Start**

The internal voltage reference,  $V_{\text{REF}},$  and the IC remain reset until  $V_{\text{IN}}$  reaches the 3.7V UVLO threshold.

The FAN2013 has an internal soft-start circuit that limits the inrush current during start-up. This prevents possible voltage drops of the input voltage and eliminates the output voltage overshoot. The soft-start is implemented as a digital circuit, increasing the switch current in four steps to the P-channel current limit (3.5A). Typical start-up time for a 40 $\mu$ F output capacitor with a load current of 2.0A is 800 $\mu$ s.

## **Output Over-Voltage Protection**

When output voltage,  $V_{OUT}$ , reaches approximately 7% above the nominal value, the device turns OFF the Pchannel switch and turns ON part of the N-channel transistor with a built-in current limit of about 400mA. When  $V_{OUT}$  reaches the hysteresis of about 2%, the device starts switching normally in closed loop. If output voltage is pulled up by an external voltage source with a current limit higher than typical 400mA, the output voltage stays up at the external voltage source level.

The over-voltage protection is designed to limit the output voltage excursion in case of a transient response from full load to a minimum load.

# **Output Short-Circuit Protection**

The switch peak current is limited cycle by cycle to a typical value of 3.5A. In the event of an output voltage short circuit, the device operates with a frequency of 400kHz and minimum duty cycle, making the average typical input current .45A.

#### **Thermal Shutdown**

When the die temperature exceeds  $150^{\circ}$ C, a reset occurs and remains in effect until the die cools to  $130^{\circ}$ C, when the circuit is allowed to restart.

(1)

# **Applications Information**

#### Setting the Output Voltage

The internal voltage reference is 0.8V. The output is divided down by a voltage divider, R1 and R2 to the FB pin. The output voltage is:

$$V_{OUT} = V_{REF} \left( 1 + \frac{R_1}{R_2} \right)$$

(2)

According to this equation, assuming desired output voltage of 1.2V, and given R2 =  $10K\Omega$  as the recommended resistance for any output voltage setting, the calculated value of R1 is  $5K\Omega$ .

#### **Inductor Selection**

The inductor parameters directly related to device performance are saturation current and DC resistance. The FAN2013 operates with a typical inductor value of  $2.2\mu$ H. The lower the DC resistance, the higher the efficiency. For saturation current, the inductor should be rated higher than the maximum load current, plus half of the inductor ripple current, calculated by:

$$\Delta I_{L} = V_{OUT} \times \frac{1 - (V_{OUT} / V_{IN})}{I \times f}$$

(3)

where:

$\Delta I_L$  = Inductor Ripple Current f = Switching Frequency L = Inductor Value

Recommended inductors are listed in Table1.

#### Table 1. Recommended Inductors

| Inductor<br>Value | Vendor      | Part Number    |

|-------------------|-------------|----------------|

| 2.2µH             | Coiltronics | SD25 2R2       |

| 2.2µH             | Murata      | LQH66SSN2R2M03 |

## **Capacitors Selection**

For best performances, a low-ESR input capacitor is required. A ceramic capacitor of at least  $10\mu F,$  placed as close to the  $V_{IN}$  and AGND pins as possible is recommended.

The output capacitor determines the output ripple and the transient response. A minimum of  $20\mu F$  output capacitor is required for the FAN2013 to operate in stable conditions.

| Table 2 | 2. | Recommended | Capacitors |

|---------|----|-------------|------------|

|---------|----|-------------|------------|

| Capacitor<br>Value | Vendor      | Part Number    |

|--------------------|-------------|----------------|

|                    |             | JMK212BJ106MG  |

|                    | Taiyo Yuden | JMK316BJ106KL  |

| 10µF               | ТДК         | C2012X5ROJ106K |

|                    | TDR         | C3216X5ROJ106M |

|                    | Murata      | GRM32ER61C106K |

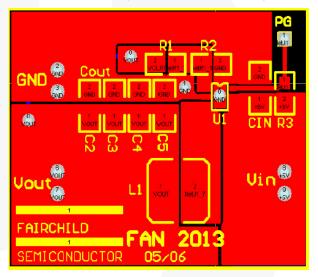

#### **PCB Layout Recommendations**

The inherently high peak currents and switching frequency of power supplies require a careful PCB layout design. For best results, use wide traces for highcurrent paths and place the input capacitor, the inductor, and the output capacitor as close as possible to the integrated circuit terminals. To minimize voltage stress to the device resulting from ever-present switching spikes, use an input bypass capacitor with low ESR. Note that the peak amplitude of the switching spikes depends upon the load current; the higher the load current, the higher the switching spikes.

The resistor divider that sets the output voltage should be routed away from the inductor to avoid RF coupling. The ground plane at the bottom side of the PCB acts as an electromagnetic shield to reduce EMI. The recommended PCB layout is shown below in Figure 11.

Figure 11. Recommended PCB Layout

П

AN2013

I

2A Low-Voltage, Current-Mode Synchronous PWM Buck Regulator

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

| ACEX®                |     |

|----------------------|-----|

| Build it Now™        |     |

| CorePLUS™            |     |

| CROSSVOLT™           |     |

| CTL™                 |     |

| Current Transfer Log | ic™ |

| EcoSPARK®            |     |

| E7SWITCHIM *         |     |

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT<sup>®</sup> FAST® FastvCore™ FlashWriter<sup>®\*</sup>

FRFET® Global Power Resource<sup>sm</sup> Green FPS™ Green FPS™e-Series™ **GTO™** i-Lo™ IntelliMAX™ ISOPLANAR™ MegaBuck™ MICROCOUPLER™ MicroFET™ MicroPak™ MillerDrive™ Motion-SPM™ OPTOLOGIC<sup>®</sup> OPTOPLANAR<sup>®</sup>

FPS™

PDP-SPM™ Power220<sup>®</sup> POWEREDGE<sup>®</sup> Power-SPM<sup>™</sup> PowerTrench® Programmable Active Droop™ QFET<sup>®</sup> QS™ QT Optoelectronics™ Quiet Series™ RapidConfigure™ SMART START™ SPM<sup>®</sup> STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6 SuperSOT™-8

SupreMOS™ SyncFET™ GENERAL The Power Franchise® p wer TinyBoost™ TinyBuck™ TinyLogic® TINYOPTO™ TinvPower™ TinyPWM™ TinyWire™ µSerDes™ и́нс® Ultra FRFET™ UniFET™

VСХ™

\* EZSWITCH™ and FlashWriter<sup>®</sup> are trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS, THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

PRODUCT STATUS DEFINITIONS

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein

- 1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support, which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| Definition of Terms      |                        |                                                                                                                                                                                                                |  |  |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                                     |  |  |

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                             |  |  |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be<br>published at a later date. Fairchild Semiconductor reserves the right to<br>make changes at any time without notice to improve design. |  |  |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                                     |  |  |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for                                                                        |  |  |

Rev. 133

reference information only