August 1986 Revised April 2000

#### DM74S74

# **Dual Positive-Edge-Triggered D Flip-Flops** with Preset, Clear, and Complementary Outputs

#### **General Description**

This device contains two independent positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock. The data on the D input may be changed while the clock is LOW or HIGH without affecting the outputs as long as setup and hold times are not violated. A low logic level on the preset or clear inputs will set or reset the outputs regardless of the logic levels of the other inputs.

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |  |  |  |  |

|--------------|----------------|-----------------------------------------------------------------------------|--|--|--|--|

| DM74S74M     | M14A           | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |  |  |  |  |

| DM74S74N     | N14A           | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |  |  |  |  |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

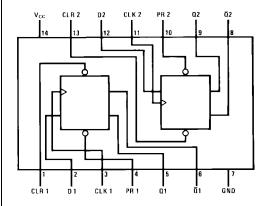

### **Connection Diagram**

## **Function Table**

|    | Inpu | ıts |   | Out   | puts             |

|----|------|-----|---|-------|------------------|

| PR | CLR  | CLK | D | Q     | Q                |

| L  | Н    | Х   | Х | Н     | L                |

| Н  | L    | Х   | Χ | L     | Н                |

| L  | L    | Х   | Χ | H*    | H*               |

| Н  | Н    | 1   | Н | Н     | L                |

| Н  | Н    | 1   | L | L     | Н                |

| Н  | Н    | L   | Х | $Q_0$ | $\overline{Q}_0$ |

- H = HIGH Logic Level X = Either LOW or HIGH Logic Level

- L = LOW Logic Level

- ↑ = Positive-going Transition

\* = This configuration is nonstable; that is, it will not persist when either the preset and/or clear inputs return to its inactive (HIGH) level.

- $\mathbf{Q}_0 = \mathsf{The}$  output logic level of  $\mathbf{Q}$  before the indicated input conditions were

# Absolute Maximum Ratings(Note 1)

Supply Voltage 7V Input Voltage 5.5V Operating Free Air Temperature Range  $0^{\circ}\text{C to } +70^{\circ}\text{C}$  Storage Temperature Range  $-65^{\circ}\text{C to } +150^{\circ}\text{C}$

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# **Recommended Operating Conditions**

| Symbol           | Parameter                        |                                  | Min  | Nom | Max  | Units |

|------------------|----------------------------------|----------------------------------|------|-----|------|-------|

| V <sub>CC</sub>  | Supply Voltage                   |                                  | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub>  | HIGH Level Input V               | HIGH Level Input Voltage         |      |     |      | V     |

| V <sub>IL</sub>  | LOW Level Input V                | LOW Level Input Voltage          |      |     | 0.8  | V     |

| Гон              | HIGH Level Output                | Current                          |      |     | -1   | mA    |

| I <sub>OL</sub>  | LOW Level Output                 | Current                          |      |     | 20   | mA    |

| f <sub>CLK</sub> | Clock Frequency (N               | Note 2)                          | 0    | 110 | 75   | MHz   |

| f <sub>CLK</sub> | Clock Frequency (N               | Note 3)                          | 0    | 95  | 65   | MHz   |

| t <sub>W</sub>   | Pulse Width                      | Clock HIGH                       | 6    |     |      |       |

|                  | (Note 2)                         | Clock LOW                        | 7.3  |     |      | ns    |

|                  |                                  | Clear LOW                        | 7    |     |      | 115   |

|                  |                                  | Preset LOW                       | 7    |     |      |       |

| t <sub>W</sub>   | Pulse Width                      | Clock HIGH                       | 8    |     |      |       |

|                  | (Note 3)                         | Clock LOW                        | 9    |     |      | ns    |

|                  |                                  | Clear LOW                        | 9    |     |      | 115   |

|                  |                                  | Preset LOW                       | 9    |     |      |       |

| t <sub>SU</sub>  | Setup Time (Note 2               | 2)(Note 4)                       | 3↑   |     |      | ns    |

| t <sub>SU</sub>  | Setup Time (Note 3)(Note 4)      |                                  | 3↑   |     |      | ns    |

| t <sub>H</sub>   | Input Hold Time (Note 2)(Note 4) |                                  | 2↑   |     |      | ns    |

| t <sub>H</sub>   | Input Hold Time (N               | Input Hold Time (Note 3)(Note 4) |      |     |      | ns    |

| T <sub>A</sub>   | Free Air Operating               | Free Air Operating Temperature   |      |     | 70   | °C    |

Note 2:  $C_L = 15$  pF,  $R_L = 280\Omega$ ,  $T_A = 25$ °C and  $V_{CC} = 5V$ .

**Note 3:**  $C_L = 50$  pF,  $R_L = 280\Omega$ ,  $T_A = 25$ °C and  $V_{CC} = 5V$ .

Note 4: The symbol  $(\hat{1})$  indicates the rising edge at the clock pulse is used for reference.

#### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                         | Conditions                                   |        | Min | Typ<br>(Note 5) | Max  | Units |

|-----------------|-----------------------------------|----------------------------------------------|--------|-----|-----------------|------|-------|

| VI              | Input Clamp Voltage               | $V_{CC} = Min, I_I = -18 \text{ mA}$         |        |     |                 | -1.2 | V     |

| V <sub>OH</sub> | HIGH Level                        | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max |        | 2.7 | 3.4             |      | V     |

|                 | Output Voltage                    | $V_{IL} = Max, V_{IH} = Min$                 |        | 2.1 | 5.4             |      | V     |

| V <sub>OL</sub> | LOW Level                         | V <sub>CC</sub> = Min, I <sub>OL</sub> = Max |        |     |                 | 0.5  | V     |

|                 | Output Voltage                    | $V_{IH} = Min, V_{IL} = Max$                 |        |     |                 | 0.5  | V     |

| I <sub>I</sub>  | Input Current @ Max Input Voltage | $V_{CC} = Max, V_I = 5.5V$                   |        |     |                 | 1    | mA    |

| I <sub>IH</sub> | HIGH Level                        | V <sub>CC</sub> = Max                        | D      |     |                 | 50   |       |

|                 | Input Current                     | $V_I = 2.7V$                                 | Clear  |     |                 | 150  | μА    |

|                 |                                   |                                              | Preset |     |                 | 100  | μΛ    |

|                 |                                   |                                              | Clock  |     |                 | 100  |       |

| I <sub>IL</sub> | LOW Level                         | V <sub>CC</sub> = Max                        | D      |     |                 | -2   |       |

|                 | Input Current                     | $V_I = 0.5V$                                 | Clear  |     |                 | -6   | mA    |

|                 |                                   | (Note 6)                                     | Preset |     |                 | -4   | IIIA  |

|                 |                                   |                                              | Clock  |     |                 | -4   |       |

| Ios             | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 7)               |        | -40 |                 | -100 | mA    |

| I <sub>CC</sub> | Supply Current                    | V <sub>CC</sub> = Max, (Note 8)              | •      |     | 30              | 50   | mA    |

Note 5: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 6: Clear is tested with preset HIGH and preset is tested with clear HIGH.

Note 7: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 8: With all outputs OPEN,  $I_{CC}$  is measured with the Q and  $\overline{Q}$  outputs HIGH in turn. At the time of measurement, the clock is grounded.

# **Switching Characteristics**

at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

|                  | Parameter                |                             |                        | $R_L = 280\Omega$ |                        |     |       |

|------------------|--------------------------|-----------------------------|------------------------|-------------------|------------------------|-----|-------|

| Symbol           |                          | From (Input)<br>To (Output) | C <sub>L</sub> = 15 pF |                   | C <sub>L</sub> = 50 pF |     | Units |

|                  |                          |                             | Min                    | Max               | Min                    | Max | 1     |

| f <sub>MAX</sub> | Maximum Clock Frequency  |                             | 75                     |                   | 65                     |     | MHz   |

| t <sub>PLH</sub> | Propagation Delay Time   | Preset to Q                 |                        | 6                 |                        | 9   | ns    |

|                  | LOW-to-HIGH Level Output | Flesel to Q                 |                        | 0                 |                        |     |       |

| t <sub>PLH</sub> | Propagation Delay Time   | Clear to Q                  |                        | 6                 |                        | 9   | ns    |

|                  | LOW-to-HIGH Level Output | Clear to Q                  |                        | 0                 |                        |     |       |

| t <sub>PHL</sub> | Propagation Delay Time   | Preset to Q                 |                        |                   |                        | 17  | ns    |

|                  | HIGH-to-LOW Level Output |                             |                        | 13.5              |                        |     |       |

|                  | (Clock HIGH)             |                             |                        |                   |                        |     |       |

| t <sub>PHL</sub> | Propagation Delay Time   | Preset to Q                 |                        | 8                 |                        | 14  | ns    |

|                  | HIGH-to-LOW Level Output |                             |                        |                   |                        |     |       |

|                  | (Clock LOW)              |                             |                        |                   |                        |     |       |

| t <sub>PHL</sub> | Propagation Delay Time   |                             |                        |                   |                        |     |       |

|                  | HIGH-to-LOW Level Output | Clear to Q                  |                        | 13.5              |                        | 16  | ns    |

|                  | (Clock HIGH)             |                             |                        |                   |                        |     |       |

| t <sub>PHL</sub> | Propagation Delay Time   | Clear to Q                  |                        | 8                 |                        |     | ns    |

|                  | HIGH-to-LOW Level Output |                             |                        |                   |                        | 13  |       |

|                  | (Clock LOW)              |                             |                        |                   |                        |     |       |

| t <sub>PLH</sub> | Propagation Delay Time   | Clock to Q or Q             |                        | 9                 |                        | 12  | ns    |

|                  | LOW-to-HIGH Level Output |                             |                        |                   |                        | 12  | 115   |

| t <sub>PHL</sub> | Propagation Delay Time   | Clock to Q or Q             |                        | 9                 |                        | 14  | ns    |

|                  | HIGH-to-LOW Level Output |                             |                        |                   |                        | 14  |       |

#

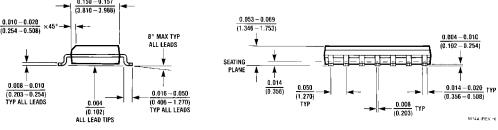

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow Package Number M14A

N144 (REV.E)

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 0.740 - 0.770(18.80 - 19.56)0.090 (2.286) 14 13 12 11 10 9 8 14 13 12 0.250 ± 0.010 PIN NO. 1 IDENT PIN NO. 1 IDENT 1 2 3 4 5 6 7 1 2 3 $\frac{0.092}{(2.337)}$ DIA 0.030 MAX (0.762) DEPTH OPTION 1 OPTION 02 $\frac{0.135 \pm 0.005}{(3.429 \pm 0.127)}$ 0.300 - 0.320 $\overline{(7.620 - 8.128)}$ 0.065 $\frac{0.145 - 0.200}{(3.683 - 5.080)}$ 0.060 4° TYP Optional (1.524) (1.651) 0.008-0.016 TYP 0.020 (0.203 - 0.406)(0.508) 0.125 - 0.150 $0.075 \pm 0.015$ $\overline{(3.175 - 3.810)}$ 0.280 (1.905 ± 0.381) (7.112) MIN 0.014 - 0.0230.100 ± 0.010 (2.540 ± 0.254) TYP (0.356 - 0.584) $\frac{0.050\pm0.010}{(1.270-0.254)}$ TYP 0.325 <sup>+0.040</sup> -0.015 $8.255 + 1.016 \\ -0.381$

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N14A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com