74F402 Serial Data Polynomial Generator/Checker

# 74F402 Serial Data Polynomial Generator/Checker

# **General Description**

FAIRCHILD

SEMICONDUCTOR

The 74F402 expandable Serial Data Polynomial generator/ checker is an expandable version of the 74F401. It provides an advanced tool for the implementation of the most widely used error detection scheme in serial digital handling systems. A 4-bit control input selects one-of-six generator polynomials. The list of polynomials includes CRC-16, CRC-CCITT and Ethernet®, as well as three other standard polynomials (56<sup>th</sup> order, 48<sup>th</sup> order, 32<sup>nd</sup> order). Individual clear and preset inputs are provided for floppy disk and other applications. The Error output indicates whether or not a transmission error has occurred. The CWG Control input inhibits feedback during check word transmission. The 74F402 is compatible with FAST® devices and with all TTL families.

### Features

- Guaranteed 30 MHz data rate

- Six selectable polynomials

- Other polynomials available

- Separate preset and clear controls

- Expandable

- Automatic right justification

- Error output open collector

- Typical applications: Floppy and other disk storage systems Digital cassette and cartridge systems Data communication systems

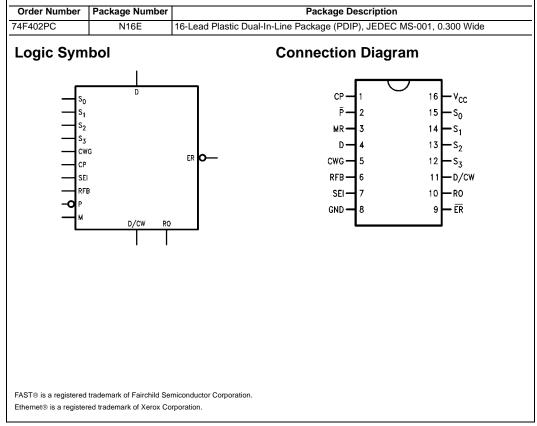

# Ordering Code:

www.fairchildsemi.com

| <b>D</b> : N                   | <b>D</b> ata tarita       | U.L.                 | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |

|--------------------------------|---------------------------|----------------------|-----------------------------------------|--|

| Pin Names                      | Description               | HIGH/LOW             | Output I <sub>OH</sub> /I <sub>OL</sub> |  |

| S <sub>0</sub> –S <sub>3</sub> | Polynomial Select Inputs  | 1.0/0.67             | 20 µA/–0.4 mA                           |  |

| CWG                            | Check Word Generate Input | 1.0/0.67             | 20 μA/–0.4 mA                           |  |

| D/CW                           | Serial Data/Check Word    | 285(100)/13.3(6.7)   | -5.7 mA(-2 mA)/8 mA (4 mA               |  |

| D                              | Data Input                | 1.0/0.67             | 20 μA/–0.4 mA                           |  |

| ER                             | Error Output              | (Note 1) /26.7(13.3) | (Note 1) /16 mA (8 mA)                  |  |

| RO                             | Register Output           | 285(100)/13.3(6.7)   | -5.7 mA(-2 mA)/8 mA (4 mA)              |  |

| CP                             | Clock Pulse               | 1.0/0.67             | 20 μA/–0.4 mA                           |  |

| SEI                            | Serial Expansion Input    | 1.0/0.67             | 20 μA/–0.4 mA                           |  |

| RFB                            | Register Feedback         | 1.0/0.67             | 20 µA/–0.4 mA                           |  |

| MR                             | Master Reset              | 1.0/0.67             | 20 μA/–0.4 mA                           |  |

| P                              | Preset                    | 1.0/0.67             | 20 μA/–0.4 mA                           |  |

#### **Functional Description**

The 74F402 Serial Data Polynomial Generator/Checker is an expandable 16-bit programmable device which operates on serial data streams and provides a means of detecting transmission errors. Cyclic encoding and decoding schemes for error detection are based on polynomial manipulation in modulo arithmetic. For encoding, the data stream (message polynomial) is divided by a selected polynomial. This division results in a remainder (or residue) which is appended to the message as check bits. For error checking, the bit stream containing both data and check bits is divided by the same selected polynomial. If there are no detectable errors, this division results in a zero remainder. Although it is possible to choose many generating polynomials of a given degree, standards exist that specify a small number of useful polynomials. The 74F402 implements the polynomials listed in Table 1 by applying the appropriate logic levels to the select pins  $S_0$ ,  $S_1$ ,  $S_2$  and  $S_3$ .

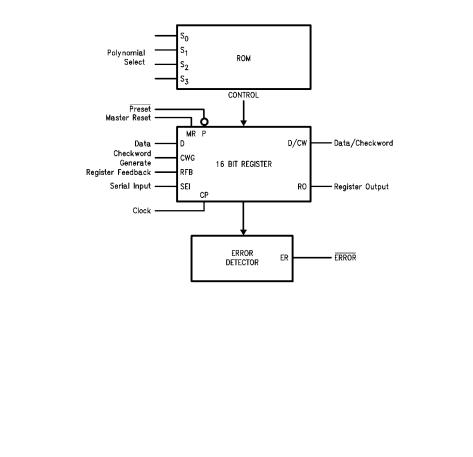

The 74F402 consists of a 16-bit register, a Read Only Memory (ROM) and associated control circuitry as shown in the Block Diagram. The polynomial control code presented at inputs  $S_0$ ,  $S_1$ ,  $S_2$  and  $S_3$  is decoded by the ROM, selecting the desired polynomial or part of a polynomial by establishing shift mode operation on the register with Exclusive OR (XOR) gates at appropriate inputs. To generate the check bits, the data stream is entered via the Data Inputs (D), using the LOW-to-HIGH transition of the Clock Input (CP). This data is gated with the most significant Register Output (RO) via the Register Feedback Input (RFB), and controls the XOR gates. The Check Word Gen-

erate (CWG) must be held HIGH while the data is being entered. After the last data bit is entered, the CWG is brought LOW and the check bits are shifted out of the register(s) and appended to the data bits (no external gating is needed).

To check an incoming message for errors, both the data and check bits are entered through the D Input with the CWG Input held HIGH. The Error Output becomes valid after the last check bit has been entered into the 'F402 by a LOW-to-HIGH transition of CP, with the exception of the Ethernet polynomial (see Applications paragraph). If no detectable errors have occurred during the data transmission, the resultant internal register bits are all LOW and the Error Output (ER) is HIGH. If a detectable error has occurred, ER is LOW. ER remains valid until the next LOW-to-HIGH transition of CP or until the device has been preset or reset.

A HIGH on the Master Reset Input (MR) asynchronously clears the entire register. A LOW on the Preset Input  $(\overline{P})$  asynchronously sets the entire register with the exception of:

- 1. The Ethernet residue selection, in which the registers containing the non-zero residue are cleared;

- The 56th order polynomial, in which the 8 least significant register bits of the least significant device are cleared; and,

- 3. Register S = 0, in which all bits are cleared.

| Hex |                | Select         | Code           |                |                                                                                                                         |            |

|-----|----------------|----------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------|------------|

|     | S <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Polynomial                                                                                                              | Remarks    |

| 0   | L              | L              | L              | L              | 0                                                                                                                       | S = 0      |

| С   | Н              | Н              | L              | L              | X <sup>32</sup> +X <sup>26</sup> +X <sup>23</sup> +X <sup>22</sup> +X <sup>16</sup> +                                   | Ethernet   |

| D   | н              | н              | L              | н              | $X^{12}+X^{11}+X^{10}+X^8+X^7+X^5+X^4+X^2+X+1$                                                                          | Polynomial |

| Е   | Н              | Н              | Н              | L              | X <sup>32</sup> +X <sup>31</sup> +X <sup>27</sup> +X <sup>26</sup> +X <sup>25</sup> +X <sup>19</sup> +X <sup>16</sup> + | Ethernet   |

| F   | н              | н              | н              | н              | $X^{15}+X^{13}+X^{12}+X^{11}+X^{9}+X^{7}+X^{6}+X^{5}+X^{4}+X^{2}+X+1$                                                   | Residue    |

| 7   | L              | Н              | Н              | Н              | X <sup>16</sup> +X <sup>15</sup> +X <sup>2</sup> +1                                                                     | CRC-16     |

| В   | Н              | L              | Н              | Н              | X <sup>16</sup> +X <sup>12</sup> +X <sup>5</sup> +1                                                                     | CRC-CCITT  |

| 3   | L              | L              | Н              | Н              | X <sup>56</sup> +X <sup>55</sup> +X <sup>49</sup> +X <sup>45</sup> +X <sup>41</sup> +                                   |            |

| 2   | L              | L              | н              | L              | $X^{39}+X^{38}+X^{37}+X^{36}+X^{31}+$                                                                                   | 56th       |

| 4   | L              | н              | L              | L              | $X^{22}+X^{19}+X^{17}+X^{16}+X^{15}+X^{14}+X^{12}+X^{11}+X^{9}+$                                                        | Order      |

| 8   | н              | L              | L              | L              | X <sup>5</sup> +X+1                                                                                                     |            |

| 5   | L              | Н              | L              | Н              | X <sup>48</sup> +X <sup>36</sup> +X <sup>35+</sup>                                                                      |            |

| 9   | н              | L              | L              | н              | $X^{23}+X^{21}+$                                                                                                        | 48th       |

| 1   | L              | L              | L              | н              | $X^{15}+X^{13}+X^{8}+X^{2}+1$                                                                                           | Order      |

| 6   | L              | Н              | Н              | L              | X <sup>32</sup> +X <sup>23</sup> +X <sup>21</sup> +                                                                     | 32nd       |

| А   | н              | L              | н              | L              | X <sup>11</sup> +X <sup>2</sup> +1                                                                                      | Order      |

# **Block Diagram**

www.fairchildsemi.com

74F402

3

#### TABLE 2.

| IABLE 2.    |                |                |                |                |                |                |                |            |

|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------|

| Select Code | P <sub>3</sub> | P <sub>2</sub> | P <sub>1</sub> | P <sub>0</sub> | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> | Polynomial |

| 0           | 0              | 0              | 0              | 0              | 1              | 0              | 0              | S = 0      |

| С           | 1              | 1              | 1              | 1              | 1              | 0              | 1              | Ethernet   |

| D           | 1              | 1              | 1              | 1              | 1              | 0              | 1              | Polynomial |

| E           | 0              | 0              | 0              | 0              | 0              | 0              | 0              | Ethernet   |

| F           | 0              | 0              | 0              | 0              | 0              | 1              | 0              | Residue    |

| 7           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | CRC-16     |

| В           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | CRC-CCITT  |

| 3           | 1              | 1              | 1              | 1              | 1              | 0              | 0              |            |

| 2           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | 56th       |

| 4           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | Order      |

| 8           | 0              | 0              | 1              | 1              | 1              | 0              | 0              |            |

| 5           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | 48th       |

| 9           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | Order      |

| 1           | 1              | 1              | 1              | 1              | 1              | 0              | 0              |            |

| 6           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | 32nd       |

| А           | 1              | 1              | 1              | 1              | 1              | 0              | 0              | Order      |

#### Applications

In addition to polynomial selection there are four other capabilities provided for in the 74F402 ROM. The first is set or clear selectability. The sixteen internal registers have the capability to be either set or cleared when P is brought LOW. This set or clear capability is done in four groups of 4 (see Table 2,  $P_0-P_3$ ). The second ROM capability ( $C_0$ ) is in determining the polarity of the check word. As is the case with the Ethernet polynomial the check word can be inverted when it is appended to the data stream or as is the case with the other polynomials, the residue is appended with no inversion. Thirdly, the ROM contains a bit (C1) which is used to select the RFB input instead of the SEI input to be fed into the LSB. This is used when the polynomial selected is actually a residue (least significant) stored in the ROM which indicates whether the selected location is a polynomial or a residue. If the latter, then it inhibits the RFB input.

As mentioned previously, upon a successful data transmission, the CRC register has a zero residue. There is an exception to this, however, with respect to the Ethernet polynomial. This polynomial, upon a successful data transmission, has a non-zero residue in the CRC register (C7 04 DD 7B)<sub>16</sub>. In order to provide a no-error indication, two ROM locations have been preloaded with the residue so that by selecting these locations and clocking the device one additional time, after the last check bit has been entered, will result in zeroing the CRC register. In this manner a no-error indication is achieved.

With the present mix of polynomials, the largest is 56<sup>th</sup> order requiring four devices while the smallest is 16<sup>th</sup> order requiring just one device. In order to accommodate multiplexing between high order polynomials (X 16<sup>th</sup> order) and lower order polynomials, a location of all zeros is provided.

This allows the user to choose a lower order polynomial even if the system is configured for a higher order one.

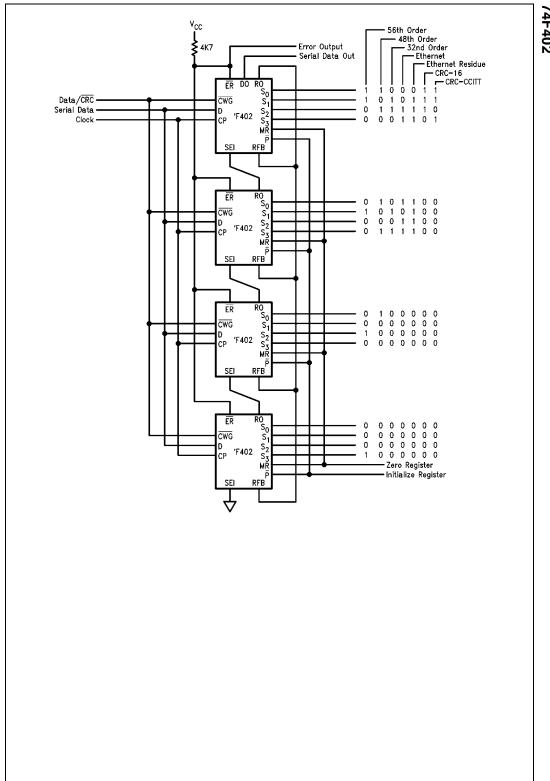

The 74F402 expandable CRC generator checker contains 6 popular CRC polynomials, 2-16<sup>th</sup> Order, 2-32<sup>nd</sup> Order, 1-48<sup>th</sup> Order and 1-56<sup>th</sup> Order. The application diagram shows the 74F402 connected for a 56<sup>th</sup> Order polynomial. Also shown are the input patterns for other polynomials. When the 74F402 is used with a gated clock, disabling the clock in a HIGH state will ensure no erroneous clocking occurs when the clock is re-enabled. Preset and Master Reset are asynchronous inputs presetting the register to S or clearing to 1s respectively (note Ethernet residue and 56<sup>th</sup> Order select code 8, LSB, are exceptions to this).

To generate a CRC, the pattern for the selected polynomial is applied to the S inputs, the register is preset or cleared as required, clock is enabled, CWG is set HIGH, data is applied to D input, output data is on D/CW. When the last data bit has been entered, CWG is set LOW and the register is clocked for n bits (where n is the order of the polynomial). The clock may now be stopped if desired (holding CWG LOW and clocking the register will output zeros from D/CW after the residue has been shifted out).

To check a CRC, the pattern for the selected polynomial is applied to the S inputs, the register is preset or cleared as required, clock is enabled, CWG is set HIGH, the data stream including the CRC is applied to D input. When the last bit of the CRC has been entered, the  $\overline{\text{ER}}$  output is checked: HIGH = error free data, LOW = corrupt data. The clock may now be stopped if desired.

To implement polynomials of lower order than 56<sup>th</sup>, select the number of packages required for the order of polynomial and apply the pattern for the selected polynomial to the S inputs (0000 on S inputs disables the package from the feedback chain).

www.fairchildsemi.com

### Absolute Maximum Ratings(Note 2)

| $-65^{\circ}C$ to $+150^{\circ}C$    |

|--------------------------------------|

| $-55^{\circ}C$ to $+125^{\circ}C$    |

| $-55^{\circ}C$ to $+150^{\circ}C$    |

| -0.5V to +7.0V                       |

| -0.5V to +7.0V                       |

| -30 mA to +5.0 mA                    |

|                                      |

|                                      |

| –0.5V to $V_{\mbox{\scriptsize CC}}$ |

| -0.5V to +5.5V                       |

|                                      |

| twice the rated $I_{OL}\ (mA)$       |

|                                      |

# **Recommended Operating Conditions**

Free Air Ambient Temperature Supply Voltage

0°C to +70°C +4.5V to +5.5V

Note 2: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

### **DC Electrical Characteristics**

Symbol Parameter Min Тур Мах Units  $v_{cc}$ Conditions VIH Input HIGH Voltage 2.0 V Recognized as a HIGH Signal Input LOW Voltage Recognized as a LOW Signal  $V_{IL}$ 0.8 V I<sub>IN</sub> = -18 mA  $V_{CD}$ Input Clamp Diode Voltage V -1.2 Min V<sub>OH</sub> 10% V<sub>CC</sub> I<sub>OH</sub> = -5.7 mA (RO, D/CW) Output HIGH 2.4 V Min Voltage 5% V<sub>CC</sub> 2.7  $I_{OH} = -5.7 \text{ mA} (RO, D/CW)$ Output LOW 10% V<sub>CC</sub> 0.5  $I_{OL} = 16 \text{ mA} (\overline{\text{ER}})$ V<sub>OL</sub> 10% V<sub>CC</sub> I<sub>OL</sub> = 8 mA (D/CW, RO) Voltage 0.5  $\mathsf{I}_{\mathsf{IH}}$ Input HIGH 5.0 μΑ Max  $V_{IN} = 2.7V$ Current Input HIGH Current I<sub>BVI</sub>  $V_{IN} = 7.0V$ 7.0 μA Max Breakdown Test Output HIGH  $I_{CEX}$ 50 μA Max  $V_{OUT} = V_{CC}$ Leakage Current VID Input Leakage I<sub>ID</sub> = 1.9 μA 4.75 V 0.0 All Other Pins Grounded Test V<sub>IOD</sub> = 150 mV Output Leakage IOD 3.75 0.0 μA Circuit Current All Other Pins Grounded Input LOW Current -0.4 mΑ Max  $V_{IN} = 0.5V$  $\mathsf{I}_{\mathsf{IL}}$ V<sub>OUT</sub> = 0V (D/CW, RO) los Output Short-Circuit Current -20 -130 mΑ Max Open Collector, Output I<sub>OHC</sub> 250 μΑ Min  $V_{OUT} = V_{CC} (\overline{ER})$ OFF Leakage Test Max Power Supply Current 110 I<sub>CC</sub> 165 mΑ

| Symbol           |                              |                                                   | T <sub>A</sub> = +25°C |      |                                                   | $T_A = -55^{\circ}C$ to $+125^{\circ}C$ |                                                   | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ |       |  |

|------------------|------------------------------|---------------------------------------------------|------------------------|------|---------------------------------------------------|-----------------------------------------|---------------------------------------------------|---------------------------------------------|-------|--|

|                  |                              | V <sub>CC</sub> = +5.0V<br>C <sub>L</sub> = 50 pF |                        |      | V <sub>CC</sub> = +5.0V<br>C <sub>L</sub> = 50 pF |                                         | V <sub>CC</sub> = +5.0V<br>C <sub>L</sub> = 50 pF |                                             | Units |  |

|                  | Parameter                    |                                                   |                        |      |                                                   |                                         |                                                   |                                             |       |  |

|                  |                              | Min                                               | Тур                    | Max  | Min                                               | Max                                     | Min                                               | Max                                         | ł     |  |

| f <sub>MAX</sub> | Maximum Clock Frequency      | 30                                                | 45                     |      | 30                                                |                                         | 30                                                |                                             | MHz   |  |

| t <sub>PLH</sub> | Propagation Delay            | 8.5                                               | 15.0                   | 19.0 | 7.5                                               | 26.5                                    | 7.5                                               | 21.0                                        |       |  |

| t <sub>PHL</sub> | CP to D/CW                   | 10.5                                              | 18.0                   | 23.0 | 9.5                                               | 26.5                                    | 9.5                                               | 25.0                                        | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 8.0                                               | 13.5                   | 17.0 | 7.0                                               | 26.0                                    | 7.0                                               | 19.0                                        | ns    |  |

| t <sub>PHL</sub> | CP to RO                     | 8.0                                               | 14.0                   | 18.0 | 7.0                                               | 22.5                                    | 7.0                                               | 20.0                                        |       |  |

| t <sub>PLH</sub> | Propagation Delay            | 15.5                                              | 26.0                   | 33.0 | 14.0                                              | 38.5                                    | 14.0                                              | 35.0                                        |       |  |

| t <sub>PHL</sub> | CP to ER                     | 8.5                                               | 14.5                   | 18.5 | 7.5                                               | 23.5                                    | 7.5                                               | 20.5                                        | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 11.0                                              | 18.5                   | 23.5 | 10.0                                              | 31.0                                    | 10.0                                              | 25.5                                        | ns    |  |

| t <sub>PHL</sub> | P to D/CW                    | 11.5                                              | 19.5                   | 24.5 | 10.5                                              | 32.0                                    | 10.5                                              | 26.5                                        |       |  |

| t <sub>PLH</sub> | Propagation Delay<br>P to RO |                                                   | 16.0 20.5              |      |                                                   | 0.5 00.5                                |                                                   |                                             |       |  |

|                  |                              | 9.5                                               |                        | 20.5 | 8.5                                               | 31.5                                    | 8.5                                               | 22.5                                        | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 40.0                                              | 17.0                   | 21.5 | 9.0                                               | 26.0                                    | 9.0                                               | 23.5                                        |       |  |

|                  | P to ER                      | 10.0                                              |                        |      |                                                   |                                         |                                                   |                                             | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 10.5                                              | 18.0                   | 23.0 | 9.5                                               | 29.0                                    | 9.5                                               | 25.5                                        |       |  |

| t <sub>PHL</sub> | MR to D/CW                   | 11.0                                              | 19.0                   | 24.0 | 10.0                                              | 28.5                                    | 10.0                                              | 26.0                                        | ns    |  |

| t <sub>PHL</sub> | Propagation Delay            | 0.0                                               | 45 F                   | 10 F |                                                   | 00 F                                    | 0.0                                               | 24.5                                        | -     |  |

|                  | MR to RO                     | 9.0                                               | 15.5                   | 19.5 | 8.0                                               | 23.5                                    | 8.0                                               | 21.5                                        | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 16.5                                              | 28.0                   | 2E E | 14.5                                              | 20.0                                    | 145                                               | 27 E                                        |       |  |

|                  | MR to ER                     | 16.5                                              | 5 28.0                 | 35.5 | 14.5                                              | 39.0                                    | 14.5                                              | 37.5                                        | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 6.0                                               | 10.5                   | 13.5 | 5.0                                               | 19.5                                    | 5.0                                               | 15.0                                        |       |  |

| t <sub>PHL</sub> | D to D/CW                    | 7.5                                               | 12.0                   | 16.0 | 6.5                                               | 20.0                                    | 6.5                                               | 18.0                                        | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 6.5                                               | 11.0                   | 14.0 | 5.5                                               | 21.5                                    | 5.5                                               | 15.5                                        |       |  |

| t <sub>PHL</sub> | CWG to D/CW                  | 7.0                                               | 12.0                   | 15.5 | 6.0                                               | 21.5                                    | 6.0                                               | 17.5                                        | ns    |  |

| t <sub>PLH</sub> | Propagation Delay            | 11.5                                              | 19.5                   | 24.5 | 9.0                                               | 29.0                                    | 10.5                                              | 26.5                                        |       |  |

| t <sub>PHL</sub> | S <sub>n</sub> to D/CW       | 9.5                                               | 16.0                   | 20.0 | 8.5                                               | 25.0                                    | 8.5                                               | 22.0                                        | ns    |  |

| Symbol             |                           | T <sub>A</sub> = +25°C | $T_A = -55^{\circ}C$ to $+125^{\circ}C$ | $T_A = 0^{\circ}C$ to $+70^{\circ}C$ | Unit |

|--------------------|---------------------------|------------------------|-----------------------------------------|--------------------------------------|------|

|                    | Parameter                 | $V_{CC} = +5.0V$       | $V_{CC} = +5.0V$                        | $V_{CC} = +5.0V$                     |      |

|                    |                           | Min Max                | Min Max                                 | Min Max                              |      |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW   | 4.5                    | 6.0                                     | 5.0                                  |      |

| t <sub>S</sub> (L) | SEI to CP                 | 4.5                    | 6.0                                     | 5.0                                  |      |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW    | 0                      | 1.0                                     | 0                                    | ns   |

| t <sub>H</sub> (L) | SEI to CP                 | 0                      | 1.0                                     | 0                                    |      |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW   | 11.0                   | 14.0                                    | 12.5                                 |      |

| t <sub>S</sub> (L) | RFB to CP                 | 11.0                   | 14.0                                    | 12.5                                 |      |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW    | 0                      | 0                                       | 0                                    | ns   |

| t <sub>H</sub> (L) | RFB to CP                 | 0                      | 0                                       | 0                                    |      |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW   | 13.5                   | 16.0                                    | 15.0                                 | ns   |

| t <sub>S</sub> (L) | S <sub>1</sub> to CP      | 13.0                   | 15.5                                    | 14.5                                 |      |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW    | 0                      | 0                                       | 0                                    |      |

| t <sub>H</sub> (L) | S <sub>1</sub> to CP      | 0                      | 0                                       | 0                                    |      |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW   | 9.0                    | 11.5                                    | 10.0                                 |      |

| t <sub>S</sub> (L) | D to CP                   | 9.0                    | 11.5                                    | 10.0                                 |      |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW    | 0                      | 0                                       | 0                                    | ns   |

| t <sub>H</sub> (L) | D to CP                   | 0                      | 0                                       | 0                                    |      |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW   | 7.0                    | 9.0                                     | 8.0                                  |      |

| t <sub>S</sub> (L) | CWG to CP                 | 5.5                    | 8.0                                     | 6.5                                  |      |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW    | 0                      | 0                                       | 0                                    | ns   |

| t <sub>H</sub> (L) | CWG to CP                 | 0                      | 0                                       | 0                                    |      |

| t <sub>W</sub> (H) | Clock Pulse Width         | 4.0                    | 7.0                                     | 4.5                                  |      |

| t <sub>W</sub> (L) | HIGH or LOW               | 4.0                    | 5.0                                     | 4.5                                  | ns   |

| t <sub>W</sub> (H) | MR Pulse Width, HIGH      | 4.0                    | 7.0                                     | 4.5                                  | ns   |

| t <sub>W</sub> (L) | P Pulse Width, LOW        | 4.0                    | 5.0                                     | 4.5                                  | ns   |

| t <sub>REC</sub>   | Recovery Time<br>MR to CP | 3.0                    | 4.0                                     | 3.5                                  |      |

| t <sub>REC</sub>   | Recovery Time             | 5.0                    | 6.5                                     | 6.0                                  | ns   |

www.fairchildsemi.com