April 1988 Revised August 1999

## 74F323

# Octal Universal Shift/Storage Register with Synchronous Reset and Common I/O Pins

## **General Description**

The 74F323 is an 8-bit universal shift/storage register with 3-STATE outputs. Its function is similar to the 74F299 with the exception of Synchronous Reset. Parallel load inputs and flip-flop outputs are multiplexed to minimize pin count. Separate serial inputs and outputs are provided for  $\mathbf{Q}_0$  and  $\mathbf{Q}_7$  to allow easy cascading. Four operation modes are possible: hold (store), shift left, shift right and parallel load.

#### **Features**

- Common parallel I/O for reduced pin count

- Additional serial inputs and outputs for expansion

- Four operating modes: shift left, shift right, load and store

- 3-STATE outputs for bus-oriented applications

## **Ordering Code:**

| Order Number | Package Number | Package Description                                                       |

|--------------|----------------|---------------------------------------------------------------------------|

| 74F323SC     | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

| 74F323PC     | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide     |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

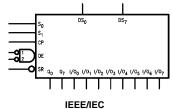

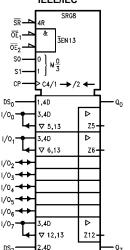

## **Logic Symbols**

## **Connection Diagram**

## **Unit Loading/Fan Out**

| Pin Names                              | Description                               | U.L.          | Input I <sub>IH</sub> /I <sub>IL</sub>  |  |  |

|----------------------------------------|-------------------------------------------|---------------|-----------------------------------------|--|--|

|                                        | Description                               | HIGH/LOW      | Output I <sub>OH</sub> /I <sub>OL</sub> |  |  |

| CP                                     | Clock Pulse Input (Active Rising Edge)    | 1.0/1.0       | 20 μA/-0.6 mA                           |  |  |

| DS <sub>0</sub>                        | Serial Data Input for Right Shift         | 1.0/1.0       | 20 μA/–0.6 mA                           |  |  |

| DS <sub>7</sub>                        | Serial Data Input for Left Shift          | 1.0/1.0       | 20 μA/–0.6 mA                           |  |  |

| S <sub>0,</sub> S <sub>1</sub>         | Mode Select Inputs                        | 1.0/2.0       | 20 μA/–1.2 mA                           |  |  |

| SR                                     | Synchronous Reset Input (Active LOW)      | 1.0/1.0       | 20 μA/–0.6 mA                           |  |  |

| $\overline{OE}_{1}, \overline{OE}_{2}$ | 3-STATE Output Enable Inputs (Active LOW) | 1.0/1.0       | 20 μA/–0.6 mA                           |  |  |

| I/O <sub>0</sub> –I/O <sub>7</sub>     | Multiplexed Parallel Data Inputs          | 3.5/1.083     | 70 μA/–0.65 mA                          |  |  |

|                                        | 3-STATE Parallel Data Outputs             | 150/40 (33.3) | -3 mA/24 mA (20 mA)                     |  |  |

| $Q_{0, Q_7}$                           | Serial Outputs                            | 50/33.3       | −1 mA/20 mA                             |  |  |

## **Functional Description**

The 74F323 contains eight edge-triggered D-type flip-flops and the interstage logic necessary to perform synchronous reset, shift left, shift right, parallel load and hold operations. The type of operation is determined by  $S_0$  and  $S_1$  as shown in the Mode Select Table. All flip-flop outputs are brought out through 3-STATE buffers to separate I/O pins that also serve as data inputs in the parallel load mode.  $Q_0$  and  $Q_7$  are also brought out on other pins for expansion in serial shifting of longer words.

A LOW signal on  $\overline{\text{SR}}$  overrides the Select inputs and allows the flip-flops to be reset by the next rising edge of CP. All other state changes are also initiated by the LOW-to-HIGH CP transition. Inputs can change when the clock is in either state provided only that the recommended setup and hold times, relative to the rising edge of CP, are observed.

A HIGH signal on either  $\overline{OE}_1$  or  $\overline{OE}_2$  disables the 3-STATE buffers and puts the I/O pins in the high impedance state. In this condition the shift, load, hold and reset operations can still occur. The 3-STATE buffers are also disabled by HIGH signals on both  $S_0$  and  $S_1$  in preparation for a parallel load operation.

#### **Mode Select Table**

| Inputs |                |                |    | Response                                                           |

|--------|----------------|----------------|----|--------------------------------------------------------------------|

| SR     | S <sub>1</sub> | S <sub>0</sub> | СР |                                                                    |

| L      | Χ              | Χ              | _  | Synchronous Reset; Q <sub>0</sub> –Q <sub>7</sub> = LOW            |

|        |                |                |    | Parallel Load; $I/O_n \rightarrow Q_n$                             |

| Н      |                |                |    | Shift Right; $DS_0 \rightarrow Q_{0,} Q_0 \rightarrow Q_{1,}$ etc. |

| Н      | Н              | L              | _  | Shift Left; $DS_7 \rightarrow Q_{7,} Q_7 \rightarrow Q_{6,}$ etc.  |

| Н      | L              | L              | Χ  | Hold                                                               |

- H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Immateria

- ∠ = LOW-to-HIGH transition

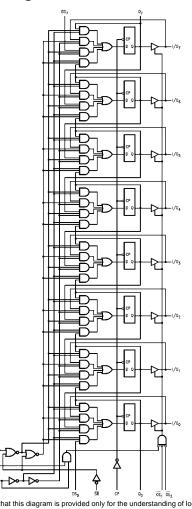

## **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

## **Absolute Maximum Ratings**(Note 1)

## **Recommended Operating Conditions**

-65°C to +150°C Storage Temperature -55°C to +125°C

Ambient Temperature under Bias

Junction Temperature under Bias -55°C to +150°C V<sub>CC</sub> Pin Potential to Ground Pin -0.5V to +7.0VInput Voltage (Note 2) -0.5V to +7.0VInput Current (Note 2) -30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with  $V_{CC} = 0V$ )

Standard Output -0.5V to  $V_{CC}$ 3-STATE Output -0.5V to +5.5V

Current Applied to Output

in LOW State (Max) twice the rated I<sub>OL</sub> (mA) ESD Last Passing Voltage (Min) 4000V

Free Air Ambient Temperature 0°C to +70°C Supply Voltage +4.5V to +5.5V

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

## **DC Electrical Characteristics**

| Symbol            | Parameter                    |                     | Min  | Тур | Max  | Units | v <sub>cc</sub> | Conditions                                                                                                         |

|-------------------|------------------------------|---------------------|------|-----|------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------|

| V <sub>IH</sub>   | Input HIGH Voltage           |                     | 2.0  |     |      | V     |                 | Recognized as a HIGH Signal                                                                                        |

| V <sub>IL</sub>   | Input LOW Voltage            |                     |      |     | 0.8  | V     |                 | Recognized as a LOW Signal                                                                                         |

| V <sub>CD</sub>   | Input Clamp Diode Voltage    |                     |      |     | -1.2 | V     | Min             | I <sub>IN</sub> = -18 mA                                                                                           |

| V <sub>OH</sub>   | Output HIGH                  | 10% V <sub>CC</sub> | 2.5  |     |      |       |                 | $I_{OH} = -1 \text{ mA}  (Q_0, Q_7)$                                                                               |

|                   | Voltage                      | 10% V <sub>CC</sub> | 2.4  |     |      | V     | Min             | $I_{OH} = -3 \text{ mA}  (I/O_n)$                                                                                  |

|                   |                              | $5\% V_{CC}$        | 2.7  |     |      | V     | IVIIII          | $I_{OH} = -1 \text{ mA}  (Q_0, Q_7)$                                                                               |

|                   |                              | $5\% V_{CC}$        | 2.7  |     |      |       |                 | $I_{OH} = -3 \text{ mA}  (I/O_n)$                                                                                  |

| V <sub>OL</sub>   | Output LOW                   | 10% V <sub>CC</sub> |      |     | 0.5  | V     | Min             | $I_{OL} = 20 \text{ mA}  (Q_0, Q_7)$                                                                               |

|                   | Voltage                      | 10% V <sub>CC</sub> |      |     | 0.5  | V     | IVIII           | $I_{OL} = 24 \text{ mA}  (I/O_n)$                                                                                  |

| I <sub>IH</sub>   | Input HIGH Current           |                     |      |     | 5.0  | μΑ    | Max             | V <sub>IN</sub> = 2.7V                                                                                             |

| I <sub>BVI</sub>  | Input HIGH Current           |                     |      |     | 7.0  | μА    | Max             | V <sub>IN</sub> = 7.0V (Non I/O Inputs)                                                                            |

|                   | Breakdown Test               |                     |      |     | 7.0  | μΛ    | IVIAA           | VIN = 7.0V (Non 1/O inputs)                                                                                        |

| I <sub>BVIT</sub> | Input HIGH Current           |                     |      |     | 0.5  | mA    | Max             | V <sub>IN</sub> = 5.5V (I/O Inputs)                                                                                |

|                   | Breakdown (I/O)              |                     |      |     | 0.5  | IIIA  | IVIAA           | VIN = 3.5V (I/O Inputs)                                                                                            |

| I <sub>CEX</sub>  | Output HIGH                  |                     |      |     | 50   | ^     | Max             | V V                                                                                                                |

|                   | Leakage Current              |                     |      |     | 50   | μА    | iviax           | $V_{OUT} = V_{CC}$                                                                                                 |

| V <sub>ID</sub>   | Input Leakage                |                     | 4.75 |     |      | V     | 0.0             | $I_{ID} = 1.9 \mu A$                                                                                               |

|                   | Test                         |                     | 4.75 |     |      | V     | 0.0             | All Other Pins Grounded                                                                                            |

| I <sub>OD</sub>   | Output Leakage               |                     |      |     | 3.75 | μА    | 0.0             | V <sub>IOD</sub> = 150 mV                                                                                          |

|                   | Circuit Current              |                     |      |     | 3.73 | μΑ    | 0.0             | All Other Pins Grounded                                                                                            |

| I <sub>IL</sub>   | Input LOW Current            |                     |      |     | -0.6 | mA    | Max             | $V_{IN} = 0.5V$ (CP, DS <sub>0</sub> , DS <sub>7</sub> , $\overline{SR}$ , $\overline{OE}_1$ , $\overline{OE}_2$ ) |

|                   |                              |                     |      |     | -1.2 | mA    | Max             | $V_{IN} = 0.5V  (S_0, S_1)$                                                                                        |

| Ios               | Output Short-Circuit Current |                     | -60  |     | -150 | mA    | Max             | V <sub>OUT</sub> = 0V                                                                                              |

| I <sub>ZZ</sub>   | Bus Drainage Test            |                     |      |     | 500  | μΑ    | 0.0V            | V <sub>OUT</sub> = 5.25V                                                                                           |

| I <sub>CCH</sub>  | Power Supply Current         |                     |      | 68  | 95   | mA    | Max             | V <sub>O</sub> = HIGH                                                                                              |

| I <sub>CCL</sub>  | Power Supply Current         |                     |      | 68  | 95   | mA    | Max             | $V_O = LOW$                                                                                                        |

| I <sub>CCZ</sub>  | Power Supply Current         |                     |      | 68  | 95   | mA    | Max             | V <sub>O</sub> = HIGH Z                                                                                            |

# **AC Electrical Characteristics**

| Symbol           | Parameter                              |     | $T_A = +25$ °C<br>$V_{CC} = +5.0$ V<br>$C_L = 50$ pF | '    | $T_A = 0$ °C to +70°C $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |      | Units |

|------------------|----------------------------------------|-----|------------------------------------------------------|------|--------------------------------------------------------------|------|-------|

|                  |                                        | Min | Тур                                                  | Max  | Min                                                          | Max  |       |

| f <sub>MAX</sub> | Maximum Input Frequency                | 70  | 100                                                  |      | 70                                                           |      | MHz   |

| t <sub>PLH</sub> | Propagation Delay                      | 4.0 | 7.0                                                  | 8.0  | 4.0                                                          | 8.5  |       |

| t <sub>PHL</sub> | CP to Q <sub>0</sub> or Q <sub>7</sub> | 4.5 | 6.5                                                  | 8.0  | 4.5                                                          | 8.5  | ns    |

| t <sub>PLH</sub> | Propagation Delay                      | 3.5 | 7.0                                                  | 9.0  | 3.5                                                          | 10.0 | 115   |

| t <sub>PHL</sub> | CP to I/O <sub>n</sub>                 | 4.0 | 8.5                                                  | 9.0  | 4.0                                                          | 10.0 |       |

| t <sub>PZH</sub> | Output Enable Time                     | 3.5 | 6.0                                                  | 8.0  | 3.5                                                          | 9.0  |       |

| t <sub>PZL</sub> |                                        | 4.0 | 7.0                                                  | 10.0 | 4.0                                                          | 11.0 | ns    |

| t <sub>PHZ</sub> | Output Disable Time                    | 2.0 | 4.5                                                  | 6.0  | 2.0                                                          | 7.0  | 115   |

| t <sub>PLZ</sub> |                                        | 1.0 | 4.0                                                  | 5.5  | 1.0                                                          | 6.5  |       |

| t <sub>PZH</sub> | Output Enable Time                     | 3.5 |                                                      | 9.0  | 3.5                                                          | 10.0 | ns    |

| t <sub>PZL</sub> | S <sub>n</sub> to I/O <sub>n</sub>     | 4.0 |                                                      | 10.0 | 4.0                                                          | 11.0 | 115   |

| t <sub>PHZ</sub> | Output Disable Time                    | 2.5 |                                                      | 6.0  | 2.5                                                          | 7.0  | ns    |

| t <sub>PLZ</sub> | S <sub>n</sub> to I/O <sub>n</sub>     | 1.0 |                                                      | 5.5  | 1.5                                                          | 6.5  | 113   |

# **AC Operating Requirements**

|                    |                                                            |                   | +25°C | $T_A = 0$ °C to +70°C |     |       |

|--------------------|------------------------------------------------------------|-------------------|-------|-----------------------|-----|-------|

| Symbol             | Parameter                                                  | V <sub>CC</sub> = | +5.0V | $V_{CC} = +5.0V$      |     | Units |

|                    |                                                            | Min               | Max   | Min                   | Max |       |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                    | 8.5               |       | 8.5                   |     |       |

| t <sub>S</sub> (L) | S <sub>0</sub> or S <sub>1</sub> to CP                     | 8.5               |       | 8.5                   |     | ns    |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                     | 0                 |       | 0                     |     | 115   |

| t <sub>H</sub> (L) | S <sub>0</sub> or S <sub>1</sub> to CP                     | 0                 |       | 0                     |     |       |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                    | 5.0               |       | 5.0                   |     |       |

| t <sub>S</sub> (L) | I/O <sub>n</sub> , DS <sub>0</sub> , DS <sub>7</sub> to CP | 5.0               |       | 5.0                   |     | ns    |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                     | 2.0               |       | 2.0                   |     | 115   |

| $t_H(L)$           | I/O <sub>n</sub> , DS <sub>0</sub> , DS <sub>7</sub> to CP | 2.0               |       | 2.0                   |     |       |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                    | 10.0              |       | 10.0                  |     |       |

| t <sub>S</sub> (L) | SR to CP                                                   | 10.0              |       | 10.0                  |     |       |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                     | 0                 |       | 0                     |     | ns    |

| $t_H(L)$           | SR to CP                                                   | 0                 |       | 0                     |     |       |

| t <sub>W</sub> (H) | CP Pulse Width                                             | 5.0               |       | 5.0                   |     | ns    |

| $t_W(L)$           | HIGH or LOW                                                | 5.0               |       | 5.0                   |     | 115   |

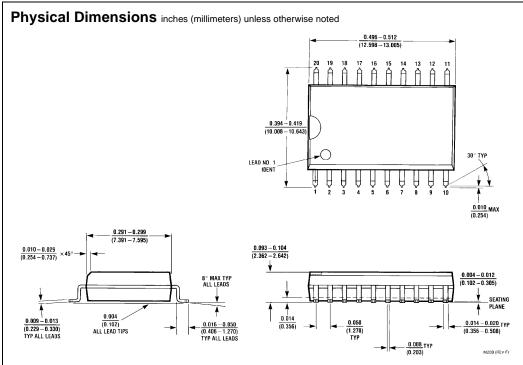

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide Package Number M20B

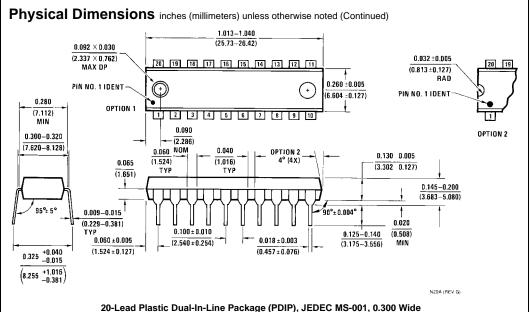

Package Number N20A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com