## FAIRCHILD

SEMICONDUCTOR TM

## 74ACT1284 IEEE 1284 Transceiver

## **General Description**

The 74ACT1284 contains four non-inverting bidirectional buffers and three non-inverting buffers with open Drain outputs and high drive capability on the B Ports. It is intended to provide a standard signaling method for a bi-direction parallel peripheral in an Extended Capabilities Port mode (ECP).

The HD (active HIGH) input pin enables the B Ports to switch from open Drain to a high drive totem pole output, capable of sourcing 14 mA on all seven buffers. The DIR input determines the direction of data flow on the bidirectional buffers. DIR (active HIGH) enables data flow from A Ports to B Ports. DIR (active LOW) enables data flow from B Ports to A Ports.

#### Features

- TTL-compatible inputs

- A Ports have standard 4 mA totem pole outputs

- Typical input hysteresis of 0.5V

- B Port high drive source/sink capability of 14 mA

- Bidirectional non-inverting buffers

- Supports IEEE P1284 Level 1 and Level 2 signaling standards for bidirectional parallel communications between personal computers and printing peripherals

June 1996

Revised November 2000

- B Port outputs in High Impedance mode during power down

- Guaranteed 4000V minimum ESD protection

## Ordering Code:

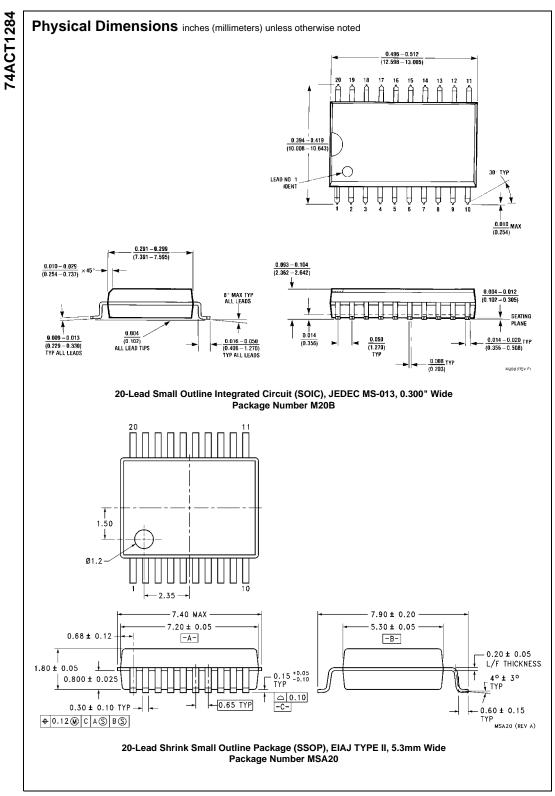

| Order Number                                                                                        | Package Number | Package Description                                                         |  |  |  |  |

|-----------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|--|--|--|--|

| 74ACT1284SC                                                                                         | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide  |  |  |  |  |

| 74ACT1284MSA                                                                                        | MSA20          | 20-Lead Shrink Small Outline Package (SSOP), EIAJ TYPE II, 5.3mm Wide       |  |  |  |  |

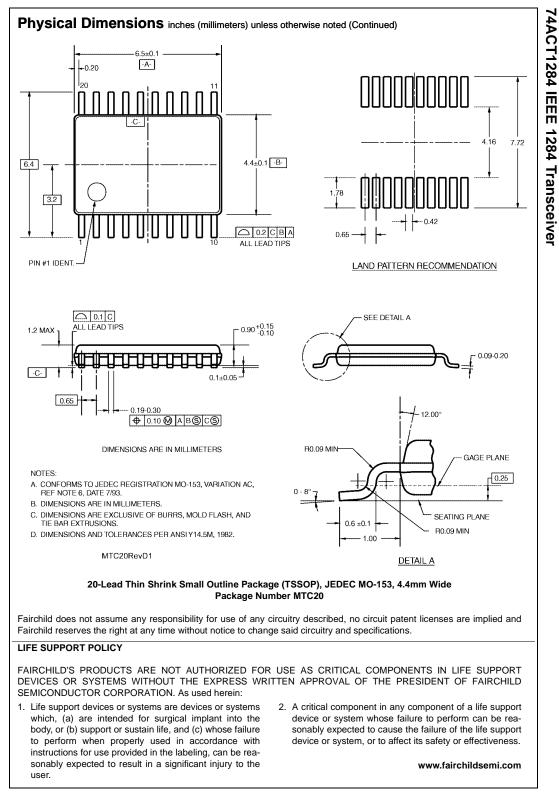

| 74ACT1284MTC                                                                                        | MTC20          | 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |  |  |  |  |

| Device also available in Tape and Real. Specify by appending suffix letter "X" to the ordering code |                |                                                                             |  |  |  |  |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code

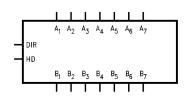

## Logic Symbol

### **Pin Descriptions**

| Pin Names                                                          | Description                           |

|--------------------------------------------------------------------|---------------------------------------|

| HD                                                                 | High Drive Enable input (Active HIGH) |

| DIR                                                                | Direction Control Input               |

| A <sub>1</sub> - A <sub>4</sub>                                    | Side A Inputs or Outputs              |

| A <sub>1</sub> - A <sub>4</sub><br>B <sub>1</sub> - B <sub>4</sub> | Side B Inputs or Outputs              |

| A <sub>5</sub> - A <sub>7</sub>                                    | Side A Inputs                         |

| B <sub>5</sub> - B <sub>7</sub>                                    | Side B Outputs                        |

### **Connection Diagram**

| A1 —             | 1  | $\bigcirc$ | 20 | — B <sub>1</sub> |

|------------------|----|------------|----|------------------|

| A <sub>2</sub> — | 2  |            | 19 | — в <sub>2</sub> |

| A3 —             | 3  |            | 18 | — В <sub>3</sub> |

| A4               | 4  |            | 17 | — В <sub>4</sub> |

| GND —            | 5  |            | 16 | -v <sub>cc</sub> |

| GND —            | 6  |            | 15 | -v <sub>cc</sub> |

| A <sub>5</sub> — | 7  |            | 14 | — В <sub>5</sub> |

| A <sub>6</sub> — | 8  |            | 13 | — В <sub>6</sub> |

| A <sub>7</sub> — | 9  |            | 12 | — В <sub>7</sub> |

| DIR —            | 10 |            | 11 | — нр             |

|                  |    |            |    |                  |

FACT<sup>™</sup> is a trademark of Fairchild Semiconductor Corporation.

© 2000 Fairchild Semiconductor Corporation DS011683

www.fairchildsemi.com

# 74ACT1284

## Truth Table

| Inp | uts | Outputs                                                                                                                                                                                                                                                                                           |  |  |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DIR | HD  | Outputs                                                                                                                                                                                                                                                                                           |  |  |

| L   | L   | $B_1$ - $B_4$ Data to $A_1$ - $A_4$ , and                                                                                                                                                                                                                                                         |  |  |

|     |     | A <sub>5</sub> - A <sub>7</sub> Data to B <sub>5</sub> - B <sub>7</sub> (Note 1)                                                                                                                                                                                                                  |  |  |

| L   | н   | $ \begin{array}{l} A_5 - A_7 \text{ Data to } B_1 - A_4, \text{ and} \\ A_5 - A_7 \text{ Data to } B_5 - B_7 \text{ (Note 1)} \\ B_1 - B_4 \text{ Data to } A_1 - A_4, \text{ and} \\ A_5 - A_7 \text{ Data to } B_5 - B_7 \\ A_1 - A_7 \text{ Data to } B_1 - B_7 \text{ (Note 2)} \end{array} $ |  |  |

|     |     | A <sub>5</sub> - A <sub>7</sub> Data to B <sub>5</sub> - B <sub>7</sub>                                                                                                                                                                                                                           |  |  |

| н   | L   | A <sub>1</sub> - A <sub>7</sub> Data to B <sub>1</sub> - B <sub>7</sub> (Note 2)                                                                                                                                                                                                                  |  |  |

| н   | н   | A <sub>1</sub> - A <sub>7</sub> Data to B <sub>1</sub> - B <sub>7</sub>                                                                                                                                                                                                                           |  |  |

Note 1: B<sub>5</sub> - B<sub>7</sub> Open Drain Outputs Note 2: B<sub>1</sub> - B<sub>7</sub> Open Drain Outputs

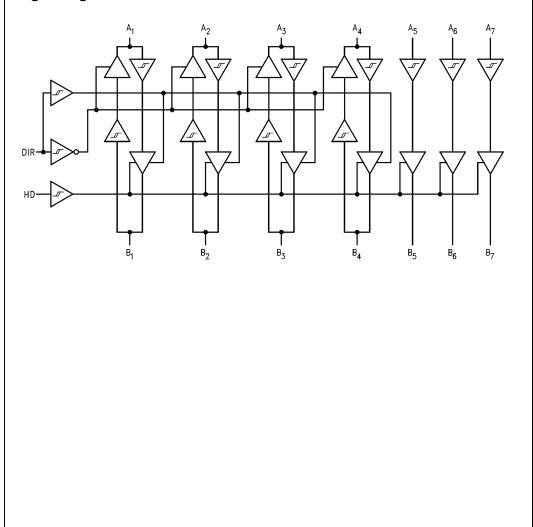

## Logic Diagram

### Absolute Maximum Ratings(Note 3)

|                                                       | U ( )                             |

|-------------------------------------------------------|-----------------------------------|

| (Note 4)                                              |                                   |

| Supply Voltage (V <sub>CC</sub> )                     | -0.5V to +7.0V                    |

| DC Input Diode Current (I <sub>IK</sub> )             |                                   |

| $V_{I} = -0.5V$                                       | –20 mA                            |

| $V_I = V_{CC} + 0.5V$                                 | +20 mA                            |

| DC Input Voltage (VI) A Side                          | –0.5V to V <sub>CC</sub> + 0.5V   |

| DC Input Voltage (VI) B Side                          | -2V to +7V                        |

| DC Output Diode Current (I <sub>OK</sub> )            |                                   |

| $V_{O} = -0.5V$                                       | –20 mA                            |

| $V_O = V_{CC} + 0.5V$                                 | +20 mA                            |

| DC Output Voltage (V <sub>O</sub> ) A Side            | –0.5V to V <sub>CC</sub> + 0.5V   |

| DC Output Voltage (V <sub>O</sub> ) B Side            | -2V to +7V                        |

| DC Output Source                                      |                                   |

| or Sink Current (I <sub>O</sub> )                     | $\pm$ 50 mA                       |

| DC V <sub>CC</sub> or Ground Current                  |                                   |

| per Output Pin (I <sub>CC</sub> or I <sub>GND</sub> ) | $\pm$ 50 mA                       |

| Storage Temperature (T <sub>STG</sub> )               | $-65^{\circ}C$ to $+150^{\circ}C$ |

|                                                       |                                   |

## Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> )       |

|-----------------------------------------|

| Input Voltage (V <sub>I</sub> )         |

| Output Voltage (V <sub>O</sub> )        |

| Operating Temperature (T <sub>A</sub> ) |

4.7V to 5.5V 0V to V<sub>CC</sub> 0V to V<sub>CC</sub> -40°C to +85°C 74ACT1284

Note 3: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT™ circuits outside databook specifications. Note 4: Either voltage limit or current limit is sufficient to protect inputs.

## **DC Electrical Characteristics**

| Sumbol            | Parameter                      | v <sub>cc</sub> | Guaranteed Limits                                                                |      |                                        |       | Conditions                                            |  |

|-------------------|--------------------------------|-----------------|----------------------------------------------------------------------------------|------|----------------------------------------|-------|-------------------------------------------------------|--|

| Symbol            | Farameter                      | (V)             | $T_{A} = +25^{\circ}C \qquad T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C  T_{A}$ |      | $T_{A}=-40^{\circ}C$ to $+85^{\circ}C$ | Units | Conditions                                            |  |

| V <sub>IH</sub>   | Minimum HIGH Level             | 4.7             | 2.0                                                                              | 2.0  | 2.0                                    | V     | Recognized                                            |  |

|                   | Input Voltage                  | 5.5             | 2.0                                                                              | 2.0  | 2.0                                    | v     | High Signal                                           |  |

| V <sub>IL</sub>   | Maximum LOW Level              | 4.7             | 0.8                                                                              | 0.8  | 0.8                                    | V     | Recognized                                            |  |

|                   | Input Voltage                  | 5.5             | 0.8                                                                              | 0.8  | 0.8                                    | v     | Low Signal                                            |  |

| V <sub>OH</sub>   | Minimum HIGH Level             |                 | 4.5                                                                              | 4.5  | 4.5                                    |       | I <sub>OUT</sub> = -50 μA (An)                        |  |

|                   | Output Voltage                 | 4.7             |                                                                                  |      |                                        | v     | $V_{IN} = V_{IL} \text{ or } V_{IH} \text{ (Note 5)}$ |  |

|                   |                                | 4.7             | 3.7                                                                              | 3.7  | 3.7                                    |       | $I_{OH} = -4 \text{ mA} (A_n)$                        |  |

|                   |                                |                 | 2.4                                                                              | 2.4  | 2.4                                    |       | $I_{OH} = -14 \text{ mA} (B_n)$                       |  |

| V <sub>OL</sub>   | Maximum LOW Level              |                 | 0.2                                                                              | 0.2  | 0.2                                    |       | I <sub>OUT</sub> = 50 μA (An)                         |  |

|                   | Output Voltage                 | 4.7             |                                                                                  |      |                                        | v     | $V_{IN} = V_{IL} \text{ or } V_{IH} \text{ (Note 5)}$ |  |

|                   |                                | 4.7             | 0.4                                                                              | 0.4  | 0.4                                    |       | $I_{OH} = 4 \text{ mA} (A_n)$                         |  |

|                   |                                |                 |                                                                                  |      |                                        |       | I <sub>OH</sub> = 14 mA (B <sub>n</sub> )             |  |

| I <sub>IN</sub>   | Maximum Input                  | 5.5             |                                                                                  | ±0.1 | ±1.0                                   | μA    | $V_I = V_{CC}$ , GND                                  |  |

|                   | Leakage Current                | 5.5             |                                                                                  | ±0.1 | 1.0                                    | μА    | (DIR, A5, A6, A7, HD)                                 |  |

| ICCT              | Maximum I <sub>CC</sub> /Input | 5.5             |                                                                                  | 1.5  | 1.5                                    | mA    | $V_I = V_{CC} - 2.1V$                                 |  |

| I <sub>CC</sub>   | Maximum Quiescent              | 5.5             | 400                                                                              | 400  | 500                                    |       | $V_{IN} = V_{CC}$ or GND                              |  |

|                   | Supply Current                 | 5.5             | 400                                                                              | 400  | 500                                    | μΛ    | $v_{IN} = v_{CC}$ or GND                              |  |

| I <sub>OZ</sub>   | Maximum Output                 | 5.5             | ±20                                                                              | ±20  | ±20                                    |       | $V_0 = V_{CC_1}$ GND                                  |  |

|                   | Leakage Current                | 5.5             | 120                                                                              | ±20  | ±20                                    | μA    | $v_0 = v_{CC}$ , GND                                  |  |

| I <sub>OFF</sub>  | Maximum B-Side Power Down      | 0.0             | 100                                                                              | 100  | 100                                    | μA    | V <sub>OUT</sub> = 5.25V                              |  |

|                   | Leakage Current                | 0.0             | 100                                                                              | 100  | 100                                    | μΛ    | VOUT - 3.23V                                          |  |

| $\Delta_{\rm VT}$ | Input Hysteresis               | 5.0             | 0.4                                                                              | 0.4  | 0.35                                   | V     | $V_T + - V_T -$                                       |  |

| R <sub>D</sub>    | Maximum Output Impedance       | 5.0             | 22                                                                               | 22   | 24                                     | Ω     | B <sub>n</sub> (Note 6)                               |  |

|                   | Minimum Output Impedance       | 5.0             | 8                                                                                | 8    | 6                                      | Ω     | B <sub>n</sub> (Note 6)                               |  |

Note 5: All outputs loaded; thresholds on input associated with output under test.

Note 6: This parameter is guaranteed but not tested, characterized only: RD is the measure of the B-Side output impedance with the output in the HIGH state.

74ACT1284

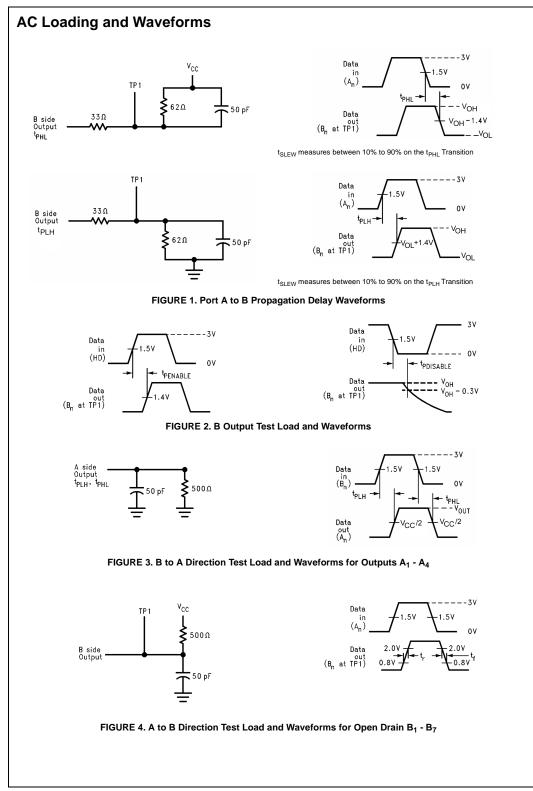

## **AC Electrical Characteristics**

| Symbol                          | Parameter                                                          | <b>T</b> <sub>A</sub> = | $T_A = +25^{\circ}C$<br>$V_{CC} = 4.7V - 5.5V$ |      | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ $V_{CC} = 4.7V - 5.5V$ |      | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ $V_{CC} = 4.7V - 5.5V$ |      | Figure<br>Number |

|---------------------------------|--------------------------------------------------------------------|-------------------------|------------------------------------------------|------|--------------------------------------------------------------------|------|----------------------------------------------------------------------|------|------------------|

|                                 |                                                                    | $V_{CC} = 4.$           |                                                |      |                                                                    |      |                                                                      |      |                  |

|                                 |                                                                    | Min                     | Max                                            | Min  | Max                                                                | Min  | Max                                                                  | 1    |                  |

| t <sub>PHL</sub>                | A <sub>1</sub> - A <sub>7</sub> to B <sub>1</sub> - B <sub>7</sub> | 2.0                     | 20.0                                           | 2.0  | 20.0                                                               | 2.0  | 24.0                                                                 | ns   | Figure 1         |

| t <sub>PLH</sub>                | A <sub>1</sub> - A <sub>7</sub> to B <sub>1</sub> - B <sub>7</sub> | 2.0                     | 20.0                                           | 2.0  | 20.0                                                               | 2.0  | 24.0                                                                 | ns   | Figure 2         |

| t <sub>PHL</sub>                | B <sub>1</sub> - B <sub>4</sub> to A <sub>1</sub> - A <sub>4</sub> | 2.0                     | 20.0                                           | 2.0  | 20.0                                                               | 2.0  | 24.0                                                                 | ns   | Figure 3         |

| t <sub>PLH</sub>                | B <sub>1</sub> - B <sub>4</sub> to A <sub>1</sub> - A <sub>4</sub> | 2.0                     | 20.0                                           | 2.0  | 20.0                                                               | 2.0  | 24.0                                                                 | ns   | Figure 3         |

| t <sub>pEnable</sub>            | Output Enable Time<br>HD to B <sub>1</sub> - B <sub>7</sub>        | 2.0                     | 20.0                                           | 2.0  | 20.0                                                               | 2.0  | 24.0                                                                 | ns   | Figure 2         |

| t <sub>pDisable</sub>           | Output Disable Time<br>HD to B <sub>1</sub> - B <sub>7</sub>       | 2.0                     | 20.0                                           | 2.0  | 20.0                                                               | 2.0  | 24.0                                                                 | ns   | Figure 2         |

| t <sub>SKEW</sub>               | Output Slew Rate                                                   |                         |                                                |      |                                                                    |      |                                                                      |      |                  |

| t <sub>PLH</sub>                | B <sub>1</sub> - B <sub>7</sub>                                    | 0.05                    | 0.40                                           | 0.05 | 0.40                                                               | 0.05 | 0.40                                                                 | V/ns | Figures<br>1, 2  |

| t <sub>PHL</sub>                |                                                                    |                         |                                                |      |                                                                    |      |                                                                      |      | ., _             |

| t <sub>r</sub> , t <sub>f</sub> | t <sub>RISE</sub> and t <sub>FALL</sub>                            |                         | 120                                            |      | 120                                                                |      | 120                                                                  | ns   | Figure 4         |

|                                 | B <sub>1</sub> - B <sub>7</sub> (Note 7)                           |                         | 120                                            | 120  | 120                                                                | 115  | (Note 8)                                                             |      |                  |

Note 7: Open Drain

Note 8: This parameter is guaranteed but not tested, characterized only.

Note: Pulse Generator for all pulses; Rate  $\leq$  1.0 MHz; A\_{O}  $\leq$  500; t\_{f}  $\leq$  2.5 ns, t\_{r}  $\leq$  2.5 ns.

### Capacitance

| Symbol           | Parameter           | Parameter Typ |    | Conditions                          |  |

|------------------|---------------------|---------------|----|-------------------------------------|--|

| CIN              | Input Capacitance   | 4.0           | pF | $V_{CC} = OPEN (HD, DIR A_5 - A_7)$ |  |

| C <sub>I/O</sub> | I/O Pin Capacitance | 12.0          | pF | $V_{CC} = 5.0V$                     |  |

74ACT1284

www.fairchildsemi.com

www.fairchildsemi.com

6

www.fairchildsemi.com