October 1993 Revised January 1999

## 74ABT16543 16-Bit Registered Transceiver with 3-STATE Outputs

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

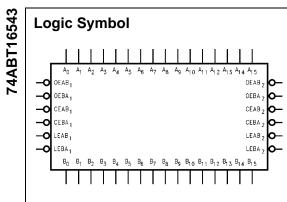

The ABT16543 16-bit transceiver contains two sets of Dtype latches for temporary storage of data flowing in either direction. Separate Latch Enable and Output Enable inputs are provided for each register to permit independent control of inputting and outputting in either direction of data flow. Each byte has separate control inputs, which can be shorted together for full 16-bit operation.

#### Features

- Back-to-back registers for storage

- Bidirectional data path

- A and B outputs have current sourcing capability of 32 mA and current sinking capability of 64 mA

- Separate control logic for each byte

- 16-bit version of the ABT543

- Separate controls for data flow in each direction

- Guaranteed latchup protection

- High impedance glitch free bus loading during entire power up and power down cycle

- Nondestructive hot insertion capability

#### **Ordering Code:**

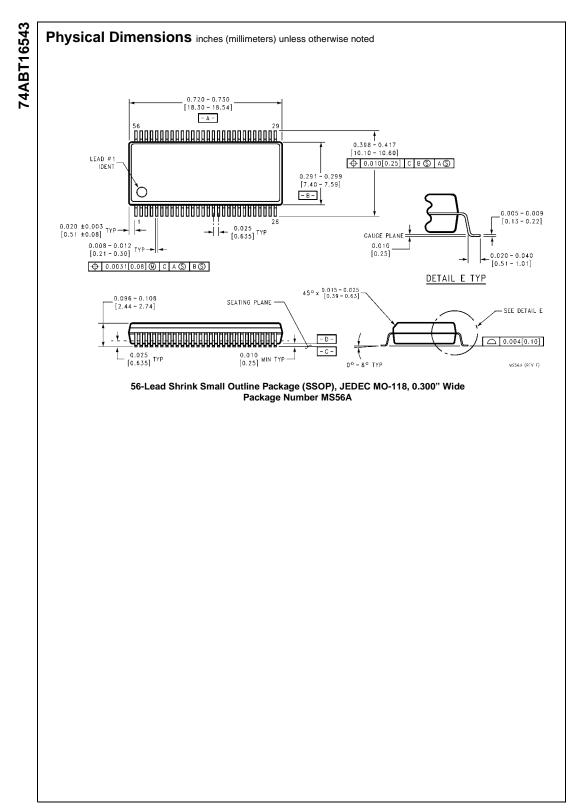

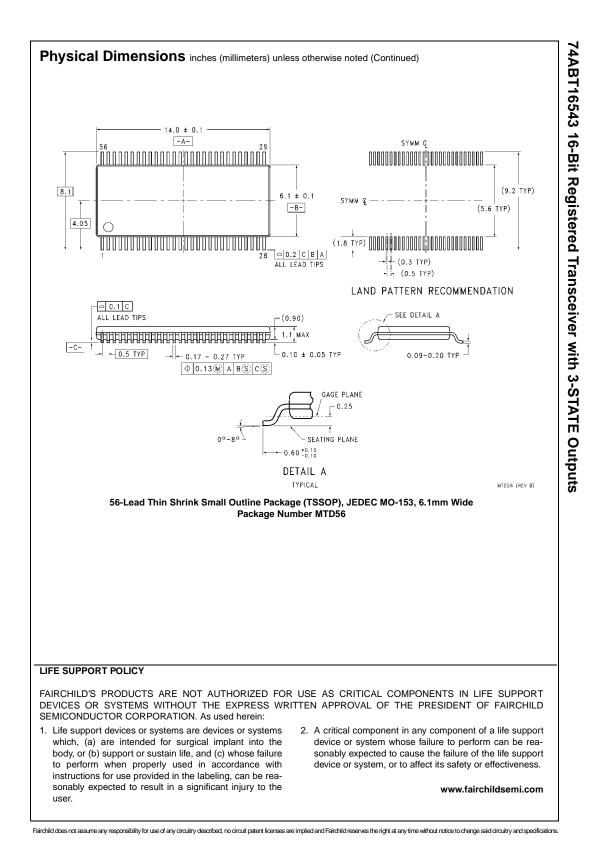

|                                                                                                          | Order Number         | Package Number | Package Description                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------------------------------------------------------------|--|--|--|

|                                                                                                          | 74ABT16543CSSC       | MS56A          | 56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300" Wide      |  |  |  |

|                                                                                                          | 74ABT16543CMTD MTD56 |                | 56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |  |  |  |

| Devices also available on Tana and Real. Specify by appending the suffix latter "V" to the ordering code |                      |                |                                                                             |  |  |  |

Devices also available on Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

#### **Connection Diagram**

#### **Pin Descriptions**

| Pin Names                       | Description                             |

|---------------------------------|-----------------------------------------|

| OEAB                            | A-to-B Output Enable Input (Active LOW) |

| OEBAn                           | B-to-A Output Enable Input (Active LOW) |

| CEAB                            | A-to-B Enable Input (Active LOW)        |

| CEBAn                           | B-to-A Enable Input (Active LOW)        |

| LEAB <sub>n</sub>               | A-to-B Latch Enable Input (Active LOW)  |

| LEBAn                           | B-to-A Latch Enable Input (Active LOW)  |

| A <sub>0</sub> -A <sub>15</sub> | A-to-B Data Inputs or                   |

|                                 | B-to-A 3-STATE Outputs                  |

| B <sub>0</sub> -B <sub>15</sub> | B-to-A Data Inputs or                   |

|                                 | A-to-B 3-STATE Outputs                  |

|                                 |                                         |

74ABT16543 16-Bit Registered Transceiver with 3-STATE Outputs

© 1999 Fairchild Semiconductor Corporation DS011646.prf

#### **Data I/O Control Table**

|                   | Inputs            |                   | Latch Status | Output Buffers |  |

|-------------------|-------------------|-------------------|--------------|----------------|--|

| CEAB <sub>n</sub> | LEAB <sub>n</sub> | OEAB <sub>n</sub> | (Byte n)     | (Byte n)       |  |

| Н                 | Х                 | Х                 | Latched      | HIGH Z         |  |

| Х                 | н                 | Х                 | Latched      | —              |  |

| L                 | L                 | Х                 | Transparent  | _              |  |

| х                 | Х                 | н                 | _            | HIGH Z         |  |

| L                 | Х                 | L                 | —            | Driving        |  |

H = HIGH Voltage Level

L = LOW Voltage Level X = Immaterial

A-to-B data flow shown;

B-to-A flow control is the same, except using  $\overline{\text{CEBA}}_n, \overline{\text{LEBA}}_n$  and  $\overline{\text{OEBA}}_n$

#### **Functional Description**

The ABT16543 contains two sets of D-type latches, with separate input and output controls for each. For data flow from A to B, for example, the A to B Enable (CEAB) input must be low in order to enter data from the A port or take data from the B-Port as indicated in the Data I/O Control Table. With CEAB low, a low signal on (LEAB) input makes the A to B latches transparent; a subsequent low to high transition of the LEAB line puts the A latches in the storage

mode and their outputs no longer change with the A inputs. With  $\overrightarrow{CEAB}$  and  $\overrightarrow{OEAB}$  both low, the B output buffers are active and reflect the data present on the output of the A latches. Control of data flow from B to A is similar, but using the  $\overrightarrow{CEBA}$ ,  $\overrightarrow{LEBA}$  and  $\overrightarrow{OEBA}$ . Each byte has separate control inputs, allowing the device to be used as two 8-bit transceivers or as one 16-bit transceiver.

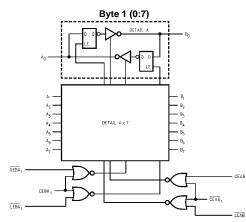

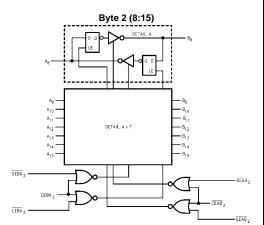

#### Logic Diagrams

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

### Absolute Maximum Ratings(Note 1)

|                                  |                                      | C        |

|----------------------------------|--------------------------------------|----------|

| Storage Temperature              | -65°C to +150°C                      | C        |

| Ambient Temperature under Bias   | -55°C to +125°C                      | R        |

| Junction Temperature under Bias  | -55°C to +150°C                      | C        |

| V <sub>CC</sub> Pin Potential to |                                      | Ŭ        |

| Ground Pin                       | -0.5V to +7.0V                       | F        |

| Input Voltage (Note 2)           | -0.5V to +7.0V                       | 5        |

| Input Current (Note 2)           | -30 mA to +5.0 mA                    | Ν        |

| Voltage Applied to Any Output    |                                      |          |

| in the Disable or                |                                      |          |

| Power-Off State                  | -0.5V to +5.5V                       |          |

| in the HIGH State                | -0.5V to V <sub>CC</sub>             | No       |

| Current Applied to Output        |                                      | ma<br>un |

| in LOW State (Max)               | twice the rated I <sub>OL</sub> (mA) | No       |

|                                  |                                      |          |

DC Latchup Source Current Over Voltage Latchup (I/O)

# Recommended Operating Conditions

| Free Air Ambient Temperature                                                                                                       | $-40^{\circ}C$ to $+85^{\circ}C$ |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Supply Voltage                                                                                                                     | +4.5V to +5.5V                   |

| Minimum Input Edge Rate (ΔV/Δt)                                                                                                    |                                  |

| Data Input                                                                                                                         | 50 mV/ns                         |

| Enable Input                                                                                                                       | 20 mV/ns                         |

| Clock Input                                                                                                                        | 100 mV/ns                        |

| Note 1: Absolute maximum ratings are value<br>may be damaged or have its useful life imp<br>under these conditions is not implied. | ,                                |

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

## **DC Electrical Characteristics**

| Symbol                             | Parameter                         | Min  | Тур | Мах  | Units  | v <sub>cc</sub> | Conditions                                                                    |

|------------------------------------|-----------------------------------|------|-----|------|--------|-----------------|-------------------------------------------------------------------------------|

| VIH                                | Input HIGH Voltage                | 2.0  |     |      | V      |                 | Recognized HIGH Signal                                                        |

| V <sub>IL</sub>                    | Input LOW Voltage                 |      |     | 0.8  | V      |                 | Recognized LOW Signal                                                         |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage         |      |     | -1.2 | V      | Min             | I <sub>IN</sub> = -18 mA (Non I/O Pins)                                       |

| V <sub>OH</sub>                    | Output HIGH Voltage               | 2.5  |     |      |        |                 | $I_{OH} = -3 \text{ mA}, (A_n, B_n)$                                          |

|                                    |                                   | 2.0  |     |      |        |                 | I <sub>OH</sub> = -32 mA, (A <sub>n</sub> , B <sub>n</sub> )                  |

| V <sub>OL</sub>                    | Output LOW Voltage                |      |     | 0.55 | V      | Min             | $I_{OL} = 64 \text{ mA}, (A_n, B_n)$                                          |

| V <sub>ID</sub>                    | Input Leakage Test                | 4.75 |     |      | V      | 0.0             | I <sub>ID</sub> = 1.9 μA, (Non-I/O Pins)<br>All Other Pins Grounded           |

| IIH                                | Input HIGH Current                |      |     | 1    | μA     | Max             | V <sub>IN</sub> = 2.7V (Non-I/O Pins) ((Note 3)                               |

|                                    |                                   |      |     | 1    |        |                 | $V_{IN} = V_{CC}$ (Non-I/O Pins)                                              |

| I <sub>BVI</sub>                   | Input HIGH Current Breakdown Test |      |     | 7    | μA     | Max             | $V_{IN} = 7.0V$ (Non-I/O Pins)                                                |

| IBVIT                              | Input HIGH Current                |      |     | 100  | μA     | Max             | $V_{IN} = 5.5V (A_n, B_n)$                                                    |

|                                    | Breakdown Test (I/O)              |      |     |      |        |                 |                                                                               |

| IIL                                | Input LOW Current                 |      |     | -1   | μA     | Max             | V <sub>IN</sub> = 0.5V (Non-I/O Pins) (Note 3)                                |

|                                    |                                   |      |     | -1   |        |                 | V <sub>IN</sub> = 0.0V (Non-I/O Pins)                                         |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current            |      |     | 10   | μA     | 0V-5.5V         | $V_{OUT} = 2.7V (A_n, B_n);$                                                  |

|                                    |                                   |      |     |      |        |                 | $\overline{OEAB}$ or $\overline{CEAB} = 2V$                                   |

| I <sub>IL</sub> + I <sub>OZL</sub> | Output Leakage Current            |      |     | -10  | μA     | 0V-5.5V         | $V_{OUT} = 0.5V (A_n, B_n);$                                                  |

|                                    |                                   |      |     |      |        |                 | $\overline{OEAB}$ or $\overline{CEAB} = 2V$                                   |

| I <sub>OS</sub>                    | Output Short-Circuit Current      | -100 |     | -275 | mA     | Max             | $V_{OUT} = 0V (A_n, B_n)$                                                     |

| I <sub>CEX</sub>                   | Output HIGH Leakage Current       |      |     | 50   | μA     | Max             | $V_{OUT} = V_{CC} (A_n, B_n)$                                                 |

| I <sub>ZZ</sub>                    | Bus Drainage Test                 |      |     | 100  | μA     | 0.0V            | V <sub>OUT</sub> = 5.5V (A <sub>n</sub> , B <sub>n</sub> ); All Others GND    |

| I <sub>CCH</sub>                   | Power Supply Current              |      |     | 1.0  | mA     | Max             | All Outputs HIGH                                                              |

| I <sub>CCL</sub>                   | Power Supply Current              |      |     | 60   | mA     | Max             | All Outputs LOW                                                               |

| I <sub>CCZ</sub>                   | Power Supply Current              |      |     | 1.0  | mA     | Max             | Outputs 3-STATE                                                               |

|                                    |                                   |      |     |      |        |                 | All Others at $V_{CC}$ or GND                                                 |

| I <sub>CCT</sub>                   | Additional I <sub>CC</sub> /Input |      |     | 2.5  | mA     | Max             | $V_I = V_{CC} - 2.1V$                                                         |

|                                    | <u> </u>                          |      |     |      |        |                 | All Others at $V_{CC}$ or GND                                                 |

| I <sub>CCD</sub>                   | Dynamic I <sub>CC</sub> No Load   |      |     |      |        |                 | Outputs Open, $\overline{CEAB}$ , $\overline{OEAB}$ , $\overline{LEAB} = GND$ |

|                                    | (Note 3)                          |      |     | 0.25 | mA/MHz | Max             | $\overline{CEBA} = V_{CC}$ , One Bit Toggling,                                |

|                                    |                                   |      |     |      |        |                 | 50% Duty Cycle                                                                |

74ABT16543

–500 mA 10V

74ABT16543

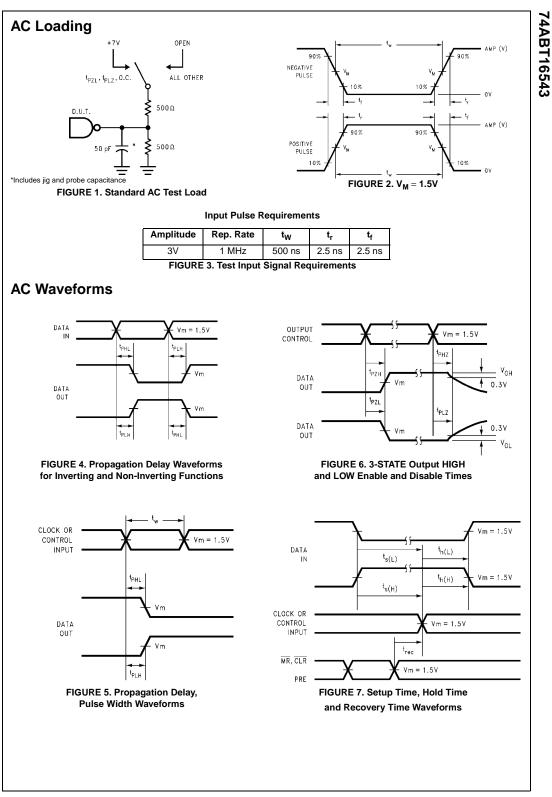

## **AC Electrical Characteristics**

| Symbol           | Parameter                                                                                                             |     | $T_{A} = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_{L} = 50 \text{ pF}$ |     |     | $T_A = -55^{\circ}C \text{ to } +85^{\circ}C$<br>$V_{CC} = 4.5V - 5.5V$<br>$C_L = 50 \text{ pF}$ |    |

|------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------|-----|-----|--------------------------------------------------------------------------------------------------|----|

|                  |                                                                                                                       | Min | Тур                                                             | Max | Min | Max                                                                                              |    |

| t <sub>PLH</sub> | Propagation Delay                                                                                                     | 1.5 | 3.0                                                             | 5.7 | 1.5 | 5.7                                                                                              | ns |

| t <sub>PHL</sub> | A <sub>n</sub> to B <sub>n</sub> or B <sub>n</sub> to A <sub>n</sub>                                                  |     |                                                                 |     |     |                                                                                                  |    |

| t <sub>PLH</sub> | Propagation Delay                                                                                                     | 1.5 | 3.0                                                             | 5.5 | 1.5 | 5.5                                                                                              | ns |

| t <sub>PHL</sub> | $\overline{\text{LEAB}}_{\overline{n}}$ to B <sub>n</sub> , $\overline{\text{LEBA}}_{\overline{n}}$ to A <sub>n</sub> |     |                                                                 |     |     |                                                                                                  |    |

| t <sub>PZH</sub> | Enable Time                                                                                                           | 1.5 | 2.8                                                             | 5.2 | 1.5 | 5.2                                                                                              | ns |

| t <sub>PZL</sub> | $\overline{OEBA_n}$ or $\overline{OEAB_n}$ to $A_n$ or $B_n$                                                          |     |                                                                 |     |     |                                                                                                  |    |

| t <sub>PHZ</sub> | Disable Time                                                                                                          | 1.6 | 3.1                                                             | 6.0 | 1.6 | 6.0                                                                                              | ns |

| t <sub>PLZ</sub> | $\overline{OEAB}_n$ or $\overline{OEBA}_n$ to $A_n$ or $B_n$                                                          |     |                                                                 |     |     |                                                                                                  |    |

| t <sub>PZH</sub> | Enable Time                                                                                                           | 1.5 | 3.1                                                             | 6.2 | 1.5 | 6.2                                                                                              | ns |

| t <sub>PZL</sub> | $\overline{\text{CEBA}}_n$ or $\overline{\text{CEAB}}_n$ to $A_n$ or $B_n$                                            |     |                                                                 |     |     |                                                                                                  |    |

| t <sub>PHZ</sub> | Disable Time                                                                                                          | 1.7 | 3.2                                                             | 6.3 | 1.7 | 6.3                                                                                              | ns |

| t <sub>PLZ</sub> | $\overline{CEBA}_n$ or $\overline{CEAB}_n$ to $A_n$ or $B_n$                                                          |     |                                                                 |     |     |                                                                                                  |    |

## AC Operating Requirements

(SSOP Package)

| Symbol             | Parameter                                                    | $T_A = +25^{\circ}C$ $V_{CC} = +5.0V$ $C_L = 50 \text{ pF}$ |     | $T_A = -55^{\circ}C \text{ to } +85^{\circ}C$<br>$V_{CC} = 4.5V - 5.5V$<br>$C_L = 50 \text{ pF}$ |     | Units |

|--------------------|--------------------------------------------------------------|-------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------|-----|-------|

|                    |                                                              | Min                                                         | Max | Min                                                                                              | Max |       |

| t <sub>S</sub> (H) | Setup Time, HIGH or LOW                                      | 2.0                                                         |     | 2.0                                                                                              |     | ns    |

| t <sub>S</sub> (L) | $A_n$ or $B_n$ to $\overline{LEBA_n}$ or $\overline{LEAB_n}$ | 2.0                                                         |     | 2.0                                                                                              |     |       |

| t <sub>H</sub> (H) | Hold Time, HIGH or LOW                                       | 1.0                                                         |     | 1.0                                                                                              |     | ns    |

| t <sub>H</sub> (L) | $A_n$ or $B_n$ to $\overline{LEBA_n}$ or $\overline{LEAB_n}$ | 1.0                                                         |     | 1.0                                                                                              |     |       |

| t <sub>W</sub> (L) | Pulse Width, LOW                                             | 3.0                                                         |     | 3.0                                                                                              |     | ns    |

## Capacitance

| Symbol                    | Parameter          | Тур  | Units | Conditions<br>T <sub>A</sub> = 25°C |

|---------------------------|--------------------|------|-------|-------------------------------------|

| C <sub>IN</sub>           | Input Capacitance  | 5.0  | pF    | V <sub>CC</sub> = 0V (non I/O pins) |

| C <sub>I/O</sub> (Note 4) | Output Capacitance | 11.0 | pF    | $V_{CC} = 5.0V (A_n, B_n)$          |

Note 4:  $C_{I/O}$  is measured at frequency, f = 1 MHz, per MIL-STD-883, Method 3012.