### Freescale Semiconductor Technical Data

Document Number: MMA6222EG Rev 1, 10/2008

**MMA6222EG**

**MMA6255EG**

**√**RoHS

# Digital Dual Axis Micromachined Accelerometer

The MMA62XXEG is a two-axis member of Freescale's family of SPI-compatible accelerometers. These devices incorporate digital signal processing for filtering, trim and data formatting.

#### Features

- Available in ±20/20g, ±50/50g, or ±100/100g versions. Additional g-ranges between 20 and 100g may be available upon request

- · Full-scale range is independently specified for each axis

- 400 Hz low-pass filter, 0.1 Hz high-pass filter, 4-pole, 16 μs sample time, additional filter options are available

- Ratiometric analog voltage output

- 10-bit digital signed data output

- SPI-compatible serial interface

- · Capture/hold input for system-wide synchronization support

- 3.3 or 5 V single supply operation

- · On-chip temperature sensor and voltage regulator

- Bidirectional internal self-test

- Minimal external component requirements

- Pb-free 20-pin SOIC package

- Automotive AEC-Q100 qualified

#### **Typical Applications**

- Crash detection (Airbag)

- Impact and vibration monitoring

- Shock detection

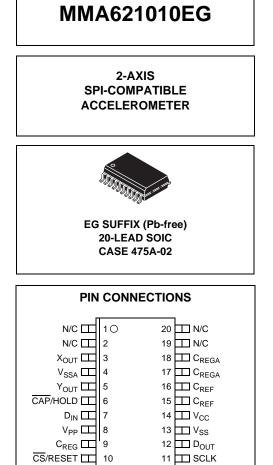

MMA621010EGR2

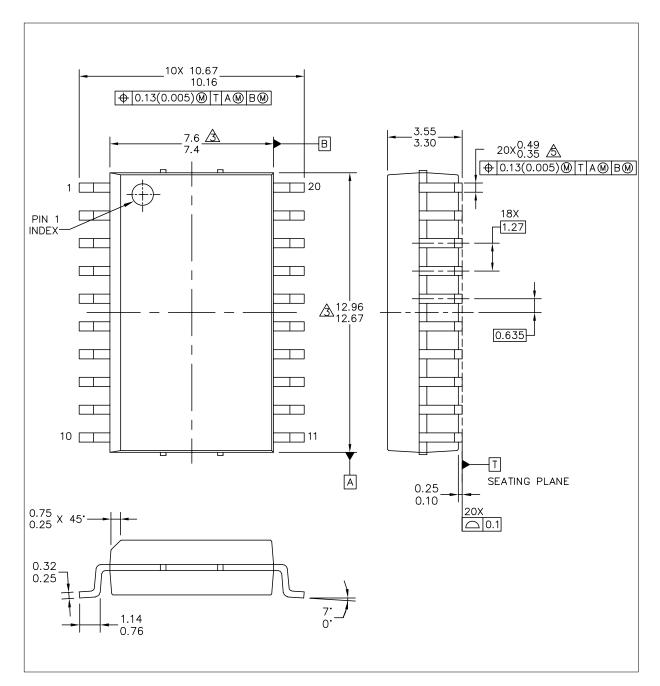

20-PIN SOIC PACKAGE

475A-02

|                      |                |                |                      | N/C: NO INTERNA | LCONNECTION |  |  |  |  |  |  |

|----------------------|----------------|----------------|----------------------|-----------------|-------------|--|--|--|--|--|--|

| Γ                    |                |                |                      |                 |             |  |  |  |  |  |  |

| ORDERING INFORMATION |                |                |                      |                 |             |  |  |  |  |  |  |

| Device Name          | X-Axis g-Level | Y-Axis g-Level | Temperature<br>Range | Package         | Packaging   |  |  |  |  |  |  |

| MMA6222EG            | 20             | 20             | -40 to +105°C        | 475A-02         | Tubes       |  |  |  |  |  |  |

| MMA6222EGR2          | 20             | 20             | -40 to +105°C        | 475A-02         | Tape & Reel |  |  |  |  |  |  |

| MMA6255EG            | 50             | 50             | -40 to +105°C        | 475A-02         | Tubes       |  |  |  |  |  |  |

| MMA6255EGR2          | 50             | 50             | -40 to +105°C        | 475A-02         | Tape & Reel |  |  |  |  |  |  |

| MMA621010EG          | 100            | 100            | -40 to +105°C        | 475A-02         | Tubes       |  |  |  |  |  |  |

-40 to +105°C

Tape & Reel

100

100

Note: If one axis of the MMA62XXEG sensor is expected to be used as a confirmation of the other axis, Freescale recommends that MMA62XXEG used in conjunction with an additional sensing/safing device for each axis.

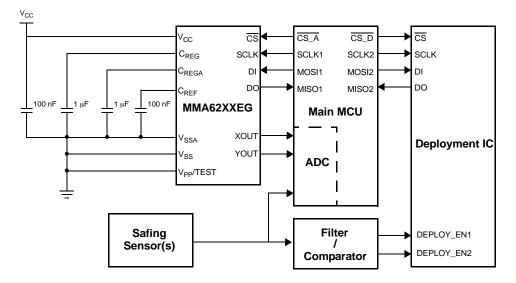

Figure 1-1 Simplified Airbag Application Diagram

### 1.1 INTRODUCTION

The MMA62XXEG is intended for applications which utilize serial communications as the primary data transfer mechanism. In addition, an analog output with lower accuracy is available.

Device serial number, acceleration range, filter characteristics and status information are available along with acceleration data via the SPI interface. A pair of digital-to-analog converters is enabled to provide ratiometric voltage outputs in addition to the digital acceleration value accessible via the SPI.

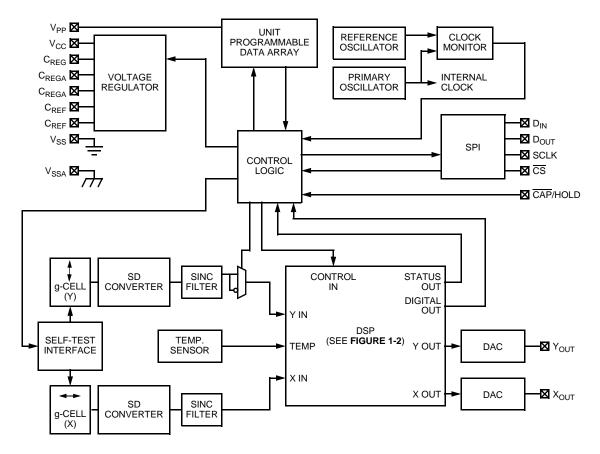

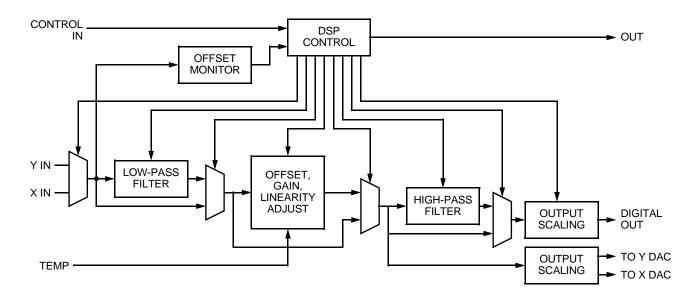

## 1.2 BLOCK DIAGRAM

A block diagram illustrating the major components of the design is shown in Figure 1-2.

Figure 1-3 MMA62XXEG DSP Block Diagram NOTE: Models of signal chain are available upon request.

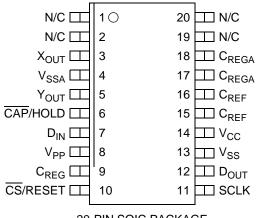

### 1.3 PIN FUNCTIONS

The pinout for the MMA62XXEG device is illustrated in Figure 1-4. Pin functions are described below. When self-test is active, the output becomes more positive in both axes if ST1 is cleared, or more negative in both axes if ST1 is set, as described in Section 3.1.1.

20-PIN SOIC PACKAGE

#### N/C: NO INTERNAL CONNECTION

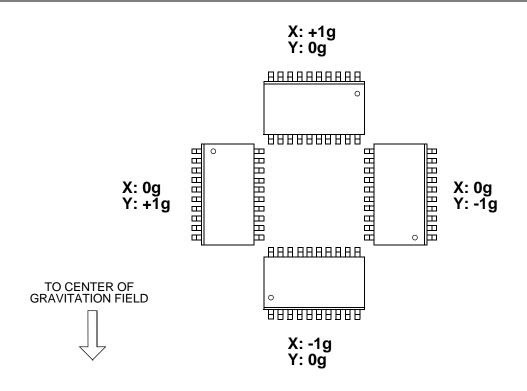

### Response to static orientation within 1g field.

Figure 1-4 MMA62XXEG Pinout

### 1.4 PIN FUNCTION DESCRIPTIONS

### 1.4.1 V<sub>CC</sub>

This pin supplies power to the device. Careful printed wiring board layout and capacitor placement is critical to ensure best performance. An external bypass capacitor between this pin and  $V_{SS}$  is required, as described in Section 1.5.

### 1.4.2 V<sub>SS</sub>

This pin is the power supply return node for the digital circuitry on the MMA62XXEG device.

### 1.4.3 V<sub>SSA</sub>

This pin is the power supply return node for analog circuitry on the MMA62XXAEG device. An external bypass capacitor between this pin and  $V_{CC}$  is required, as described in Section 1.5.

### 1.4.4 C<sub>REG</sub>

This pin is connected to the internal digital circuitry power supply rail. An external filter capacitor must be connected between this pin and  $V_{SS}$ , as described in Section 1.5.

### 1.4.5 C<sub>REGA</sub>

These pins are connected in parallel to the internal analog circuitry power supply rail. One or two external filter capacitors must be connected between these pins and  $V_{SSA}$ , as described in Section 1.5. Two pins are provided to support redundant connection to the printed wiring board assembly. Redundant external capacitors may be connected to these pins for maximum reliability, as described in Section 1.5.

#### 1.4.6 C<sub>REF</sub>

These pins are connected in parallel to an internal reference voltage node utilized by the analog circuitry. One or two external filter capacitors must be connected between these pins and  $V_{SSA}$ , as described shown in Section 1.5. Two pins are provided to support redundant connection to the printed wiring board assembly. Redundant external capacitors may be connected to these pins for maximum reliability, as described in Section 1.5.

#### 1.4.7 VPP

This pin should be tied directly to V<sub>SS</sub>.

### 1.4.8 SCLK

This input pin provides the serial clock to the SPI port. The state of this pin is also used as a qualifier for externally-controlled reset. An internal pull-down device is connected to this pin. This input may be left unconnected unless it is desired to initiate device reset as described in Section 1.4.9.

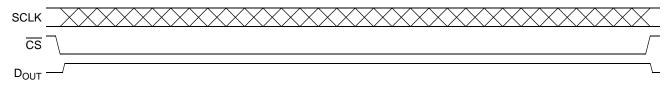

### 1.4.9 CS/RESET

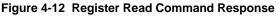

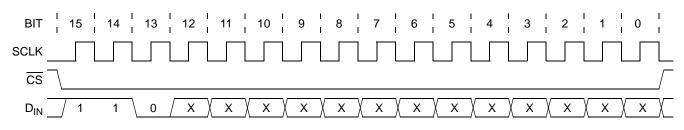

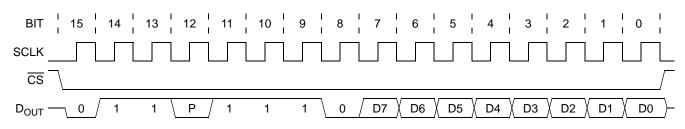

This pin provides two functions. When the SPI is enabled, this pin functions as the chip select input for the SPI port. The state of the  $D_{IN}$  pin during low-to-high transitions of SCLK is latched internally and  $D_{OUT}$  is enabled when  $\overline{CS}$  is at a logic low level.

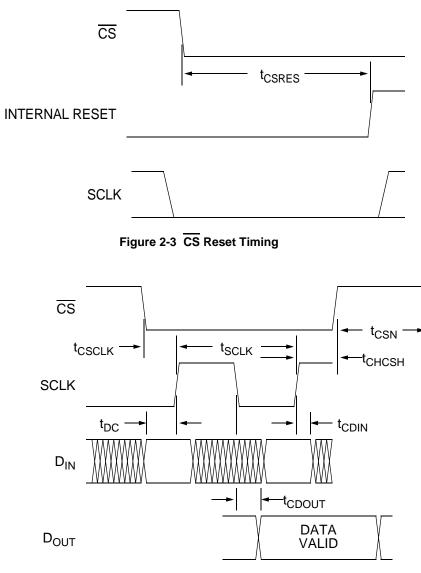

This pin may also be used to initiate a hardware reset. If  $\overline{CS}$  is held low and SCLK is held high for 512  $\mu$ s, the internal reset signal is asserted.

An internal pull-up device is connected to this pin.

### 1.4.10 D<sub>OUT</sub>

This pin functions as the serial data output for the SPI port.

Immediately following device reset,  $D_{OUT}$  is placed in a high impedance state for approximately 800  $\mu$ s. At the end of this time,  $D_{OUT}$  is driven high and a 3ms stabilization delay required by the internal circuitry begins. Reset is reported by the device so the system can be aware of potential difficulties if unexpected resets occur.

### 1.4.11 D<sub>IN</sub>

This pin functions as the serial data input to the SPI.

### 1.4.12 CAP/HOLD

When this input pin is low, the SPI acceleration result registers are updated by the DSP whenever a data sample becomes available. Upon a low-to-high transition of CAP/HOLD, the contents of the acceleration result registers are frozen. The result registers will not be updated so long as this pin remains at a logic '1' level. This pin may be tied directly to  $V_{SS}$  if the hold function is not desired.

### 1.4.13 X<sub>OUT</sub>, Y<sub>OUT</sub>

Two Digital-to-Analog Converters (DACs) translate output of the DSP block into voltage levels proportional to the magnitude of the numerical result and ratiometric to  $V_{CC}$ . The DAC outputs have an inherent accuracy of about ±12%.

### 1.5 EXTERNAL COMPONENTS

The connections illustrated below are recommended. Careful printed wiring board layout and component placement is essential for best performance. Low ESR capacitors must be connected to  $C_{REG}$  and  $C_{REGA}$  pins for the best performance. A grounded land area with solder mask should be placed under the package for improved shielding of the device from external effects. If a land area is not provided, no signals should be routed beneath the package. See Figure 1-1.

#### MMA6222EG

Sensors

## SECTION 2 PERFORMANCE SPECIFICATION

### 2.1 MAXIMUM RATINGS

Maximum ratings are the extreme limits to which the device can be exposed without permanently damaging it. The device contains circuitry to protect the inputs against damage from high static voltages; however, do not apply voltages higher than those shown in the table below. Keep input and output voltages within the range  $V_{SS} \le V \le V_{CC}$ .

| Ref            | Rating                                                                                               | Symbol                                                   | Value                         | Unit        |

|----------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------|-------------|

| 1              | Supply Voltage                                                                                       | V <sub>CC</sub>                                          | -0.3 to +7                    | V           |

| 2              | C <sub>REG</sub> , C <sub>REGA</sub> , C <sub>REF</sub>                                              | V <sub>REG</sub>                                         | -0.3 to +3                    | V           |

| 3              | V <sub>PP</sub>                                                                                      | V <sub>REG</sub>                                         | -0.3 to +11                   | V           |

| 4              | SCLK, CS, D <sub>IN</sub> , CAP/HOLD                                                                 | V <sub>IN</sub>                                          | -0.3 to V <sub>CC</sub> + 0.3 | V           |

| 5              | D <sub>OUT</sub> (high impedance state)                                                              | V <sub>IN</sub>                                          | -0.3 to V <sub>CC</sub> + 0.3 | V           |

| 6              | Current Drain per Pin Excluding $V_{CC}$ and $V_{SS}$                                                | I                                                        | 10                            | mA          |

| 7              | Acceleration (without hitting internal g-cell stops)                                                 | 9 <sub>max</sub>                                         | ±800                          | g           |

| 8              | Powered Shock (six sides, 0.5 ms duration)                                                           | 9 <sub>pms</sub>                                         | ±1500                         | g           |

| 9              | Unpowered Shock (six sides, 0.5 ms duration)                                                         | <b>g</b> shock                                           | ±2000                         | g           |

| 10             | Drop Shock (to concrete surface)                                                                     | h <sub>DROP</sub>                                        | 1.2                           | m           |

| 11<br>12<br>13 | Electrostatic Discharge<br>Human Body Model (HBM)<br>Charge Device Model (CDM)<br>Machine Model (MM) | V <sub>ESD</sub><br>V <sub>ESD</sub><br>V <sub>ESD</sub> | ±2000<br>±500<br>±200         | V<br>V<br>V |

| 14             | Storage Temperature Range                                                                            | T <sub>stg</sub>                                         | -40 to +125                   | °C          |

Notes:

1. Verified by characterization, not tested in production.

## 2.2 OPERATING RANGE

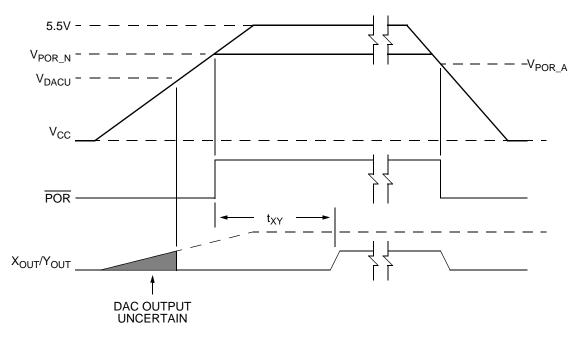

The operating ratings are the limits normally expected in the application and define the range of operation.

| Ref      | Characteristic                                                                                                       | Symbol                             | Min                              | Тур          | Max                              | Units  |          |

|----------|----------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|--------------|----------------------------------|--------|----------|

| 16<br>17 | Supply Voltage<br>Standard Operating Voltage, 3.3V operating range<br>Standard Operating Voltage, 5V operating range | V <sub>CC</sub><br>V <sub>CC</sub> | V <sub>L</sub><br>+3.15<br>+4.75 | +3.3<br>+5.0 | V <sub>H</sub><br>+3.45<br>+5.25 | V<br>V | (1<br>(1 |

| 18       | Operating Temperature Range                                                                                          | T <sub>A</sub>                     | T <sub>L</sub><br>-40            | _            | T <sub>H</sub><br>+105           | С      | (2       |

Notes:

1. Characterized at all values of V<sub>L</sub> and V<sub>H</sub>. Production test is conducted at typical voltage unless otherwise noted.

2. Parameters tested 100% at final test.

#### **ELECTRICAL CHARACTERISTICS** 2.3

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \, T_L \leq T_A \leq T_H, \, |\Delta T_A| < 4 \; \text{K/min unless otherwise specified}$

| Ref      | Characteristic                                                          | Symbol             | Min  | Тур      | Max     | Units    | 1 |

|----------|-------------------------------------------------------------------------|--------------------|------|----------|---------|----------|---|

| 19       | Supply Current Drain<br>$V_{CC} = 5.25 \text{ V}, t_S = 16 \mu\text{s}$ | t I <sub>DD</sub>  |      | _        | 9.5     | mA       |   |

|          | Power-On Recovery Threshold (See Figure 2-1)                            |                    |      |          |         |          |   |

| 20       | V <sub>CC</sub>                                                         | V <sub>POR N</sub> | 2.77 | _        | 3.15    | V        |   |

| 21       | C <sub>REG</sub>                                                        | V <sub>POR_N</sub> | 1.80 | —        | 2.32    | V        |   |

| 22       | C <sub>REGA</sub>                                                       | V <sub>POR_N</sub> | 2.18 | _        | 2.50    | V        |   |

| 23       | C <sub>REF</sub>                                                        | V <sub>POR_N</sub> | 1.11 | —        | 1.29    | V        |   |

|          | Power-On Reset Threshold (See Figure 2-1)                               |                    |      |          |         |          |   |

| 24       | V <sub>CC</sub>                                                         | V <sub>POR A</sub> | 2.77 | _        | 2.95    | V        |   |

| 25       | C <sub>REG</sub>                                                        | V <sub>POR_A</sub> | 1.80 | _        | 2.10    | V        |   |

| 26       | C <sub>REGA</sub>                                                       | V <sub>POR A</sub> | 2.18 | _        | 2.31    | V        |   |

| 27       | C <sub>REF</sub>                                                        | V <sub>POR_A</sub> | 1.11 |          | 1.19    | V        |   |

|          | Hysteresis (VPOR_N - VPOR_A, See Figure 2-1)                            |                    |      |          |         |          |   |

| 28       | V <sub>CC</sub>                                                         | V <sub>HYST</sub>  | 0    |          | 388     | mV       |   |

| 29       | C <sub>REG</sub>                                                        | V <sub>HYST</sub>  | 0    | _        | 300     | mV       |   |

| 30       | C <sub>REGA</sub>                                                       | V <sub>HYST</sub>  | 0    |          | 261     | mV       |   |

| 31       | C <sub>REF</sub>                                                        | V <sub>HYST</sub>  | 0    |          | 150     | mV       |   |

|          | Minimum Functional Voltage (See Figure 2-1)                             |                    |      |          |         | V        | _ |

| 32       |                                                                         | V <sub>DACU</sub>  |      |          | 2.0     | V        | _ |

|          | Internally Regulated Voltages                                           |                    |      |          |         |          |   |

| 33       | C <sub>REG</sub>                                                        | V <sub>DD</sub>    | 2.42 | 2.50     | 2.58    | V        |   |

| 34       | C <sub>REGA</sub> (3)                                                   | V <sub>2.5</sub>   | 2.42 | 2.50     | 2.58    | V        |   |

| 35       | C <sub>REF</sub>                                                        | V <sub>REF</sub>   | 1.20 | 1.25     | 1.29    | V        |   |

|          | External Filter Capacitor (C <sub>REG</sub> , C <sub>REGA</sub> )       |                    |      |          |         |          |   |

| 36       | Value                                                                   | C <sub>REG</sub>   | 800  | 1000     |         | nF       |   |

| 37       | ESR (including interconnect resistance)                                 | ESR                |      | —        | 200     | mΩ       |   |

| 00       | Power Supply Coupling (4)                                               |                    |      |          | 0.004   | 1        |   |

| 38<br>39 | Digital output<br>Analog output                                         |                    |      | —        | 0.004   | digit/mv |   |

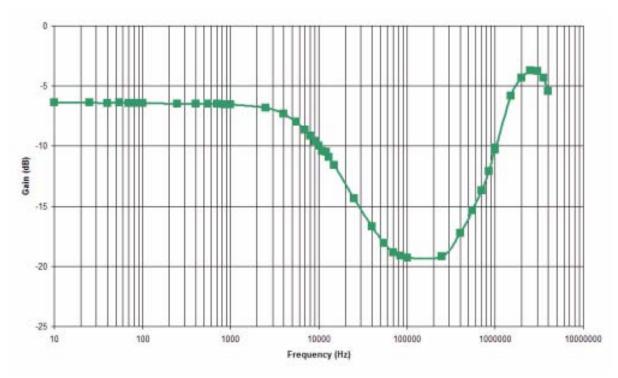

| 39       | Analog output                                                           |                    |      | See Figu | ure 2-2 |          |   |

|          | Digital Sensitivity (D <sub>OUT</sub> )                                 |                    |      |          |         |          | 1 |

| 40       | 20 g Range                                                              | SENS               | —    | 0.04097  | —       | g/digit  |   |

| 41       | 35 g Range                                                              | SENS               | —    | 0.0717   |         | g/digit  |   |

| 42       | 50 g Range                                                              | SENS               | —    | 0.1024   | —       | g/digit  |   |

| 43       | 100 g Range                                                             | SENS               | —    | 0.2048   |         | g/digit  |   |

|          | Sensitivity Error                                                       |                    |      |          |         |          | 1 |

| 44       | $T_A = 25^{\circ}C$                                                     | ASENS              | -4   | -        | +4      | %        |   |

| 45       | $-40^{\circ}C \le T_{A} \le 105^{\circ}C$                               |                    | -4   | 1        | +4      | %        |   |

Notes:

1. Parameters tested 100% at final test.

2. Verified by characterization, not tested in production.

Tested at V<sub>CC</sub> = V<sub>L</sub> and V<sub>CC</sub> = V<sub>H</sub>.

Power supply ripple at frequencies greater than 900 kHz should be minimized to the greatest extent possible.

5. Devices are trimmed at 100 Hz with 1000 Hz low pass filter selected.

(#) Indicates a FSL significant parameter (CPK > 1.33).

(\*) Indicates a FSL critical parameter (CPK > 1.67).

## 2.3 ELECTRICAL CHARACTERISTICS (CONTINUED)

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, \, T_L \leq T_A \leq T_H, \, |\Delta T_A| < 4 \; \text{K/min unless otherwise specified}$

| Ref                                    | Characteristic                                                                                                                                                                                                                                               |             | Symbol                                                                                                | Min                               | Тур                               | Мах                               | Units                                                       | ]                                        |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-------------------------------------------------------------|------------------------------------------|

| 46<br>47<br>48<br>49                   | Analog Sensitivity (X <sub>OUT</sub> , Y <sub>OUT</sub> )<br>20 g Range<br>35 g Range<br>50 g Range<br>100 g Range                                                                                                                                           | *<br>*<br>* | ASENS<br>ASENS<br>ASENS<br>ASENS                                                                      |                                   | 23.4<br>13.40<br>9.37<br>4.68.    |                                   | mV/V/g<br>mV/V/g<br>mV/V/g<br>mV/V/g                        | (1<br>(1<br>(1<br>(1                     |

| 50<br>51                               | Sensitivity Error<br>$T_A = 25^{\circ}C$<br>$-40^{\circ}C \le T_A \le 105^{\circ}C$                                                                                                                                                                          | *           | ∆SENS<br>∆SENS                                                                                        | -16<br>-16                        | _                                 | +16<br>+16                        | %<br>%                                                      | (1<br>(1                                 |

| 52<br>53                               | Offset at 0 g (High-pass filter disabled)<br>10-bits, signed<br>Analog output trimmed for digital operation                                                                                                                                                  | *           | D <sub>OUT</sub><br>A <sub>OUT</sub>                                                                  | -40<br>0.44 × V <sub>CC</sub>     | 0<br>0.5 × V <sub>CC</sub>        | +40<br>0.56 × V <sub>CC</sub>     | digit<br>V                                                  | (1<br>(1                                 |

| 54<br>55<br>56<br>57<br>58<br>59<br>60 | Range of Output (D <sub>OUT</sub> , 10 bits, signed)<br>Normal<br>Positive Acceleration Overflow Code<br>Positive Acceleration Overrange Code<br>Negative Acceleration Underrange Code<br>Negative Acceleration Underlfow Code<br>Unused Code<br>Unused Code |             | RANGE<br>OF <sub>S</sub><br>OR <sub>S</sub><br>UR <sub>S</sub><br>UF <sub>S</sub><br>UNUSED<br>UNUSED | -509<br>—<br>—<br>—<br>—          |                                   | 508<br>—<br>—<br>—<br>—           | digit<br>digit<br>digit<br>digit<br>digit<br>digit<br>digit | (5<br>(5<br>(5<br>(5<br>(5<br>(5)<br>(5) |

| 61<br>62<br>63<br>64                   | Output value on overrange<br>20 g Range<br>35 g Range<br>50 g Range<br>100 g Range                                                                                                                                                                           |             | 9over<br>9over<br>9over<br>9over                                                                      | +20.0<br>+35.0<br>+50.0<br>+100.1 | +20.9<br>+36.6<br>+52.1<br>+104.3 | +22.1<br>+38.7<br>+55.3<br>+110.5 | g<br>g<br>g                                                 | (2                                       |

| 65<br>66<br>67<br>68                   | Output value on underrange<br>20 g Range<br>35 g Range<br>50 g Range<br>100 g Range                                                                                                                                                                          |             | 9under<br>9under<br>9under<br>9under<br>9under                                                        | -20.1<br>-35.1<br>-50.0<br>-100.1 | -20.9<br>-36.6<br>-52.2<br>-104.5 | -22.2<br>-38.8<br>-55.4<br>-110.7 | g<br>g<br>g                                                 |                                          |

| 69                                     | Maximum acceleration without saturation of internal<br>circuitry<br>All ranges                                                                                                                                                                               |             | gsat                                                                                                  | -200                              | _                                 | +200                              | g                                                           | (2                                       |

| 70                                     | Nonlinearity                                                                                                                                                                                                                                                 |             | NL <sub>OUT</sub>                                                                                     | -1                                | _                                 | 1                                 | % FSR                                                       | (2                                       |

| 71                                     | Noise (1Hz-1kHz)                                                                                                                                                                                                                                             |             | n <sub>SD</sub>                                                                                       | —                                 | —                                 | 1.1                               | mg/√Hz                                                      | (2                                       |

| 72<br>73                               | Positive Self Test Output Change<br>$(D_{OUT}, digital)$<br>$T_A = 25^{\circ}C$<br>$-40^{\circ}C \le T_A \le 105^{\circ}C$<br>$(X_{OUT}, Y_{OUT}, analog)$                                                                                                   | *           | ∆ST<br>∆ST                                                                                            | 67<br>62                          | 72<br>72                          | 77<br>82                          | digit<br>digit                                              | (1<br>(1                                 |

| 74<br>75                               | T <sub>A</sub> = 25°C<br>-40°C ≤ T <sub>A</sub> ≤ 105°C                                                                                                                                                                                                      | *           | ∆ST<br>∆ST                                                                                            | 10<br>10                          | —                                 | 18<br>18                          | % FS<br>% FS                                                | (1<br>(1                                 |

Notes:

1. Parameters tested 100% at final test.

2. Verified by characterization, not tested in production.

5. Functionality verified 100% via scan.

(\*) Indicates a FSL critical parameter (CPK > 1.67).

#### 2.3 ELECTRICAL CHARACTERISTICS (CONTINUED)

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, T_L \leq T_A \leq T_H, |\Delta T_A| < 4 \text{ K/min unless otherwise specified}$

| Ref                        | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Symbol                                                                   | Min                      | Тур            | Max                            | Units                           |                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|----------------|--------------------------------|---------------------------------|---------------------------------|

| 76<br>77<br>78<br>79       | Negative Self Test Output Change<br>$(D_{OUT}, digital)$<br>$T_A = 25^{\circ}C$<br>$-40^{\circ}C \le T_A \le 105^{\circ}C$<br>$(X_{OUT}, Y_{OUT}, analog)$<br>$T_A = 25^{\circ}C$<br>$-40^{\circ}C \le T_A \le 105^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AST<br>AST<br>AST<br>AST                                                 | -78<br>-82<br>-18<br>-18 | -72<br>-72<br> | -66<br>-62<br>-10<br>-10       | digit<br>digit<br>% FS<br>% FS  | (6)<br>(6)<br>(6)<br>(6)        |

| 80<br>81<br>82<br>83       | Cross-Axis Sensitivity<br>V <sub>ZX</sub><br>V <sub>YX</sub><br>V <sub>ZY</sub><br>V <sub>ZY</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>ZX</sub><br>V <sub>YX</sub><br>V <sub>ZY</sub><br>V <sub>XY</sub> | -4<br>-4<br>-4<br>-4     |                | +4<br>+4<br>+4<br>+4           | %<br>%<br>%<br>%                | (6)<br>(6)<br>(6)<br>(6)        |

| 84<br>85<br>86<br>87<br>88 | DAC Characteristics (X <sub>OUT</sub> , Y <sub>OUT</sub> )<br>Minimum Output Level, I <sub>OUT</sub> = -200 μA<br>Maximum Output Level, I <sub>OUT</sub> = 200 μA<br>Offset Error<br>Gain Error<br>Differential Nonlinearity<br>Integral Nonlinearity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AV <sub>LOW</sub><br>AV <sub>HIGH</sub><br>OFST<br>GERR<br>DNL           |                          |                | 0.25<br><br>+0.2<br>+0.3<br>+2 | V<br>V<br>%FSR<br>%FSR<br>digit | (2)<br>(2)<br>(2)<br>(2)<br>(2) |

| 89<br>90                   | $T_A = 25^{\circ}C$<br>-40°C ≤ $T_A \le 105^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INL<br>INL                                                               | -3<br>-3.5               | _              | +3<br>+3.5                     | digit<br>digit                  | (2)<br>(6)                      |

| 91<br>92                   | Output High Voltage<br>$D_{OUT} (I_{Load} = -100 \ \mu A)$<br>3.15 V $\leq (V_{CC} - V_{SS}) \leq 3.45 \ V$<br>4.75 V $\leq (V_{CC} - V_{SS}) \leq 5.25 \ V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>OH</sub><br>V <sub>OH</sub>                                       | 3.25<br>3.75             |                |                                | V<br>V                          | (2)<br>(2)                      |

| 93<br>94                   | Output Low Voltage<br>$D_{OUT}$ , ( $I_{Load} = 100 \ \mu A$ )<br>3.15 V $\leq$ ( $V_{CC} - V_{SS}$ ) $\leq$ 3.45 V<br>4.75 V $\leq$ ( $V_{CC} - V_{SS}$ ) $\leq$ 5.25 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>OL</sub><br>V <sub>OL</sub>                                       |                          |                | 0.4<br>0.4                     | V<br>V                          | (2)<br>(2)                      |

| 95<br>96                   | Output Loading (D <sub>OUT</sub> )<br>Load Resistance<br>Load Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Z <sub>OUT</sub><br>C <sub>OUT</sub>                                     | 47                       |                | <br>35                         | kΩ<br>pF                        | (6)<br>(6)                      |

| 97<br>98                   | Output Loading (X <sub>OUT</sub> , Y <sub>OUT</sub> )<br>Load Resistance<br>Load Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z <sub>OUT</sub><br>C <sub>OUT</sub>                                     | 25<br>—                  | _              | <br>60                         | kΩ<br>pF                        | (6)<br>(6)                      |

| 99<br>100                  | $\begin{array}{l} \mbox{Input High Voltage} \\ \mbox{CS/RESET, SCLK, D_{IN}/ST, CAP/HOLD} \\ \mbox{3.15 V} \leq (V_{CC} - V_{SS}) \leq 3.45 V \\ \mbox{4.75 V} \leq (V_{CC} - V_{SS}) \leq 5.25 V \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>IH</sub><br>V <sub>IH</sub>                                       | 1.5<br>2.5               |                |                                | V<br>V                          | (2)<br>(2)                      |

| 101<br>102                 | $\begin{array}{l} \mbox{Input L} Ownerse of the second s$ | V <sub>IL</sub><br>V <sub>IL</sub>                                       |                          |                | 0.85<br>1.0                    | V<br>V                          | (2)<br>(2)                      |

| 103<br>104                 | Input Current<br>High (at V <sub>IH</sub> )<br>SCLK, D <sub>IN</sub> , CAP/HOLD<br>V <sub>PP</sub> /TEST (internal pulldown resistor)<br>Low (at V <sub>II</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I <sub>IH</sub><br>R <sub>IN</sub>                                       | -30<br>190               | -50<br>270     | -260<br>350                    | μA<br>kΩ                        | (2)<br>(2)                      |

| 105<br>Note                | CS/RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ι <sub>ΙL</sub>                                                          | 30                       | 50             | 260                            | μΑ                              | (2)                             |

Notes:

1. Parameters tested 100% at final test.

Verified by characterization, not tested in production.

Parameters tested 100% at unit probe.

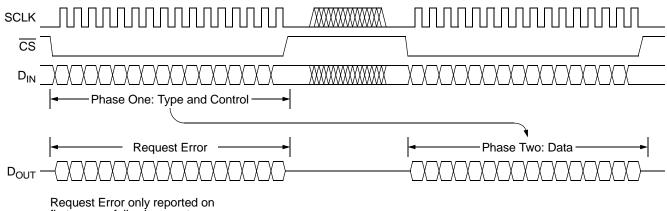

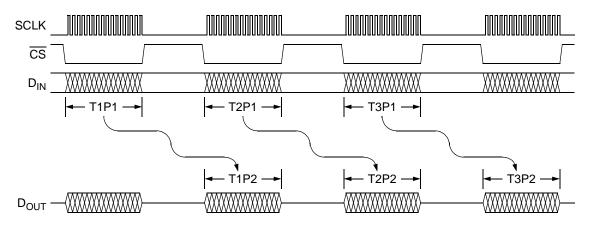

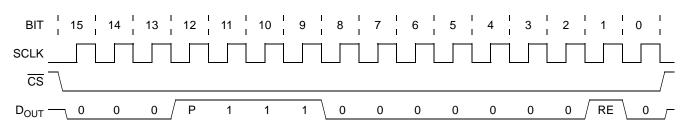

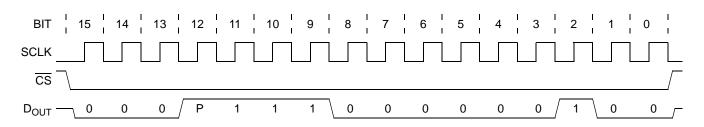

### 2.4 CONTROL TIMING

$V_L \leq (V_{CC} - V_{SS}) \leq V_H, T_L \leq T_A \leq T_H, |\Delta T_A| < 4 \text{ K/min unless otherwise specified}$

| Ref                                           | Characteristic                                                                                                                                                                                            | Symbol                                                               | Min                                     | Тур      | Max            | Units                                  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------|----------|----------------|----------------------------------------|

| 106                                           | DSP Low-Pass Filter (5)<br>Cutoff frequency (6)<br>DSP Low-Pass Filter                                                                                                                                    |                                                                      | 380                                     | 400      | 420            | Hz                                     |

| 107                                           | Cutoff frequency (-3dB, referenced to 0 Hz)                                                                                                                                                               |                                                                      | 335                                     | 353      | 371            | Hz                                     |

| 108<br>109                                    | DSP High-Pass Filter<br>Cutoff frequency<br>Filter Order                                                                                                                                                  | f <sub>C(HPF)</sub><br>O <sub>HPF</sub>                              | 0.095                                   | 0.1<br>1 | 0.105<br>—     | Hz<br>1                                |

| 110<br>111                                    | Power-On Recover <u>y</u> Time<br>POR negated to CS low<br>Power applied to X <sub>OUT</sub> , Y <sub>OUT</sub> valid                                                                                     | t <sub>OP</sub><br>t <sub>XY</sub>                                   | _                                       |          | 840<br>10      | μs<br>ms                               |

| 112                                           | Internal Oscillator Frequency                                                                                                                                                                             | fosc                                                                 | 3.8                                     | 4.0      | 4.2            | MHz                                    |

| 113                                           | Clock Monitor Threshold                                                                                                                                                                                   | f <sub>MON</sub>                                                     | 3.6                                     | —        | 4.4            | MHz                                    |

| 114                                           | Chip Select to Internal Reset (See Figure 2-3)                                                                                                                                                            | t <sub>CSRES</sub>                                                   | 486                                     | 512      | 538            | μs                                     |

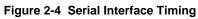

| 115<br>116<br>117<br>118<br>119<br>120<br>121 | Serial Interface Timing (See Figure 2-4)<br>Clock period<br>CS asserted to SCLK high<br>Data setup time<br>Data hold time<br>SCLK low to data out<br>SCLK high to CS negated<br>CS negated to CS asserted | tsclk<br>tcsclk<br>tdc<br>tcdin<br>tcdin<br>tcdout<br>tchcsh<br>tcsn | 120<br>60<br>20<br>10<br>—<br>60<br>526 |          | <br><br>50<br> | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

| 122                                           | DAC Low-Pass Filter<br>Cutoff Frequency                                                                                                                                                                   | f <sub>C</sub>                                                       | 5                                       | 10       | 20             | kHz                                    |

| 123                                           | Sensing Element Rolloff Frequency (-3 dB)                                                                                                                                                                 | BW <sub>GCELL</sub>                                                  | _                                       | 3        | —              | kHz                                    |

Notes:

1. Functionality verified 100% via scan. Timing characteristic is directly determined by internal oscillator frequency.

2. Verified by characterization, not tested in production.

3. Parameters tested 100% at final test.

4. Parameters tested 100% at unit probe.

5. Devices are trimmed at 100 Hz with 1000 Hz low-pass filter option selected.

6. Cutoff frequencies shown are -4dB referenced to 0 Hz response, to correspond with previous specifications.

Figure 2-2 Power Supply Coupling - DAC Outputs

## SECTION 3 INTERNAL MODULES

### 3.1 ONE-TIME PROGRAMMABLE DATA ARRAY

A 400-bit programmable data array allows each device to be customized. The array interface incorporates parity circuitry for fault detection along with a locking mechanism to prevent unintended changes. Portions of the array are reserved for factory-programmed trim values. Customer accessible data stored in the array are shown in the table below.

Addresses \$00 - \$0D are associated with the programmable data array. A writable register at address \$0E is provided for device control operations. Two read-only registers at addresses \$0F and \$10 provide status information.

Unused bits within the data array are always read as '0' values. Unprogrammed OTP bits are also read as '0' values.

| Lo      | cation                       |          |          |          | Bit Fu     | nction   |          |          |          | Turne |  |

|---------|------------------------------|----------|----------|----------|------------|----------|----------|----------|----------|-------|--|

| Address | Register                     | 7        | 6        | 5        | 4          | 3        | 2        | 1        | 0        | Туре  |  |

| \$00    | SN0                          | SN[7]    | SN[6]    | SN[5]    | SN[4]      | SN[3]    | SN[2]    | SN[1]    | SN[0]    |       |  |

| \$01    | SN1                          | SN[15]   | SN[14]   | SN[13]   | SN[12]     | SN[11]   | SN[10]   | SN[9]    | SN[8]    |       |  |

| \$02    | SN2                          | SN[23]   | SN[22]   | SN[21]   | SN[20]     | SN[19]   | SN[18]   | SN[17]   | SN[16]   |       |  |

| \$03    | SN3                          | SN[31]   | SN[30]   | SN[29]   | SN[28]     | SN[27]   | SN[26]   | SN[25]   | SN[24]   |       |  |

| \$04    | DEVCFG0 Factory Programmed   |          |          |          |            |          |          |          |          |       |  |

| \$05    | DEVCFG1 Factory Programmed   |          |          |          |            |          |          |          |          | -     |  |

| \$06    | 6 DEVCFG2 Factory Programmed |          |          |          |            |          |          |          |          | F     |  |

| \$07    | 7 DEVCFG3 Factory Programmed |          |          |          |            |          |          |          |          |       |  |

| \$08    | DEVCFG4                      |          |          |          | Factory Pr | ogrammed |          |          |          |       |  |

| \$09    | DEVCFG5                      | LOCK2    | PAR2     | COMP1    | COMP0      | SPARE    | DACEN    | AD3      | AD2      |       |  |

| \$0A    | AXCFG_X                      | RNG_X[2] | RNG_X[1] | RNG_X[0] | LPF_X[4]   | LPF_X[3] | LPF_X[2] | LPF_X[1] | LPF_X[0] |       |  |

| \$0B    | AXCFG_Y                      | RNG_Y[2] | RNG_Y[1] | RNG_Y[0] | LPF_Y[4]   | LPF_Y[3] | LPF_Y[2] | LPF_Y[1] | LPF_Y[0] |       |  |

| \$0C    |                              | L        | L        | L        | Unused     |          | L        |          |          | N/A   |  |

| \$0E    | DEVCTL                       | RES_1    | RES_0    | CE       | Reserved   | HPFB     | YINV     | ST1      | ST0      | R/W   |  |

| \$0D    | DSPCFG                       | SPARE    | SPARE    | INTERP   | OVLD       | SD       | HPFD     | HPFSEL   | OFMON    | F     |  |

| \$0F    | TEMP                         | TEMP[7]  | TEMP[6]  | TEMP[5]  | TEMP[4]    | TEMP[3]  | TEMP[2]  | TEMP[1]  | TEMP[0]  |       |  |

| \$10    | DEVSTAT                      | IDE      | OSCF     | DEVINIT  | TF         | HPF      | OFF_Y    | OFF_X    | DEVRES   | R     |  |

| \$11    | COUNT                        | COUNT[7] | COUNT[6] | COUNT[5] | COUNT[4]   | COUNT[3] | COUNT[2] | COUNT[1] | COUNT[0] |       |  |

#### Table 3-1 Customer Accessible Data

Type codes

F: Factory programmed OTP location

R: Read-only register

R/W: Read/write register

N/A: Not applicable

### 3.1.1 'DEVICE CONTROL REGISTER (DEVCTL)

A read-write register at address \$0E supports a number of device control operations as described below. Reserved bits within DEVCTL are always read as logic '0' values.

| Address | Register |      |      |    | В        | Bit  |      |     |     |

|---------|----------|------|------|----|----------|------|------|-----|-----|

| Address | Register | 7    | 6    | 5  | 4        | 3    | 2    | 1   | 0   |

| \$0E    | DEVCTL   | RES1 | RES0 | CE | Reserved | HPFB | YINV | ST1 | ST0 |

#### 3.1.1.1 Reset Control (RES\_1, RES\_0)

A specific series of three write operations involving these two bits will cause the internal digital circuitry to be reset. The state of the remaining bits in the DEVCTL register do not affect the reset sequence, however any write operation involving this register in which both RES\_1 and RES\_0 are cleared will terminate the sequence.

To reset the internal digital circuitry, the following register write operations must be performed in the order shown:

- 1. Set RES1. RES0 must remain cleared.

- 2. Set RES1 and RES0.

- 3. Clear RES1 and set RES0.

RES1 and RES0 are always read as logic '0' values. After reset sequence has been completed DEVCTL register will read 0X00. It should be noted that after a reset or power-cycle sequence is completed the DEVCTL register reset to the value 0X00.

#### 3.1.1.2 Clear Error (CE)

Setting this bit to a logic '1' state will clear transient error status conditions. It is necessary to either set this bit or perform a device reset if an error condition has been reported by the device before acceleration data transfer can be resumed. The device reset condition may be cleared only after device initialization has completed.

Error conditions and classification are described in Section 4.2.

The state of this bit is always read as logic '0'.

#### 3.1.1.3 High-Pass Filter Bypass (HPFB)

Setting this bit will remove the high-pass filter from the signal chain within the DSP block. The state of this bit is indicated when DEVCTL is read. This bit is always cleared following reset.

The state of the high-pass filter is frozen when this bit is at a logic '1' level.

#### 3.1.1.4 Self-Test Control (ST1, ST0)

Bidirectional self-test control is provided through manipulation of these bits. ST1 controls direction while ST0 enables and disables the self-test circuitry. ST1 and ST0 are always cleared following internal reset. When ST0 is set, the high-pass filter is bypassed and the values within the high-pass filter are frozen. Both axes are affected simultaneously by the state of these bits. If the offset monitor is enabled, self-test activation in a single direction should be limited to less than 30 ms.

The state of the ST0 bit is indicated as part of all acceleration results.

#### 3.1.1.5 Y-Axis Signal Inversion Control (YINV)

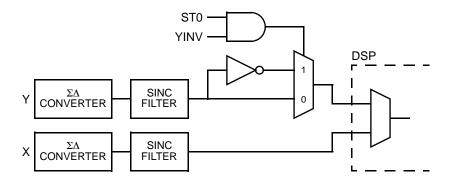

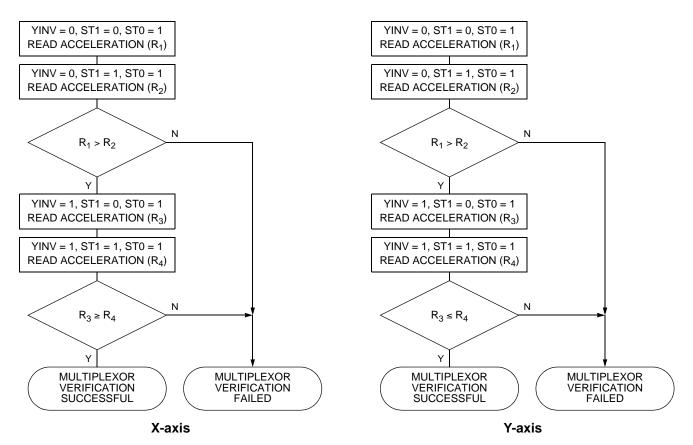

This control function is provided as a means to verify operation of the two-channel multiplexor which alternately provides X-axis and Y-axis data to the DSP. An inverter block and multiplexor at the Y-axis input to the DSP are controlled by the YINV bit. Setting this bit when ST0 is set has the effect of changing the sign of acceleration in the Y-axis. Operation of the YINV bit is illustrated in Figure 3-1 below. Y-axis inversion may be selected only during self-test; the state of this bit has no effect when ST0 is cleared.

Figure 3-1 Y-Axis Inversion Function

Self-test operations controlled by YINV along with ST1 and ST0 are summarized in the following table.

| YINV | ST1 | ST0 | ST0 Self-Test Operation                              |                     |  |  |  |  |

|------|-----|-----|------------------------------------------------------|---------------------|--|--|--|--|

| TINV | 511 | 510 | X-Axis                                               | Y-Axis              |  |  |  |  |

| Х    | Х   | 0   | Self Test Disabled, Y-Axis Signal Inversion Disabled |                     |  |  |  |  |

| 0    | 0   | 1   | Positive Deflection                                  |                     |  |  |  |  |

| 0    | 1   | 1   | Negative                                             | Deflection          |  |  |  |  |

| 1    | 0   | 1   | Positive Deflection                                  | Negative Deflection |  |  |  |  |

| 1    | 1   | 1   | Negative Deflection Positive Deflection              |                     |  |  |  |  |

#### Table 3-3 Self-Test Control Operations

#### NOTE:

Offset correction is applied within the DSP, and is not affected by the state of the YINV bit. Consequently, inversion of the Y-axis signal may result in saturation of the Y-axis output value.

Correct operation of the DSP input multiplexor may be confirmed by performing the operations shown in Figure 3-2.

Figure 3-2 DSP Input Multiplexor Verification Flow Chart

### 3.1.2 Temperature Sensor Value (TEMP)

This read-only register contains a signed value which provides a relative temperature indication. The temperature sensor is uncalibrated and its output for a given temperature will vary from one device to the next. The value in this register increases with temperature.

| Loc     | cation   |         | Bit Function |         |         |         |         |         |         |

|---------|----------|---------|--------------|---------|---------|---------|---------|---------|---------|

| Address | Register | 7       | 6            | 5       | 4       | 3       | 2       | 1       | 0       |

| \$0F    | TEMP     | TEMP[7] | TEMP[6]      | TEMP[5] | TEMP[4] | TEMP[3] | TEMP[2] | TEMP[1] | TEMP[0] |

Table 3-4 Temperature Sensor Value Register

### 3.1.3 Device Status Register (DEVSTAT)

This read-only register is accessible in all modes.

| Table 3-5 | Device Status | Register |

|-----------|---------------|----------|

|-----------|---------------|----------|

| Loc     | cation   | Bit Function |                 |         |    |     |       |       |        |

|---------|----------|--------------|-----------------|---------|----|-----|-------|-------|--------|

| Address | Register | 7            | 7 6 5 4 3 2 1 0 |         |    |     |       |       |        |

| \$10    | DEVSTAT  | IDE          | OSCF            | DEVINIT | TF | HPF | OFF_Y | OFF_X | DEVRES |

#### 3.1.3.1 Internal Data Error Flag (IDE)

This flag will be set if a register data parity fault or a marginally programmed fuse is detected. Device reset is required to clear this fault condition. If a parity error is associated with the data stored in the fuse array, this fault condition cannot be cleared. This flag is disabled when the device is in test mode.

#### 3.1.3.2 Oscillator Fault Flag (OCSF)

This flag will be set if the primary oscillator and reference oscillator frequencies vary by an amount greater than the specified tolerance. In normal operating mode, an oscillator fault condition will result in  $D_{OUT}$  being driven high when  $\overline{CS}$  is asserted.

#### 3.1.3.3 Device Initialization Flag (DEVINIT)

This flag is set during the interval between negation of internal reset and completion of device initialization. DEVINIT is cleared automatically.

#### 3.1.3.4 Temperature Fault Flag (TF)

This flag is set if the value reported by the on-chip temperature sensor exceeds specified limits. TF may be cleared by writing a logic '1' value to the CE bit in DEVCTL, provided that the fault condition is no longer detected.

#### 3.1.3.5 High-Pass Filter Status (HPF)

This bit is set when a high-pass filter is present in the DSP signal chain when the HPFB bit has been set.

#### 3.1.3.6 Y-Axis Offset Error Flag (OFF\_Y)

#### 3.1.3.7 X-Axis Offset Error Flag (OFF\_X)

The offset error flags are set if the associated signal reaches the specified offset limit. These flags may be cleared by writing a logic '1' value to the CE bit in DEVCTL. Offset faults are not reported for 1.5 seconds following reset.

#### 3.1.3.8 Device Reset Flag (DEVRES)

This flag is set during device initialization. A logic '1' must be written to the CE bit in the Device Control register (DEVCTL) to clear this bit.

#### 3.1.4 Counter Register (COUNT)

This read-only register provides the value of a free-running 8-bit counter derived from the primary oscillator. A five-bit prescaler divides the 4 MHz primary oscillator frequency by 32. Thus, the value in the register increases by one count every 8  $\mu$ s, and the counter rolls over every 2.048 ms.

| Loc     | cation   | Bit Function |                 |          |          |          |          |          |          |

|---------|----------|--------------|-----------------|----------|----------|----------|----------|----------|----------|

| Address | Register | 7            | 7 6 5 4 3 2 1 0 |          |          |          |          |          |          |

| \$11    | COUNT    | COUNT[7]     | COUNT[6]        | COUNT[5] | COUNT[4] | COUNT[3] | COUNT[2] | COUNT[1] | COUNT[0] |

#### Table 3-6 Counter Register

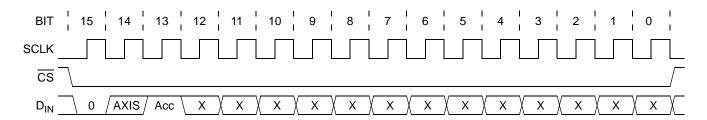

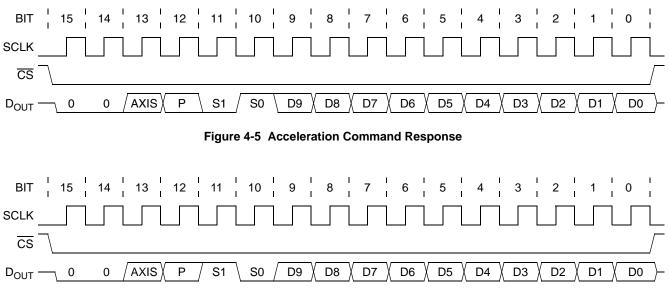

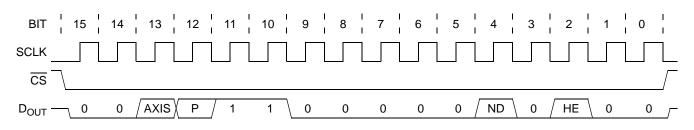

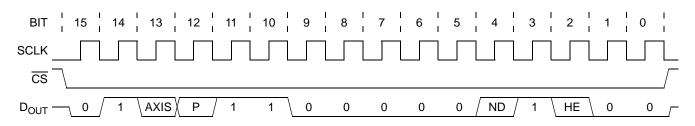

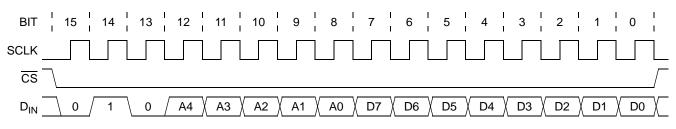

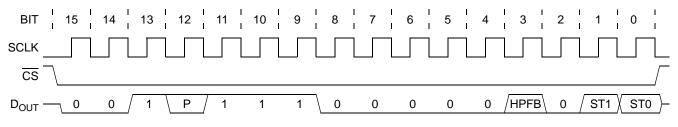

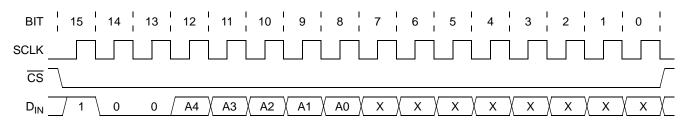

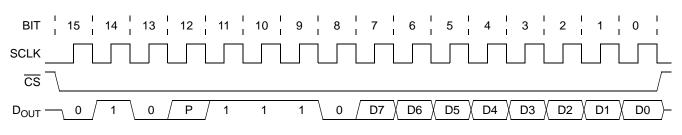

## SECTION 4 SERIAL COMMUNICATIONS