#### **PRODUCTION DATA SHEET**

#### **DESCRIPTION**

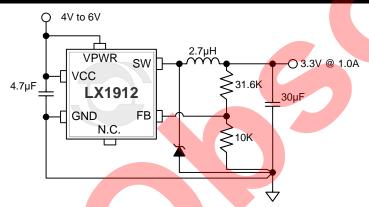

The LX1912 operates as a Current Mode PWM Buck regulator that switches to PFM mode with light loads. The entire regulator function is implemented with few external components.

The LX1912 responds quickly to dynamic load changes using a high bandwidth error amplifier and internal compensation. Tight output voltage regulation is maintained with the compensated 800mV, ±2% reference (line and temp regulation). With two external resistors the output voltage is easily programmed, from 800mV to 90% of  $V_{IN}$ .

The regulator is capable of providing an output load current of 1.0A, has no minimum load current requirement for stable operation. Current limit is cycle-by-cycle to protect the switch. Power conversion efficiency maximized with low regulator IO and

covers 4.0V to 6.0V, features include power on delay; soft start to limit inrush currents; and thermal shutdown during fault conditions.

The 6-pin TSOT package provides a small form factor with excellent power dissipation capability.

PFM mode of operation The LX1912 operational range

#### **KEY FEATURES**

- Internal Reference 800mv ±2% Accuracy (Line and Temp.)

- 4.0V to 6.0V Input Range

- Internal Soft Start

- Adj. Output From 0.8V to 90% of VIN

- Output Current up to 1.0A

- Quiescent Current < 550µA, Typical @ 23°C

- 1.2MHz PWM Frequency

- Over Voltage Protection

#### **APPLICATIONS**

- Portable Microprocessor Core Voltage Supplies

- 5V to 3V

- RoHS Compliant Product

#### PRODUCT HIGHLIGHT

IMPORTANT: For the most current data, consult MICROSEMI's website: http://www.microsemi.com

Figure 1 – LX1912 Circuit Topology and Typical Efficiency Performance

| PACKAGE ORDER INFO  |               |                            |                                                 |              |  |

|---------------------|---------------|----------------------------|-------------------------------------------------|--------------|--|

| T <sub>A</sub> (°C) | Input Voltage | Output<br>Voltage<br>Range | Plastic TSOT<br>6-Pin  RoHS Compliant / Pb-free | Part Marking |  |

| 0 to +70            | 4.0V – 6.0V   | Adjustable                 | LX1912CSG                                       | 1912         |  |

Note: Available in Tape & Reel. Append the letters "TR" to the part number. (i.e. LX1912CSG-TR)

#### **PRODUCTION DATA SHEET**

### **ABSOLUTE MAXIMUM RATINGS** Input Voltage (VCC and VPWR).....-0.3V to 7.0V SW to GND -0.3V to $(V_{IN} + 0.3V)$ $V_{FB}$ to GND .....-0.3V to +2V Operating Junction Temperature Range (T<sub>J</sub>).....-40°C to +125°C Storage Temperature Range, T<sub>A</sub>.....-65°C to 150°C Note: Exceeding these ratings could cause damage to the device. All voltages are with respect to

Ground. Currents are positive into, negative out of specified terminal.

## PACKAGE PIN OUT N.C. SW GND [ **VPWR** FΒ VCC SG PACKAGE (Top View) RoHS / Pb-free 100% Matte Tin Lead Finish N.C. - No Internal Connection

#### THERMAL DATA

**SG** Plastic TSOT 6-Pin

THERMAL RESISTANCE-JUNCTION TO AMBIENT,  $\theta_{\text{JA}}$

134°C/W

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

|      | FUNCTIONAL PIN DESCRIPTION                                                                            |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name | Name Description                                                                                      |  |  |  |  |  |

| VCC  | VCC Unregulated supply voltage input, ranging from +4V to 6.0V for internal analog control circuitry. |  |  |  |  |  |

| VPWR | Unregulated supply voltage for PMOS <mark>FET drain to drive t</mark> he switch pin.                  |  |  |  |  |  |

| FB   | Feedback input for setting programming output voltage.                                                |  |  |  |  |  |

| GND  | Circuit ground providing bias for IC operation and high frequency gate drive bias.                    |  |  |  |  |  |

| SW   | Inductor and commutation diode connection point. Connects to internal PMOSFET source.                 |  |  |  |  |  |

#### **PRODUCTION DATA SHEET**

#### **ELECTRICAL CHARACTERISTICS**

Specifications apply over junction temperature of:  $-20^{\circ}\text{C} \le T_J \le 125^{\circ}\text{C}$  for VCC = VPWR = 5V (except where otherwise noted). Typical values are at  $T_A = 23^{\circ}\text{C}$ .

| Parameter                      |                               | Symbol                 | Test Conditions                                                   | Min  | Тур   | Max  | Units |

|--------------------------------|-------------------------------|------------------------|-------------------------------------------------------------------|------|-------|------|-------|

| Operating Range <sup>1</sup>   |                               | VCC                    | Functional operation guaranteed by design                         | 4.0  |       | 6.0  | V     |

| Feed Back Threshold            |                               | $V_{FBT}$              | 4.0V ≤ VCC ≤ 6.0V                                                 | 784  | 800   | 816  | mV    |

| FB Input                       | Current                       | I <sub>FB</sub>        | V <sub>FB</sub> = 0.81V                                           |      | 40    | 75   | nA    |

| Error Am                       | plifier                       | BW                     | Closed Loop                                                       |      | 200   |      | KHz   |

| Quiescent Operating Current    |                               | I <sub>Q</sub> (Pin 4) | $V_{FB} > 0.825V$ , $R_{LOAD}$ Switch Pin < 1K $\Omega$           |      | 500   | 850  | μА    |

| Soft Start                     | t, V <sub>OUT</sub> Slew Rate | Vo                     | Initial Power On or after Short Circuit                           |      | 21    | 50   | V/mS  |

| P-Channel Switch ON Resistance |                               | R <sub>DS(ON)</sub>    | I <sub>SW</sub> = 1.0A                                            |      | 0.375 | 0.6  | Ω     |

| Maximum Duty Cycle             |                               | D                      | I <sub>SW</sub> = 1.0A (assured by design, not ATE tested)        |      | 80    |      | %     |

| SW Leak                        | age Current                   | I <sub>LEAK</sub>      | V <sub>FB</sub> = 0.825V                                          |      | 0.01  | 5    | μА    |

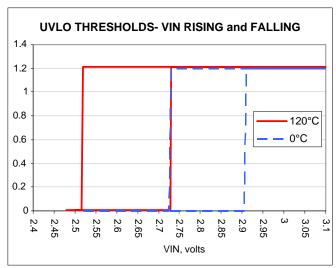

|                                | Under Voltage Lockout         |                        | VCC Rising                                                        |      |       | 3.00 | V     |

| UVLO                           | Under Voltage Lockout         |                        | VCC Falling                                                       | 2.4  |       |      |       |

|                                | UVLO Hysteresis               |                        |                                                                   |      | 0.15  |      |       |

| P-Chann                        | el Current Limit <sup>2</sup> | I <sub>LIM</sub>       | Peak Current at Switch Pin (not DC current)                       | 1.50 | 2.30  |      | Α     |

| PWM Fre                        | PWM Frequency                 |                        | PWM Mode                                                          | 820  | 1200  | 1920 | KHz   |

| PFM Mod                        | de Region                     | CI TVIIII              |                                                                   |      | mA    |      |       |

| Feed Back PSRR                 |                               |                        | 1Hz < Frequency VCC < 10KHz                                       |      | -40   |      | dB    |

| Closed Loop Load Regulation    |                               | Load Reg               | V <sub>O</sub> = 1.2V, 50mA ≤ I <sub>O</sub> ≤ 1.0A, ckt figure 1 |      | 0.85  |      | %Vo   |

| Thermal Shutdown               |                               | T <sub>SD</sub>        | (assured by design, not ATE tested)                               | 135  | 150   |      | °C    |

Note 1:  $V_{IN}$  vs  $V_{OUT}$  ratio @ 1.0A LOAD IS SET AT  $V_{IN} = V_{OUT} + 1.0V$

Note 2: 1.0 amp operation @ 70°C ambient depends on adequate heat sinking to keep T<sub>J</sub> below 125°C

**PRODUCTION DATA SHEET**

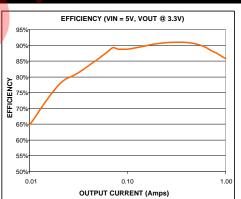

### Figure 2 – LX1912 Block Diagram

## $V_{OUT}$ C<sub>OUT</sub> Inductor Diode $C_{OUT}$ $\mathbf{C}_{\mathrm{OUT}}$ ☐ N.C. SW VPWR GND $\mathbf{C}_{\mathrm{OUT}}$ 岙 VCC <sub>FB</sub> LX1912 C<sub>IN</sub> Rf GROUND

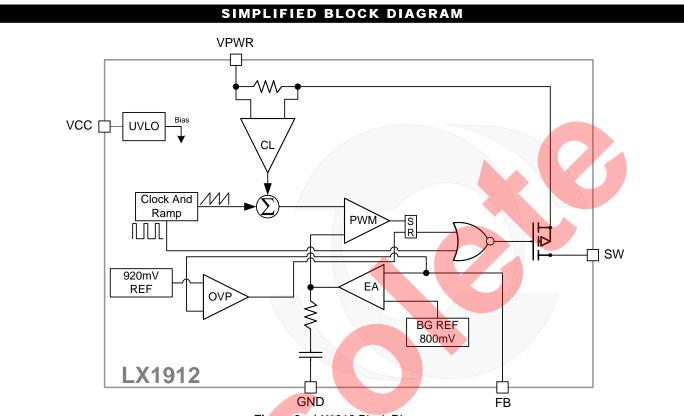

Figure 3 - PCB Layout Considerations

#### **PRODUCTION DATA SHEET**

#### **APPLICATION NOTE**

#### **FUNCTIONAL DESCRIPTION**

The LX1912 is a Current Mode PWM regulator with internal compensation.

The internal PMOS high side switch is protected with current limit on a pulse by pulse basis and with thermal shutdown. Thermal shutdown is activated with a junction temperature of 160°C (typical) and has 20°C of hysteresis.

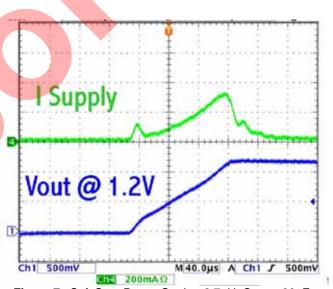

The regulator has an internal Power On Reset delay of 50- $100\mu s$  to ensure all circuitry is operating before enabling the Switch output.

Soft Start is activated upon initial power-on, or following recovery from either thermal shutdown or short circuit. The Soft start control block generates a voltage ramp that clamps the error amplifier non-inverting reference voltage. As this clamp voltage rises, the duty cycle is gradually increased, thus limiting the peak inrush currents.

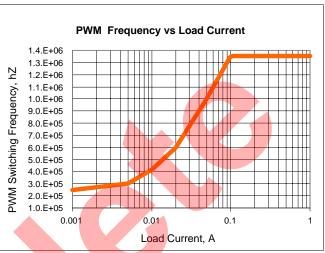

PWM / PFM mode of operation is determined by the load current condition. The PFM mode increases system efficiency by reducing the switching frequency thus switching losses. During light loading,  $I_{OUT}\!<\!200\text{mA}$  typically, PFM mode becomes active, the switching frequency begins to decrease, the frequency change occurs over a continuous range, decreasing further as  $I_{OUT}$  decreases.

#### **OUTPUT OVER VOLTAGE PROTECTION**

The over voltage comparator compares the FB pin voltage to a voltage that is 15% higher than the internal referenced VREF. Once the FB pin voltage goes 15% above the internal reference, the internal PMOS control switch is turned off, which allows the output voltage to decrease toward regulation.

#### **OUTPUT VOLTAGE PROGRAMMING**

Resistors R1 and R2 program the output voltage. The total impedance of both feedback resistors should not exceed 50K Ohms to ensure optimal frequency stability. The value of R1 can be determined using the following equation, note  $V_{REF}$  is also referred to as  $V_{FRT}$ .

$$R1 = R2 \left( \frac{V_{OUT}}{V_{REF}} \right) - 1$$

#### **DIODE SELECTION**

A Schottky diode is required for switching speed and low forward voltage. Efficiency is determined mostly by the diode's forward voltage. The diode conducts 1-D%, for  $V_{OUT}$  =1.2V this becomes 76% in a 5V system.

#### INDUCTOR SELECTION

Selecting the appropriate inductor type and value ensures optimal performance of the converter circuit for the intended application. A primary consideration requires the selection of an inductor that will not saturate at the peak current level. EMI, output voltage ripple, and overall circuit efficiency affect inductor choice. The inductor that works best depends upon the application's requirements and some experimentation with actual devices in-circuit is typically necessary to make the most effective choice.

#### INDUCTOR SELECTION, CONT.

The LX1912 stability performance is optimized by using an inductor value of  $2.7\mu H$   $\pm 20\%$ . The benefit of a larger inductor value can increase efficiency at the lower output currents and reduces output voltage ripple, thus output capacitance related to ripple filtering. Smaller inductors typically provide smaller package size (critical in many portable applications) at the expense of increasing output ripple current. Regardless of inductor value, selecting a device manufactured with a ferrite-core produces lower losses at higher switching frequencies and thus better overall performance. Larger inductors may lead to diminished Step-Load response.

#### **CAPACITOR SELECTION**

To minimize ripple voltage, output capacitors with a low series resistance (ESR) are recommended. Multi-layer ceramic capacitors with X5R or X7R dielectric make an effective choice because they feature small size, very low ESR, a temperature stable dielectric, and can be connected in parallel to increase capacitance. Typical output capacitance values of 20 to 60 $\mu$ F have proven effective. Other low ESR capacitors such as solid tantalum, specialty polymer, or organic semiconductor, make effective choices provided that the capacitor is properly rated for the output voltage and ripple current. Finally, choose an input capacitor of sufficient size to effectively decouple the input voltage source impedance (e.g.,  $C_{\rm IN} \geq 4.7 \mu F)$ .

#### LAYOUT CONSIDERATIONS

The high peak currents and switching frequencies present in DC/DC converter applications require careful attention to device layout for optimal performance. Basic design rules include: (1) maintaining wide traces for power components (e.g., width > 50mils); (2) place CIN, COUT, the Schottky diode, and the inductor close to the LX1912; (3) minimizing trace capacitance by reducing the etch area connecting the SW pin to the inductor; and (4) minimizing the etch length to the FB pin to reduce noise coupling into this high impedance sense input. Other considerations include placing a 0.1uF capacitor between the LX1912 VOUT pin and GND pin to reduce high frequency noise and decoupling the VCC, VPWR pins using a 0.1µF capacitor.

#### **PRODUCTION DATA SHEET**

#### CHARACTERISTIC CURVES

Figure 4- Under Voltage Lockout for VIN

Figure 5 - PFM / PWM Range of Output Switch

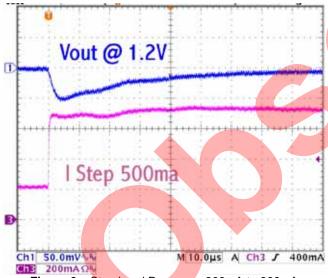

Figure 6 – Step Load Response 300mA to 800mA, L = 2.7µH, C<sub>OUT</sub> = 30µF

Figure 7– Soft Start Power On, L =  $2.7\mu H$ ,  $C_{OUT} = 30\mu F$ ,  $I_{OUT} = 0 m A_{DC}$

**PRODUCTION DATA SHEET**

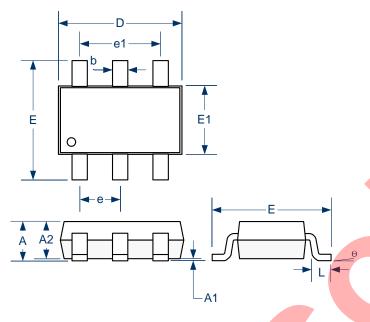

#### PACKAGE DIMENSIONS

# SG 6 Pin TSOT

|     | MILLIN    | MILLIMETERS |           | INCHES    |  |  |

|-----|-----------|-------------|-----------|-----------|--|--|

| Dim | MIN       | MAX         | MIN       | MAX       |  |  |

| Α   | -         | 1.00        |           | 0.039     |  |  |

| A1  | 0.01      | 0.10        | 0.0004    | 0.004     |  |  |

| A2  | 0.84      | 0.90        | 0.033     | 0.035     |  |  |

| b   | 0.30      | 0.45        | 0.012     | 0.018     |  |  |

| С   | 0.12      | 0.20        | 0.005     | 0.008     |  |  |

| D   | 2.90 BSC  |             | 0.114 BSC |           |  |  |

| Е   | 2.80 BSC  |             | 0.110 BSC |           |  |  |

| E1  | 1.60      | 1.60 BSC    |           | 0.063 BSC |  |  |

| e1  | 1.90 BSC  |             | 0.075 BSC |           |  |  |

| е   | 0.095 BSC |             | 0.037 BSC |           |  |  |

| L   | 0.30      | 0.50        | 0.012     |           |  |  |

| L2  | 0.25 BSC  |             | 0.010 BSC |           |  |  |

Note:

Dimensions do not include mold flash or protrusions; these shall not exceed 0.15mm (.006") on any side. Lead Dimension shall not include solder coverage.

**PRODUCTION DATA SHEET**

PRODUCTION DATA – Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.