#### THE INFINITE POWER OF INNOVATION

# PROGRAMMABLE DC:DC CONTROLLER

PRODUCTION DATA SHEET

### DESCRIPTION

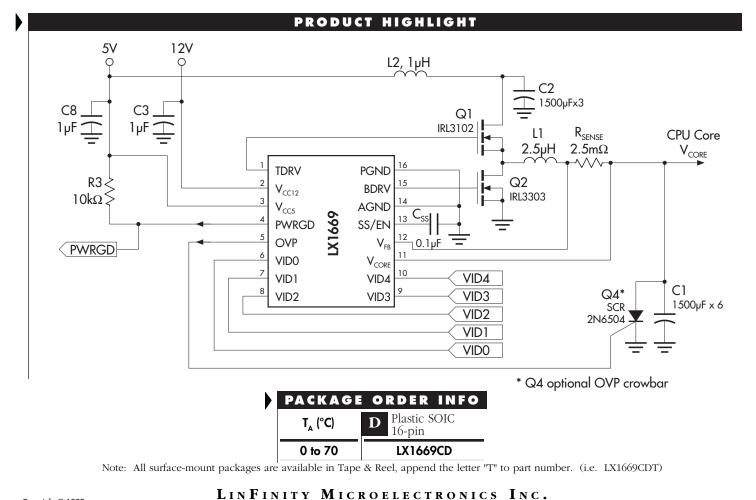

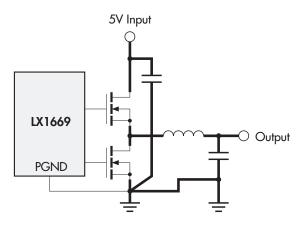

The LX1669 is a Monolithic Switching Regulator Controller IC designed to provide a low cost, high performance adjustable power supply for advanced microprocessors and other applications requiring a very fast transient response and a high degree of accuracy. It provides a programmable switching regulator output suitable for powering Pentium<sup>®</sup> II and other processors.

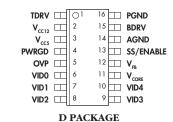

**Programmable Synchronous Rectifier Driver for CPU Core.** The main output is adjustable from 1.3 to 3.5V using a TTL-compatible 5-bit digital code to meet Intel specifications. The IC can read the signal from a DIP-switch, hardwired to Pentium II processor's pins or from software. The 5-bit code adjusts the output voltage between 1.30 and 2.05V in 50mV increments, and between 2.0 and 3.5V in 100mV increments. The device can drive dual MOSFET's resulting in typical efficiencies of 85 - 90%, even with loads in excess of 10A.

**Short-circuit Current Limiting without Expensive Current Sense Resistors.** The current sensing mechanism can use a PCB trace resistance or the parasitic resistance of the main inductor. For applications requiring a high degree of accuracy, a conventional sense resistor can be used.

**Ultra-Fast Transient Response Reduces System Cost.** The fixed frequency modulated off-time architecture results in the fastest transient response for a given inductor.

**Small Package Size.** The LX1669 is available in an economical 16-pin narrow body SOIC package.

NOTE: For current data & package dimensions, visit our web site: http://www.linfinity.com.

#### **KEY FEATURES**

- 5-Bit Programmable Output For CPU Core Supply

- Power Solution For Pentium II Processors

- No Sense Resistor Required For Short-Circuit Current Limiting

- Soft-Start And Hiccup-Mode Current Limiting Functions

- Modulated Constant Off-Time Control Mechanism For Fast Transient Response And Simple System Design

- Power Good Flag

- Over-Voltage Pin Can Drive SCR Crowbar Or Turn Off Signal Silver-Box Power Supply

- Digital-Compatible Inputs (Including VID Pins)

#### APPLICATIONS

- Socket 7 Processor Supplies

- Pentium II Processor Supplies

- Deschutes CPU & L2-Cache Memory Supplies

- Voltage Regulator Modules

- General Purpose And Microprocessor DC:DC Supplies

#### Copyright © 1999 Rev. 1.0 4/99 11861 WESTER

#### $W_{\text{construct}} = C_{\text{construct}} = C_{\text{constr$

11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

# PROGRAMMABLE DC:DC CONTROLLER

## PRODUCTION DATA SHEET

#### ABSOLUTE MAXIMUM RATINGS (Note 1 & 2)

| 12V Supply Voltage (V <sub>CC12</sub> )  | 18V            |

|------------------------------------------|----------------|

| 5V Supply Voltage (V <sub>CC</sub> )     |                |

| Output Drive Peak Current Source (500ns) | 1.0A           |

| Output Drive Peak Current Sink (500ns)   | 1.0A           |

| Input Voltage (SS, VID[0:4])             | 0.3V to 6V     |

| Operating Junction Temperature           | 150°C          |

| Storage Temperature Range                | 65°C to +150°C |

| Lead Temperature (Soldering, 10 Seconds) | 300°C          |

|                                          |                |

Note 1. Exceeding these ratings could cause damage to the device. All voltages are with respect to Ground. Currents are positive into, negative out of the specified terminal.

Note 2.  $V_{ccs}$  supply is used as input to internal low dropout regulator. Voltages above 3.3V will cause increased thermal dissipation in the package. Power dissipation should be limited to keep junction temperature below maximum rating.

#### THERMAL DATA

#### D PACKAGE:

THERMAL RESISTANCE-JUNCTION TO AMBIENT,  $\theta_{JA}$

120°C/W

Junction Temperature Calculation:  $T_J = T_A + (P_D \ge \theta_{JA})$ .

The  $\theta_{jA}$  numbers are guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

#### PACKAGE PIN OUTS

(Top View)

PRODUCTION DATA SHEET

|                                          | C                  | Cumbel Test Conditions                                                                                             |      |      | LX1669 |     |  |

|------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|------|------|--------|-----|--|

| Parameter                                | Symbol             | Test Conditions                                                                                                    | Min. | Тур. | Max.   | Uni |  |

| Reference & DAC                          |                    |                                                                                                                    |      |      |        | -   |  |

| Initial Accuracy                         | V <sub>CORE</sub>  | (Less 40mV output adaptive positioning), $1.3V \leq V_{\text{CORE}} \leq 3.5V,  T_{\text{A}} = 25^{\circ}\text{C}$ | -1   |      | +1     | %   |  |

| Cumulative Regulation Accuracy           |                    | $1.3V \le V_{CORE} \le 3.5V$                                                                                       | -1.5 |      | 1.5    | %   |  |

| Timing                                   |                    |                                                                                                                    |      |      |        | _   |  |

| Off Time                                 | OT                 | $V_{CORE} = 2.0V$                                                                                                  |      | 2.4  |        | μ   |  |

| Switching Frequency                      | Freq               | $V_{CORE} = 1.3V$ to $3.5V$                                                                                        |      | 250  |        | k⊦  |  |

| Error Comparator / CS-                   |                    |                                                                                                                    |      |      |        |     |  |

| Input Bias Current                       | I <sub>FB</sub>    | $1.0V < V_{SS} = V_{FB} < 3.5V$                                                                                    |      | -0.3 | -1     | μ   |  |

| E <sub>c</sub> Delay to Output           |                    | $Overdrive \leq 5mV$                                                                                               |      | 100  |        | n   |  |

| Current Sense +                          |                    |                                                                                                                    |      |      |        | •   |  |

| Input Resistance                         | R <sub>CORE</sub>  | $0V < V_{FB} = V_{CORE} < 3.5V$                                                                                    |      | 12   |        | k   |  |

| Pulse By Pulse Current Limit             | V <sub>CLP</sub>   |                                                                                                                    | 45   | 60   |        | m   |  |

| Current Sense Delay To Output            |                    | $Overdrive \leq 5mV$                                                                                               |      | 100  |        | r   |  |

| Output Drivers                           |                    |                                                                                                                    |      |      |        |     |  |

| Drive Rise Time, Fall Time               | T <sub>RF</sub>    | C <sub>L</sub> = 3000pF                                                                                            |      | 100  |        | r   |  |

| Drive High                               | V <sub>DH</sub>    | I <sub>SOURCE</sub> = 20mA                                                                                         | 10   | 11   |        | , I |  |

| Drive Low V <sub>DL</sub>                |                    | I <sub>SINK</sub> = 20mA                                                                                           |      | 0.1  | 0.2    | , I |  |

| UVLO and Soft-Start (SS)                 |                    |                                                                                                                    |      |      | 1      |     |  |

| V <sub>ccs</sub> Start-Up Threshold      | V <sub>st</sub>    | V <sub>cc12</sub> > 3.9V                                                                                           | 3.9  | 4.2  | 4.6    | ۱ N |  |

| Hysteresis                               |                    |                                                                                                                    |      | 0.10 |        |     |  |

| SS Resistor                              | R <sub>ss</sub>    |                                                                                                                    |      | 18   |        | k   |  |

| SS Output Enable                         | V <sub>EN</sub>    |                                                                                                                    | 0.4  | 0.5  |        |     |  |

| Hiccup Duty Cycle                        | DC                 | C <sub>ss</sub> = 0.1µF, V <sub>DAC</sub> = 2.00V, F <sub>REQ</sub> = 100Hz                                        |      | 10   |        | 9   |  |

| Supply Current                           | I FIC              |                                                                                                                    |      | 1    |        |     |  |

| V <sub>cc12</sub> Dynamic Supply Current | I <sub>CD</sub>    | Out Freq = 200kHz, $C_1$ = 3000pF, Synch., $V_{ss} > 0.5V$                                                         |      | 24   |        | m   |  |

| Static Supply Current 12V                | I <sub>VCC12</sub> | V <sub>ss</sub> < 0.5V                                                                                             |      | 6    | 9      | m   |  |

| 57                                       | I <sub>VCC5</sub>  | <sup>33</sup><br>V <sub>ss</sub> < 0.5V                                                                            |      | 13   | 18     | m   |  |

| Power Good / Over-Voltage Pro            | 1000               |                                                                                                                    |      | 1    | 1      |     |  |

| Threshold                                |                    | $(V_{CORE} / V_{SET})$ $V_{CORE}$ rising, $V_{OUT2} \ge 2.0V$                                                      | 108  | 110  | 111    | 9   |  |

|                                          |                    | $(V_{CORE} / V_{SET})$ $V_{CORE}$ falling, $V_{OUT2} \ge 2.0V$                                                     | 90   | 91   | 92     | 9   |  |

| Hysteresis                               |                    |                                                                                                                    |      | 2    |        | 9   |  |

| Power Good Voltage Low                   |                    | $I_{PWRGD} = 4mA$                                                                                                  |      | 0.5  | 0.7    | 1   |  |

| Over-Voltage Threshold                   |                    | (V <sub>CORE</sub> / V <sub>SET</sub> ), V <sub>CORE</sub> rising                                                  | 110  | 117  | 125    | 9   |  |

| OVP Sourcing Current                     |                    | $V_{OVP} = 2.0V$                                                                                                   | 35   | 60   |        | m   |  |

| VID Pins                                 | I                  | orr in                                                                                                             |      | 1    | 1      |     |  |

| Low Input                                | V,                 | Internally pulled up to V <sub>cc5</sub> thru 30k                                                                  |      |      | 0.8    |     |  |

| High Input                               | V <sub>H</sub>     | , , , , , , , , , , , , , , , , , , ,                                                                              | 2.0  |      |        |     |  |

# PROGRAMMABLE DC:DC CONTROLLER

**PRODUCTION DATA SHEET**

| Processor Pins |      |              |      | Outr | out Voltage (V <sub>set</sub> ) |                                     |  |

|----------------|------|--------------|------|------|---------------------------------|-------------------------------------|--|

|                | 0 =  | Low, $1 = 1$ | ligh |      | Set ( SET                       |                                     |  |

| VID4           | VID3 | VID2         | VID1 | VID0 | 0.0A                            | Nominal Output* (V <sub>SET</sub> ) |  |

| 0              | 1    | 1            | 1    | 1    | 1.34V                           | 1.30V                               |  |

| 0              | 1    | 1            | 1    | 0    | 1.39V                           | 1.35V                               |  |

| 0              | 1    | 1            | 0    | 1    | 1.44V                           | 1.40V                               |  |

| 0              | 1    | 1            | 0    | 0    | 1.49V                           | 1.45V                               |  |

| 0              | 1    | 0            | 1    | 1    | 1.54V                           | 1.50V                               |  |

| Ō              | 1    | Ō            | 1    | Ó    | 1.59V                           | 1.55V                               |  |

| Ō              | 1    | Ō            | 0    | 1    | 1.64V                           | 1.60V                               |  |

| Ō              | 1    | Ō            | Ō    | Ó    | 1.69V                           | 1.65V                               |  |

| Ō              | 0    | 1            | 1    | 1    | 1.74V                           | 1.70V                               |  |

| Ō              | 0    | 1            | 1    | Ó    | 1.79V                           | 1.75V                               |  |

| 0              | 0    | 1            | 0    | 1    | 1.84V                           | 1.80V                               |  |

| 0              | 0    | 1            | 0    | 0    | 1.89V                           | 1.85V                               |  |

| 0              | 0    | 0            | 1    | 1    | 1.94V                           | 1.90V                               |  |

| 0              | 0    | 0            | 1    | 0    | 1.99V                           | 1.95V                               |  |

| 0              | 0    | 0            | 0    | 1    | 2.04V                           | 2.00V                               |  |

| 0              | 0    | 0            | 0    | 0    | 2.09V                           | 2.05V                               |  |

| 1              | 1    | 1            | 1    | 1    | 2.04V                           | 2.00V                               |  |

| 1              | 1    | 1            | 1    | 0    | 2.14V                           | 2.10V                               |  |

| 1              | 1    | 1            | 0    | 1    | 2.24V                           | 2.20V                               |  |

| 1              | 1    | 1            | 0    | 0    | 2.34V                           | 2.30V                               |  |

| 1              | 1    | 0            | 1    | 1    | 2.44V                           | 2.40V                               |  |

| 1              | 1    | 0            | 1    | 0    | 2.54V                           | 2.50V                               |  |

| 1              | 1    | 0            | 0    | 1    | 2.64V                           | 2.60V                               |  |

| 1              | 1    | 0            | 0    | 0    | 2.74V                           | 2.70V                               |  |

| 1              | 0    | 1            | 1    | 1    | 2.84V                           | 2.80V                               |  |

| 1              | 0    | 1            | 1    | 0    | 2.94V                           | 2.90V                               |  |

| 1              | 0    | 1            | 0    | 1    | 3.04V                           | 3.00V                               |  |

| 1              | 0    | 1            | 0    | 0    | 3.14V                           | 3.10V                               |  |

| 1              | 0    | 0            | 1    | 1    | 3.24V                           | 3.20V                               |  |

| 1              | 0    | 0            | 1    | 0    | 3.34V                           | 3.30V                               |  |

| 1              | 0    | 0            | 0    | 1    | 3.44V                           | 3.40V                               |  |

| 1              | 0    | 0            | 0    | 0    | 3.54V                           | 3.50V                               |  |

## **ELECTRICAL CHARACTERISTICS**

\* Nominal = DAC setpoint voltage with no adaptive output voltage positioning.

# Note:

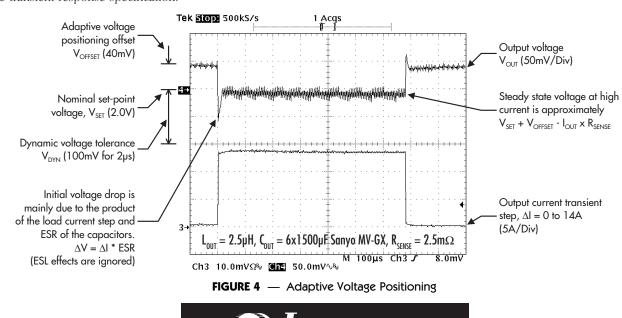

## Adaptive Transient Voltage Output

In order to improve transient response a 40mV offset is built into the voltage comparator. At high currents, the peak output voltage will be lower than the nominal set point, as shown in Figure 4. The actual output voltage will be a function of the sense resistor, output current and output ripple.

# PROGRAMMABLE DC:DC CONTROLLER

**PRODUCTION DATA SHEET**

5

PRODUCTION DATA SHEET

# FUNCTIONAL PIN DESCRIPTION

| Pin<br>Number          | Pin<br>Designator                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | TDRV                                 | Gate drive to the top FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2                      | V <sub>CC12</sub>                    | +12V supply for the gate drivers. If 12V is not available in the application, a bootstrap circuit is required to create the biasing voltage for the FET gate drivers.                                                                                                                                                                                                                                                                                                                         |

| 3                      | V <sub>CC5</sub>                     | +5V supply for internal biasing and power to the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4                      | PWRGD                                | Open collector output, pulled down when the core voltage is not within ±10% of the DAC output.                                                                                                                                                                                                                                                                                                                                                                                                |

| 5                      | OVP                                  | Over-voltage protection: this pin is pulled to above 3V when the switcher output is above 17% of its set voltage. This pin is capable of sourcing 40mA current, and can be used to drive an SCR crowbar or as a signal to turn off the main power supply.                                                                                                                                                                                                                                     |

| 6<br>7<br>8<br>9<br>10 | VID0<br>VID1<br>VID2<br>VID3<br>VID4 | Input pins to the DAC. The output of the DAC sets the nominal voltage of the PWM output (see Table 1).<br>These inputs are TTL-compatible.                                                                                                                                                                                                                                                                                                                                                    |

| 11                     | V <sub>CORE</sub>                    | Output (CPU core) voltage, connected to the output of the regulator (after the sense resistor). This pin is also connected to the power good and the over current comparators in the IC.                                                                                                                                                                                                                                                                                                      |

| 12                     | V <sub>FB</sub>                      | Dual function pin for feedback and current sensing. The peak voltage of this is set 40mV above the nominal set-point (VID) voltage. When the voltage difference between this pin and $V_{OUT}$ (pin 15) exceeds 60mV, the over current comparator will be tripped. The over current tripping level can be set as $I = 60mV/R_{SENSE}$ where $R_{SENSE}$ is the sensing resistance (see Application Note section).                                                                             |

| 13                     | SS/ENABLE                            | Soft-startup and hiccup capacitor pin. During startup, the voltage of this pin controls the core voltage. An internal $20k\Omega$ resistor and the external capacitor set the time constant for the soft-startup. Soft-start does not begin until the supply voltage exceeds the UVLO threshold. When over-current occurs, this capacitor is used for timing the hiccup. See Application Information for more detail. The PWM output can be disabled by pulling the SS/ENABLE pin below 0.5V. |

| 14                     | AGND                                 | Analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15                     | BDRV                                 | Bottom FET drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16                     | PGND                                 | Power ground. Ground return for FET drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## PRODUCTION DATA SHEET

## THEORY OF OPERATION

### SWITCHER OUTPUT VOLTAGE REGULATION

#### **POWER UP and INITIALIZATION**

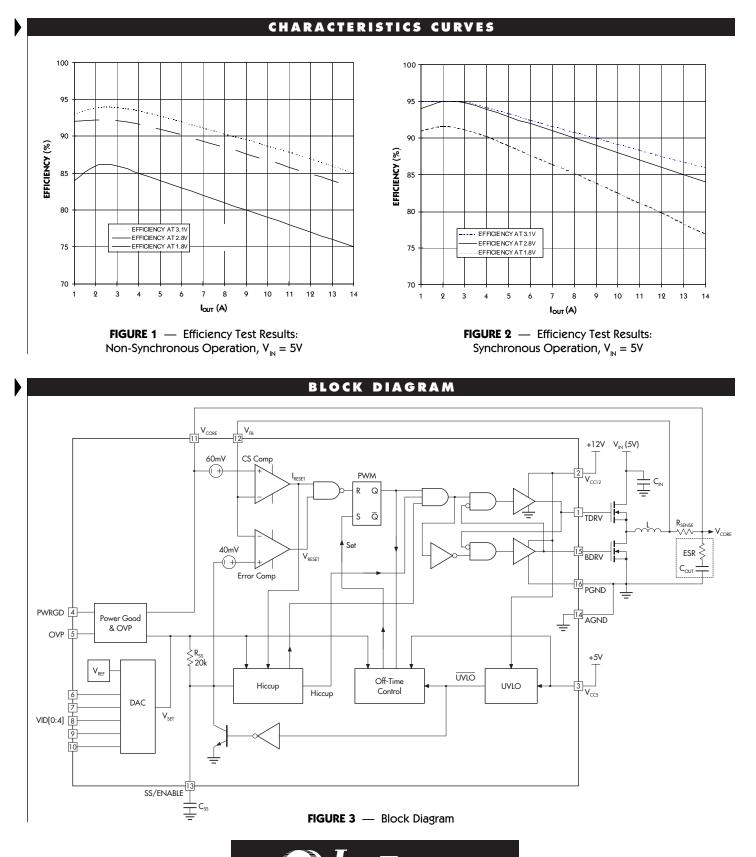

Refer to the IC Block Diagram and the Product Highlight circuit. When the top MOSFET turns ON, the inductor current increases. The voltage at  $V_{FB}$  pin increases due to the ESR of the output capacitor and the current-sensing resistor. When the  $V_{FB}$  pin voltage reaches the threshold voltage of the error comparator,  $V_{SET}$  (the DAC output set-point voltage) plus 40mV offset, the PWM latch is reset. Consequently, the top MOSFET turns OFF and the bottom (synchronous) MOSFET turns ON. The off-time control block controls the off-time of the top MOSFET. During the off-time, the inductor current and the  $V_{FB}$  pin voltage decrease. As the off-time finishes, the synchronous MOSFET turns OFF and the top MOSFET turns ON again, repeating the previous cycle. A break-before-make circuit prevents simultaneous conduction of the two MOSFET's.

The 40mV offset to the set voltage enhances the transient response of the output voltage, as shown in Figure 4 below.

- The peak voltage at the V<sub>FB</sub> pin is 40mV higher than the set voltage and its average is the peak voltage minus the ripple voltage at V<sub>FB</sub> pin.

- The output voltage is the voltage at the V<sub>FB</sub> pin minus the voltage drop across the current sensing resistor (I \* R<sub>SENSF</sub>).

- At light loads, the voltage drop across the sensing resistor is small; hence, the output voltage is approximately the voltage at the  $V_{FB}$  pin (approximately 40mV higher than the set voltage,  $V_{SFT}$ ).

- At heavy loads, larger current flows in the sense resistor, therefore, the voltage drop is higher and the output voltage is lower.

This adaptive positioning of the output voltage as the load changes allows a greater output voltage excursion during a fast step-load transient and requires fewer output capacitors to meet the transient-response specification. At power up, the LX1669 monitors the supply voltage to both the +5V and the +12V pins (there is no special requirement for the sequence of the two supplies). Before both supplies reach their under-voltage lock-out (UVLO) thresholds, the soft-start (SS) pin is held low to prevent soft-start from beginning; the off-time control is disabled and the top MOSFET is kept OFF. After both supplies pass the UVLO thresholds, the circuit begins soft-start.

#### SOFT-START

Once the supplies are above the UVLO threshold, the soft-start capacitor begins to be charged up by the set voltage (DAC output) through a  $20k\Omega$  internal resistor. The capacitor voltage at the SS pin rises as a simple RC circuit. The SS pin plus a 40mV offset is connected to the error comparator's non-inverting input that controls the output peak voltage. The output voltage will follow the SS pin voltage if sufficient charging current is provided to the output capacitor.

The simple RC soft-start allows the output to rise faster at the beginning and slower at the end of the soft-start interval. Thus, the required charging current into the output capacitor is less at the end of the soft-start interval so decreasing the possibility of an over-current. A comparator monitors the SS pin voltage and indicates the end of soft-start when SS pin voltage reaches 95% of  $V_{\rm SFF}$ . See Application Information section for further details.

# Programmable DC:DC Controller

### **PRODUCTION DATA SHEET**

### THEORY OF OPERATION

#### **OVER-CURRENT PROTECTION (OCP) and HICCUP**

The over-current protection function is tripped when the inductor current exceeds its maximum limit. The current is sensed with a resistor in series with the inductor. When the voltage across the sensing resistor exceeds the 60mV threshold, the OCP comparator outputs a signal to reset the PWM latch and to start hiccup mode. The soft-start capacitor,  $C_{ss}$ , is discharged slowly (10 times slower than when being charged up by  $R_{ss}$ ). When the voltage on the SS/ENABLE pin reaches a 0.3V threshold, hiccup finishes and the circuit soft-starts again. During hiccup, the top MOSFET is OFF and the bottom MOSFET remains ON.

Hiccup is disabled during the soft-start interval, allowing the circuit to start up with the maximum current. If the rise speed of the output voltage is too fast, the required charging current to the output capacitor may be higher than the limit-current. In this case, the peak inductor current is regulated to the limit-current by the current-sense comparator. The top MOSFET is turned on at the end of the controlled off-time and is turned off when the inductor current reaches the limit. If the inductor current still reaches its limit after the soft-start finishes, the hiccup is triggered again. The hiccup ensures the average heat generation on both MOSFET's and the average current to be much less than that in normal operation, if the output has a short circuit.

### **OVER-VOLTAGE PROTECTION (OVP)**

The output voltage is inherently protected from an over-voltage situation because of the peak-voltage control mechanism. Whenever the  $V_{FB}$  pin voltage is higher than the set voltage by 40mV, the top MOSFET is turned off and the bottom MOSFET is turned on. In the case that a fault condition occurs where the

### **OVER-VOLTAGE PROTECTION (OVP)** (continued)

output voltage exceeds the 117%  $V_{SET}$  threshold, the OVP comparator will pull up the OVP pin to 2 volts. The OVP pin has a 40mA source current capability, so it can be used to trigger an SCR crowbar or shut off the main power supply.

#### **OFF-TIME CONTROL and SWITCHING FREQUENCY**

An internal timer controls the off-time of the top MOSFET so that the switching frequency is constant at 250kHz under steady-state operation. The timer begins timing once the PWM latch is reset and set the PWM flip-flop again when the off-time finishes. The off-time is controlled to be:

$$T_{OFF} = 4\mu s (1 - V_{OUT} / V_{CC5})$$

For a buck converter, the switching frequency is

$$f_{SW} = (1 - V_{OUT} / V_{CC5}) / T_{OFF}$$

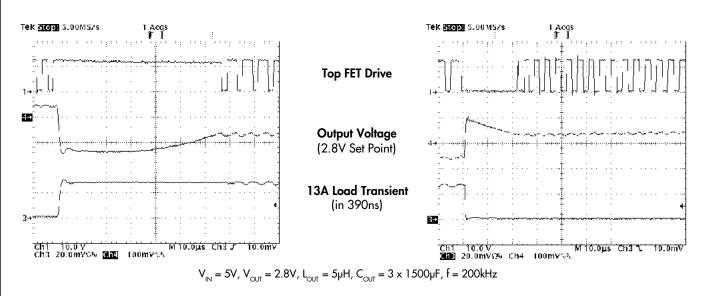

Therefore, the switching frequency is nearly constant in steady state operation. During transient loading, the top drive can remain switched on or off until the output voltage is within specification (see Figure 5) in order to reduce transient response time.

#### POWER GOOD OUTPUT

An open-collector output, PWRGD, is provided to indicate the status of the output voltages. PWRGD presents high impedance when the switcher output voltage is within  $\pm 10\%$  of its set voltage. Otherwise, PWRGD presents a low impedance path to ground.

# PROGRAMMABLE DC:DC CONTROLLER

PRODUCTION DATA SHEET

# BILL OF MATERIALS

## LX1669 Bill of Materials (Refer to Product Highlight)

| Ref                | Description                       | Part Number / Manufacturer                | Qty. |

|--------------------|-----------------------------------|-------------------------------------------|------|

| U1                 | Controller IC                     | LX1668 - LinFinity                        | 1    |

| C1                 | Capacitor, 1500μF, 6.3V, 44mΩ ESR | MV-GX Sanyo                               | 6    |

| C2                 | Capacitor, 1500μF, 6.3V, 44mΩ ESR | MV-GX Sanyo                               | 3    |

| C8                 | Capacitor, 1µF, SMD               |                                           | 2    |

| C3                 | Capacitor, 1µF, SMD, 16V          |                                           | 1    |

| CSS                | Capacitor, 0.1µF, SMD             |                                           | 1    |

| Q1                 | MOSFET (low R <sub>DSIONI</sub> ) | IRL3102/3103, International Rectifier     | 1    |

| Q2                 | MOSFET (low R <sub>DSIONI</sub> ) | IRL3303/3103, International Rectifier     | 1    |

| R <sub>sense</sub> | Sense Resistor, $2.5m\Omega$      | PCB trace                                 | 1    |

| L1                 | Inductor, 2 - 3µH                 | HM00-97713 or HM00-98637, BI Technologies | 1    |

| L2                 | Inductor, 1µH                     |                                           | 1    |

| Total Nun          | ber of Components                 |                                           | 19   |

Optional Components for Over-Voltage Protection and Power Good Signal

| Q4 | SCR            | 2N6504 | 1 |

|----|----------------|--------|---|

| R3 | Resistor, 10kΩ | SMD    | 1 |

# PROGRAMMABLE DC:DC CONTROLLER

PRODUCTION DATA SHEET

#### APPLICATION INFORMATION Tek Run: 500kS/s Tek Stop: 500kS/s Sample 2 Acq **Output Voltage** (2.8V Set Point) Input Ripple Voltage Input Current $L_{out} = 5\mu H, L_{IN} = 0$ L<sub>out</sub> = 2.2μH, L<sub>in</sub> = 0 M 100µs Ch3 J 4 8m Ch1 100mV M 100µs Ch1 J Ch1 100mV∿ Ch3 10.0mVΩ Ch3 10.0mVΩ% Ch4 2.00 V∿% 1.00 V∿ Ch4

#### FIGURE 6 — Effect Of Different Inductor Values

### OUTPUT INDUCTOR

The output inductor should be selected to meet the requirements of the output voltage ripple in steady-state operation and the inductor current slew-rate during transient.

The peak-to-peak output voltage ripple is:

$$V_{RIPPLE} = ESR * I_{RIPPLE}$$

where

$$I_{RIPPLE} = \frac{(V_{IN} - V_{OUT})}{f_{SW} * L} * \frac{V_{OUT}}{V_{IN}}$$

${\rm I}_{\rm RIPPLE}$  is the inductor ripple current, L is the output inductor value and ESR is the Effective Series Resistance of the output capacitor.

$I_{RIPPLE}$  should typically be in the range of 20% to 40% of the maximum output current. Higher inductance results in lower output voltage ripple, allowing slightly higher ESR to satisfy the transient specification. Higher inductance also slows the inductor current slew rate in response to the load-current step change,  $\Delta I$ , resulting in more output-capacitor voltage droop. The inductor-current rise and fall times are:

$$T_{RISE} = L * \Delta I / (V_{IN} - V_{OUT})$$

and

$$T_{FALL} = L * \Delta I / V_{OUT}$$

When using electrolytic capacitors, the capacitor voltage droop is usually negligible, due to the large capacitance.

For higher current applications, such as Pentium II processors, a 2.5µH inductor is recommended for the best combination of fast response and manageable ripple voltage. For lower current applications, such as Pentium and other Socket 7 processors, a  $5\mu$ H inductor is sufficient. The effect of different inductor values is shown in Figure 6 above.

Notice how, with a smaller inductor, transient response time is improved, but at the expense of much greater ripple.

#### INPUT INDUCTOR

In order to supply faster transient load changes, a smaller output inductor is needed. However, reducing the size of the output inductor will result in a higher ripple voltage on the input supply, as shown in Figure 6 above. This noise on the 5V rail can affect other system components, such as graphics cards. It is recommended that a  $1 - 1.5\mu$ H inductor, L2, is used on input to the regulator, to filter the ripple on the 5V supply. Ensure that this inductor has the same current rating as the output inductor.

#### **OUTPUT CAPACITOR**

The output capacitor is sized to meet ripple and transient performance specifications. Effective Series Resistance (ESR) is a critical parameter. When a step load current occurs, the output voltage will have a step that equals the product of the ESR and the current step,  $\Delta I$ . In an advanced microprocessor power supply, the output capacitor is usually selected for ESR instead of capacitance or RMS current capability. A capacitor that satisfies the ESR requirement usually has a larger capacitance and current capability than strictly needed. The allowed ESR can be found by:

$$ESR * (I_{RIPPLF} + \Delta I) < V_{FX}$$

where  $I_{_{RIPPLE}}$  is the inductor ripple current,  $\Delta I$  is the maximum load current step change, and  $V_{_{\rm FX}}$  is the allowed output voltage

## PRODUCTION DATA SHEET

### APPLICATION INFORMATION

#### **OUTPUT CAPACITOR** (continued)

excursion in the transient. Adaptive voltage positioning increases the value of V<sub>EX</sub>, allowing a higher ESR value and reducing the cost of the output capacitor. The positioning voltage is 40mV (peak), using the LX1669, and the transient tolerance is 100mV, resulting in a V<sub>EX</sub> of 140mV (see Figure 4).

Electrolytic capacitors can be used for the output capacitor, but are less stable with age than tantalum capacitors. As they age, their ESR degrades, reducing the system performance and increasing the risk of failure. It is recommended that multiple parallel capacitors be used, so that, as ESR increases with age, overall performance will still meet the processor's requirements.

There is frequently strong pressure to use the least expensive components possible, however, this could lead to degraded long-term reliability, especially in the case of filter capacitors. Linfinity's demonstration boards use Sanyo MV-GX filter capacitors, which are aluminum electrolytic, and have demonstrated reliability. The Oscon series from Sanyo generally provides the very best performance in terms of long term ESR stability and general reliability, but at a substantial cost penalty. The MV-GX series provides excellent ESR performance at a reasonable cost. Beware of off-brand, very low-cost filter capacitors, which have been shown to degrade in both ESR and general electrolytic characteristics over time.

#### INPUT CAPACITOR

The input capacitor and the input inductor are to filter the pulsating current generated by the buck converter to reduce interference to other circuits connected to the same 5V rail. In addition, the input capacitor provides local de-coupling the buck converter. The capacitor should be rated to handle the RMS current requirement. The RMS current is:

$$I_{RMS} = I_L \sqrt{d(1-d)}$$

where  $I_L$  is the inductor current and the d is the duty cycle. The maximum value, when d = 50%,  $I_{RMS} = 0.5I_L$ . For 5V input and output in the range of 2 to 3V, the required RMS current is very close to  $0.5I_L$ .

A high-frequency (ceramic) capacitor should be placed across the drain of the top MOSFET and the source of the bottom one to avoid ringing due to the parasitic inductor being switched ON and OFF. See capacitor C7 in the Product Highlight.

### SOFT-START CAPACITOR

The value of the soft-start capacitor determines how fast the output voltage rises and how large the inductor current is required to charge the output capacitor. The output voltage will follow the voltage at SS pin if the required inductor current does not exceed the maximum current in the inductor.

#### SOFT-START CAPACITOR (continued)

The SS pin voltage can be expressed as:

$$V_{SS} = V_{SET} (1 - e^{-t/R_{SS}C_{SS}})$$

where  $V_{SET}$  is the output of the DAC.  $R_{SS}$  and  $C_{SS}$  are soft start resistor and capacitor, as shown in Figure 3. The required inductor current for the output capacitor to follow the SS-pin voltage equals the required capacitor current plus the load current. The soft-start capacitor should be selected so that the overall inductor current does not exceed it maximum.

The capacitor current to follow the SS-pin voltage is:

$$I_{Cout} = C_{OUT} \frac{dV}{dt} = \frac{C_{OUT}}{C_{SS}} * e^{(t/R_{SS}C_{SS})}$$

where  $C_{OUT}$  is the output capacitance. The typical value of  $C_{ss}$  should be in the range of 0.1 to 0.2µF.

During the soft-start interval, before the PWRGD signal becomes valid, the load current from a microprocessor is negligible; therefore, the capacitor current is approximately the required inductor current.

#### **CURRENT LIMIT**

Current limiting occurs when a sensed voltage, proportional to load current, exceeds the current-sense comparator threshold value. The current can be sensed either by using a fixed sense resistor in series with the inductor to cause a voltage drop proportional to current, or by using a resistor and capacitor in parallel with the inductor to sense the voltage drop across the parasitic resistance of the inductor. The LX1669 has a threshold of 60mV.

#### **Sense Resistor**

The current sense resistor,  $\mathrm{R}_{\mathrm{SENSE}}$  is selected according to the formula:

$$R_{SENSE} = V_{TRIP} / I_{TRIP}$$

Where  $V_{TRIP}$  is the current sense comparator threshold (60mV) and  $I_{TRIP}$  is the desired current limit. Typical choices are shown below.

#### **TABLE 2 - Current Sense Resistor Selection Guide**

| Load                           | Sense Resistor<br>Value |

|--------------------------------|-------------------------|

| Pentium-Class Processor (<10A) | 5mΩ                     |

| Pentium II Class (>10A)        | 2.5mΩ                   |

A smaller sense resistor will result in lower heat dissipation (I<sup>2</sup>R) and also a smaller output voltage droop at higher currents.

# PROGRAMMABLE DC:DC CONTROLLER

**PRODUCTION DATA SHEET**

## APPLICATION INFORMATION

#### CURRENT LIMIT (continued)

There are several alternative types of sense resistor. The surface-mount metal "staple" form of resistor has the advantage of exposure to free air to dissipate heat and its value can be controlled very tightly. Its main drawback, however, is cost. An alternative is to construct the sense resistor using a copper PCB trace. Although the resistance cannot be controlled as tightly, the PCB trace is very low cost.

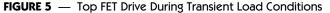

#### **PCB Sense Resistor**

A PCB sense resistor should be constructed as shown in Figure 7. By attaching directly to the large pads for the capacitor and inductor, heat is dissipated efficiently by the larger copper masses. Connect the current sense lines as shown to avoid any errors.

FIGURE 7 — Sense Resistor Construction Diagram

Recommended sense resistor sizes are given in the following table:

| Copper<br>Weight | Copper<br>Thickness | Desired Resistor<br>Value | Dimensio<br>mm | ns (w x l)<br>inches |  |  |  |

|------------------|---------------------|---------------------------|----------------|----------------------|--|--|--|

| 2 oz/ft²         | 68µm                | 2.5mΩ                     | 2.5 x 22       | 0.1 x 0.85           |  |  |  |

|                  |                     | $5 m \Omega$              | 2.5 x 43       | 0.1 x 1.7            |  |  |  |

#### TABLE 3 - PCB Sense Resistor Selection Guide

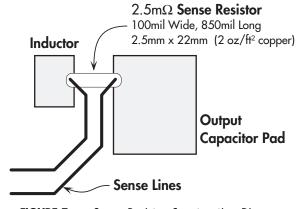

#### Loss-Less Current Sensing Using Resistance of Inductor

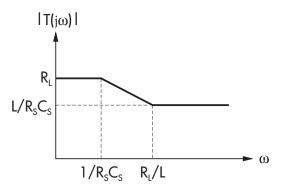

Any inductor has a parasitic resistance  $(R_L)$  which causes a DC voltage drop when current flows through the inductor. Figure 8 shows a sensor circuit comprising of a surface mount resistor,  $R_{s}$ , and capacitor,  $C_{s}$ , in parallel with the inductor, eliminating the current sense resistor.

The current flowing through the inductor is a triangle wave. If the sensor components are selected such that:

$$L/R_L = R_S * C_S$$

FIGURE 8 — Current Sense Circuit

The voltage across the capacitor will be equal to the current flowing through the resistor, i.e.

$V_{CS} = I_L R_L$

Since  $V_{CS}$  reflects the inductor current, by selecting the appropriate  $R_S$  and  $C_S$ ,  $V_{CS}$  can used to sense current.

#### Design Example

(*Pentium II circuit, with a maximum static current of 14.2A*) The gain of the sensor can be characterized as:

FIGURE 9 — Sensor Gain

The dc/static tripping current I<sub>trip,S</sub> satisfies:

$$I_{trip,S} = \frac{V_{trip}}{R_L}$$

Select  $L/R_S C_S \le R_L$  to have higher dynamic tripping current than the static one. The dynamic tripping current  $I_{trip,d}$  satisfies:

$$I_{trip,d} = \frac{V_{trip}}{L/(R_S C_S)}$$

**PRODUCTION DATA SHEET**

## APPLICATION INFORMATION

### CURRENT LIMIT (continued)

General Guidelines for Selecting R<sub>s</sub>, C<sub>s</sub>, and R<sub>L</sub>

$$R_{L} = \frac{V_{trip}}{I_{trip,S}} \qquad \text{Select: } \mathbf{R}_{S} \le 10 \text{ k}\Omega$$

and  $C_{S}$  according to:  $C_{Sn} = \frac{L_{n}}{R R}$

The above equation has taken into account the current-dependency of the inductance.

Typical values are:  $R_L$  = 3m $\Omega,\,R_S$  = 9k $\Omega,\,C_S$  = 0.1µF, and L is 2.5µH at 0A current.

In cases where  $R_L$  is so large that the trip point current would be lower than the desired short-circuit current limit, a resistor ( $R_{s2}$ ) can be put in parallel with  $C_s$ , as shown in Figure 9. The selection of components is as follows:

$$\frac{R_{L(Required)}}{R_{L(Actual)}} = \frac{R_{S2}}{R_{S2} + R_{S}}$$

$$C_{S} = \frac{L}{R_{L(Actual)} * (R_{S2} / / R_{S})} = \frac{L}{R_{L(Actual)}} * \frac{R_{S} + R_{S2}}{R_{S2} * R_{S}}$$

Again, select  $(R_{S2}^{}//R_{S}^{})$  < 10k $\Omega$  . See Application Note AN-7 for more information.

#### **OUTPUT ENABLE**

The LX1669 FET driver outputs are driven to ground by pulling the soft-start pin below 0.5V.

#### **PROGRAMMING THE OUTPUT VOLTAGE**

The output voltage is set by the DAC with a 5-bit digital voltageidentification (VID) code input (see Table 1). The DAC input is designed to be compatible with digital circuits. The VID code may be hard-wired into the package of the processor [as in the case of a Pentium II or Pentium Pro processor]. If the processor does not have a VID code, the output voltage can be set by means of a DIP-switch, jumpers or TTL-compatible digital circuits. When using a DIP-switch or jumpers, connect the VID pin to ground (DIP-switch ON) for a low or "0" signal and leave the VID pin open (DIP-switch OFF) for a high or "1" signal.

#### FET SELECTION

To insure reliable operation, the operating junction temperature of the FET switches must be kept below certain limits. The Intel specification states that 115°C maximum junction temperature should be maintained with an ambient of 50°C. This is achieved by properly derating the part, and by adequate heat sinking. One of the most critical parameters for FET selection is the  $R_{DS(ON)}$  resistance. This parameter directly contributes to the power dissipation of the FET devices, and thus impacts heat sink design, mechanical layout, and reliability. In general, the larger the current handling capability of the FET, the lower the  $R_{DS(ON)}$  will be, since more die area is available.

#### FET SELECTION (continued)

| TABLE 4 - FET Selection Guide                                           |

|-------------------------------------------------------------------------|

| This table gives selection of suitable FETs from International Pactifia |

| Device    | R <sub>DS(ON)</sub> @<br>10V (mΩ) | Ι <sub>D</sub> @<br>Τ <sub>c</sub> = 100°C | Max. Break-<br>down Voltage |

|-----------|-----------------------------------|--------------------------------------------|-----------------------------|

| IRL3803   | 6                                 | 83                                         | 30                          |

| IRL22203N | 7                                 | 71                                         | 30                          |

| IRL3103   | 14                                | 40                                         | 30                          |

| IRL3102   | 13                                | 56                                         | 20                          |

| IRL3303   | 26                                | 24                                         | 30                          |

| IRL2703   | 40                                | 17                                         | 30                          |

All devices in TO-220 package. For surface mount devices (TO-263 /  $D^2$ -Pak), add 'S' to part number, e.g. IRL3103S.

The recommended solution is to use IRL3102 for the high side and IRL3303 for the low side FET, for the best combination of cost and performance. Alternative FET's from any manufacturer could be used, provided they meet the same criteria for  $R_{\rm DS(ON)}$ .

#### Heat Dissipated In Upper MOSFET

The heat dissipated in the top MOSFET will be:

$$P_D = (I^2 * R_{DS(ON)} * Duty Cycle) + (0.5 * I * V_{IN} * t_{SW} * f_S)$$

Where  $t_{sw}$  is switching transition line for body diode (~100ns) and  $f_s$  is the switching frequency.

For the IRL3102 ( $13m\Omega R_{DS(ON)}$ ), converting 5V to 2.0V at 15A will result in typical heat dissipation of 1.92W.

#### Synchronous Rectification – Lower MOSFET

The lower pass element can be either a MOSFET or a Schottky diode. The use of a MOSFET (synchronous rectification) will result in higher efficiency, but at higher cost than using a Schottky diode (non-synchronous).

Power dissipated in the bottom MOSFET will be:

$$P_D = I^2 * R_{DS(ON)} * [1 - Duty Cycle] = 3.51W$$

[IRL3303 or 1.76W for the IRL3102]

#### Non-Synchronous Operation - Schottky Diode

A typical Schottky diode with a forward drop of 0.6V will dissipate  $0.6 \ge 15 * (1-2/5) = 5.4W$  (compared to the 1.8 to 3.5W dissipated by a MOSFET under the same conditions). This power loss becomes much more significant at lower duty cycles – synchronous rectification is recommended. The use of a dual Schottky diode in a single TO-220 package (e.g. the MBR2535) helps improve thermal dissipation.

## PRODUCTION DATA SHEET

## APPLICATION INFORMATION

#### LAYOUT GUIDELINES - THERMAL DESIGN

A great deal of time and effort were spent optimizing the thermal design of the demonstration boards. Any user who intends to implement an embedded motherboard would be well advised to carefully read and follow these guidelines. If the FET switches have been carefully selected, external heatsinking is generally not required. However, this means that copper trace on the PC board must now be used. This is a potential trouble spot; as much copper area as possible must be dedicated to heatsinking the FET switches, and the diode as well if a non-synchronous solution is used.

In our demonstration board, heatsink area was taken from internal ground and  $V_{CC}$  planes which were actually split and connected with VIAS to the power device tabs. The TO-220 and TO-263 cases are well suited for this application, and are the preferred packages. Remember to remove any conformal coating from all exposed PC traces which are involved in heatsinking.

#### General Notes

As always, be sure to provide local capacitive decoupling close to the chip. Be sure use ground plane construction for all highfrequency work. Use low ESR capacitors where justified, but be alert for damping and ringing problems. High-frequency designs demand careful routing and layout, and may require several iterations to achieve desired performance levels.

#### **Power Traces**

To reduce power losses due to ohmic resistance, careful consideration should be given to the layout of traces that carry high currents. The main paths to consider are:

- Input power from 5V supply to drain of top MOSFET.

- Trace between top MOSFET and lower MOSFET or Schottky diode.

- Trace between lower MOSFET or Schottky diode and ground.

- Trace between source of top MOSFET and inductor, sense resistor and load.

- Current traces on both LDO sections

All of these traces should be made as wide and thick as possible, in order to minimize resistance and hence power losses. It is also recommended that, whenever possible, the ground, input and output power signals should be on separate planes (PCB layers). See Figure 10 – bold traces are power traces.

FIGURE 10 — Power Traces

#### Input Decoupling Capacitors

Ensure that capacitors C8 and C3 are placed as close to the IC as possible to minimize the effects of noise on the device.

#### Layout Assistance

Please contact Linfinity's Applications Engineers for assistance with any layout or component selection issues. A Gerber file with layout for the most popular devices is available upon request.

Evaluation boards are also available upon request. Please check Linfinity's web site for further application notes.

#### **RELATED DEVICES**

LX1668

Triple Output Regulator (Programmable switching regulator with internal 2.5V LDO plus linear regulator driver)

Pentium is a registered trademark of Intel Corporation

PRODUCTION DATA- Information contained in this document is proprietary to I.in Finity, and is current as of publication date. This document may not be modified in any way without the express written consent of LinFinity. Product processing does not necessarily include testing of all parameters. Infinity reserves the right to change the configuration and performance of the product and to discontinue product at any time