# **Mobile Low-Power DDR SDRAM**

MT46H32M16LF - 8 Meg x 16 x 4 Banks

MT46H16M32LF – 4 Meg x 32 x 4 Banks

| Features |

|----------|

|----------|

| • | $V_{\rm DD}/V_{\rm DDQ} = 1.70 - 1.95 V$ |  |

|---|------------------------------------------|--|

|---|------------------------------------------|--|

- 1.2V I/O option V<sub>DDO</sub> = 1.14–1.30V

- Bidirectional data strobe per byte of data (DQS)

- Internal, pipelined double data rate (DDR)architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- · Commands entered on each positive CK edge

- · DQS edge-aligned with data for READs;centeraligned with data for WRITEs

- 4 internal banks for concurrent operation

- · Data masks (DM) for masking write data-one mask per byte

- Programmable burst lengths (BL): 2, 4, 8, or 16

- · Concurrent auto precharge option is supported

- · Auto refresh and self refresh modes

- 1.8V LVCMOS-compatible inputs

- · On-chip temp sensor to control self refresh rate

- Partial-array self refresh (PASR)

- Deep power-down (DPD)

- Status read register (SRR)

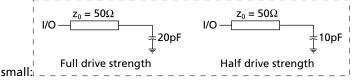

- Selectable output drive strength (DS)

- · Clock stop capability

- 64ms refresh

### Table 1: Key Timing Parameters (CL = 3)

| Speed Grade | Clock Rate (MHz) | Access Time |  |  |

|-------------|------------------|-------------|--|--|

| -5          | 200              | 5.0ns       |  |  |

| -54         | 185              | 5.0ns       |  |  |

| -6          | 166              | 5.0ns       |  |  |

| -75         | 133              | 6.0ns       |  |  |

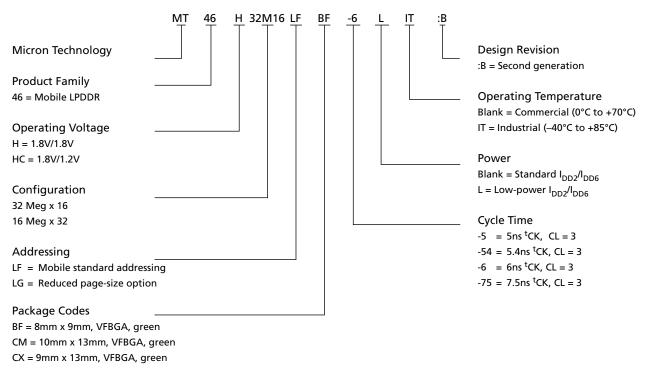

| Options                                                      | Marking |

|--------------------------------------------------------------|---------|

| • V <sub>DD</sub> /V <sub>DDQ</sub>                          |         |

| – 1.8V/1.8V                                                  | Н       |

| $- 1.8V/1.2V^{1}$                                            | HC      |

| Configuration                                                |         |

| - 32 Meg x 16 (8 Meg x 16 x 4 banks)                         | 32M16   |

| - 16 Meg x 32 (4 Meg x 32 x 4 banks)                         | 16M32   |

| Row-size option                                              |         |

| <ul> <li>JEDEC-standard option</li> </ul>                    | LF      |

| <ul> <li>Reduced page-size option<sup>1</sup></li> </ul>     | LG      |

| Plastic green package                                        |         |

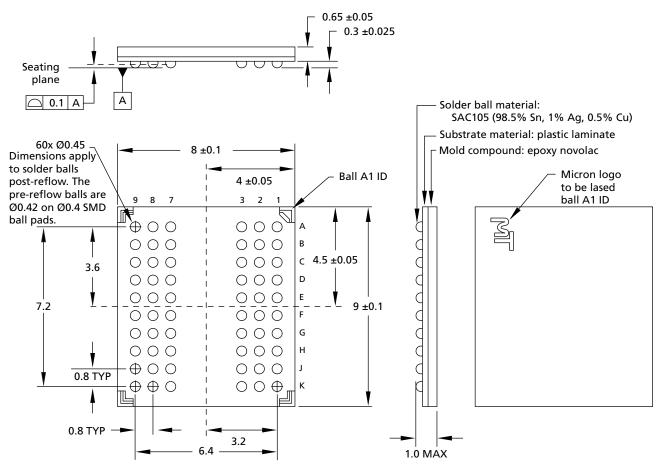

| - 60-ball VFBGA (8mm x 9mm) <sup>2</sup>                     | BF      |

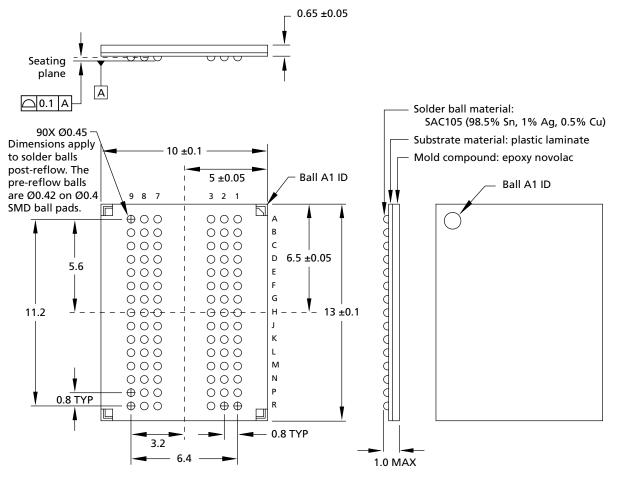

| <ul> <li>90-ball VFBGA (10mm x 13mm)<sup>3</sup></li> </ul>  | CM      |

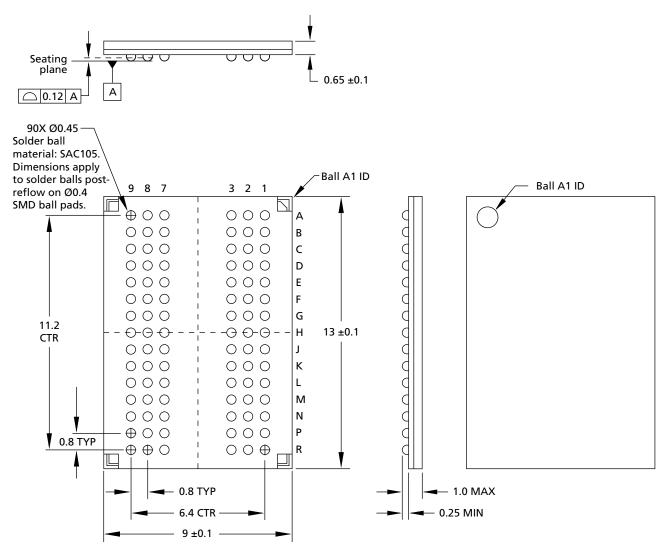

| – 90-ball VFBGA (9mm x 13mm) <sup>3</sup>                    | CX      |

| <ul> <li>Timing – cycle time</li> </ul>                      |         |

| -5ns@CL = 3                                                  | -5      |

| -5.4 ms @ CL = 3                                             | -54     |

| -6ns@CL = 3                                                  | -6      |

| -7.5 m CL $= 3$                                              | -75     |

| • Power                                                      |         |

| <ul> <li>Standard I<sub>DD2</sub>/I<sub>DD6</sub></li> </ul> | None    |

| - Low-power $I_{DD2}/I_{DD6}^{1}$                            | L       |

| Operating temperature range                                  |         |

| – Commercial (0° to +70°C)                                   | None    |

| – Industrial ( $-40^{\circ}$ C to $+85^{\circ}$ C)           | IT      |

| Design revision                                              | :B      |

| Notes: 1. Contact factory for availability                   |         |

- - 2. Only available for x16 configuration.

- 3. Only available for x32 configuration.

PDF: 09005aef82d5d305 512mb\_ddr\_mobile\_sdram\_t47m.pdf - Rev. I 12/09 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice. © 2004 Micron Technology, Inc. All rights reserved. Products and specifications discussed herein are subject to change by Micron without notice.

#### **Table 2: Configuration Addressing 512**

| Architecture      | 32 Meg x 16          | 16 Meg x 32          | Reduced Page-Size Option 16 Meg x 32 |

|-------------------|----------------------|----------------------|--------------------------------------|

| Configuration     | 8 Meg x 16 x 4 banks | 4 Meg x 32 x 4 banks | 4 Meg x 32 x 4 banks                 |

| Refresh count     | 8K                   | 8K                   | 8К                                   |

| Row addressing    | A[12:0]              | A[12:0]              | A[13:0]                              |

| Column addressing | A[9:0]               | A[8:0]               | A[7:0]                               |

#### Figure 1: 512Mb Mobile LPDDR Part Numbering

### **FBGA Part Marking Decoder**

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the part number. Micron's FBGA part marking decoder is available at www.micron.com/decoder.

### 512Mb: x16, x32 Mobile LPDDR SDRAM

# Contents

| General Description                                    |      |

|--------------------------------------------------------|------|

| Functional Block Diagrams                              | 9    |

| Ball Assignments and Descriptions                      | . 11 |

| Package Dimensions                                     |      |

| Electrical Specifications                              | . 18 |

| Electrical Specifications – I <sub>DD</sub> Parameters | . 22 |

| Electrical Specifications – AC Operating Conditions    |      |

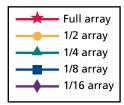

| Output Drive Characteristics                           |      |

| Functional Description                                 |      |

| Commands                                               |      |

| DESELECT                                               |      |

| NO OPERATION                                           |      |

| LOAD MODE REGISTER                                     |      |

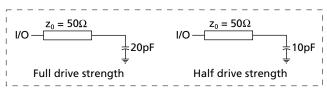

| ACTIVE                                                 |      |

| READ                                                   |      |

| WRITE                                                  |      |

| PRECHARGE                                              |      |

| BURST TERMINATE                                        |      |

| AUTO REFRESH                                           |      |

| SELF REFRESH                                           |      |

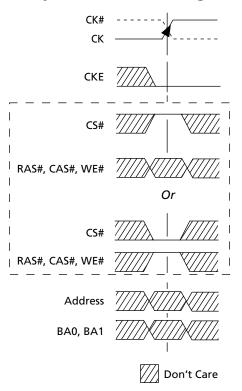

| DEEP POWER-DOWN                                        |      |

| Truth Tables                                           |      |

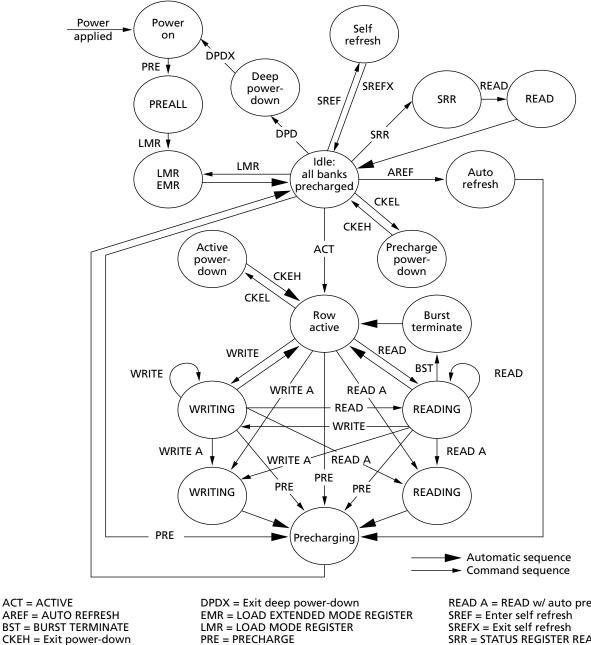

| State Diagram                                          |      |

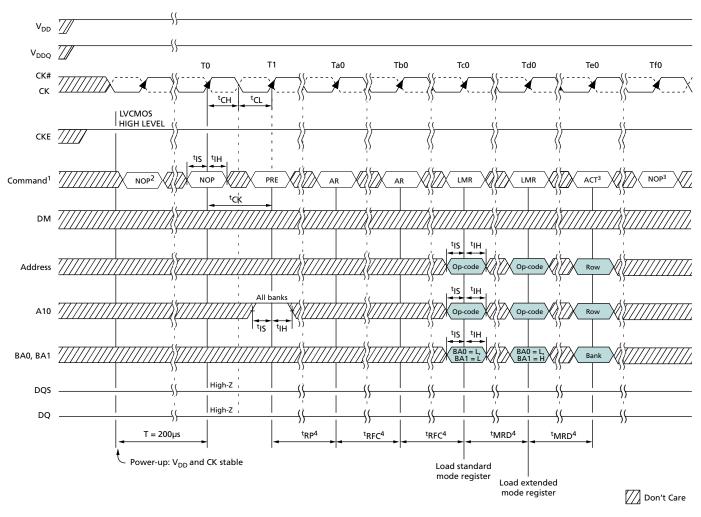

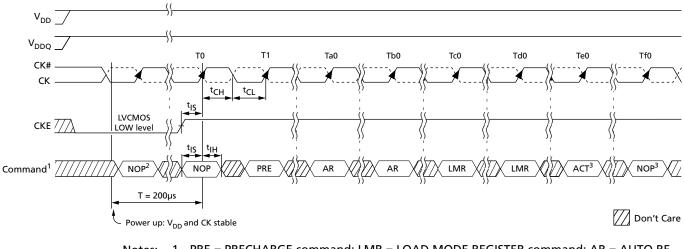

| Initialization                                         |      |

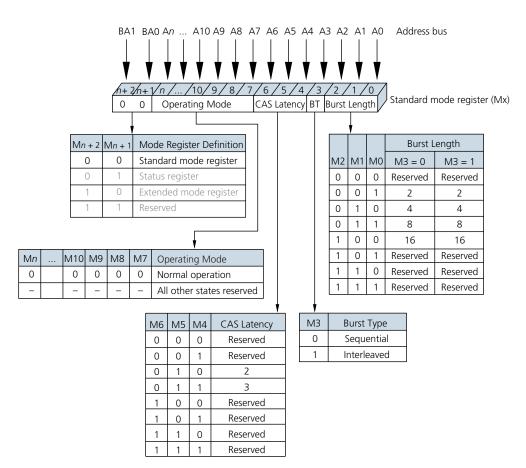

| Standard Mode Register                                 |      |

| Burst Length                                           |      |

| Burst Type                                             |      |

| CAS Latency                                            |      |

| Operating Mode                                         |      |

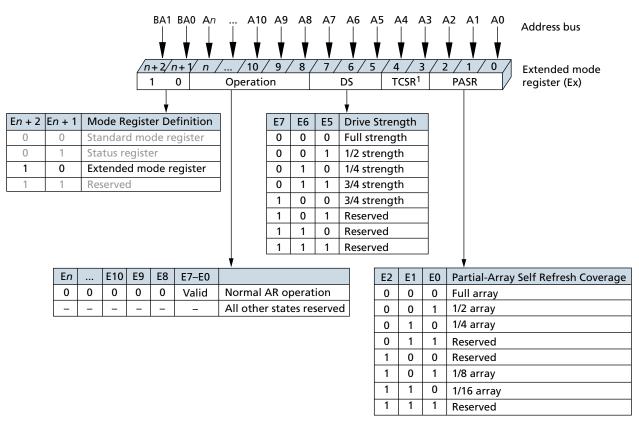

| Extended Mode Register                                 |      |

| Temperature-Compensated Self Refresh                   |      |

| Partial-Array Self Refresh                             | . 55 |

| Output Drive Strength                                  |      |

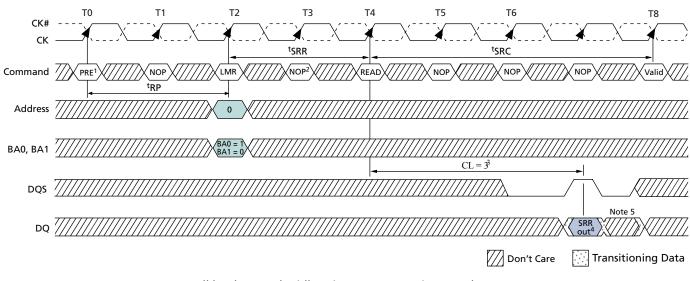

| Status Read Register                                   |      |

| Bank/Row Activation                                    |      |

|                                                        |      |

| READ Operation                                         |      |

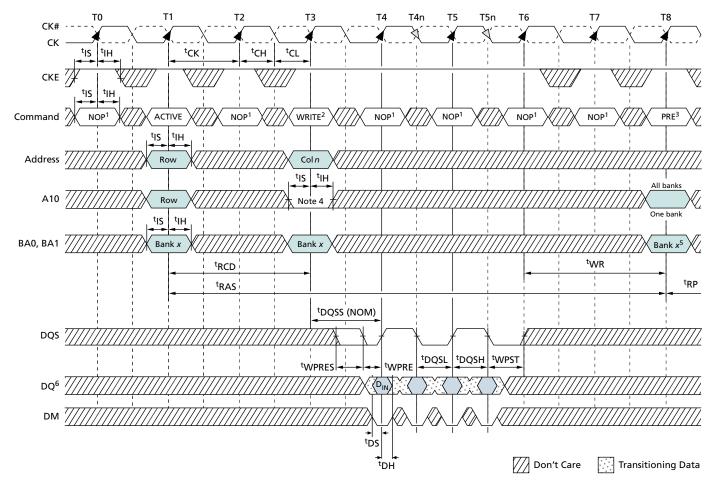

| WRITE Operation                                        |      |

| PRECHARGE Operation                                    |      |

| Auto Precharge                                         |      |

| Concurrent Auto Precharge                              |      |

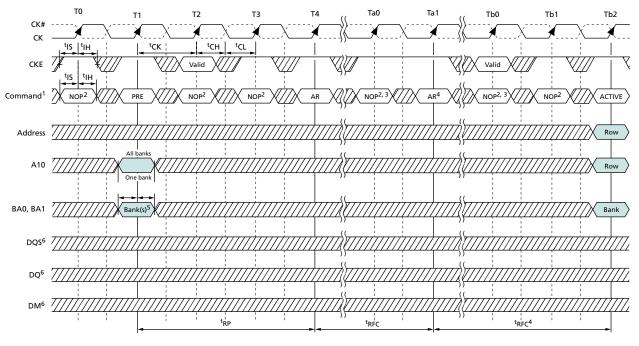

| AUTO REFRESH Operation                                 |      |

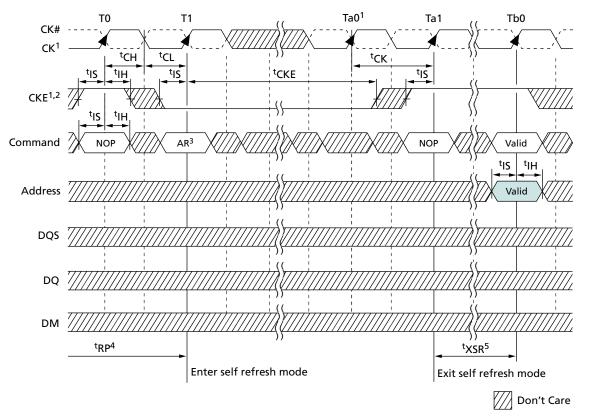

| SELF REFRESH Operation                                 |      |

| Power-Down                                             |      |

| Deep Power-Down                                        |      |

| Clock Change Frequency                                 |      |

| Revision History                                       |      |

| Rev. I, Production – 12/09                             |      |

| Rev. H, Production – 03/09                             |      |

| Rev. G, Production – 02/09                             |      |

| Rev. F, Production – 10/08                             | . 96 |

### 512Mb: x16, x32 Mobile LPDDR SDRAM

| Rev. E, Production – 8/08                                     |

|---------------------------------------------------------------|

| Nev. D, Production – 05/08                                    |

| Rev. C, Production – 03/08                                    |

| Nev. B, Preliminary – 12/07                                   |

| ev. A, Advance – 7/07                                         |

| evision History for Commands, Operations, and Timing Diagrams |

| Jpdate – 05/08                                                |

|                                                               |

|                                                               |

|                                                               |

| Jpdate – 07/07                                                |

# **List of Tables**

| Table 1:  | Key Timing Parameters (CL = 3)                                        | . 1 |

|-----------|-----------------------------------------------------------------------|-----|

| Table 2:  | Configuration Addressing 512                                          | . 2 |

| Table 3:  | VFBGA Ball Descriptions                                               | 13  |

| Table 4:  | Absolute Maximum Ratings                                              | 18  |

| Table 5:  | AC/DC Electrical Characteristics and Operating Conditions             | 18  |

| Table 6:  | 1.2V I/O AC/DC Electrical Characteristics and Operating Conditions    | 19  |

| Table 7:  | Capacitance (x16, x32)                                                | 20  |

| Table 8:  | I <sub>DD</sub> Specifications and Conditions (x16)                   | 22  |

| Table 9:  | I <sub>DD</sub> Specifications and Conditions (x32)                   | 23  |

| Table 10: | IDD6 Specifications and Conditions                                    | 24  |

| Table 11: | Electrical Characteristics and Recommended AC Operating Conditions    | 26  |

|           | Target Output Drive Characteristics (Full Strength)                   |     |

| Table 13: | Target Output Drive Characteristics (Three-Quarter Strength)          | 31  |

| Table 14: | 1.2V I/O Target Output Drive Characteristics (Three-Quarter Strength) | 32  |

| Table 15: | Target Output Drive Characteristics (One-Half Strength)               | 33  |

| Table 16: | : Truth Table – Commands                                              | 35  |

| Table 17: | DM Operation Truth Table                                              | 36  |

| Table 18: | Truth Table – Current State Bank <i>n</i> – Command to Bank <i>n</i>  | 42  |

| Table 19: | Truth Table – Current State Bank <i>n</i> – Command to Bank <i>m</i>  | 43  |

|           | Truth Table – CKE                                                     |     |

| Table 21: | Burst Definition Table                                                | 52  |

|           |                                                                       |     |

# **List of Figures**

|            | 512Mb Mobile LPDDR Part Numbering                                                    |    |

|------------|--------------------------------------------------------------------------------------|----|

|            | Functional Block Diagram (x16)                                                       |    |

|            | Functional Block Diagram (x32)                                                       |    |

| Figure 4:  | 60-Ball VFBGA – 8mm x 9mm (Top View)                                                 | 11 |

| Figure 5:  | 90-Ball VFBGA – 10mm x 13mm and 9mm x 13mm (Top View)                                | 12 |

| Figure 6:  | 60-Ball VFBGA (8mm x 9mm)                                                            | 15 |

| Figure 7:  | 90-Ball VFBGA (10mm x 13mm)                                                          | 16 |

| Figure 8:  | 90-Ball VFBGA (9mm x 13mm)                                                           | 17 |

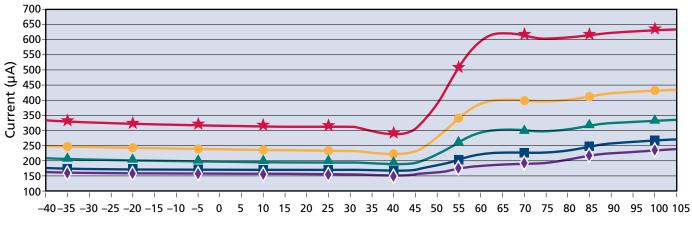

| Figure 9:  | Typical Self Refresh Current vs. Temperature                                         | 25 |

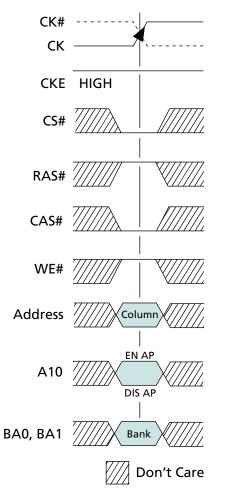

| Figure 10: | ACTIVE Command                                                                       | 37 |

| Figure 11: | READ Command                                                                         | 38 |

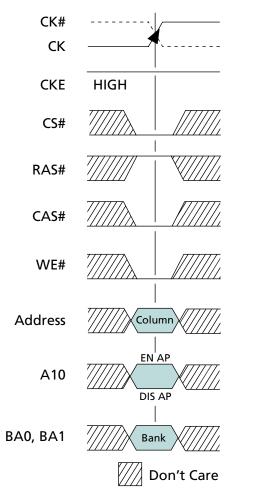

|            | WRITE Command                                                                        |    |

| Figure 13: | PRECHARGE Command                                                                    | 40 |

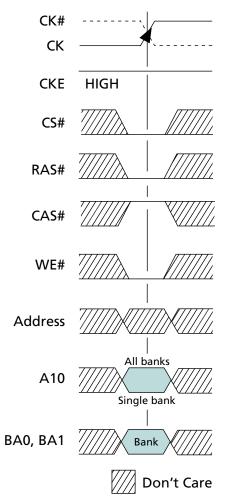

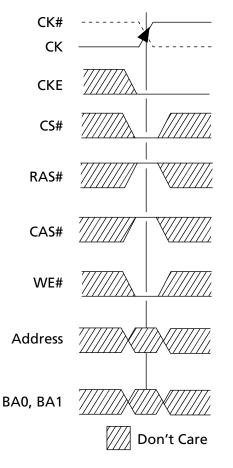

|            | DEEP POWER-DOWN Command                                                              |    |

| Figure 15: | Simplified State Diagram                                                             | 47 |

| Figure 16: | Initialize and Load Mode Registers                                                   | 49 |

| Figure 17: | Alternate Initialization with CKE LOW                                                | 50 |

| Figure 18: | Standard Mode Register Definition                                                    | 51 |

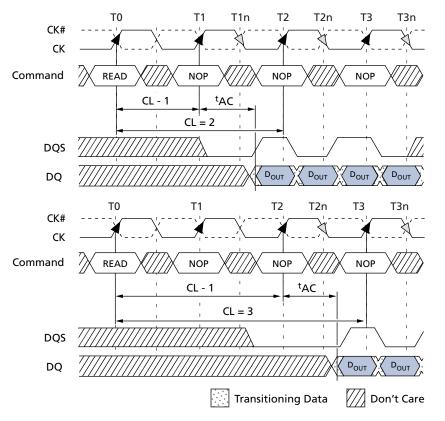

| Figure 19: | CAS Latency                                                                          | 54 |

| Figure 20: | Extended Mode Register                                                               | 55 |

| Figure 21: | Status Read Register Timing                                                          | 57 |

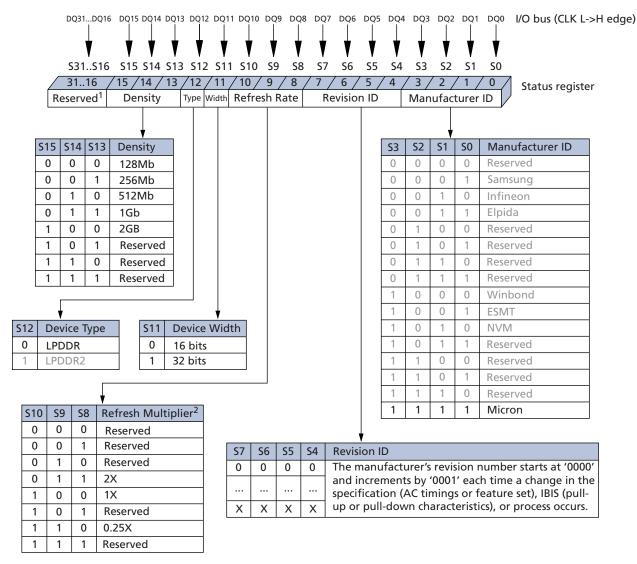

| Figure 22: | Status Register Definition                                                           | 58 |

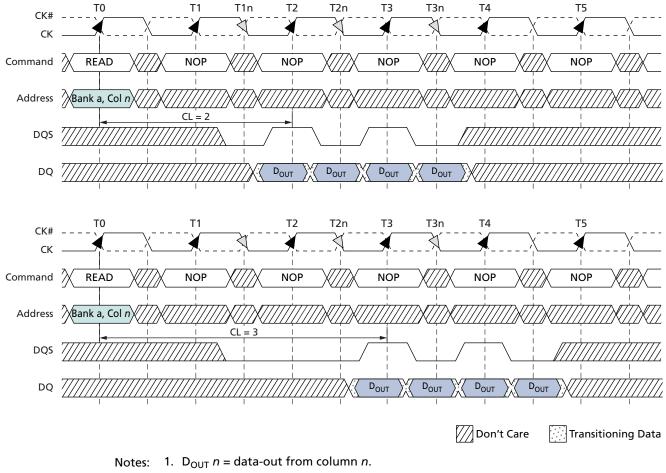

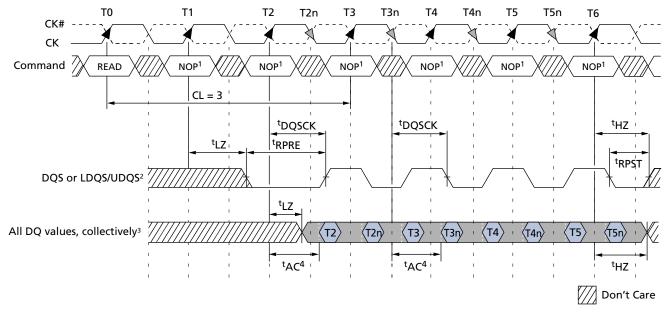

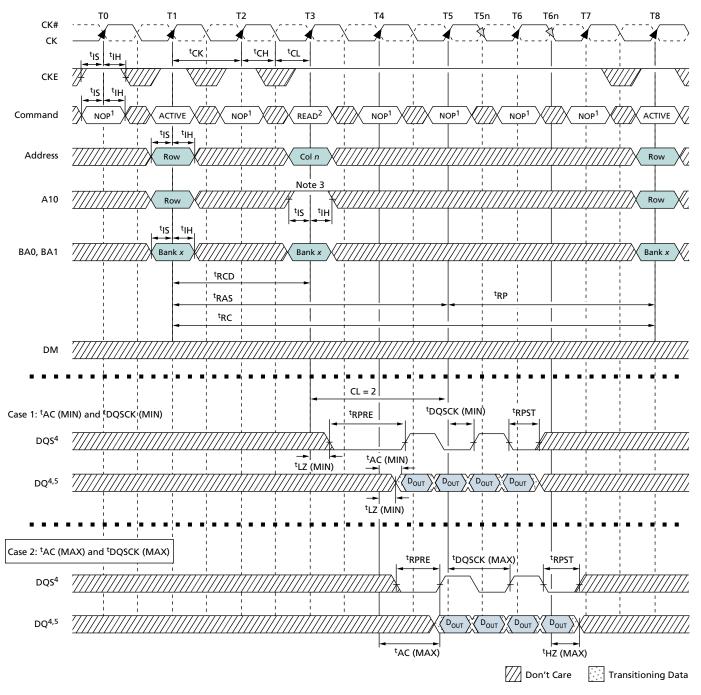

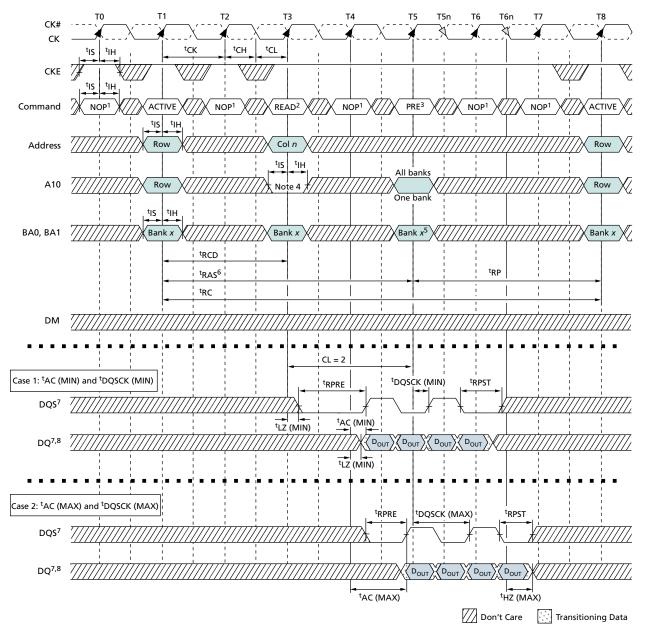

| Figure 23: | READ Burst                                                                           | 61 |

|            | Consecutive READ Bursts                                                              |    |

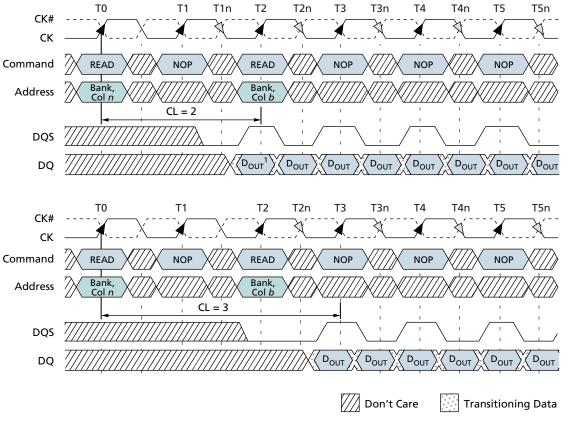

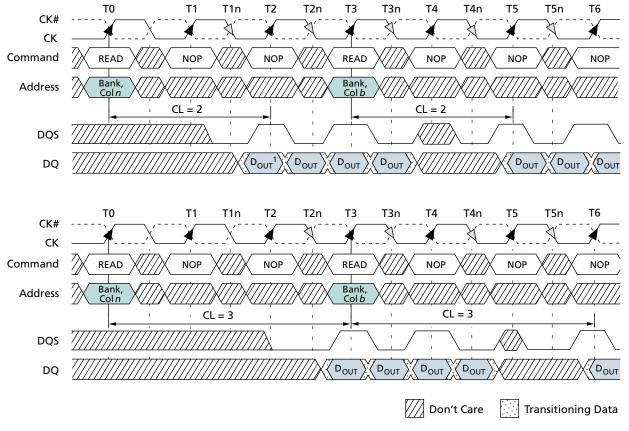

| Figure 25: | Nonconsecutive READ Bursts                                                           | 63 |

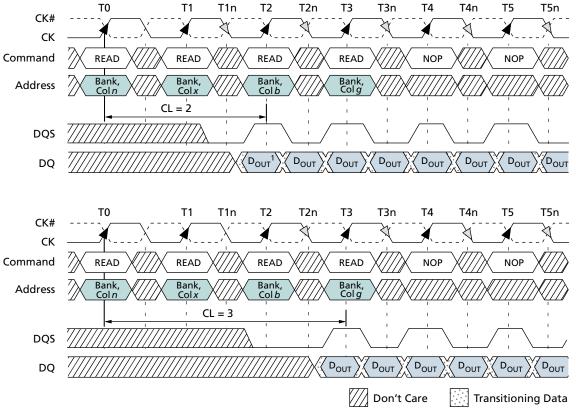

|            | Random Read Accesses                                                                 |    |

| Figure 27: | Terminating a READ Burst                                                             | 65 |

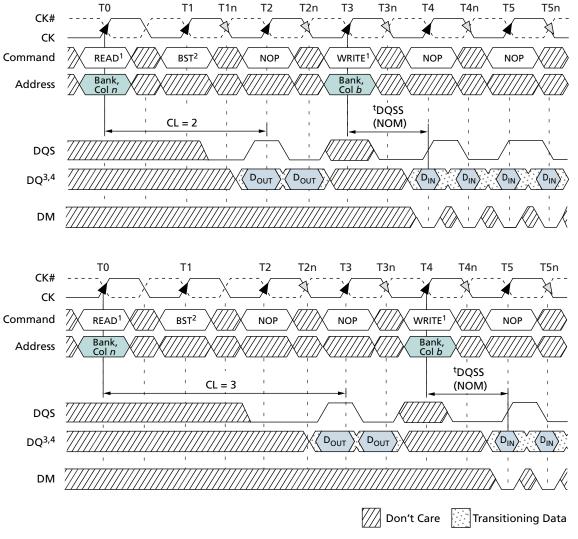

|            | READ-to-WRITE                                                                        |    |

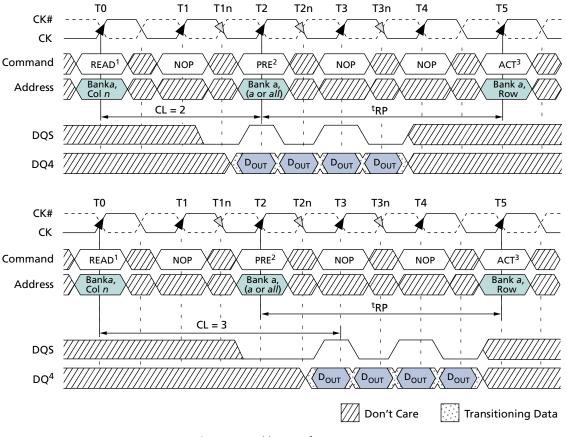

| Figure 29: | READ-to-PRECHARGE                                                                    | 67 |

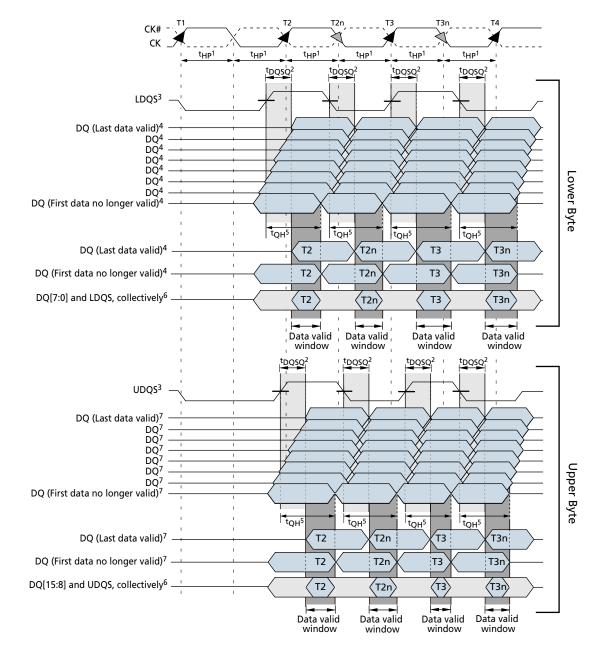

| Figure 30: | Data Output Timing – <sup>t</sup> DQSQ, <sup>t</sup> QH, and Data Valid Window (x16) | 68 |

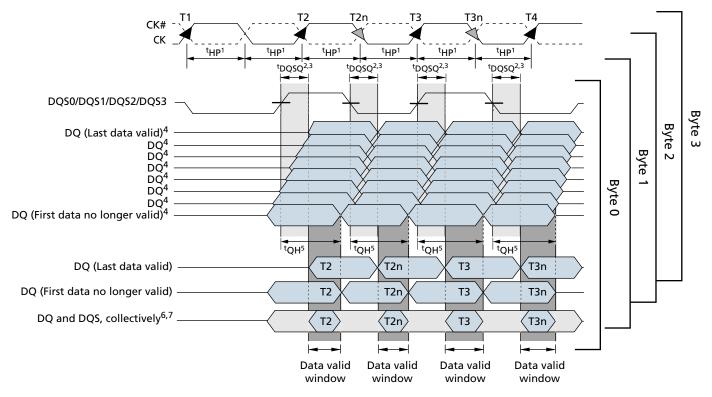

| Figure 31: | Data Output Timing – <sup>t</sup> DQSQ, <sup>t</sup> QH, and Data Valid Window (x32) | 69 |

| Figure 32: | Data Output Timing – <sup>t</sup> AC and <sup>t</sup> DQSCK                          | 70 |

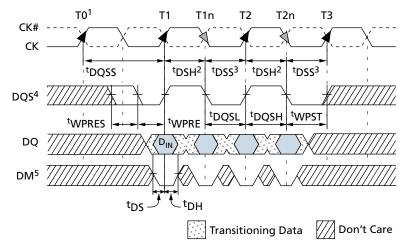

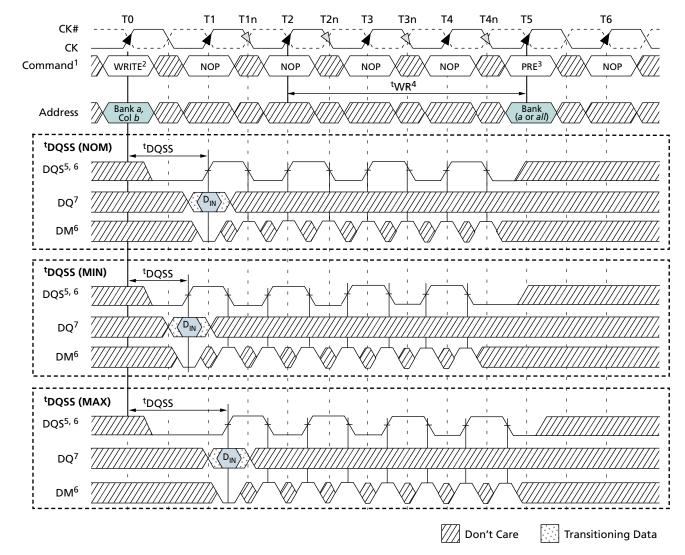

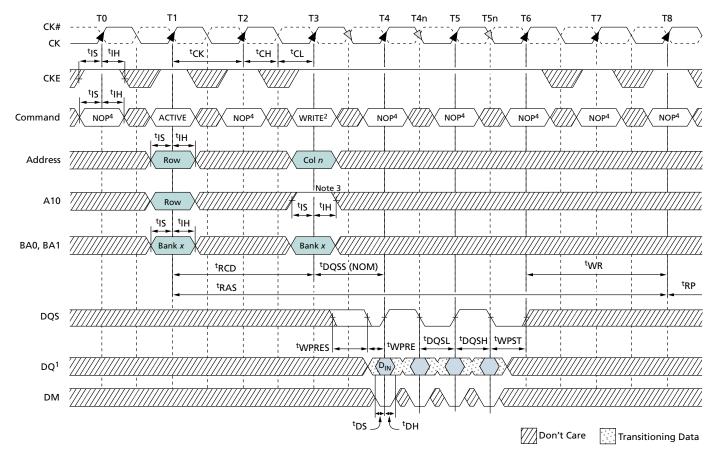

| Figure 33: | Data Input Timing                                                                    | 72 |

| Figure 34: | Write – DM Operation                                                                 | 73 |

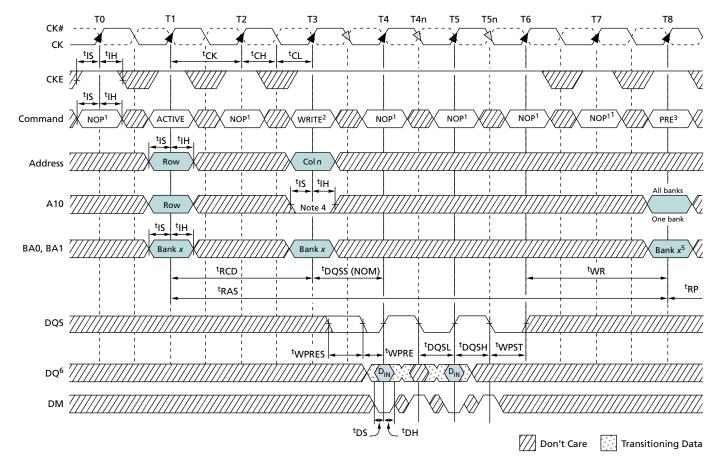

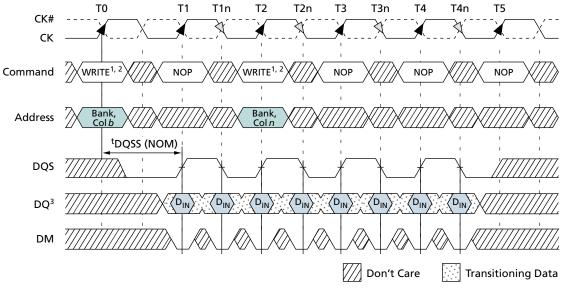

|            | WRITE Burst                                                                          |    |

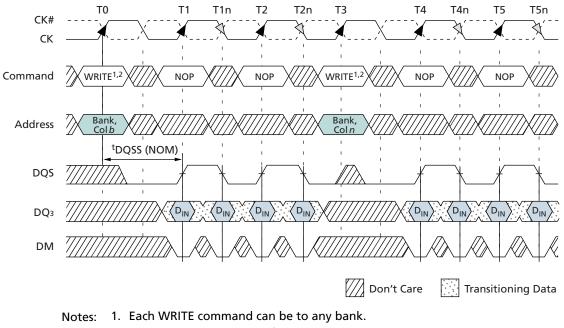

|            | Consecutive WRITE-to-WRITE                                                           |    |

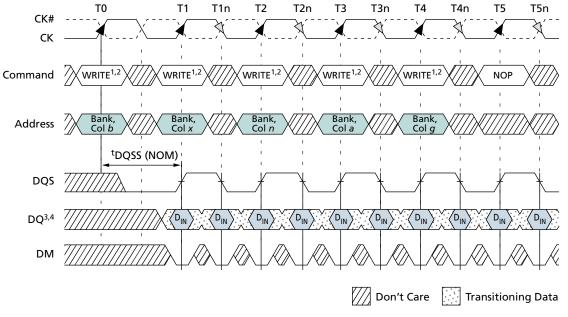

|            | Nonconsecutive WRITE-to-WRITE                                                        |    |

| Figure 38: | Random WRITE Cycles                                                                  | 76 |

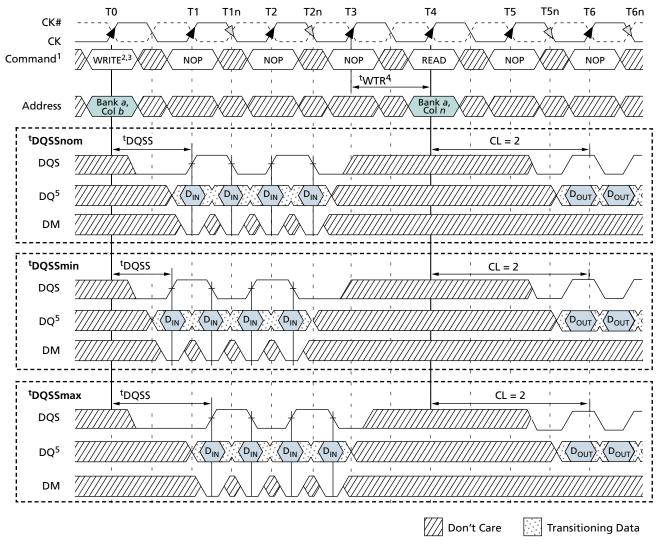

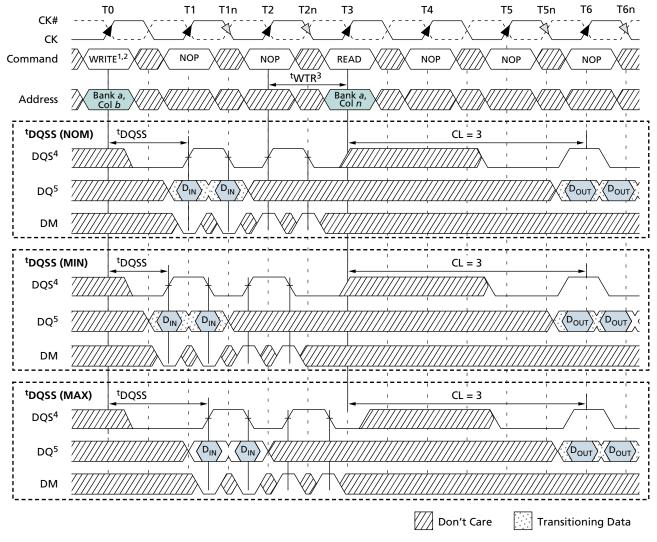

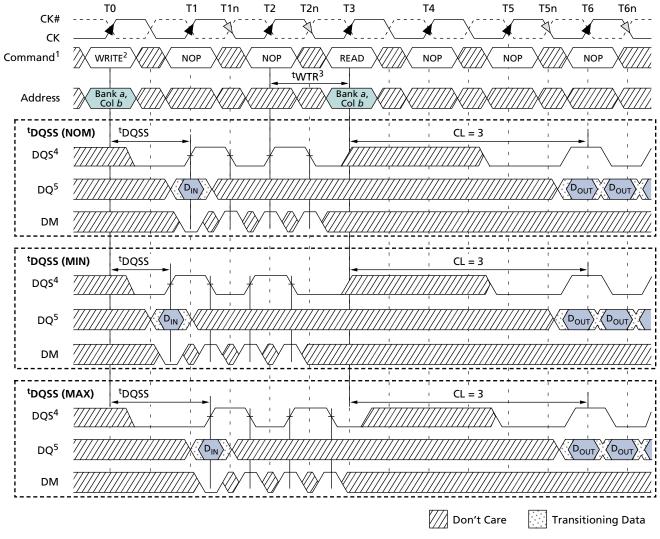

|            | WRITE-to-READ – Uninterrupting                                                       |    |

|            | WRITE-to-READ – Interrupting                                                         |    |

| Figure 41: | WRITE-to-READ – Odd Number of Data, Interrupting                                     | 79 |

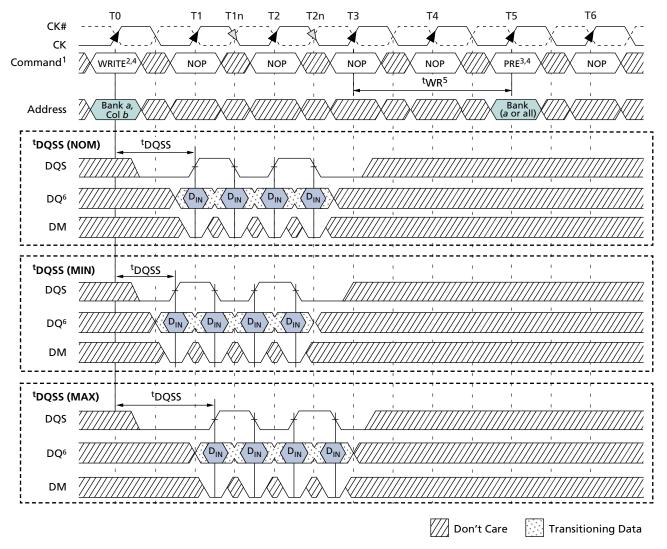

| Figure 42: | WRITE-to-PRECHARGE – Uninterrupting                                                  | 80 |

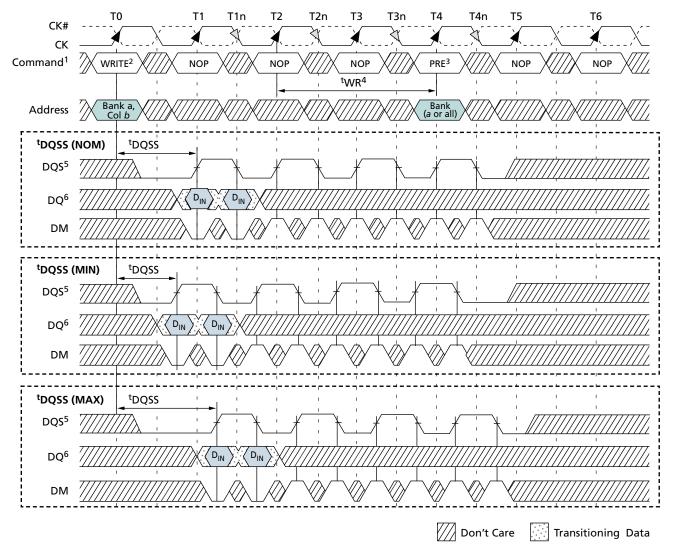

| Figure 43: | WRITE-to-PRECHARGE – Interrupting                                                    | 81 |

| Figure 44: | WRITE-to-PRECHARGE – Odd Number of Data, Interrupting                                | 82 |

|            | Bank Read – With Auto Precharge                                                      |    |

|            | Bank Read – Without Auto Precharge                                                   |    |

| Figure 47: | Bank Write – With Auto Precharge                                                     | 87 |

| Figure 48: | Bank Write – Without Auto Precharge                                                  | 88 |

|            | Auto Refresh Mode                                                                    |    |

| Figure 50: | Self Refresh Mode                                                                    | 91 |

### 512Mb: x16, x32 Mobile LPDDR SDRAM

| Figure 51: | Power-Down Entry (in Active or Precharge Mode) | 92 |

|------------|------------------------------------------------|----|

| Figure 52: | Power-Down Mode (Active or Precharge)          | 93 |

| Figure 53: | Deep Power-Down Mode                           | 94 |

| Figure 54: | Clock Stop Mode                                | 95 |

# **General Description**

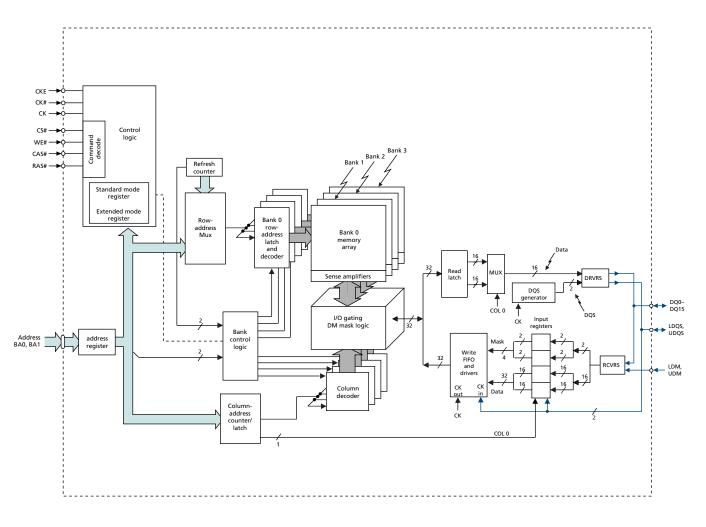

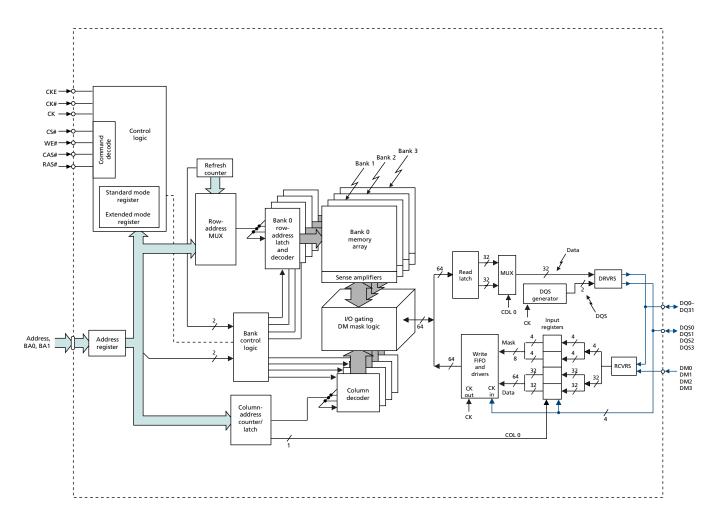

The 512Mb Mobile DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits. It is internally configured as a quad-bank DRAM. Each of the x16's 134,217,728-bit banks is organized as 8,192 rows by 1,024 columns by 16 bits. Each of the x32's 134,217,728-bit banks is organized as 8,192 rows by 512 columns by 32 bits. In the reduced page-size (LG) option, each of the x32's 134,217,728-bit banks are organized as 16,384 rows by 256 columns by 32 bits. **Note:**

1. Throughout this data sheet, various figures and text refer to DQs as "DQ." DQ should be interpreted as any and all DQ collectively, unless specifically stated otherwise. Additionally, the x16 is divided into 2 bytes: the lower byte and the upper byte. For the lower byte (DQ[7:0]), DM refers to LDM and DQS refers to LDQS. For the upper byte (DQ[15:8]), DM refers to UDM and DQS refers to UDQS. The x32 is divided into 4 bytes. For DQ[7:0], DM refers to DM0 and DQS refers to DQS0. For DQ[15:8], DM refers to DM1 and DQS refers to DQS1. For DQ[23:16], DM refers to DM2 and DQS refers to DQS2. For DQ[31:24], DM refers to DM3 and DQS refers to DQS3.

2. Complete functionality is described throughout the document; any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

3. Any specific requirement takes precedence over a general statement.

# **Functional Block Diagrams**

#### Figure 2: Functional Block Diagram (x16)

### 512Mb: x16, x32 Mobile LPDDR SDRAM Functional Block Diagrams

#### Figure 3: Functional Block Diagram (x32)

### **Ball Assignments and Descriptions**

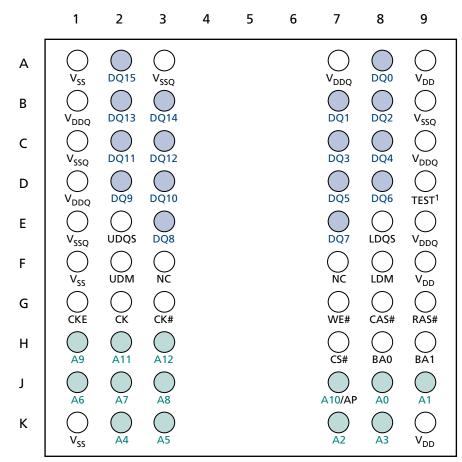

#### Figure 4: 60-Ball VFBGA – 8mm x 9mm (Top View)

Note: 1. D9 is a test pin that must be tied to  $V_{SS}$  or  $V_{SSQ}$  in normal operations.

|   |                  |             |                       |   | J ( | 100 |                             |             |                             |

|---|------------------|-------------|-----------------------|---|-----|-----|-----------------------------|-------------|-----------------------------|

|   | 1                | 2           | 3                     | 4 | 5   | 6   | 7                           | 8           | 9                           |

| A |                  | DQ31        | O<br>V <sub>SSQ</sub> |   |     |     | O<br>V <sub>DDQ</sub>       | DQ16        |                             |

| В |                  | DQ29        | <b>DQ30</b>           |   |     |     | DQ17                        | DQ18        | O<br>V <sub>SSQ</sub>       |

| С | V <sub>SSQ</sub> | DQ27        | DQ28                  |   |     |     | <b>DQ19</b>                 | <b>DQ20</b> | O<br>V <sub>DDQ</sub>       |

| D |                  | DQ25        | <b>DQ26</b>           |   |     |     | DQ21                        | DQ22        | TEST <sup>1</sup>           |

| E |                  | DQS3        | DQ24                  |   |     |     | DQ23                        | O<br>DQS2   | O<br>V <sub>DDQ</sub>       |

| F |                  | O<br>DM3    |                       |   |     |     | O<br>DNU/A13                | O<br>DM2    | $\bigcup_{V_{SS}}$          |

| G | CKE              | Ск          | O<br>CK#              |   |     |     | WE#                         | O<br>CAS#   | RAS#                        |

| Н | A9               | A11         | A12                   |   |     |     | O<br>CS#                    | O<br>BA0    | O<br>BA1                    |

| J | A6               | A7          | <b>A8</b>             |   |     |     | A10/AP                      | A0          | A1                          |

| К | A4               | O<br>DM1    | <b>A5</b>             |   |     |     | A2                          | O<br>DM0    | A3                          |

| L |                  | O<br>DQS1   | DQ8                   |   |     |     | DQ7                         | O<br>DQS0   | $\bigcirc$ V <sub>DDQ</sub> |

| М |                  | DQ9         | <b>DQ10</b>           |   |     |     | DQ5                         | DQ6         | ⊖<br>V <sub>ssQ</sub>       |

| Ν |                  | DQ11        | DQ12                  |   |     |     | DQ3                         | DQ4         | V <sub>DDQ</sub>            |

| Ρ |                  | <b>DQ13</b> | DQ14                  |   |     |     | DQ1                         | DQ2         | ⊖<br>V <sub>ssQ</sub>       |

| R |                  | DQ15        | $\bigcirc_{V_{SSQ}}$  |   |     |     | $\bigcirc$ V <sub>DDQ</sub> | DQ0         |                             |

|   | L                |             |                       |   |     |     |                             |             |                             |

#### Figure 5: 90-Ball VFBGA – 10mm x 13mm and 9mm x 13mm (Top View)

Note: 1. D9 is a test pin that must be tied to  $V_{SS}$  or  $V_{SSQ}$  in normal operations.

### **Table 3: VFBGA Ball Descriptions**

| Symbol                                        | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK#                                       | Input            | Clock: CK is the system clock input. CK and CK# are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and the negative edge of CK#. Input and output data is referenced to the crossing of CK and CK# (both directions of the crossing).                                                                                                                                                               |

| CKE                                           | Input            | Clock enable: CKE HIGH activates, and CKE LOW deactivates,<br>the internal clock signals, input buffers, and output drivers. Tak-<br>ing CKE LOW enables PRECHARGE power-down and SELF RE-<br>FRESH operations (all banks idle), or ACTIVE power-down (row<br>active in any bank). CKE is synchronous for all functions except<br>SELF REFRESH exit. All input buffers (except CKE) are disabled<br>during power-down and self refresh modes.                                |

| CS#                                           | Input            | Chip select: CS# enables (registered LOW) and disables (regis-<br>tered HIGH) the command decoder. All commands are masked<br>when CS# is registered HIGH. CS# provides for external bank se-<br>lection on systems with multiple banks. CS# is considered part<br>of the command code.                                                                                                                                                                                      |

| RAS#, CAS#,<br>WE#                            | Input            | Command inputs: RAS#, CAS#, and WE# (along with CS#) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                       |

| UDM, LDM<br>(60-ball)<br>DM[3:0]<br>(90-ball) | Input            | Input data mask: DM is an input mask signal for write data. In-<br>put data is masked when DM is sampled HIGH along with that<br>input data during a WRITE access. DM is sampled on both edges<br>of DQS. Although DM balls are input-only, the DM loading is<br>designed to match that of DQ and DQS balls.                                                                                                                                                                 |

| BA0, BA1                                      | Input            | Bank address inputs: BA0 and BA1 define to which bank an AC-<br>TIVE, READ, WRITE, or PRECHARGE command is being applied.<br>BA0 and BA1 also determine which mode register is loaded dur-<br>ing a LOAD MODE REGISTER command.                                                                                                                                                                                                                                              |

| A[12:0]<br>(60-ball)<br>A[12:0]<br>(90-ball)  | Input            | Address inputs: Provide the row address for ACTIVE commands,<br>and the column address and auto precharge bit (A10) for READ<br>or WRITE commands, to select one location out of the memory<br>array in the respective bank. During a PRECHARGE command,<br>A10 determines whether the PRECHARGE applies to one bank<br>(A10 LOW, bank selected by BA0, BA1) or all banks (A10 HIGH).<br>The address inputs also provide the op-code during a LOAD<br>MODE REGISTER command. |

| DQ[15:0]<br>(60-ball)                         | Input/<br>output | Data input/output: Data bus for x16 and x32.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DQ[31:0]<br>(90-ball)                         |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LDQS, UDQS<br>(60-ball)                       | Input/<br>output | Data strobe: Output with read data, input with write data. DQS is edge-aligned with read data, center-aligned in write data. It                                                                                                                                                                                                                                                                                                                                              |

| DQS[3:0]<br>(90-ball)                         |                  | is used to capture data.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### 512Mb: x16, x32 Mobile LPDDR SDRAM Ball Assignments and Descriptions

| Symbol           | Туре   | Description                                                                   |

|------------------|--------|-------------------------------------------------------------------------------|

| V <sub>DDQ</sub> | Supply | DQ power supply.                                                              |

| V <sub>SSQ</sub> | Supply | DQ ground.                                                                    |

| V <sub>DD</sub>  | Supply | Power supply.                                                                 |

| V <sub>SS</sub>  | Supply | Ground.                                                                       |

| NC               | _      | No connect: May be left unconnected.                                          |

| DNU/A13          | Input  | Do not use. A13 if reduced page-size option is selected; other-<br>wise, DNU. |

| TEST             | Input  | Test pin: Must be tied to $V_{SS}$ or $V_{SSQ}$ in normal operations.         |

#### Table 3: VFBGA Ball Descriptions (Continued)

# **Package Dimensions**

#### Figure 6: 60-Ball VFBGA (8mm x 9mm)

Note: 1. All dimensions are in millimeters.

#### Figure 7: 90-Ball VFBGA (10mm x 13mm)

Note: 1. All dimensions are in millimeters.

PDF: 09005aef82d5d305 512mb\_ddr\_mobile\_sdram\_t47m.pdf - Rev. I 12/09 EN

#### Figure 8: 90-Ball VFBGA (9mm x 13mm)

Note: 1. All dimensions are in millimeters.

# **Electrical Specifications**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Table 4: Absolute Maximum Ratings**

Note 1 applies to all parameters in this table

| Parameter                                            | Symbol           | Min  | Мах                                                    | Unit |

|------------------------------------------------------|------------------|------|--------------------------------------------------------|------|

| $V_{DD}/V_{DDQ}$ supply voltage relative to $V_{SS}$ | $V_{DD}/V_{DDQ}$ | -1.0 | 2.4                                                    | V    |

| Voltage on any pin relative to $V_{SS}$              | V <sub>IN</sub>  | -0.5 | 2.4 or (V <sub>DDQ</sub> + 0.3V),<br>whichever is less | V    |

| Storage temperature (plastic)                        | T <sub>STG</sub> | -55  | +150                                                   | °C   |

Note: 1.  $V_{DD}$  and  $V_{DDQ}$  must be within 300mV of each other at all times.  $V_{DDQ}$  must not exceed  $V_{DD}$ .

#### Table 5: AC/DC Electrical Characteristics and Operating Conditions

| Parameter/Condition                                        | Symbol              | Min                  | Max                    | Unit | Notes    |

|------------------------------------------------------------|---------------------|----------------------|------------------------|------|----------|

| Supply voltage                                             | V <sub>DD</sub>     | 1.70                 | 1.95                   | V    | 6, 7     |

| I/O supply voltage                                         | V <sub>DDQ</sub>    | 1.70                 | 1.95                   | V    | 6, 7     |

| Address and command inputs                                 |                     |                      |                        |      |          |

| Input voltage high                                         | V <sub>IH</sub>     | $0.8 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.3 | V    | 8, 9     |

| Input voltage low                                          | V <sub>IL</sub>     | -0.3                 | $0.2 \times V_{DDQ}$   | V    | 8, 9     |

| Clock inputs (CK, CK#)                                     |                     |                      |                        |      |          |

| DC input voltage                                           | V <sub>IN</sub>     | -0.3                 | V <sub>DDQ</sub> + 0.3 | V    | 10       |

| DC input differential voltage                              | V <sub>ID(DC)</sub> | $0.4 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.6 | V    | 10, 11   |

| AC input differential voltage                              | V <sub>ID(AC)</sub> | $0.6 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.6 | V    | 10, 11   |

| AC differential crossing voltage                           | V <sub>IX</sub>     | $0.4 \times V_{DDQ}$ | $0.6 \times V_{DDQ}$   | V    | 10, 12   |

| Data inputs                                                |                     |                      |                        |      |          |

| DC input high voltage                                      | V <sub>IH(DC)</sub> | $0.7 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.3 | V    | 8, 9, 13 |

| DC input low voltage                                       | V <sub>IL(DC)</sub> | -0.3                 | $0.3 \times V_{DDQ}$   | V    | 8, 9, 13 |

| AC input high voltage                                      | V <sub>IH(AC)</sub> | $0.8 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.3 | V    | 8, 9, 13 |

| AC input low voltage                                       | V <sub>IL(AC)</sub> | -0.3                 | $0.2 \times V_{DDQ}$   | V    | 8, 9, 13 |

| Data outputs                                               |                     |                      |                        |      |          |

| DC output high voltage: Logic 1 (I <sub>OH</sub> = –0.1mA) | V <sub>OH</sub>     | $0.9 \times V_{DDQ}$ | _                      | V    |          |

| DC output low voltage: Logic 0 (I <sub>OL</sub> = 0.1mA)   | V <sub>OL</sub>     | _                    | $0.1 \times V_{DDQ}$   | V    |          |

| Leakage current                                            |                     |                      |                        |      |          |

| Input leakage current                                      | I <sub>I</sub>      | -1                   | 1                      | μA   |          |

| Any input $0V \le V_{IN} \le V_{DD}$                       |                     |                      |                        |      |          |

| (All other pins not under test = 0V)                       |                     |                      |                        |      |          |

Notes 1–5 apply to all parameters/conditions in this table;  $V_{DD}/V_{DDO} = 1.70-1.95V$

#### Table 5: AC/DC Electrical Characteristics and Operating Conditions (Continued)

Notes 1–5 apply to all parameters/conditions in this table; V<sub>DD</sub>/V<sub>DDO</sub> = 1.70–1.95V

| Parameter/Condition                                                                    | Symbol          | Min | Мах | Unit | Notes |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------|-----|-----|------|-------|--|--|--|--|--|--|

| Output leakage current<br>(DQ are disabled; 0V ≤ V <sub>OUT</sub> ≤ V <sub>DDQ</sub> ) | I <sub>OZ</sub> | -5  | 5   | μA   |       |  |  |  |  |  |  |

| Operating temperature                                                                  |                 |     |     |      |       |  |  |  |  |  |  |

| Commercial                                                                             | T <sub>A</sub>  | 0   | +70 | °C   |       |  |  |  |  |  |  |

| Industrial                                                                             | T <sub>A</sub>  | -40 | +85 | °C   |       |  |  |  |  |  |  |

#### Table 6: 1.2V I/O AC/DC Electrical Characteristics and Operating Conditions

Notes 1–5 apply to all parameters/conditions in this table;  $V_{DD}/V_{DDQ} = 1.70-1.95V$

| Parameter/Condition                                        | Symbol              | Min                  | Мах                    | Unit | Notes    |

|------------------------------------------------------------|---------------------|----------------------|------------------------|------|----------|

| Supply voltage                                             | V <sub>DD</sub>     | 1.70                 | 1.95                   | V    | 6, 7     |

| I/O supply voltage                                         | V <sub>DDQ</sub>    | 1.14                 | 1.30                   | V    | 6, 7     |

| Address and command inputs                                 |                     |                      |                        |      | ·        |

| Input voltage high                                         | V <sub>IH</sub>     | $0.9 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.2 | V    | 8, 9     |

| Input voltage low                                          | V <sub>IL</sub>     | -0.2                 | $0.1 \times V_{DDQ}$   | V    | 8, 9     |

| Clock inputs (CK, CK#)                                     |                     |                      |                        |      | ·        |

| DC input voltage                                           | V <sub>IN</sub>     | -0.2                 | V <sub>DDQ</sub> + 0.2 | V    | 10       |

| DC input differential voltage                              | V <sub>ID(DC)</sub> | $0.4 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.4 | V    | 10, 11   |

| AC input differential voltage                              | V <sub>ID(AC)</sub> | $0.6 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.4 | V    | 10, 11   |

| AC differential crossing voltage                           | V <sub>IX</sub>     | $0.4 \times V_{DDQ}$ | $0.6 \times V_{DDQ}$   | V    | 10, 12   |

| Data inputs                                                |                     |                      |                        |      | ·        |

| DC input high voltage                                      | V <sub>IH(DC)</sub> | $0.8 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.2 | V    | 8, 9, 13 |

| DC input low voltage                                       | V <sub>IL(DC)</sub> | -0.2                 | $0.2 \times V_{DDQ}$   | V    | 8, 9, 13 |

| AC input high voltage                                      | V <sub>IH(AC)</sub> | $0.9 \times V_{DDQ}$ | V <sub>DDQ</sub> + 0.2 | V    | 8, 9, 13 |

| AC input low voltage                                       | V <sub>IL(AC)</sub> | -0.2                 | $0.1 \times V_{DDQ}$   | V    | 8, 9, 13 |

| Data outputs                                               |                     |                      |                        |      | ·        |

| DC output high voltage: Logic 1 (I <sub>OH</sub> = -0.1mA) | V <sub>OH</sub>     | $0.9 \times V_{DDQ}$ | -                      | V    |          |

| DC output low voltage: Logic 0 (I <sub>OL</sub> = 0.1mA)   | V <sub>OL</sub>     | _                    | $0.1 \times V_{DDQ}$   | V    |          |

| Leakage current                                            |                     |                      |                        |      | ·        |

| Input leakage current                                      | I <sub>I</sub>      | -1                   | 1                      | μA   |          |

| Any input $0V \le V_{IN} \le V_{DD}$                       |                     |                      |                        |      |          |

| (All other pins not under test = 0V)                       |                     |                      |                        |      |          |

| Output leakage current                                     | I <sub>OZ</sub>     | -5                   | 5                      | μA   |          |

| (DQ are disabled; $0V \le V_{OUT} \le V_{DDQ}$ )           |                     |                      |                        |      |          |

| Operating temperature                                      | -                   |                      |                        | 0-   | 1        |

| Commercial                                                 |                     | 0                    | +70                    | °C   |          |

| Industrial                                                 | T <sub>A</sub>      | -40                  | +85                    | °C   |          |

Notes: 1. All voltages referenced to V<sub>SS</sub>.

2. All parameters assume proper device initialization.

#### 512Mb: x16, x32 Mobile LPDDR SDRAM Electrical Specifications

- Tests for AC timing, I<sub>DD</sub>, and electrical AC and DC characteristics may be conducted at nominal supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- 4. Outputs measured with equivalent load; transmission line delay is assumed to be very

- 5. Timing and  $I_{DD}$  tests may use a  $V_{IL}$ -to- $V_{IH}$  swing of up to 1.5V in the test environment, but input timing is still referenced to  $V_{DDQ}/2$  (or to the crossing point for CK/CK#). The output timing reference voltage level is  $V_{DDQ}/2$ .

- Any positive glitch must be less than one-third of the clock cycle and not more than +200mV or 2.0V, whichever is less. Any negative glitch must be less than one-third of the clock cycle and not exceed either –150mV or +1.6V, whichever is more positive.

- 7.  $V_{DD}$  and  $V_{DDQ}$  must track each other and  $V_{DDQ}$  must be less than or equal to  $V_{DD}$ .

- 8. To maintain a valid level, the transitioning edge of the input must:

8a. Sustain a constant slew rate from the current AC level through to the target AC level,  $V_{IL(AC)}$  Or  $V_{IH(AC)}.$

8b. Reach at least the target AC level.

8c. After the AC target level is reached, continue to maintain at least the target DC level,  $V_{IL(DC)}$  or  $V_{IH(DC)}.$

- 9.  $V_{IH}$  overshoot:  $V_{IH(MAX)} = V_{DDQ} + 1.0V$  for a pulse width  $\leq$ 3ns and the pulse width cannot be greater than one-third of the cycle rate.  $V_{IL}$  undershoot:  $V_{IL(MIN)} = -1.0V$  for a pulse width  $\leq$ 3ns and the pulse width cannot be greater than one-third of the cycle rate.

- 10. CK and CK# input slew rate must be ≥1 V/ns (2 V/ns if measured differentially).

- 11.  $V_{ID}$  is the magnitude of the difference between the input level on CK and the input level on CK#.

- 12. The value of  $V_{IX}$  is expected to equal  $V_{DDQ}/2$  of the transmitting device and must track variations in the DC level of the same.

- DQ and DM input slew rates must not deviate from DQS by more than 10%. 50ps must be added to <sup>t</sup>DS and <sup>t</sup>DH for each 100 mV/ns reduction in slew rate. If slew rate exceeds 4 V/ns, functionality is uncertain.

#### Table 7: Capacitance (x16, x32)

Note 1 applies to all the parameters in this table

| Parameter                                    | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input capacitance: CK, CK#                   | С <sub>СК</sub>  | 2.0 | 4.0 | pF   |       |

| Delta input capacitance: CK, CK#             | C <sub>DCK</sub> | _   | 0.5 | pF   | 2     |

| Input capacitance: command and address       | CI               | 2.0 | 4.0 | pF   |       |

| Delta input capacitance: command and address | C <sub>DI</sub>  | -   | 1.0 | pF   | 2     |

| Input/output capacitance: DQ, DQS, DM        | C <sub>IO</sub>  | 2.0 | 4.5 | pF   |       |

| Delta input/output capacitance: DQ, DQS, DM  | C <sub>DIO</sub> | -   | 1.0 | pF   | 3     |

- Notes: 1. This parameter is sampled.  $V_{DD}/V_{DDQ} = 1.70-1.95V$ , f = 100 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT(DC)} = V_{DDQ}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2V. DM input is grouped with I/O pins, reflecting the fact that they are matched in loading.

- 2. The input capacitance per pin group will not differ by more than this maximum amount for any given device.

### 512Mb: x16, x32 Mobile LPDDR SDRAM Electrical Specifications

3. The I/O capacitance per DQS and DQ byte/group will not differ by more than this maximum amount for any given device.

# **Electrical Specifications – IDD Parameters**

#### Table 8: I<sub>DD</sub> Specifications and Conditions (x16)

Notes 1–5 apply to all parameters/conditions in this table;  $V_{DD}/V_{DDQ} = 1.70-1.95V$

|                                                                                                                                                                                          |                                      |                    |     | М   | ах  |     |      |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------|-----|-----|-----|-----|------|--------|

| Parameter/Condition                                                                                                                                                                      |                                      | Symbol             | -5  | -54 | -6  | -75 | Unit | Notes  |

| Operating 1 bank active precharge current: <sup>t</sup> RC = <sup>t</sup> CK (MIN); CKE is HIGH; CS is HIGH between valid dress inputs are switching every 2 clock cycles; Da are stable | commands; Ad-                        | I <sub>DD0</sub>   | 70  | 65  | 60  | 50  | mA   | 6      |

| Precharge power-down standby current: All bank<br>LOW; CS is HIGH, <sup>t</sup> CK = <sup>t</sup> CK (MIN); Address and co<br>switching; Data bus inputs are stable                      |                                      | I <sub>DD2P</sub>  | 300 | 300 | 300 | 300 | μA   | 7, 8   |

| Precharge power-down standby current: Clock sto<br>idle; CKE is LOW; CS is HIGH; CK = LOW, CK# = HIG<br>control inputs are switching; Data bus inputs are s                              | GH; Address and                      | I <sub>DD2PS</sub> | 300 | 300 | 300 | 300 | μA   | 7      |

| Precharge nonpower-down standby current: All b<br>HIGH; CS = HIGH; <sup>t</sup> CK = <sup>t</sup> CK (MIN); Address and co<br>switching; Data bus inputs are stable                      |                                      | I <sub>DD2N</sub>  | 15  | 15  | 15  | 12  | mA   | 9      |

| Precharge nonpower-down standby current: Cloc<br>banks idle, CKE = HIGH; CS = HIGH; CK = LOW, CK<br>dress and control inputs are switching; Data bus i                                   | # = HIGH; Ad-                        | I <sub>DD2NS</sub> | 8   | 8   | 8   | 8   | mA   | 9      |

| Active power-down standby current: 1 bank activ<br>CS = HIGH; <sup>t</sup> CK = <sup>t</sup> CK (MIN); Address and control ir<br>ing; Data bus inputs are stable                         |                                      | I <sub>DD3P</sub>  | 3   | 3   | 3   | 3   | mA   | 8      |

| Active power-down standby current: Clock stoppe<br>tive, CKE = LOW; CS = HIGH; CK = LOW; CK# = HIC<br>control inputs are switching; Data bus inputs are s                                | GH; Address and                      | I <sub>DD3PS</sub> | 2   | 2   | 2   | 2   | mA   |        |

| Active nonpower-down standby: 1 bank active, C<br>HIGH; <sup>t</sup> CK = <sup>t</sup> CK (MIN); Address and control inputs<br>Data bus inputs are stable                                |                                      | I <sub>DD3N</sub>  | 15  | 15  | 15  | 15  | mA   | 6      |

| Active nonpower-down standby: Clock stopped; 1<br>CKE = HIGH; CS = HIGH; CK = LOW; CK# = HIGH; A<br>trol inputs are switching; Data bus inputs are stab                                  | Address and con-                     | I <sub>DD3NS</sub> | 8   | 8   | 8   | 8   | mA   | 6      |

| Operating burst read: 1 bank active; BL = 4; <sup>t</sup> CK =<br>tinuous READ bursts; I <sub>OUT</sub> = 0mA; Address inputs a<br>every 2 clock cycles; 50% data changing each burs     | are switching                        | I <sub>DD4R</sub>  | 115 | 110 | 105 | 90  | mA   | 6      |

| Operating burst write: 1 bank active; BL = 4; <sup>t</sup> CK =<br>tinuous WRITE bursts; Address inputs are switchin<br>changing each burst                                              |                                      | I <sub>DD4W</sub>  | 115 | 110 | 105 | 90  | mA   | 6      |

|                                                                                                                                                                                          | <sup>t</sup> RFC = 110ns             | I <sub>DD5</sub>   | 105 | 105 | 100 | 100 | mA   | 10     |

| dress and control inputs are switching; Data bus inputs are stable                                                                                                                       | <sup>t</sup> RFC = <sup>t</sup> REFI | I <sub>DD5A</sub>  | 3   | 3   | 3   | 3   | mA   | 10, 11 |

| Deep power-down current: Address and control b<br>Data bus inputs are stable                                                                                                             | oalls are stable;                    | I <sub>DD8</sub>   |     | 1   | 0   |     | μA   | 7, 13  |

### 512Mb: x16, x32 Mobile LPDDR SDRAM Electrical Specifications – I<sub>DD</sub> Parameters

### Table 9: I<sub>DD</sub> Specifications and Conditions (x32)

Notes 1–5 apply to all parameters/conditions in this table;  $V_{DD}/V_{DDQ} = 1.70-1.95V$

|                                                                                                                                                                                                                                                                    |                    |     | М   | ах  |     |      |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|-----|------|--------|

| Parameter/Condition                                                                                                                                                                                                                                                | Symbol             | -5  | -54 | -6  | -75 | Unit | Notes  |

| Operating 1 bank active precharge current: <sup>t</sup> RC = <sup>t</sup> RC (MIN); <sup>t</sup> CK = <sup>t</sup> CK (MIN); CKE is HIGH; CS is HIGH between valid commands; Ad-<br>dress inputs are switching every 2 clock cycles; Data bus inputs<br>are stable | I <sub>DD0</sub>   | 70  | 65  | 60  | 50  | mA   | 6      |

| Precharge power-down standby current: All banks idle; CKE is LOW; CS is HIGH; ${}^{t}CK = {}^{t}CK$ (MIN); Address and control inputs are switching; Data bus inputs are stable                                                                                    | I <sub>DD2P</sub>  | 300 | 300 | 300 | 300 | μA   | 7, 8   |

| Precharge power-down standby current: Clock stopped; All banks<br>idle; CKE is LOW; CS is HIGH, CK = LOW, CK# = HIGH; Address and<br>control inputs are switching; Data bus inputs are stable                                                                      |                    | 300 | 300 | 300 | 300 | μA   | 7      |

| Precharge nonpower-down standby current: All banks idle CKE = HIGH; CS = HIGH; <sup>t</sup> CK = <sup>t</sup> CK (MIN); Address and control inputs are switching; Data bus inputs are stable                                                                       | I <sub>DD2N</sub>  | 15  | 15  | 15  | 12  | mA   | 9      |

| Precharge nonpower-down standby current: Clock stopped; All<br>banks idle, CKE = HIGH; CS = HIGH; CK = LOW, CK# = HIGH; Ad-<br>dress and control inputs are switching; Data bus inputs are stable                                                                  | I <sub>DD2NS</sub> | 8   | 8   | 8   | 8   | mA   | 9      |

| Active power-down standby current: 1 bank active, CKE = LOW;<br>CS = HIGH; <sup>t</sup> CK = <sup>t</sup> CK (MIN); Address and control inputs are switch-<br>ing; Data bus inputs are stable                                                                      | I <sub>DD3P</sub>  | 3   | 3   | 3   | 3   | mA   | 8      |

| Active power-down standby current: Clock stopped; 1 bank ac-<br>tive, CKE = LOW; CS = HIGH; CK = LOW; CK# = HIGH; Address and<br>control inputs are switching; Data bus inputs are stable                                                                          | I <sub>DD3PS</sub> | 2   | 2   | 2   | 2   | mA   |        |

| Active nonpower-down standby: 1 bank active; $CKE = HIGH$ ; $CS = HIGH$ ; $^{t}CK = ^{t}CK$ (MIN); Address and control inputs are switching; Data bus inputs are stable                                                                                            | I <sub>DD3N</sub>  | 15  | 15  | 15  | 15  | mA   | 6      |

| Active nonpower-down standby: Clock stopped; 1 bank active,<br>CKE = HIGH; CS = HIGH; CK = LOW; CK# = HIGH; Address and con-<br>trol inputs are switching; Data bus inputs are stable                                                                              | I <sub>DD3NS</sub> | 8   | 8   | 8   | 8   | mA   | 6      |

| Operating burst read: 1 bank active; $BL = 4$ ; $CL = 3$ ; ${}^{t}CK = {}^{t}CK$ (MIN); Continuous READ bursts; $I_{OUT} = 0$ mA; Address inputs are switching every 2 clock cycles; 50% data changing each burst                                                  | I <sub>DD4R</sub>  | 125 | 120 | 115 | 100 | mA   | 6      |

| Operating burst write: One bank active; BL = 4; <sup>t</sup> CK = <sup>t</sup> CK (MIN);<br>Continuous WRITE bursts; Address inputs are switching; 50% da-<br>ta changing each burst                                                                               | I <sub>DD4W</sub>  | 125 | 120 | 115 | 100 | mA   | 6      |

| Auto refresh: Burst refresh; CKE = HIGH; Ad-                                                                                                                                                                                                                       | I <sub>DD5</sub>   | 105 | 105 | 100 | 100 | mA   | 10     |

| dress and control inputs are switching; Data bus TRFC = TREFI inputs are stable                                                                                                                                                                                    | I <sub>DD5A</sub>  | 3   | 3   | 3   | 3   | mA   | 10, 11 |

| Deep power-down current: Address and control pins are stable;<br>Data bus inputs are stable                                                                                                                                                                        | I <sub>DD8</sub>   |     | 1   | 0   |     | μA   | 7, 13  |

#### Table 10: I<sub>DD6</sub> Specifications and Conditions

Notes 1–5, 7, and 12 apply to all parameters/conditions in this table;  $V_{DD}/V_{DDO} = 1.70-1.95V$

| Parameter/Condition                                         |                  | Symbol           | Low Power | Standard | Units |

|-------------------------------------------------------------|------------------|------------------|-----------|----------|-------|

| Self refresh                                                | Full array, 85°C | I <sub>DD6</sub> | 500       | 700      | μA    |

| CKE = LOW; ${}^{t}CK = {}^{t}CK$ (MIN); Address and control | Full array, 45°C |                  | 250       | 390      | μA    |

| inputs are stable; Data bus inputs are stable               | 1/2 array, 85°C  |                  | 400       | 520      | μA    |

|                                                             | 1/2 array, 45°C  |                  | 220       | 310      | μA    |

|                                                             | 1/4 array, 85°C  |                  | 350       | 430      | μA    |

|                                                             | 1/4 array, 45°C  |                  | 205       | 275      | μA    |

|                                                             | 1/8 array, 85°C  |                  | 350       | 430      | μA    |

|                                                             | 1/8 array, 45°C  | •                | 205       | 275      | μA    |

|                                                             | 1/16 array, 85°C |                  | 325       | 375      | μA    |

|                                                             | 1/16 array, 45°C |                  | 200       | 250      | μA    |

- Notes: 1. All voltages referenced to V<sub>SS</sub>.

- Tests for I<sub>DD</sub> characteristics may be conducted at nominal supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- 3. Timing and I<sub>DD</sub> tests may use a V<sub>IL</sub>-to-V<sub>IH</sub> swing of up to 1.5V in the test environment, but input timing is still referenced to  $V_{DDQ}/2$  (or to the crossing point for CK/CK#). The output timing reference voltage level is  $V_{DDQ}/2$ .

- 4. I<sub>DD</sub> is dependent on output loading and cycle rates. Specified values are obtained with minimum cycle time with the outputs open.

- 5. I<sub>DD</sub> specifications are tested after the device is properly initialized and values are averaged at the defined cycle rate.

- 6. MIN (<sup>t</sup>RC or <sup>t</sup>RFC) for I<sub>DD</sub> measurements is the smallest multiple of <sup>t</sup>CK that meets the minimum absolute value for the respective parameter. <sup>t</sup>RAS (MAX) for I<sub>DD</sub> measurements is the largest multiple of <sup>t</sup>CK that meets the maximum absolute value for <sup>t</sup>RAS.

- 7. Measurement is taken 500ms after entering into this operating mode to allow settling time for the tester.

- 8. V<sub>DD</sub> must not vary more than 4% if CKE is not active while any bank is active.

- 9. I<sub>DD2N</sub> specifies DQ, DQS, and DM to be driven to a valid high or low logic level.

- 10. CKE must be active (HIGH) during the entire time a REFRESH command is executed. From the time the AUTO REFRESH command is registered, CKE must be active at each rising clock edge until <sup>t</sup>RFC later.

- 11. This limit is a nominal value and does not result in a fail. CKE is HIGH during REFRESH command period (<sup>t</sup>RFC [MIN]) else CKE is LOW (for example, during standby).

- 12. Values for I<sub>DD6</sub> 85°C are guaranteed for the entire temperature range. All other I<sub>DD6</sub> values are estimated.

- 13. Typical values at 25°C, not a maximum value.

#### Figure 9: Typical Self Refresh Current vs. Temperature

Temperature (°C)

# **Electrical Specifications – AC Operating Conditions**

#### Table 11: Electrical Characteristics and Recommended AC Operating Conditions

|                                                    | to all parameters |                              |                   | • <u> </u>        |                   | 54                | -                 | 6                 | -75               |                   |                 |               |

|----------------------------------------------------|-------------------|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------|---------------|

| Parameter                                          |                   | Symbol                       | Min               | Max               | Min               | Мах               | Min               | Max               | Min               | Max               | Unit            | Notes         |

| Access window                                      | CL = 3            | <sup>t</sup> AC              | 2.0               | 5.0               | 2.0               | 5.0               | 2.0               | 5.0               | 2.0               | 6.0               | ns              |               |

| of DQ from<br>CK/CK#                               | CL = 2            |                              | 2.0               | 6.5               | 2.0               | 6.5               | 2.0               | 6.5               | 2.0               | 6.5               | -               |               |

| Clock cycle time                                   | CL = 3            | <sup>t</sup> CK              | 5                 | _                 | 5.4               | -                 | 6                 | -                 | 7.5               | -                 | ns              | 10            |

|                                                    | CL = 2            |                              | 12                | _                 | 12                | _                 | 12                | _                 | 12                | _                 |                 |               |

| CK high-level wi                                   | dth               | <sup>t</sup> CH              | 0.45              | 0.55              | 0.45              | 0.55              | 0.45              | 0.55              | 0.45              | 0.55              | <sup>t</sup> CK |               |

| CK low-level wid                                   | lth               | <sup>t</sup> CL              | 0.45              | 0.55              | 0.45              | 0.55              | 0.45              | 0.55              | 0.45              | 0.55              | <sup>t</sup> CK |               |

| CKE minimum p<br>(high and low)                    | ulse width        | <sup>t</sup> CKE             | 1                 | -                 | 1                 | -                 | 1                 | -                 | 1                 | -                 | <sup>t</sup> CK | 11            |

| Auto precharge<br>+ precharge tim                  | •                 | <sup>t</sup> DAL             | _                 | -                 | -                 | -                 | -                 | -                 | -                 | -                 |                 | 12            |

| DQ and DM in-<br>put hold time<br>relative to DQS  | fast slew rate    | <sup>t</sup> DH <sub>f</sub> | 0.48              | _                 | 0.54              | _                 | 0.6               | _                 | 0.8               | _                 | ns              | 13, 14,<br>15 |

| DQ and DM in-<br>put hold time<br>relative to DQS  | slow slew rate    | <sup>t</sup> DH <sub>s</sub> | 0.58              | -                 | 0.64              | -                 | 0.7               | _                 | 0.9               | _                 |                 |               |

| DQ and DM in-<br>put setup time<br>relative to DQ  | fast slew rate    | <sup>t</sup> DS <sub>f</sub> | 0.48              | -                 | 0.54              | -                 | 0.6               | -                 | 0.8               | _                 | ns              | 13, 14,<br>15 |

| DQ and DM in-<br>put setup time<br>relative to DQS | slow slew rate    | <sup>t</sup> DS <sub>s</sub> | 0.58              | -                 | 0.64              | -                 | 0.7               | _                 | 0.9               | _                 |                 |               |

| DQ and DM inpu<br>(for each input)                 | ut pulse width    | <sup>t</sup> DIPW            | 1.4               | -                 | 1.4               | -                 | 1.4               | -                 | 1.4               | -                 | ns              | 16            |

| Access window                                      | CL = 3            | <sup>t</sup> DQSCK           | 2.0               | 5.0               | 2.0               | 5.0               | 2.0               | 5.0               | 2.0               | 6.0               | ns              |               |

| of DQS from<br>CK/CK#                              | CL = 2            |                              | 2.0               | 6.5               | 2.0               | 6.5               | 2.0               | 6.5               | 2.0               | 6.5               |                 |               |

| DQS input high                                     | pulse width       | <sup>t</sup> DQSH            | 0.4               | 0.6               | 0.4               | 0.6               | 0.4               | 0.6               | 0.4               | 0.6               | <sup>t</sup> CK |               |

| DQS input low p                                    | oulse width       | <sup>t</sup> DQSL            | 0.4               | 0.6               | 0.4               | 0.6               | 0.4               | 0.6               | 0.4               | 0.6               | <sup>t</sup> CK |               |

| DQS–DQ skew, I<br>valid, per group                 |                   | <sup>t</sup> DQSQ            | -                 | 0.4               | _                 | 0.45              | _                 | 0.5               | _                 | 0.6               | ns              | 13, 17        |

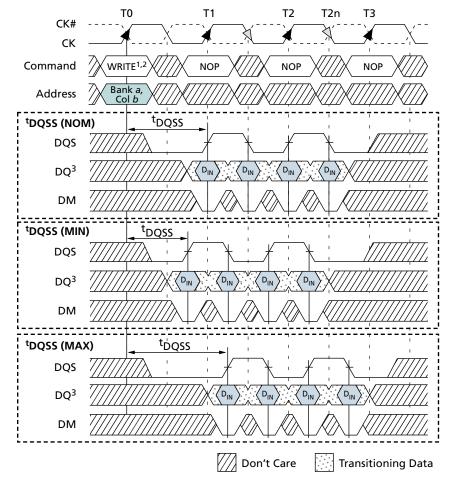

| WRITE command<br>latching transition               |                   | <sup>t</sup> DQSS            | 0.75              | 1.25              | 0.75              | 1.25              | 0.75              | 1.25              | 0.75              | 1.25              | <sup>t</sup> CK |               |

| DQS falling edge<br>rising – hold tim              |                   | <sup>t</sup> DSH             | 0.2               | -                 | 0.2               | -                 | 0.2               | -                 | 0.2               | -                 | <sup>t</sup> CK |               |

| DQS falling edge<br>setup time                     | e to CK rising –  | <sup>t</sup> DSS             | 0.2               | -                 | 0.2               | -                 | 0.2               | -                 | 0.2               | -                 | <sup>t</sup> CK |               |

| Data valid outpu                                   | ut window         | DVW                          | <sup>t</sup> QH - | <sup>t</sup> DQSQ | ns              | 17            |

Notes 1–9 apply to all parameters in this table;  $V_{DD}/V_{DDQ} = 1.70-1.95V$

#### Table 11: Electrical Characteristics and Recommended AC Operating Conditions (Continued)

|                                            |                                  |                              |                                       | ·5     |                                       | 54     | -                                     | -6     | -                                     | 75     |                 | Notes  |

|--------------------------------------------|----------------------------------|------------------------------|---------------------------------------|--------|---------------------------------------|--------|---------------------------------------|--------|---------------------------------------|--------|-----------------|--------|

| Parameter                                  |                                  | Symbol                       | Min                                   | Max    | Min                                   | Мах    | Min                                   | Max    | Min                                   | Max    | Unit            |        |

| Half-clock perio                           | d                                | tHP                          | <sup>t</sup> CH,<br><sup>t</sup> CL   | -      | ns              | 18     |

| Data-out High-                             | CL = 3                           | <sup>t</sup> HZ              | _                                     | 5.0    | I                                     | 5.0    | _                                     | 5.0    | I                                     | 6.0    | ns              | 19, 20 |

| Z window from<br>CK/CK#                    | CL = 2                           |                              | -                                     | 6.5    | _                                     | 6.5    | _                                     | 6.5    | _                                     | 6.5    |                 |        |

| Data-out Low-Z<br>CK/CK#                   | window from                      | <sup>t</sup> LZ              | 1.0                                   | -      | 1.0                                   | -      | 1.0                                   | -      | 1.0                                   | -      | ns              | 19     |

| Address and<br>control input<br>hold time  | fast slew rate                   | <sup>t</sup> IH <sub>F</sub> | 0.9                                   | -      | 1.0                                   | -      | 1.1                                   | -      | 1.3                                   | -      | ns              | 15, 21 |

| Address and<br>control input<br>hold time  | slow slew rate                   | <sup>t</sup> IH <sub>S</sub> | 1.1                                   | -      | 1.2                                   | -      | 1.3                                   | -      | 1.5                                   | -      |                 |        |

| Address and<br>control input<br>setup time | fast slew rate                   | <sup>t</sup> IS <sub>F</sub> | 0.9                                   | -      | 1.0                                   | -      | 1.1                                   | -      | 1.3                                   | -      | ns              | 15, 21 |

| Address and<br>control input<br>setup time | slow slew rate                   | <sup>t</sup> IS <sub>S</sub> | 1.1                                   | -      | 1.2                                   | -      | 1.3                                   | -      | 1.5                                   | -      |                 |        |

| Address and cor<br>width                   | ntrol input pulse                | <sup>t</sup> IPW             | 2.3                                   | -      | 2.4                                   | -      | 2.4                                   | -      | 2.6                                   | -      | ns              | 16     |

| LOAD MODE RE<br>command cycle              |                                  | <sup>t</sup> MRD             | 2                                     | -      | 2                                     | -      | 2                                     | -      | 2                                     | -      | <sup>t</sup> CK |        |

| DQ–DQS hold, E<br>to go nonvalid,          |                                  | <sup>t</sup> QH              | <sup>t</sup> HP -<br><sup>t</sup> QHS | _      | <sup>t</sup> HP -<br><sup>t</sup> QHS | -      | <sup>t</sup> HP -<br><sup>t</sup> QHS | _      | <sup>t</sup> HP -<br><sup>t</sup> QHS | -      | ns              | 13, 17 |

| Data hold skew                             | factor                           | <sup>t</sup> QHS             | _                                     | 0.5    | I                                     | 0.5    | -                                     | 0.65   | I                                     | 0.75   | ns              |        |

| ACTIVE-to-PREC command                     | HARGE                            | <sup>t</sup> RAS             | 40                                    | 70,000 | 42                                    | 70,000 | 42                                    | 70,000 | 45                                    | 70,000 | ns              |        |

| ACTIVE to ACTINTO REFRESH cor              | /E/ACTIVE to AU-<br>nmand period | <sup>t</sup> RC              | 55                                    | -      | 59.4                                  | -      | 60                                    | -      | 67.5                                  | -      | ns              |        |

| Active-to-read c                           | or write delay                   | <sup>t</sup> RCD             | 15                                    | -      | 16.2                                  | _      | 18                                    | _      | 22.5                                  | -      | ns              |        |

| Refresh period                             |                                  | <sup>t</sup> REF             | -                                     | 64     | -                                     | 64     | -                                     | 64     | -                                     | 64     | ms              |        |

| Average period<br>interval                 | ic refresh                       | <sup>t</sup> REFI            | -                                     | 7.8    | -                                     | 7.8    | -                                     | 7.8    | -                                     | 7.8    | μs              | 23     |

| AUTO REFRESH<br>period                     | command                          | <sup>t</sup> RFC             | 72                                    | -      | 72                                    | -      | 72                                    | -      | 72                                    | -      | ns              |        |

| PRECHARGE cor                              | nmand period                     | <sup>t</sup> RP              | 15                                    | _      | 16.2                                  | _      | 18                                    | _      | 22.5                                  | _      | ns              |        |

| DQS read<br>preamble                       | CL = 3                           | <sup>t</sup> RPRE            | 0.9                                   | 1.1    | 0.9                                   | 1.1    | 0.9                                   | 1.1    | 0.9                                   | 1.1    | <sup>t</sup> CK |        |

| DQS read<br>preamble                       | CL = 2                           | <sup>t</sup> RPRE            | 0.5                                   | 1.1    | 0.5                                   | 1.1    | 0.5                                   | 1.1    | 0.5                                   | 1.1    | <sup>t</sup> CK |        |

Notes 1–9 apply to all parameters in this table;  $V_{DD}/V_{DDQ} = 1.70-1.95V$

#### Table 11: Electrical Characteristics and Recommended AC Operating Conditions (Continued)

|                                                      |                   | -      | 5   | -5     | 54  | -      | 6   | -75    |     |                 |        |

|------------------------------------------------------|-------------------|--------|-----|--------|-----|--------|-----|--------|-----|-----------------|--------|

| Parameter                                            | Symbol            | Min    | Max | Min    | Мах | Min    | Max | Min    | Мах | Unit            | Notes  |

| DQS read postamble                                   | <sup>t</sup> RPST | 0.4    | 0.6 | 0.4    | 0.6 | 0.4    | 0.6 | 0.4    | 0.6 | <sup>t</sup> CK |        |

| Active bank <i>a</i> to active bank <i>b</i> command | <sup>t</sup> RRD  | 10     | -   | 10.8   | -   | 12     | -   | 15     | -   | ns              |        |

| Read of SRR to next valid command                    | <sup>t</sup> SRC  | CL + 1 | -   | <sup>t</sup> CK |        |

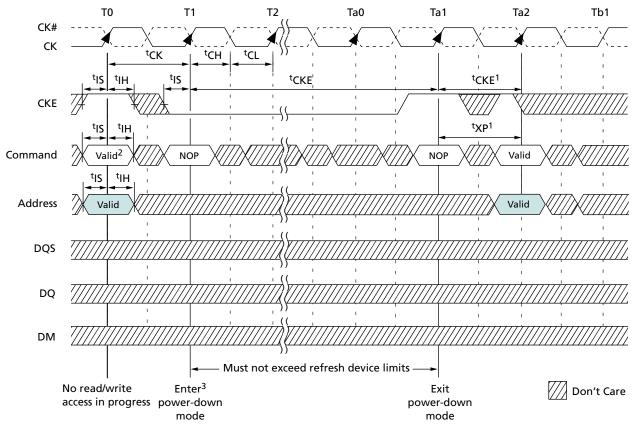

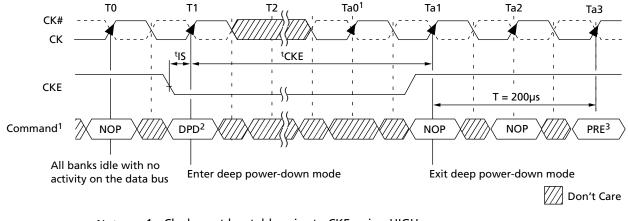

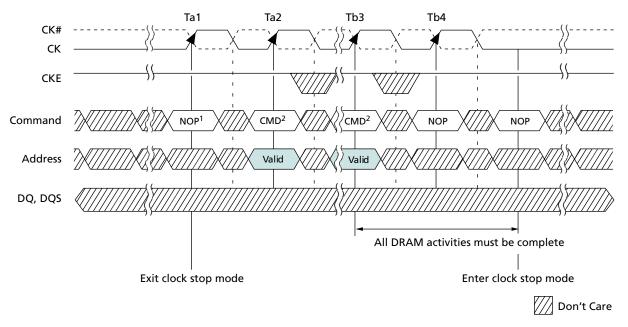

| SRR to read                                          | <sup>t</sup> SRR  | 2      | _   | 2      | -   | 2      | -   | 2      | _   | <sup>t</sup> CK |        |