### Features

- Digital Self-supervising Watchdog with Hysteresis

- One 250-mA Output Driver for Relay

- Enable Output Open Collector 8 mA

- Over/Undervoltage Detection

- ENABLE and RELAY Outputs Protected Against Standard Transients and 40 V Load Dump

- ESD Protection According to MIL-STD-883 D Test Method 3015.7

- Human Body Model:  $\pm 2$  kV (100 pF, 1.5 k $\Omega$ )

- Machine Model: ±200 V (200 pF, 0 Ω)

# Description

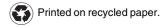

The U6808B is designed to support the fail-safe function of a safety critical system (e.g., ABS). It includes a relay driver, a watchdog controlled by an external R/C-network and a reset circuit initiated by an over and undervoltage condition of the 5-V supply providing a low-level reset signal.

Figure 1. Block Diagram

Special Fail-safe IC

# U6808B

Rev. 4707A-AUTO-05/03

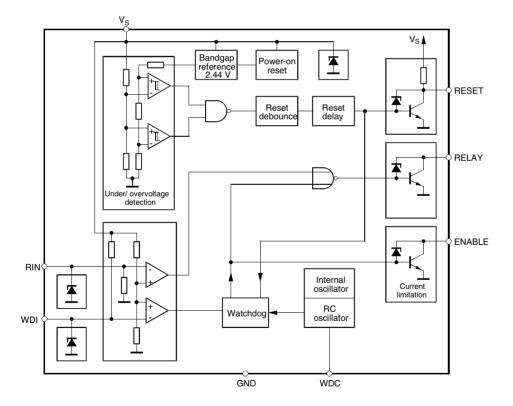

## **Pin Configuration**

Figure 2. Pinning SO8

### **Pin Description**

| Pin | Symbol | Туре                            | Function                       | Logic                                   |

|-----|--------|---------------------------------|--------------------------------|-----------------------------------------|

| 1   | RELAY  | Open collector<br>driver output | Fail-safe relay driver         | No signal: driver off<br>Low: driver on |

| 2   | GND    | Supply                          | Standard ground                | No signal                               |

| 3   | ENABLE | Digital output                  | Negative reset signal          | Low: reset                              |

| 4   | WDC    | Analog input                    | External RC for watchdog timer | No signal                               |

| 5   | RESET  | Digital output                  | Negative reset signal          | Low: reset                              |

| 6   | WDI    | Digital input                   | Watchdog trigger signal        | Pulse sequence                          |

| 7   | RIN    | Digital input                   | Activation of relay driver     | High: driver on<br>Low: driver off      |

| 8   | VS     | Supply                          | 5-V supply                     | -                                       |

## **Fail-safe Functions**

A fail-safe IC has to maintain its monitoring function even if there is a fault condition at one of the pins (e.g., short circuit). This ensures that a microcontroller system is not brought into a critical status. A critical status is reached if the system is not able to switch off the relay and to give a signal to the microcontroller via the ENABLE and RESET outputs. The following table shows the fault conditions for the pins.

### Table 1. Table of Fault Conditions

| Pin   | Function                                            | Short to Vs    | Short to VBat  | Short to GND   | Open Circuit   |

|-------|-----------------------------------------------------|----------------|----------------|----------------|----------------|

| RIN   | Digital input to<br>activate the fail-safe<br>relay | Relay on       | Relay on       | Relay off      | Relay off      |

| WDI   | Watchdog trigger<br>input                           | Watchdog reset | Watchdog reset | Watchdog reset | Watchdog reset |

| OSC   | Capacitor and resistor of watchdog                  | Watchdog reset | Watchdog reset | Watchdog reset | Watchdog reset |

| RELAY | Driver of the fail-safe relay                       |                |                | Relay on       | Relay off      |

### **Truth Tables**

Table 2. Truth Table for Over and Undervoltage Conditions

| Supply Voltage<br>(V <sub>S</sub> ) | Relay Input<br>(RIN) | Relay Output<br>Driver (RELAY) | RESET Output<br>(RESET) | Enable Output<br>Driver (ENABLE) |

|-------------------------------------|----------------------|--------------------------------|-------------------------|----------------------------------|

| Normal                              | Low                  | Off                            | High                    | Off                              |

| Normai                              | High                 | On                             | High                    | Off                              |

| Too low                             | Low                  | Off                            | Low                     | On                               |

| 100 100                             | High                 | Off                            | Low                     | On                               |

| Too high                            | Low                  | Off                            | Low                     | On                               |

| Too high                            | High                 | Off                            | Low                     | On                               |

Table 3. Truth Table for Watchdog Failures (Reset Output Do Not Care)

| Watchdog Input<br>(WDI) | Relay Input<br>(RIN) | Relay Output Driver<br>(RELAY) | Enable Output Driver<br>(ENABLE) |

|-------------------------|----------------------|--------------------------------|----------------------------------|

| Normal                  | Low                  | Off                            | Off                              |

| Normai                  | High                 | On                             | Off                              |

| Too slow                | Low                  | Off                            | On                               |

|                         | High                 | Off                            | On                               |

| Too fast                | Low                  | Off                            | On                               |

| Too fast                | High                 | Off                            | On                               |

## **Description of the Watchdog**

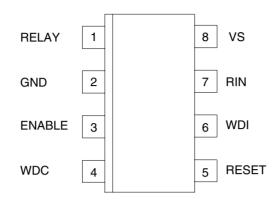

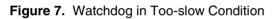

Figure 3. Watchdog Block Diagram

### Abstract

The microcontroller is monitored by a digital window watchdog which accepts an incomming trigger signal of a constant frequency for correct operation. The frequency of the trigger signal can be varied in a broad range as the watchdog's time window is determined by external R/C components. The following description refers to the block diagram, see Figure 3.

|              | (R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDI Input    | The microcontroller has to provide a trigger signal with the frequency $f_{WDI}$ which is fed to the WDI input. A positive edge of $f_{WDI}$ detected by a slope detector resets the binary counter and clocks the up/down counter additionally. The latter one counts only from 0 to 3 or reverse. Each correct trigger increments the up/down counter by 1, each wrong trigger decrements it by 1. As soon as the counter reaches status 3 the RS flip-flop is set (see Figure 4). A missing incoming trigger signal is detected after 250 clocks of the internal watchdog frequency $f_{RC}$ (see section "WD-OK Output") and resets the up/down counter directly.                                                                                          |

| RCOSC Input  | With an external R/C circuitry the IC generates a time base (frequency $f_{WDC}$ ) independent from the microcontroller. The watchdog's time window refers to a frequency of $f_{WDC} = 100 \times f_{WDI}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OSCERR Input | A smart watchdog has to ensure that internal problems with its own time base are detected and do not lead to an undesired status of the complete system. If the RC oscillator stops oscillating a signal is fed to the OSCERR input after a timeout delay. It resets the up/down counter and disables the WD-OK output.<br>Without this reset function the watchdog would freeze in its current status when f <sub>RC</sub> stops.                                                                                                                                                                                                                                                                                                                             |

| RESET Input  | During power-on and under/overvoltage detection a reset signal is fed to this pin. It resets the watchdog timer and sets the initial state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WD-OK Output | After the up/down counter is incremented to status 3 (see Figure 4) the RS flip-flop is set<br>and the WD-OK output becomes logic 1. This information is available for the microcon-<br>troller at the open-collector output ENABLE. If on the other hand the up/down counter is<br>decremented to 0 the RS flip-flop is reset, the WD-OK output and the ENABLE output<br>are disabled. The WD-OK output also controls a dual MUX stage which shifts the time<br>window by one clock after a successful trigger, thus forming a hysteresis to provide sta-<br>ble conditions for the evaluation of the trigger signal good or false. The WD-OK signal is<br>also reset in case the watchdog counter is not reset after 250 clocks (missing trigger<br>signal). |

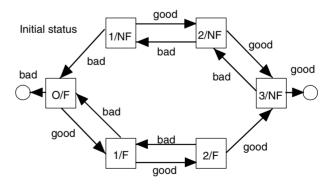

## Watchdog State Diagram Figure 4. Watchdog State Diagram

4

# U6808B

| Explanation                                           | In each block, the first character represents the state of the counter. The second nota-<br>tion indicates the fault status of the counter. A fault status is indicated by an F and a no<br>fault status is indicated by an NF. When the watchdog is powered up initially, the<br>counter starts out at the 0/F block (initial state). Good indicates that a pulse has been<br>received whose width resides within the timing window. Bad indicates that a pulse has<br>been received whose width is either too short or too long. |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Watchdog Window<br>Calculation                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

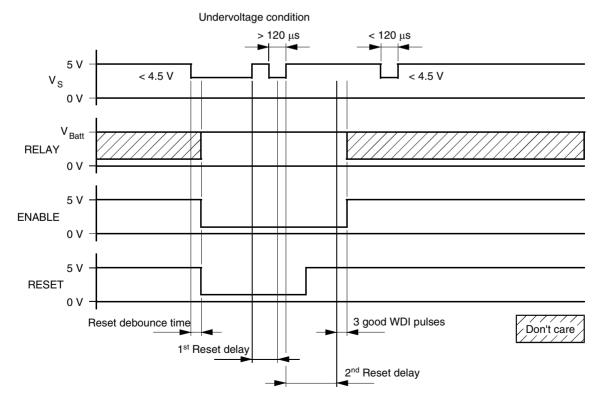

| Example with Recommended<br>Values                    | $C_{osc} = 3.3 \text{ nF}$ (should be preferably 10%, NPO)<br>$R_{osc} = 39 \text{ k}\Omega$ (may be 5%, Rosc < 100 k $\Omega$ due to leakage current and humidity)                                                                                                                                                                                                                                                                                                                                                                |

| RC Oscillator                                         | $\begin{split} t_{WDC}(s) &= 10^{-3} \times [C_{osc} \; (nF) \times [(0.00078 \times R_{osc} \; (k\Omega)) + 0.0005]] \\ f_{WDC}(Hz) &= 1/(t_{WDC}) \end{split}$                                                                                                                                                                                                                                                                                                                                                                   |

| Watchdog WDI                                          | $\begin{split} f_{WDI}(Hz) = & 0.01 \times f_{WDC} \\ t_{WDC} = & 100 \ \mu s \rightarrow f_{WDC} = & 10 \ \text{kHz} \\ f_{WDI} = & 100 \ \text{Hz} \rightarrow t_{WDI} = & 10 \ \text{ms} \end{split}$                                                                                                                                                                                                                                                                                                                           |

| WDI Pulse Width for Fault<br>Detection after 3 Pulses | Upper watchdog window<br>Minimum: $169/f_{WDC} = 16.9 \text{ ms} \rightarrow f_{WDC}/169 = 59.1 \text{ Hz}$<br>Maximum: $170/f_{WDC} = 17.0 \text{ ms} \rightarrow f_{WDC}/170 = 58.8 \text{ Hz}$<br>Lower watchdog window<br>Minimum: $79/f_{WDC} = 7.9 \text{ ms} \rightarrow f_{WDC}/79 = 126.6 \text{ Hz}$<br>Maximum: $80/f_{WDC} = 8.0 \text{ ms} \rightarrow f_{WDC}/80 = 125.0 \text{ Hz}$                                                                                                                                 |

| WDI Dropouts for Immediate<br>Fault Detection         | Minimum: $250/f_{WDC} = 25 \text{ ms}$ Maximum: $251/f_{WDC} = 25.1 \text{ ms}$                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Figure 5. Watchdog Timing Diagram with Tolerances

| Time/s 7                   | 9/f <sub>WDC</sub> 80                          | 0/f <sub>WDC</sub> 169              | 9/f <sub>WDC</sub>                        | 170/f <sub>WDC</sub> 2     | 50/f <sub>WDC</sub>                                              | 251/f <sub>WDC</sub>     |

|----------------------------|------------------------------------------------|-------------------------------------|-------------------------------------------|----------------------------|------------------------------------------------------------------|--------------------------|

|                            |                                                | Watchdog window update rate is good |                                           |                            |                                                                  |                          |

| Update rate is too<br>fast | D Update rate is<br>either too fast or<br>good |                                     | Update rate is<br>either too slow<br>good | Update rate is too<br>slow | Update rate is<br>either too slow or<br>pulse has<br>dropped out | Pulse has<br>dropped out |

Reset Delay

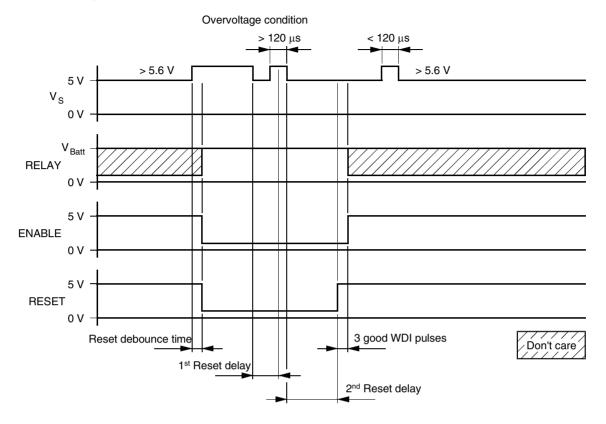

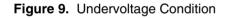

The duration of the over or undervoltage pulses determines the enable and reset output. A pulse duration shorter than the debounce time has no effect on the outputs. A pulse longer than the debounce time results in the first reset delay. If a pulse appears during this delay, a second delay time is triggered. Therefore, the total reset delay time can be longer than specified in the data sheet.

## **Absolute Maximum Ratings**

| Parameters                                                                                             | Symbol                               | Value       | Unit     |

|--------------------------------------------------------------------------------------------------------|--------------------------------------|-------------|----------|

| Supply-voltage range                                                                                   | V <sub>S</sub>                       | -0.2 to +16 | V        |

| Power dissipation<br>$V_S = 5 V$ , $T_{amb} = -40^{\circ}C$<br>$V_S = 5 V$ , $T_{amb} = +125^{\circ}C$ | P <sub>tot</sub><br>P <sub>tot</sub> | 250<br>150  | mW<br>mW |

| Thermal resistance                                                                                     | R <sub>thja</sub>                    | 160         | K/W      |

| Junction temperature                                                                                   | Tj                                   | 150         | °C       |

| Ambient temperature range                                                                              | T <sub>amb</sub>                     | -40 to +125 | °C       |

| Storage temperature range                                                                              | T <sub>stg</sub>                     | -55 to +155 | °C       |

## **Electrical Characteristics**

$V_{s}$  = 5 V,  $T_{amb}$  = -40 to +125°C, reference pin is GND,  $f_{intern}$  = 100 kHz + 50% - 45%,  $f_{WDC}$  = 10 kHz ±10%,  $f_{WDI}$  = 100 Hz

| Parameters                    | Test Conditions                                       | Symbol              | Min.                                                     | Тур. | Max.                   | Unit     |

|-------------------------------|-------------------------------------------------------|---------------------|----------------------------------------------------------|------|------------------------|----------|

| Supply Voltage                |                                                       |                     |                                                          |      | 4                      |          |

| Operation range general       |                                                       | Vs                  | 4.5                                                      |      | 5.5                    | V        |

| Operation range reset         |                                                       | V <sub>S</sub>      | 1.2                                                      |      | 16.0                   | V        |

| Supply Current                |                                                       |                     |                                                          |      | •                      |          |

| Relay off                     | $T_{amb} = - 40^{\circ}C$ $T_{amb} = +125^{\circ}C$   |                     |                                                          |      | 6                      | mA<br>mA |

| Relay on                      | $T_{amb} = -40^{\circ}C$<br>$T_{amb} = +125^{\circ}C$ |                     |                                                          |      | 15                     | mA<br>mA |

| Digital Input WDI             |                                                       |                     |                                                          |      |                        |          |

| Detection low                 |                                                       |                     | -0.2                                                     |      | $0.2 \times V_S$       | V        |

| Detection high                |                                                       |                     | $0.7 \times V_S$                                         |      | V <sub>S</sub> + 0.5 V | V        |

| Resistance to V <sub>S</sub>  |                                                       |                     | 10                                                       |      | 40                     | kΩ       |

| Input current low             | Input voltage = 0 V                                   |                     | 100                                                      |      | 550                    | μA       |

| Input current high            | Input voltage = V <sub>S</sub>                        |                     | -5                                                       |      | +5                     | μA       |

| Zener clamping voltage        |                                                       | V <sub>ZWDI</sub>   | 20                                                       |      | 24                     | V        |

| Digital Input RIN             |                                                       | ·                   |                                                          |      |                        |          |

| Detection low                 |                                                       |                     | -0.2                                                     |      | $0.2 \times V_S$       | V        |

| Detection high                |                                                       |                     | $0.7 \times V_S$                                         |      | V <sub>S</sub> + 0.5 V | V        |

| Resistance to GND             |                                                       |                     | 10                                                       |      | 40                     | kΩ       |

| Input current low             | Input voltage = 0 V                                   |                     | -5                                                       |      | +5                     | μA       |

| Input current high            | Input voltage = V <sub>S</sub>                        |                     | 100                                                      |      | 550                    | μA       |

| Zener clamping voltage        |                                                       | V <sub>ZRIN</sub>   | 20                                                       |      | 24                     | V        |

| Digital Output RESET with Int | ernal Pull-up                                         |                     |                                                          |      |                        |          |

| Voltage high                  | Pull-up = 6 kΩ                                        |                     | $\begin{array}{c} 0.7 \times \\ V_{S} + 0.1 \end{array}$ |      | Vs                     | V        |

| Voltage low                   | l ≤ 1 mA<br>1.2 V < V <sub>S</sub> < 16 V             |                     | 0                                                        |      | 0.3                    | v        |

| Zener clamping voltage        |                                                       | V <sub>ZRESET</sub> | 26                                                       |      | 30                     | V        |

| Reset debounce time           | Switch to low                                         | t <sub>deb</sub>    | 120                                                      | 320  | 500                    | μs       |

# **Electrical Characteristics (Continued)**

| Parameters                                                      | Test Conditions                                                                   | Symbol                                                     | Min.       | Тур. | Max.             | Unit           |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------|------------|------|------------------|----------------|

| Reset delay time                                                | Switch back to high                                                               | t <sub>del</sub>                                           |            | 50   |                  | ms             |

| Digital Output ENABLE with Open C                               | ollector                                                                          | •                                                          |            | I    |                  | <u> </u>       |

| Saturation voltage low                                          | l ≤ 8 mA                                                                          |                                                            | 0.01       |      | 0.5              | V              |

| Zener clamping voltage                                          |                                                                                   | V <sub>ZEN</sub>                                           | 26         |      | 30               | V              |

| Current limitation                                              |                                                                                   | I <sub>lim</sub>                                           | 8          |      |                  | mA             |

| Leakage current                                                 | V <sub>EN</sub> = 5 V<br>V <sub>EN</sub> = 16 V<br>V <sub>EN</sub> = 26 V         | I <sub>EN5</sub><br>I <sub>EN16</sub><br>I <sub>EN26</sub> |            |      | 20<br>100<br>200 | μΑ<br>μΑ<br>μΑ |

| Reset debounce time                                             | Switch to low                                                                     | t <sub>deb</sub>                                           | 120        | 320  | 500              | μs             |

| Reset delay time                                                | Switch back to high                                                               | t <sub>del</sub>                                           |            | 85   |                  | ms             |

| Relay Driver Output RELAY                                       |                                                                                   | •                                                          |            | I    |                  | <u> </u>       |

| Saturation voltage                                              | I ≤ 250 mA<br>I ≤ 130 mA                                                          | V <sub>Rsat</sub><br>V <sub>Rsat</sub>                     |            |      | 0.5<br>0.3       | V<br>V         |

| Maximum load current                                            | $T_{amb} = -40 \text{ to } +90^{\circ}\text{C}$<br>$T_{amb} > 90^{\circ}\text{C}$ | ا <sub>R</sub><br>ا <sub>R</sub>                           | 250<br>200 |      |                  | mA<br>mA       |

| Zener clamping voltage                                          |                                                                                   | V <sub>ZR</sub>                                            | 26         |      | 30               | V              |

| Turn-off enegy                                                  |                                                                                   |                                                            | 30         |      |                  | mJ             |

| Leakage current                                                 | V <sub>R</sub> = 16 V<br>V <sub>R</sub> = 26 V                                    | І <sub>R16</sub><br>І <sub>R26</sub>                       |            |      | 20<br>200        | μΑ<br>μΑ       |

| Reset and V <sub>s</sub> Control                                |                                                                                   | •                                                          |            | I    |                  | <u> </u>       |

| Lower reset level                                               |                                                                                   | Vs                                                         | 4.5        |      | 4.7              | V              |

| Upper reset level                                               |                                                                                   | Vs                                                         | 5.35       |      | 5.6              | V              |

| Hysteresis                                                      |                                                                                   |                                                            | 25         |      | 100              | mV             |

| Reset debounce time                                             |                                                                                   |                                                            | 120        | 320  | 500              | μs             |

| Reset delay                                                     |                                                                                   |                                                            | 20         | 50   | 80               | ms             |

| RC Oscillator WDC                                               |                                                                                   |                                                            |            |      | 1                |                |

| Oscillator frequency                                            |                                                                                   | f <sub>WDC</sub>                                           | 9          | 10   | 11               | kHz            |

| Watchdog Timing                                                 |                                                                                   |                                                            |            |      |                  |                |

| Power-on-reset<br>prolongation time                             |                                                                                   | t <sub>POR</sub>                                           | 34 .3      |      | 103.1            | ms             |

| Detection time for<br>RC oscillator fault                       | V <sub>RC</sub> = const.                                                          | t <sub>RCerror</sub>                                       | 81.9       |      | 246              | ms             |

| Time interval for over-/undervoltage detection                  |                                                                                   | t <sub>D,OUV</sub>                                         | 0.16       |      | 0.64             | ms             |

| Reaction time of RESET output<br>over/undervoltage              |                                                                                   | t <sub>R,OUV</sub>                                         | 0.187      |      | 0.72             | ms             |

| Nominal frequency for WDI                                       | $f_{RC} = 100 \times f_{WDI}$                                                     | f <sub>WDI</sub>                                           | 10         |      | 130              | Hz             |

| Nominal frequency for WDC                                       | $f_{WDI} = 1/100 \times f_{WDC}$                                                  | f <sub>wDC</sub>                                           | 1          |      | 13               | kHz            |

| Minimum pulse duration for a securely WDI input pulse detection |                                                                                   | t <sub>P,WDI</sub>                                         | 182        |      |                  | μs             |

| Frequency range for a<br>correct WDI signal                     |                                                                                   | f <sub>WDI</sub>                                           | 64.7       |      | 112.5            | Hz             |

# **Electrical Characteristics (Continued)**

$V_{S} = 5 V$ ,  $T_{amb} = -40$  to  $+125^{\circ}C$ , reference pin is GND,  $f_{intern} = 100 \text{ kHz} + 50\% - 45\%$ ,  $f_{WDC} = 10 \text{ kHz} \pm 10\%$ ,  $f_{WDI} = 100 \text{ Hz}$

| Parameters                                                        | Test Conditions           | Symbol                | Min. | Тур. | Max. | Unit   |

|-------------------------------------------------------------------|---------------------------|-----------------------|------|------|------|--------|

| Number of incorrect WDI trigger<br>counts for locking the outputs |                           | n <sub>lock</sub>     |      | 3    |      |        |

| Number of correct WDI trigger counts for releasing the outputs    |                           | n <sub>release</sub>  |      | 3    |      |        |

| Detection time for a stucked WDI signal                           | V <sub>WDI</sub> = const. | t <sub>WDlerror</sub> | 24.5 |      | 25.5 | ms     |

| Watchdog Timing Relative to f <sub>wDC</sub>                      |                           | ·                     |      |      |      | •      |

| Minimum pulse duration for a securely WDI input pulse detection   |                           |                       |      | 2    |      | Cycles |

| Frequency range for a<br>correct WDI signal                       |                           |                       | 80   |      | 169  | Cycles |

| Hysteresis range at the WDI ok margins                            |                           |                       |      | 1    |      | Cycle  |

| Detection time for a dropped out WDI signal                       | V <sub>WDI</sub> = const. |                       | 250  |      | 251  | Cycles |

# Protection against Transient Voltages According to ISO TR 7637-3 Level 4 (Except Pulse 5)

| Pulse | Voltage | Source<br>Resistance <sup>(1)</sup> | Rise Time | Duration | Amount |

|-------|---------|-------------------------------------|-----------|----------|--------|

| 1     | -110 V  | 10                                  | 100 V/s   | 2 ms     | 15.000 |

| 2     | +110 V  | 10                                  | 100 V/s   | 0.05 ms  | 15.000 |

| 3a    | -160 V  | 50                                  | 30 V/ns   | 0.1 s    | 1 h    |

| 3b    | +150 V  | 50                                  | 20 V/ns   | 0.1 s    | 1 h    |

| 5     | 40 V    | 2                                   | 10 V/ms   | 250 ms   | 20     |

Note: 1. Relay driver: relay coil with  $R_{min} = 70 \Omega$  to be added

8

# **Timing Diagrams**

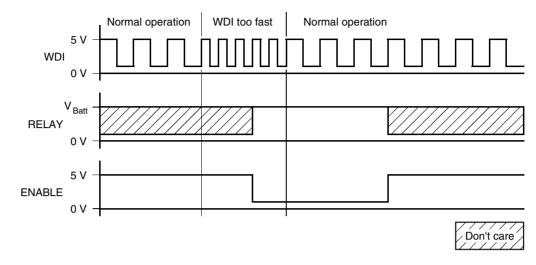

Figure 6. Watchdog in Too-fast Condition

### Figure 8. Overvoltage Condition

10 **U6808B**

### Figure 10. Application Circuit

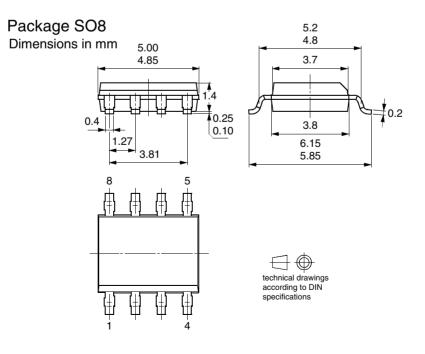

# **Ordering Information**

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| U6808B               | SO8     | _       |

## **Package Information**

#### **Atmel Headquarters**

*Corporate Headquarters* 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### **Microcontrollers**

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

ASIC/ASSP/Smart Cards Zone Industrielle

13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

#### *Biometrics/Imaging/Hi-Rel MPU/*

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2003.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel<sup>®</sup> is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.