### Features

- Pulse-width Modulation up to 2 kHz Clock Frequency

- + Protection Against Short-circuit, Load Dump Overvoltage and Reverse  $\rm V_S$

- Duty Cycle 18% to 100% Continuously

- Internally Reduced Pulse Slope of Lamp's Voltage

- Interference and Damage Protection According to VDE 0839 and ISO/TR 7637/1

- Charge-pump Noise Suppression

- Ground-wire Breakage Protection

## 1. Description

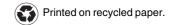

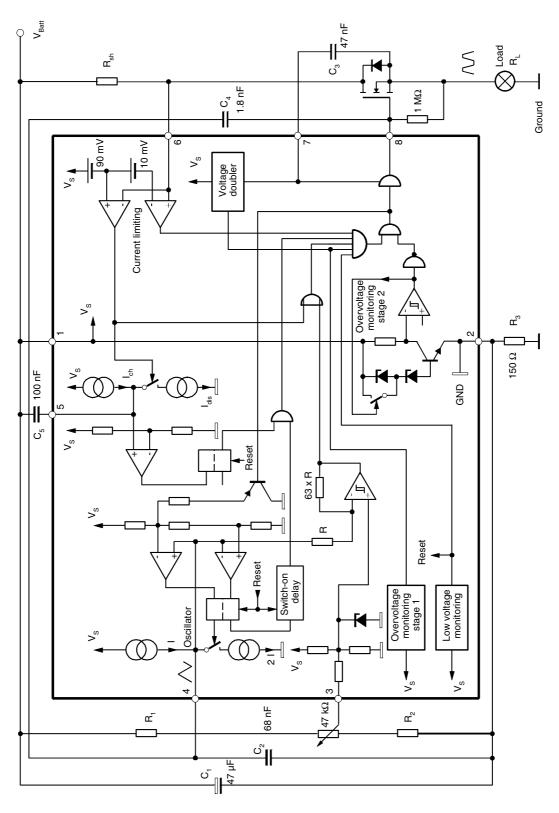

The U6083B is a PWM IC in bipolar technology for the control of an N-channel power MOSFET used as a high-side switch. The IC is ideal for use in brightness control systems (dimming) of lamps, for example, in dashboard applications.

PWM Power Control IC with Interference Suppression

# U6083B

<u>AIMEL</u>

Rev. 4770B-AUTO-09/05

Figure 1-1. Block Diagram with External Circuit

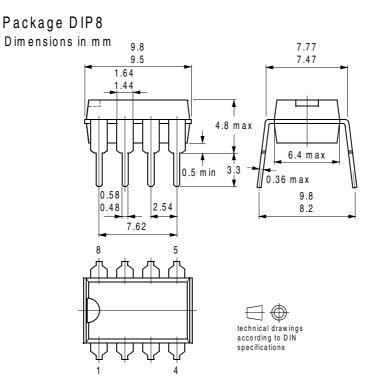

# 2. Pin Configuration

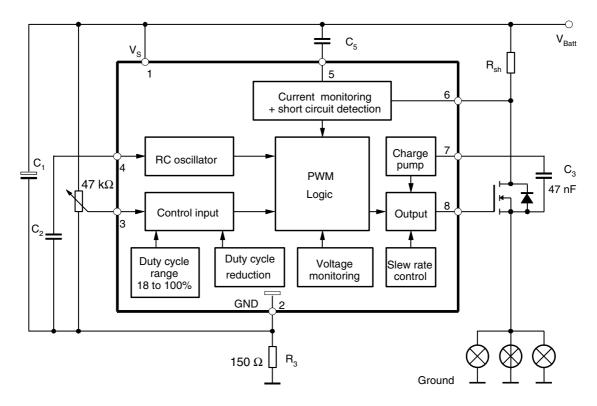

Figure 2-1. Pinning DIP8

### Table 2-1.Pin Description

| Pin | Symbol | Function                       |

|-----|--------|--------------------------------|

| 1   | VS     | Supply voltage V <sub>S</sub>  |

| 2   | GND    | IC ground                      |

| 3   | VI     | Control input (duty cycle)     |

| 4   | OSC    | Oscillator                     |

| 5   | DELAY  | Short-circuit protection delay |

| 6   | SENSE  | Current sensing                |

| 7   | 2 VS   | Voltage doubler                |

| 8   | OUTPUT | Output                         |

### 3. Functional Description

### 3.1 Pin 1, Supply Voltage, V<sub>S</sub> or V<sub>Batt</sub>

#### 3.1.1 Overvoltage Detection

3.1.1.1 Stage 1

If overvoltages of  $V_{Batt}$  > 20V (typically) occur, the external transistor is switched off, and switched on again at  $V_{Batt}$  < 18.5V (hysteresis).

#### 3.1.1.2 Stage 2

If  $V_{Batt} > 28.5V$  (typically), the voltage limitation of the IC is reduced from  $V_S = 26V$  to 20V. The gate of the external transistor remains at the potential of the IC ground, thus producing voltage sharing between FET and lamps in the event of overvoltage pulses (e.g., load dump). The short-circuit protection is not in operation. At  $V_{Batt}$  approximately < 23V, the overvoltage detection stage 2 is switched off. Thus, during overvoltage detection stage 2, the lamp voltage  $V_{lamp}$  is calculated as follows:

$V_{Lamp} = V_{Batt} - V_{S} - V_{GS}$

V<sub>S</sub> = supply voltage of the IC at overvoltage detection stage 2

$V_{GS}$  = gate - source voltage of the FET

#### 3.1.2 Undervoltage Detection

In the event of voltages of approximately  $V_{Batt}$  < 5.0V, the external FET is switched off and the latch for short-circuit detection is reset.

A hysteresis ensures that the FET is switched on again at approximately  $V_{Batt} \ge 5.4V$ .

### 3.2 Pin 2, GND

#### 3.2.1 Ground-wire Breakage

To protect the FET in the case of ground-wire breakage, a 1 M $\Omega$  resistor between gate and source is recommended to provide proper switch-off conditions.

### 3.3 Pin 3, Control Input

The pulse width is controlled by means of an external potentiometer (47 k $\Omega$ ). The characteristic (angle of rotation/duty cycle) is linear. The duty cycle can be varied from 18 to 100%. It is possible to further restrict the duty cycle with the resistors R<sub>1</sub> and R<sub>2</sub> (see Figure 7-1 on page 11).

In order to reduce the power dissipation of the FET and to increase the lifetime of the lamps, the IC automatically reduces the maximum duty cycle at pin 8 if the supply voltage exceeds  $V_2 = 13V$ . Pin 3 is protected against short-circuit to  $V_{Batt}$  and ground ( $V_{Batt} \leq 16.5V$ ).

#### 3.4 Pin 4, Oscillator

The oscillator determines the frequency of the output voltage. This is defined by an external capacitor, C<sub>2</sub>. It is charged with a constant current, I, until the upper switching threshold is reached. A second current source is then activated which taps a double current,  $2 \times I$ , from the charging current. The capacitor, C2, is thus discharged at the current, I, until the lower switching threshold is reached. The second source is then switched off again and the procedure starts once more.

#### 3.4.1 **Example for Oscillator Frequency Calculation**

Switching thresholds

| V <sub>T100</sub>     | = High switching threshold (100% duty cycle)                           |

|-----------------------|------------------------------------------------------------------------|

| V <sub>T100</sub>     | = $V_S \times \alpha_1$ = ( $V_{Batt} - I_S \times R_3$ ) × $\alpha_1$ |

| V <sub>T&lt;100</sub> | = High switching threshold (< 100% duty cycle)                         |

| V <sub>T&lt;100</sub> | = $V_S \times \alpha_2$ = ( $V_{Batt} - I_S \times R_3$ ) × $\alpha_2$ |

| V <sub>TL</sub>       | = Low switching threshold                                              |

| V <sub>TL</sub>       | = $V_S \times \alpha_3$ = ( $V_{Batt} - I_S \times R_3$ ) × $\alpha_3$ |

| where                 |                                                                        |

$\alpha_1, \alpha_2$  and  $\alpha_3$  are fixed values

#### 3.4.2 **Calculation Example**

The above mentioned threshold voltages are calculated for the following values given in the data sheet.

| V <sub>Batt</sub>     | = 12V, I_S = 4 mA, R_3 = 150\Omega, $\alpha_1$ = 0.7, $\alpha_2$ = 0.67 and $\alpha_3$ = 0.28 |

|-----------------------|-----------------------------------------------------------------------------------------------|

| V <sub>T100</sub>     | = $(12V - 4 \text{ mA} \times 150\Omega) \times 0.7 \approx 8V$                               |

| V <sub>T&lt;100</sub> | $= 11.4V \times 0.67 = 7.6V$                                                                  |

| V <sub>TL</sub>       | $= 11.4V \times 0.28 = 3.2V$                                                                  |

#### 3.4.3 **Oscillator Frequency**

3 cases have to be distinguished

1.  $f_1$  for duty cycle = 100%, no slope reduction with capacitor  $C_4$ (see Figure 7-1 on page 11)

$$f_1 = \frac{I_{OSC}}{2 \times (V_{T100} - V_{TL}) \times C_2}$$

, where  $C_2 = 68$  nF,  $I_{OSC} = 45 \ \mu A$

f<sub>1</sub> = ... = 75 Hz

2.  $f_2$  for duty cycle < 100%, no slope reduction with capacitor  $C_4$ For a duty cycle of less than 100%, the oscillator frequency, f, is as follows:

$$f_2$$

=  $\frac{I_{OSC}}{2 \times (V_{T < 100} - V_{TL}) \times C_2}$  , where  $C_2$  = 68 nF,  $I_{OSC}$  = 45  $\mu A$

$$f_2 = ... = 69 Hz$$

f<sub>3</sub> with duty cycle < 100% with slope reduction capacitor C<sub>4</sub> (see "Output Slope Control" on page 6)

$$f_{3} = \frac{I_{osc}}{2 \times (V_{T<100} - V_{TL}) \times C_{2} + 2V_{Batt} \times C_{4}}$$

where  $C_2 = 68 \text{ nF}$ ,  $I_{OSC} = 45 \mu A$ ,  $C_4 = 1.8 \text{ nF}$

f<sub>3</sub> = ... = 70 Hz

By selecting different values of  $C_2$  and  $C_4$ , it is possible to have a range of oscillator frequencies from 10 to 2000 Hz as shown in the data sheet.

#### 3.5 Output Slope Control

The slope of the lamp voltage is internally limited to reduce radio interference by limitation of the voltage gain of the PWM comparator.

Thus, the voltage rise on the lamp is proportional to the oscillator voltage increase at the switchover time according to the equation.

$$dV_8/d_t = \alpha_4 \times dV_4/d_t = 2 \times \alpha_4 \times f \times (\alpha_2 - \alpha_3) \times (V_{Batt} - I_S \times R_3)$$

when

f = 75 Hz,  $V_{TX} = V_T < 100$  and  $\alpha_4 = 63$

then

$$dV_8/d_t = 2 \times 63 \times 75 \text{ Hz} \times (0.67 - 0.28) \times (12V - 4 \text{ mA} \times 15\Omega) = 42 \text{ V/ms}$$

Via an external capacitor,  $C_4$ , the slope can be further reduced as follows:

$dV_8/d_t = I_{OSC}/(C_4 + C_2/\alpha_4)$

when

$I_{OSC}$  = 45 µA,  $C_4$  = 1.8 nF,  $C_2$  = 68 nF and  $\alpha_4$  = 63

then  $dV_8/d_t = 45 \ \mu A/(1.8 \ nF + 68 \ nF/63) = 15.6 \ V/ms$

To damp oscillation tendencies, a resistance of  $100\Omega$  in series with capacitance  $C_4$  is recommended.

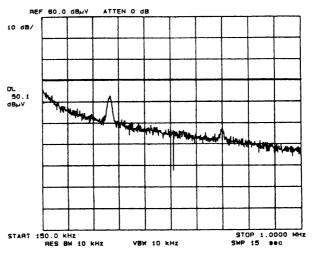

### 3.6 Interference Suppression

- "On-board" radio reception according to VDE 0879 part 3/4.81

- Test conditions referring to Figure 3-1

- Application circuit according to Figure 1-1 on page 2 or Figure 7-1 on page 11

- Load: nine 4W lamps in parallel

- Duty cycle = 18%

- V<sub>Batt</sub> = 12V

- f<sub>Osc</sub> = 100 Hz

### 3.7 Pins 5 and Pin 6, Short-circuit Protection and Current Sensing

#### 3.7.1 Short-circuit Detection and Time Delay, t<sub>d</sub>

The lamp current is monitored by means of an external shunt resistor. If the lamp current exceeds the threshold for the short-circuit detection circuit ( $V_{T2} \approx 90 \text{ mV}$ ), the duty cycle is switched over to 100% and the capacitor  $C_5$  is charged by a current source of  $I_{ch} - I_{dis}$ . The external FET again is switched off after the cut-off threshold ( $V_{T5}$ ) is reached. Switching on the FET again is possible after a power-on reset only. The current source,  $I_{dis}$ , ensures that the capacitor  $C_5$  is not charged by parasitic currents.

The time delay,  $t_d$ , is calculated as follows:

$$\begin{split} t_d &= C_5 \times \ V_{T5}/(I_{ch} - I_{dis}) \\ \text{With } C_5 &= 100 \text{ nF and } V_{T5} = 10.4 \text{V}, \ I_{ch} = 13 \ \mu\text{A}, \ I_{dis} = 3 \ \mu\text{A}, \text{ the time delay is as follows:} \\ t_d &= 100 \ \text{nF} \times \ 10.4 \text{V}/(13 \ \mu\text{A} - 3 \ \mu\text{A}) \\ t_d &= 104 \ \text{ms} \end{split}$$

#### 3.7.2 Current Limitation

The lamp current is limited by a control amplifier to protect the external power transistor. The voltage drop across the external shunt resistor acts as the measured variable. Current limitation takes place for a voltage drop of  $V_{T1} \approx 100 \text{ mV}$ . Owing to the difference  $V_{T1} - V_{T2} \approx 10 \text{ mV}$ , it ensures that current limitation occurs only when the short-circuit detection circuit has responded.

After a power-on reset, the output is inactive for half an oscillator cycle. During this time, the supply voltage capacitor can be charged so that current limitation is guaranteed in the event of a short-circuit when the IC is switched on for the first time.

### 3.8 Pins 7 and 8, Charge Pump and Output

Pin 8 (output) is suitable for controlling a power MOSFET. During the active integration phase, the supply current of the operational amplifier is mainly supplied by the capacitor  $C_3$  (bootstrapping). In addition, a trickle charge is generated by an integrated oscillator ( $f_7 \approx 400$  kHz) and a voltage doubler circuit. This permits a gate voltage supply at a duty cycle of 100%.

# U6083B

## 4. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                | Symbol           | Value       | Unit |

|---------------------------|------------------|-------------|------|

| Junction temperature      | Tj               | 150         | °C   |

| Ambient temperature range | T <sub>amb</sub> | -40 to +110 | °C   |

| Storage temperature range | T <sub>stg</sub> | -55 to +125 | °C   |

## 5. Thermal Resistance

| Parameters       | Symbol            | Value | Unit |

|------------------|-------------------|-------|------|

| Junction ambient | R <sub>thJA</sub> | 120   | K/W  |

### 6. Electrical Characteristics

$T_{amb} = -40^{\circ}$ C to +110°C,  $V_{Batt} = 9$ V to 16.5V, (basic function is guaranteed between 6.0V to 9.0V) reference point ground, unless otherwise specified (see Figure 1-1 on page 2). All other values refer to pin GND (pin 2).

| Parameters                       | Test Conditions                | Pin | Symbol            | Min.         | Тур.         | Max.         | Unit   |

|----------------------------------|--------------------------------|-----|-------------------|--------------|--------------|--------------|--------|

| Current consumption              |                                | 1   | ا <sub>S</sub>    |              |              | 7.9          | mA     |

| Supply voltage                   | Overvoltage detection, stage 1 |     | V <sub>Batt</sub> |              |              | 25           | V      |

| Stabilized voltage               | I <sub>S</sub> = 10 mA         | 1   | Vs                | 24.5         |              | 27.0         | V      |

| Battery undervoltage detection   | on<br>off                      |     | V <sub>Batt</sub> | 4.4<br>4.8   | 5.0<br>5.4   | 5.6<br>6.0   | V      |

| Battery Overvoltage Detection    |                                | •   |                   |              | •            |              |        |

| Stage 1:                         | on<br>off                      |     | V <sub>Batt</sub> | 18.3<br>16.7 | 20.0<br>18.5 | 21.7<br>20.3 | V<br>V |

| Stage 2:<br>Detection stage 2    | on<br>off                      |     | V <sub>Batt</sub> | 25.5<br>19.5 | 28.5<br>23.0 | 32.5<br>26.5 | V<br>V |

| Stabilized voltage               | I <sub>S</sub> = 30 mA         | 1   | Vs                | 18.5         | 20.0         | 21.5         | V      |

| Short-circuit Protection         |                                | 6   |                   |              |              |              |        |

| Short-circuit current limitation | $V_{T1} = V_S - V_6$           |     | V <sub>T1</sub>   | 85           | 100          | 120          | mV     |

| Short-circuit detection          | $V_{T2} = V_S - V_6$           |     | V <sub>T2</sub>   | 75           | 90           | 105          | mV     |

|                                  | $V_{T2} = V_S - V_6$           |     | $V_{T1} - V_{T2}$ | 3            | 10           | 30           | mV     |

| Delay Timer Short-circuit Dete   | ction, V <sub>Batt</sub> = 12V | 5   |                   |              |              |              |        |

| Switched off threshold           | $V_{T5} = V_S - V_5$           |     | V <sub>T5</sub>   | 10.2         | 10.4         | 10.6         | V      |

| Charge current                   |                                |     | I <sub>ch</sub>   |              | 13           |              | μA     |

| Discharge current                |                                |     | I <sub>dis</sub>  |              | 3            |              | μA     |

| Capacitance current              | $I_5 = I_{ch} - I_{dis}$       |     | $I_5$             | 5            | 10           | 15           | mA     |

Note: 1. Reference point is battery ground

| R |

|---|

## 6. Electrical Characteristics (Continued)

$T_{amb} = -40^{\circ}$ C to +110°C,  $V_{Batt} = 9$ V to 16.5V, (basic function is guaranteed between 6.0V to 9.0V) reference point ground, unless otherwise specified (see Figure 1-1 on page 2). All other values refer to pin GND (pin 2).

| Parameters                   | Test Conditions                                                         | Pin | Symbol            | Min.              | Тур.              | Max.               | Unit |

|------------------------------|-------------------------------------------------------------------------|-----|-------------------|-------------------|-------------------|--------------------|------|

| Voltage Doubler              |                                                                         | 7   |                   |                   |                   | 1                  | I    |

| Voltage                      | Duty cycle 100%                                                         |     | V <sub>7</sub>    | 2 V <sub>S</sub>  |                   |                    |      |

| Oscillator frequency         |                                                                         |     | f <sub>7</sub>    | 280               | 400               | 520                | kHz  |

| Internal valte na limitation |                                                                         |     | V <sub>7</sub>    | 26                | 27.5              | 30.0               | V    |

| Internal voltage limitation  | $I_7 = 5 \text{ mA}$ (whichever is lower)                               |     | V <sub>7</sub>    | V <sub>S+14</sub> | V <sub>S+15</sub> | V <sub>S+16</sub>  | V    |

| Edge steepness               | $dv_8/dt = \alpha_4 dV_4/dt$<br>$dV_8/dt_{max}$                         |     | α <sub>4</sub>    | 53                | 63                | 72<br>130          | V/ms |

| Gate Output                  |                                                                         | 8   |                   |                   |                   |                    |      |

|                              | Low level                                                               |     | V <sub>8</sub>    | 0.35              | 0.70              | 0.95               | V    |

| Voltage                      | $V_{Batt} = 16.5V T_{amb} = 110^{\circ}C,$<br>$R_3 = 150\Omega$         |     | V <sub>8</sub>    |                   |                   | 1.5 <sup>(1)</sup> | V    |

|                              | High level, duty cycle 100%                                             |     | V <sub>8</sub>    |                   | V <sub>7</sub>    |                    | V    |

| Current                      | V <sub>8</sub> = Low level                                              |     | I <sub>8</sub>    | 1.0               |                   |                    | mA   |

| Current                      | $V_8 =$ High level, $I_7 >  I_8 $                                       |     | I <sub>8</sub>    | -1.0              |                   |                    | mA   |

|                              | Min: C <sub>2</sub> = 68 nF                                             |     |                   | 15                | 18                | 21                 |      |

| Duty cycle                   | Max: $V_{Batt} \le 12.4V$<br>$V_{Batt} = 16.5V$ , $C_2 = 68 \text{ nF}$ |     | t <sub>p</sub> /T | 100<br>65         | 73                | 81                 | %    |

| Oscillator                   |                                                                         |     |                   |                   |                   |                    |      |

| Frequency                    |                                                                         | 4   | f                 | 10                |                   | 2000               | Hz   |

| Threshold cycle              | $V_8 = \text{High}, \ \alpha_1 = \frac{V_{T100}}{V_S}$                  |     | α                 | 0.68              | 0.7               | 0.72               |      |

| Upper                        | $V_8 = Low, \ \alpha_2 = \frac{V_{T < 100}}{V_S}$                       |     | α2                | 0.65              | 0.67              | 0.69               |      |

| Lower                        | $\alpha_3 = \frac{V_{TL}}{V_S}$                                         |     | α3                | 0.26              | 0.28              | 0.3                |      |

| Oscillator current           | V <sub>Batt</sub> = 12V                                                 |     | ±l <sub>OSC</sub> | 34                | 45                | 54                 | μA   |

| Frequency                    | $C_4$ open, $C_2 = 68$ nF<br>duty cycle = 50%                           |     | f                 | 56                | 75                | 90                 | Hz   |

Note: 1. Reference point is battery ground

# 7. Application

Figure 7-1. Application Circuit

# 8. Ordering Information

| Extended Type Number | Package | Remarks |

|----------------------|---------|---------|

| U6083B-MY            | DIP8    | Pb-free |

# 9. Package Information

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

Memory 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2005. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.