#### **Features**

- PowerPC® Single Issue Integer Core

- Precise Exception Model

- Extensive System Development Support

- On-chip Watchpoints and Breakpoints

- Program Flow Tracking

- On-chip Emulation (Once) Development Interface

- High Performance (Dhrystone 2.1: 52 MIPS at 50 MHz, 3.3V, 1.3 Watts Total Power)

- Low Power (< 241 mW at 25 MHz. 2.4V Internal, 3.3V I/O-core, Caches, MMUs, I/O)</li>

- MPC8XX PowerPC System Interface, Including a Periodic Interrupt Timer, a Bus Monitor, and Real-time Clocks

- Single Issue, 32-bit Version of the Embedded PowerPC Core (Fully Compatible with Book 1 of the PowerPC Architecture Definition) with 32 x 32-bit Fixed Point Registers

- Embedded PowerPC Performs Branch Folding, Branch Prediction with Conditional Prefetch, without Conditional Execution

- 4-Kbyte Data Cache and 4-Kbyte Instruction Cache, Each with an MMU

- Instruction and Data Caches are Two-way, Set Associative, Physical Address,

Word Line Burst, Least Recently Used (LRU) Replacement, Lockable On-line

Granularity

- MMUs with 32 Entry TLB, Fully Associative Instruction and Data TLBs

- MMUs Support Multiple Page Sizes of 4 KB, 16 KB, 256 KB, 512 KB and 8 MB;

16 Virtual Address Spaces and 8 Protection Groups

- Advanced On-chip Emulation Debug Mode

- Up to 32-bit Data Bus (Dynamic Bus Sizing for 8- and 16-bit)

- 32 Address Lines

- · Fully Static Design

- $V_{CC} = +3.3V \pm 5\%$

- f<sub>max</sub> = 66 MHz (80 MHz (TBC))

- Military Temperature Range: -55°C < T<sub>C</sub> < +125°C

- P<sub>D</sub> = 0.75 W Typical at 66 MHz

## **Description**

The TSPC860 PowerPC QUad Integrated Communication Controller (Power QUICC $^{\text{TM}}$ ) is a versatile one-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications. It particularly excels in communications and networking systems. The Power QUICC (pronounced "quick") can be described as a PowerPC-based derivative of the TS68EN360 (QUICC $^{\text{TM}}$ ).

The CPU on the TSPC860 is a 32-bit PowerPC implementation that incorporates memory management units (MMUs) and instruction and data caches. The communications processor module (CPM) of the TS68EN360 QUICC has been enhanced with the addition of a Two-wire Interface (TWI) compatible with protocols such as I<sup>2</sup>C. Moderate to high digital signal processing (DSP) functionality has been added to the CPM. The memory controller has been enhanced, enabling the TSPC860 to support any type of memory, including high performance memories and newer dynamic random access memories (DRAMs). Overall system functionality is completed with the addition of a PCMCIA socket controller supporting up to two sockets and a real-time clock.

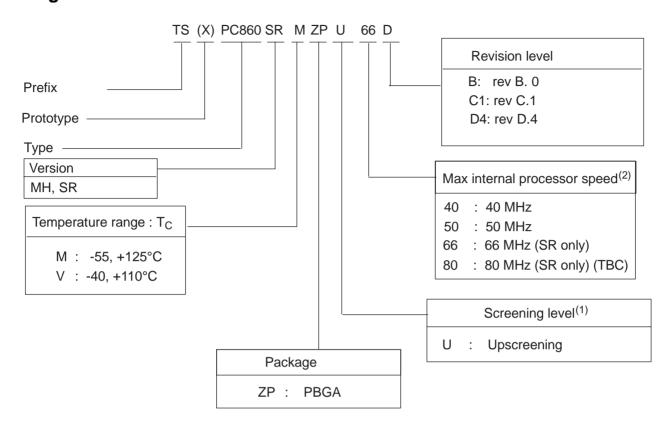

32-bit Quad Integrated Power QUICC™ Communication Controller

TSPC860

## **Screening/Quality**

This product will be manufactured in full compliance with:

According to Atmel Standards

## **General Description**

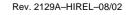

The TSPC860 is functionally composed of three major blocks:

- A 32-bit PowerPC Core with MMUs and Caches

- A System Interface Unit

- A Communications Processor Module

Figure 1. Block Diagram View of the TSPC860

#### **Main Features**

The Following is a List of the TSPC860's Important Features:

- · Fully Static Design

- Four Major Power Saving Modes

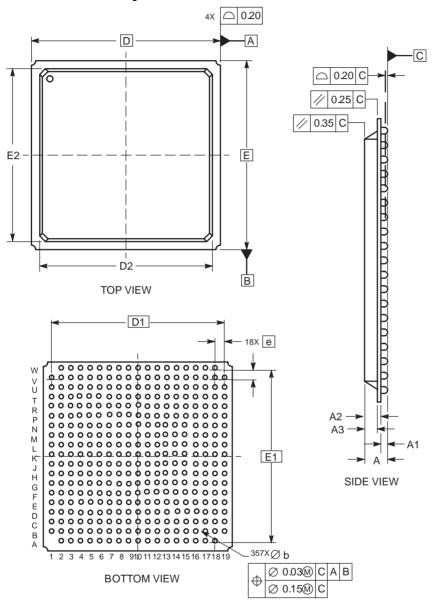

- 357 OMPAC Ball Grid Array Packaging (Plastic)

- 32-bit Address and Data Busses

- Flexible Memory Management

- 4-Kbyte Physical Address, Two-way, Set-associative Data Cache

- 4-Kbyte Physical Address, Two-way, Set-associative Instruction Cache

- Eight-bank Memory Controller

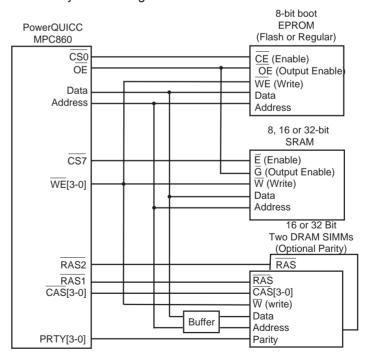

- Glueless Interface to SRAM, DRAM, EPROM, FLASH and Other Peripherals

- Byte Write Enables and Selectable Parity Generation

- 32-bit Address Decodes With Bit Masks

- System Interface Unit

- Clock Synthesizer

- Power Management

- Reset Controller

- PowerPC Decrementer And Time Base

- Real-time Clock Register

- Periodic Interrupt Timer

- Hardware Bus Monitor and Software Watchdog Timer

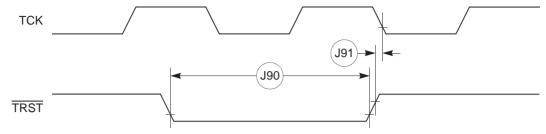

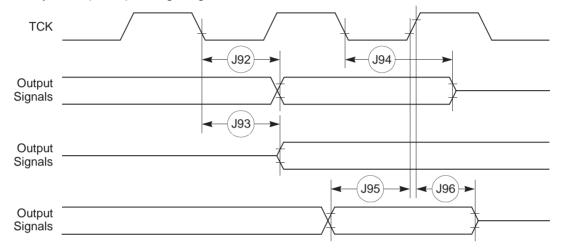

- IEEE 1149.1 JTAG Test Access Port

- Communications Processor Module

- Embedded 32-bit RISC Controller Architecture for Flexible I/O

- Interfaces to PowerPC Core Through On-chip Dual-port Ram And Virtual DMA Channel Controller

- Continuous Mode Transmission And Reception On All Serial Channels

- Serial DMA Channels For Reception And Transmission On All Serial Channels

- I/O registers with Open-drain and Interrupt Capability

- Memory-memory and Memory-I/O Transfers with Virtual DMA Functionality

- Protocols Supported by ROM or Downloadable Microcode and Include, but Limited to, the Digital Portion of:

- Ethernet/IEEE 802.3 CS/CDMA

- HDLC2/SDLC and HDLC bus

- Apple Talk

- Signaling System #7 (RAM Microcode Only)

- Universal Asynchronous Receiver Transmitter (UART)

- Synchronous UART

- Binary Synchronous (BiSync) Communications

- Totally Transparent

- Totally Transparent with CRC

- Profibus (RAM Microcode Option)

- Asynchronous HDLC

- DDCMP

- V.14 (RAM Microcode Option)

- X.21 (RAM Microcode Option)

- V.32bis Datapump Filters

- IrDA Serial Infrared

- Basis Rate ISDN (BRI) in Conjunction with SMC Channels

- Primary Rate ISDN (MH Version Only)

- Four Hardware Serial Communications Controller Channels Supporting the Protocols

- Two Hardware Serial Management Channels

- Management for BRI Devices as General Circuit Interface Controller Multiplexed Channels

- Low-speed UART operation

- Hardware Serial Peripheral Interfaces

- Two-wire Interface (TWI)

- Time-slot Assigner

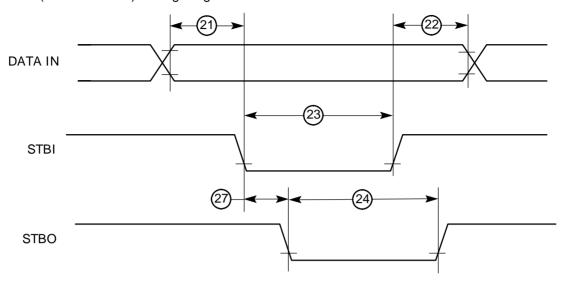

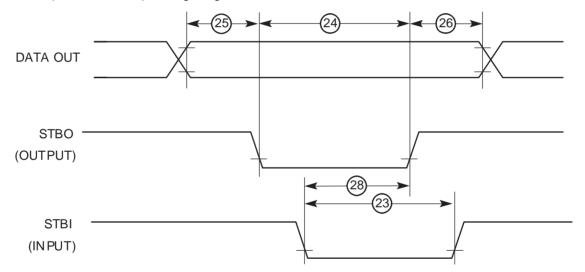

- Port Supports Centronics Interfaces and Chip-to-chip

- Four Independent Baud Rate Generators and Four Input Clock Pins for Supplying Clocks to SMC and SCC Serial Channels

- Four Independent 16-bit timers Which Can Be Interconnected as Two 32-bit Timers

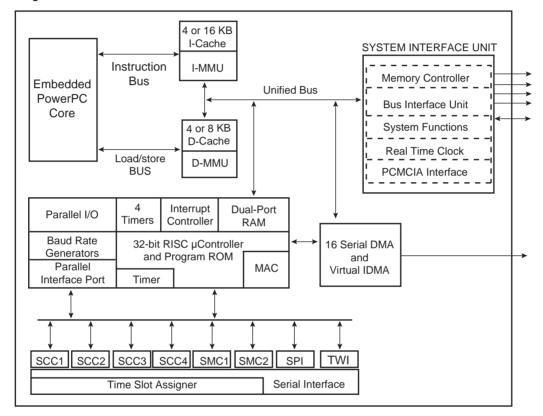

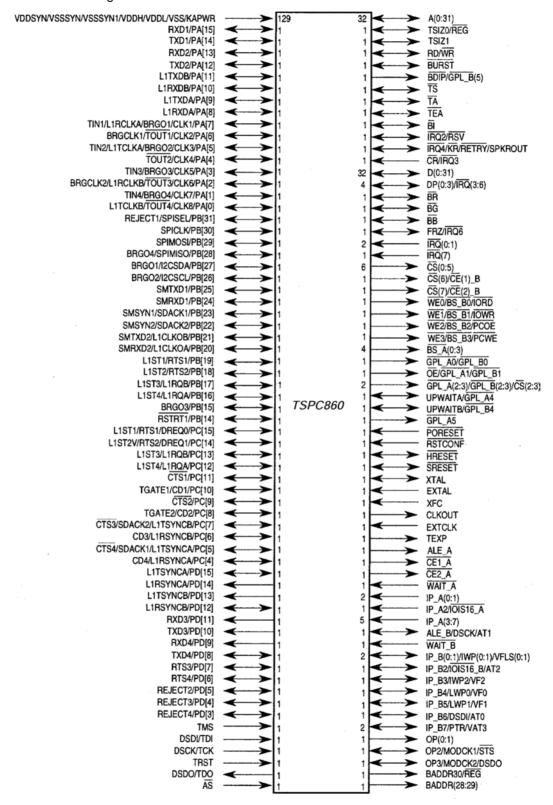

### **Pin Assignment**

#### **Plastic Ball Grid Array**

Figure 2. Pin Assignment: Top View

**Signal Descriptions**

This section describes the signals on the TSPC860.

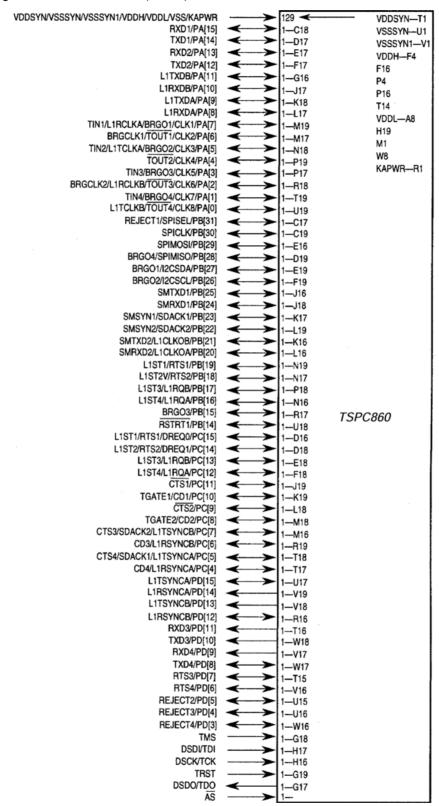

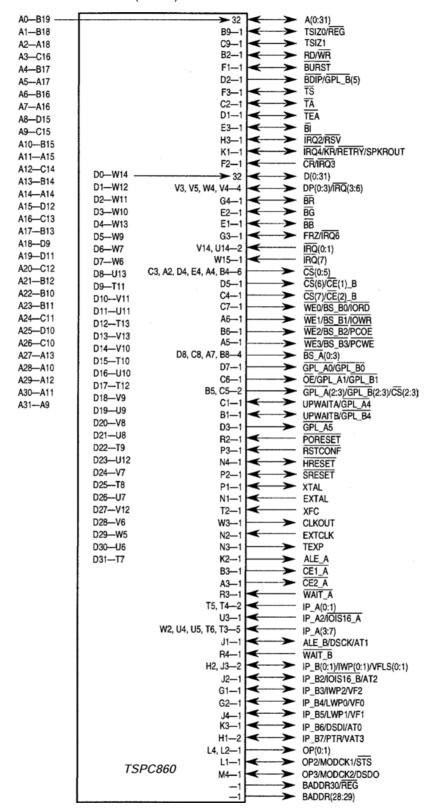

Figure 3. TSPC860 External Signals

Figure 4. TSPC860 Signals and Pin Numbers (Part 1)

Figure 5. TSPC860 Signals and Pin Numbers (Part 2)

## **System Bus Signals**

The TSPC860 system bus consists of all signals that interface with the external bus. Many of these signals perform different functions, depending on how the user assigns them. The following input and output signals are identified by their abbreviation. Each signal's pin number can be found in Figure 4 and Figure 5.

Table 1. Signal Descriptions

| Name           | Reset                                                        | Number          | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|--------------------------------------------------------------|-----------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(0-31)        | Hi-Z                                                         | See<br>Figure 2 | Bidirectional<br>Three-state    | Address Bus — Provides the address for the current bus cycle. A0 is the most-significant signal. The bus is output when an internal master starts a transaction on the external bus. The bus is input when an external master starts a transaction on the bus.                                                                                                                                                                                                                                                                                                |

| TSIZ0<br>REG   | Hi-Z                                                         | В9              | Bidirectional<br>Three-state    | Transfer Size 0 — When accessing a slave in the external bus, used (together with TSIZ1) by the bus master to indicate the number of operand bytes waiting to be transferred in the current bus cycle. TSIZ0 is an input when an external master starts a bus transaction. Register — When an internal master initiates an access to a slave controlled by the PCMCIA interface, REG is output to indicate which space in the PCMCIA card is accessed.                                                                                                        |

| TSIZ1          | Hi-Z                                                         | C9              | Bidirectional<br>Three-state    | Transfer Size 1 — Used (with TSIZ0) by the bus master to indicate the number of operand bytes waiting to be transferred in the current bus cycle. The TSPC860 drives TSIZ1 when it is bus master. TSIZ1 is input when an external master starts a bus transaction.                                                                                                                                                                                                                                                                                            |

| RD/WR          | Hi-Z                                                         | B2              | Bidirectional<br>Three-state    | Read/Write — Driven by the bus master to indicate the direction of the bus's data transfer. A logic one indicates a read from a slave device and a logic zero indicates a write to a slave device.  The TSPC860 drives this signal when it is bus master. Input when an external master initiates a transaction on the bus.                                                                                                                                                                                                                                   |

| BURST          | Hi-Z                                                         | F1              | Bidirectional<br>Three-state    | Burst Transaction — Driven by the bus master to indicate that the current initiated transfer is a burst. The TSPC860 drives this signal when it is bus master. This signal is input when an external master initiates a transaction on the bus.                                                                                                                                                                                                                                                                                                               |

| BDIP<br>GPL_B5 | See Section "Signal States During Hardware Reset" on page 28 | D2              | Bidirectional<br>Three-state    | Burst Data in Progress — When accessing a slave device in the external bus, the master on the bus asserts this signal to indicate that the data beat in front of the current one is the one requested by the master. BDIP is negated before the expected last data beat of the burst transfer.  General-Purpose Line B5-Used by the memory controller when UPMB takes control of the slave access.                                                                                                                                                            |

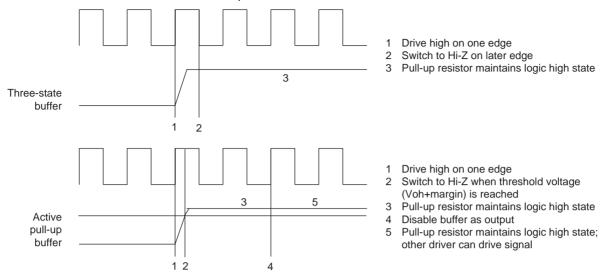

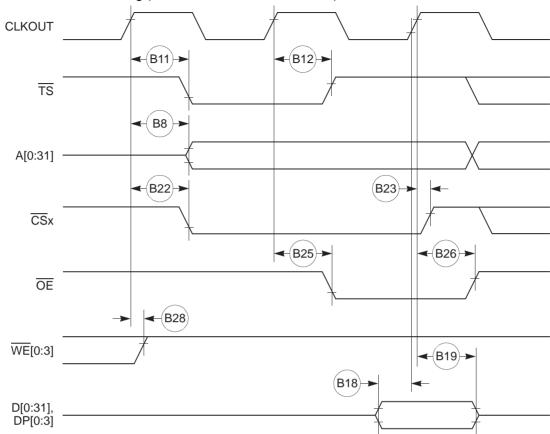

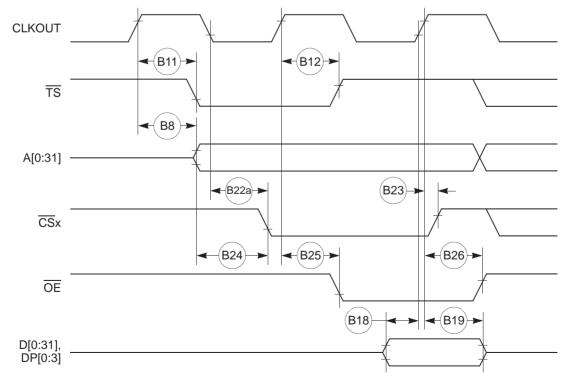

| TS             | Hi-Z                                                         | F3              | Bidirectional<br>Active Pull-up | Transfer Start — Asserted by the bus master to indicate the start of a bus cycle that transfers data to or from a slave device.  Driven by the master only when it has gained the ownership of the bus. Every master should negate this signal before the bus relinquish. To requires the use of an external pull-up resistor.  The TSPC860 samples To when it is not the external bus master to allow the memory controller/PCMCIA interface to control the accessed slave device. It indicates that an external synchronous master initiated a transaction. |

Table 1. Signal Descriptions (Continued)

| Name                        | Reset                                                        | Number | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------|--------------------------------------------------------------|--------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

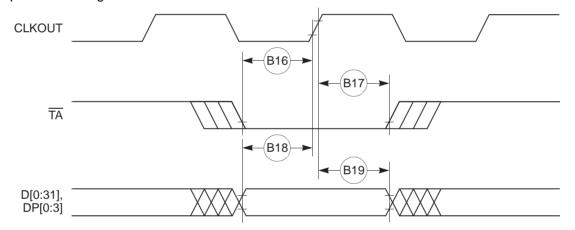

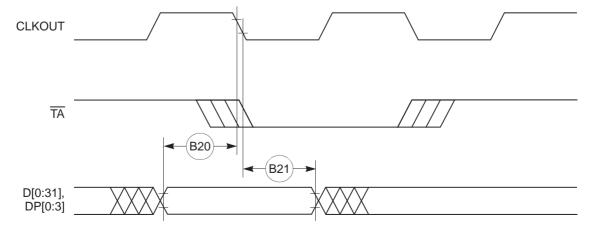

| TA                          | Hi-Z                                                         | C2     | Bidirectional<br>Active Pull-up | Transfer Acknowledge — Indicates that the slave device addressed in the current transaction accepted data sent by the master (write) or has driven the data bus with valid data (read). This is an output when the PCMCIA interface or memory controller controls the transaction. The only exception occurs when the memory controller controls the slave access by means of the GPCM and the corresponding option register is instructed to wait for an external assertion of $\overline{\text{TA}}$ . Every slave device should negate $\overline{\text{TA}}$ after a transaction ends and immediately three-state it to avoid bus contention if a new transfer is initiated addressing other slave devices. $\overline{\text{TA}}$ requires the use of an external pull-up resistor.                                                                   |

| TEA                         | Hi-Z                                                         | D1     | Open-drain                      | Transfer Error Acknowledge — Indicates that a <u>bus</u> error occurred in the current transaction. The TSPC860 asserts <u>TEA</u> when the bus monitor does not detect a <u>bus</u> cycle termination within a reasonable amount of time. Asserting <u>TEA</u> terminates the bus cycle, thus ignoring the state of <u>TA</u> . <u>TEA</u> requires the use of an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| БĪ                          | Hi-Z                                                         | E3     | Bidirectional<br>Active Pull-up | Burst Inhibit — Indicates that the slave device addressed in the current burst transaction cannot support burst transfers. It acts as an output when the PCMCIA interface or the memory controller takes control of the transaction. $\overline{\text{BI}}$ requires the use of an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RSV<br>IRQ2                 | See Section "Signal States During Hardware Reset" on page 28 | Н3     | Bidirectional<br>Three-state    | Reservation — The TSPC860 outputs this three-state signal in conjunction with the address bus to indicate that the core initiated a transfer as a result of a <b>stwcx</b> . or <b>lwarx</b> .  Interrupt Request 2 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| KR/RETRY<br>IRQ4<br>SPKROUT | See Section "Signal States During Hardware Reset" on page 28 | K1     | Bidirectional<br>Three-state    | Kill Reservation — This input is used as a part of the memory reservation protocol, when the TSPC860 initiated a transaction as the result of a <b>stwcx.</b> instruction. Retry — This input is used by a slave device to indicate it cannot accept the transaction. The TSPC860 must relinquish mastership and reinitiate the transaction after winning in the bus arbitration. Interrupt Request 4 – One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core. Note that the interrupt request signal that is sent to the interrupt controller is the logical AND of this line (if defined as $\overline{\text{IRQ4}}$ ) and DP1/ $\overline{\text{IRQ4}}$ (if defined as $\overline{\text{IRQ4}}$ ). SPKROUT — Digital audio wave form output to be driven to the system speaker. |

| CR<br>IRQ3                  | Hi-Z                                                         | F2     | Input                           | Cancel Reservation — This input is used as a part of the storage reservation protocol.  Interrupt Request 3 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core. Note that the interrupt request signal sent to the interrupt controller is the logical AND of CR/IRQ3 (if defined as IRQ3) and DP0/IRQ3 if defined as IRQ3.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 1. Signal Descriptions (Continued)

| Name        | Reset                                             | Number          | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|---------------------------------------------------|-----------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

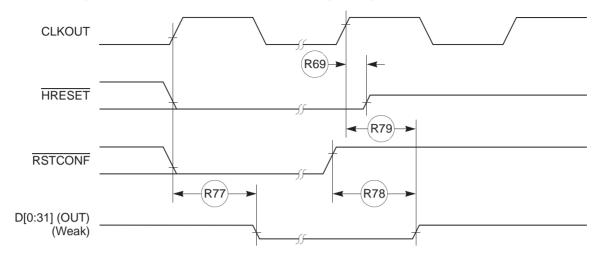

| D(0-31)     | Hi-Z (Pulled<br>Low if<br>RSTCONF<br>pulled down) | See<br>Figure 2 | Bidirectional<br>Three-state | Data Bus — This bidirectional three-state bus provides the general-purpose data path between the TSPC860 and all other devices. The 32-bit data path can be dynamically sized to support 8-, 16-, or 32-bit transfers. D0 is the MSB of the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DP0<br>IRQ3 | Hi-Z                                              | V3              | Bidirectional<br>Three-state | Data Parity 0 — Provides parity generation and checking for D(0-7) for transfers to a slave device initiated by the TSPC860. The parity function can be defined independently for each one of the addressed memory banks (if controlled by the memory controller) and for the rest of the slaves sitting on the external bus. Parity generation and checking is not supported for external masters.  Interrupt Request 3 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core. Note that the interrupt request signal sent to the interrupt controller is the logical AND of DP0/IRQ3 (if defined as IRQ3) and CR/IRQ3 (if defined as IRQ3).   |

| DP1<br>IRQ4 | Hi-Z                                              | V5              | Bidirectional<br>Three-state | Data Parity 1 — Provides parity generation and checking for D(8-15) for transfers to a slave device initiated by the TSPC860. The parity function can be defined independently for each one of the addressed memory banks (if controlled by the memory controller) and for the rest of the slaves on the external bus. Parity generation and checking is not supported for external masters.  Interrupt Request 4 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core. Note that the interrupt request signal sent to the interrupt controller is the logical AND of this line (if defined as IRQ4) and KR/IRQ4/SPKROUT (if defined as IRQ4). |

| DP2<br>IRQ5 | Hi-Z                                              | W4              | Bidirectional<br>Three-state | Data Parity 2 — Provides parity generation and checking for D(16-23) for transfers to a slave device initiated by the TSPC860. The parity function can be defined independently for each one of the addressed memory banks (if controlled by the memory controller) and for the rest of the slaves on the external bus. Parity generation and checking is not supported for external masters.  Interrupt Request 5 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                       |

| DP3<br>IRQ6 | Hi-Z                                              | V4              | Bidirectional<br>Three-state | Data Parity 3 — Provides parity generation and checking for D(24-31) for transfers to a slave device initiated by the TSPC860. The parity function can be defined independently for each one of the addressed memory banks (if controlled by the memory controller) and for the rest of the slaves on the external bus. Parity generation and checking is not supported for external masters.  Interrupt Request 6 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core. Note that the interrupt request signal sent to the interrupt controller is the logical AND of this line (if defined as IRQ6) and the FRZ/IRQ6 (if defined as IRQ6).   |

| BR          | Hi-Z                                              | G4              | Bidirectional                | Bus Request — Asserted low when a possible master is requesting ownership of the bus. When the TSPC860 is configured to work with the internal arbiter, this signal is configured as an input. When the TSPC860 is configured to work with an external arbiter, this signal is configured as an output and asserted every time a new transaction is intended to be initiated (no parking on the bus).                                                                                                                                                                                                                                                                                                                     |

Table 1. Signal Descriptions (Continued)

| Name            | Reset                                                        | Number                       | Type                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|--------------------------------------------------------------|------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BG              | Hi-Z                                                         | E2                           | Bidirectional                   | Bus Grant — Asserted low when the arbiter of the external bus grants the bus to a specific device. When the TSPC860 is configured to work with the internal arbiter, $\overline{BG}$ is configured as an output and asserted every time the external master asserts $\overline{BR}$ and its priority request is higher than any internal sources requiring a bus transfer. However, when the TSPC860 is configured to work with an external arbiter, $\overline{BG}$ is an input. |

| BB              | Hi-Z                                                         | E1                           | Bidirectional<br>Active Pull-up | Bus Busy — Asserted low by a master to show that it owns the bus. The TSPC860 asserts $\overline{BB}$ after the arbiter grants it bus ownership and $\overline{BB}$ is negated.                                                                                                                                                                                                                                                                                                   |

| FRZ<br>IRQ6     | See Section "Signal States During Hardware Reset" on page 28 | G3                           | Bidirectional                   | Freeze — Output asserted to indicate that the core is in debug mode.  Interrupt Request 6 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core. Note that the interrupt request signal sent to the interrupt controller is the logical AND of FRZ/IRQ6 (if defined as IRQ6) and DP3/IRQ6 (if defined as IRQ6).                                                                                         |

| ĪRQ0            | Hi-Z                                                         | V14                          | Input                           | Interrupt Request 0 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                              |

| ĪRQ1            | Hi-Z                                                         | U14                          | Input                           | Interrupt Request 1 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                              |

| ĪRQ7            | Hi-Z                                                         | W15                          | Input                           | Interrupt Request 7 — One of eight external inputs that can request (by means of the internal interrupt controller) a service routine from the core.                                                                                                                                                                                                                                                                                                                              |

| <u>CS</u> (0-5) | High                                                         | C3, A2,<br>D4, E4,<br>A4, B4 | Output                          | Chip Select — These outputs enable peripheral or memory devices at programmed addresses if they are appropriately defined.    CS0 can be configured to be the global chip-select for the boot device.                                                                                                                                                                                                                                                                             |

| CS6<br>CE1_B    | High                                                         | D5                           | Output                          | Chip Select 6 — This output enables a peripheral or memory device at a programmed address if defined appropriately in the BR6 and OR6 in the memory controller.  Card Enable 1 Slot B — This output enables even byte transfers when accesses to the PCMCIA Slot B are handled under the control of the PCMCIA interface.                                                                                                                                                         |

| CS7<br>CE2_B    | High                                                         | C4                           | Output                          | Chip Select 7 — This output enables a peripheral or memory device at a programmed address if defined appropriately in the BR7 and OR7 in the memory controller.  Card Enable 2 Slot B — This output enables odd byte transfers when accesses to the PCMCIA Slot B are handled under the control of the PCMCIA interface.                                                                                                                                                          |

Table 1. Signal Descriptions (Continued)

| Name                 | Reset | Number            | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|-------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WEO<br>BS_BO<br>IORD | High  | C7                | Output | Write Enable 0 — Output asserted when a write access to an external slave controlled by the GPCM is initiated by the TSPC860.  WEO is asserted if D(0-7) contains valid data to be stored by the slave device.  Byte Select 0 on UPMB — Output asserted under control of the UPMB, as programmed by the user. In a read or write transfer, the line is only asserted if D(0-7) contains valid data.  IO Device Read — Output asserted when the TSPC860 starts a read access to a region controlled by the PCMCIA interface. Asserted                                                                |

|                      |       |                   |        | only for accesses to a PC card I/O space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| WE1<br>BS_B1<br>IOWR | High  | A6                | Output | Write Enable 1 — Output asserted when the TSPC860 initiates a write access to an external slave controlled by the GPCM. WE1 is asserted if D(8-15) contains valid data to be stored by the slave device.  Byte Select 1 on UPMB — Output asserted under control of the UPMB, as programmed by the user. In a read or write transfer, the line is only asserted if D(8-15) contains valid data.  I/O Device Write — This output is asserted when the TSPC860 initiates a write access to a region controlled by the PCMCIA interface. IOWR is asserted only if the access is to a PC card I/O space. |

| WE2<br>BS_B2<br>PCOE | High  | В6                | Output | Write Enable 2 — Output asserted when the TSPC860 starts a write access to an external slave controlled by the GPCM. WE2 is asserted if D(16-23) contains valid data to be stored by the slave device.  Byte Select 2 on UPMB — Output asserted under control of the UPMB, as programmed by the user. In a read or write transfer, BS_B2 is asserted only D(16-23) contains valid data.  PCMCIA Output Enable — Output asserted when the TSPC860 initiates a read access to a memory region under the control of the PCMCIA interface.                                                              |

| WE3 BS_B3 PCWE       | High  | A5                | Output | Write Enable 3 — Output asserted when the TSPC860 initiates a write access to an external slave controlled by the GPCM. WE3 is asserted if D(24-31) contains valid data to be stored by the slave device.  Byte Select 3 on UPMB — Output asserted under control of the UPMB, as programmed by the user. In a read or write transfer, BS_B3 is asserted only if D(24-31) contains valid data.  PCMCIA Write Enable — Output asserted when the TSPC860 initiates a write access to a memory region under control of the PCMCIA interface.                                                            |

| BS_A(0-3)            | High  | D8, C8,<br>A7, B8 | Output | Byte Select 0 to 3 on UPMA — Outputs asserted under requirement of the UPMB, as programmed by the user. For read or writes, asserted only if their corresponding data lanes contain valid data:  BS_A0 for D(0-7), BS_A1 for D(8-15), BS_A2 for D(16-23), BS_A3 for D(24-31)                                                                                                                                                                                                                                                                                                                        |

Table 1. Signal Descriptions (Continued)

| Name                                | Reset | Number | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------|-------|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPL_A0<br>GPL_B0                    | High  | D7     | Output        | General-Purpose Line 0 on UPMA — This output reflects the value specified in the UPMA when an external transfer to a slave is controlled by the UPMA.                                                                                                                                                                                                                                |

|                                     |       |        |               | General-Purpose Line 0 on UPMB — This output reflects the value specified in the UPMB when an external transfer to a slave is controlled by the UPMB.                                                                                                                                                                                                                                |

| OE<br>GPL_A1                        | High  | C6     | Output        | Output Enable — Output asserted when the TSPC860 initiates a read access to an external slave controlled by the GPCM.                                                                                                                                                                                                                                                                |

| GPL_B1                              |       |        |               | General-Purpose Line 1 on UPMA — This output reflects the value specified in the UPMA when an external transfer to a slave is controlled by UPMA.                                                                                                                                                                                                                                    |

|                                     |       |        |               | General-Purpose Line 1 on UPMB — This output reflects the value specified in the UPMB when an external transfer to a slave is controlled by UPMB.                                                                                                                                                                                                                                    |

| GPL_A(2-3)<br>GPL_B(2-3)<br>CS(2-3) | High  | B5, C5 | Output        | General-Purpose Line 2 and 3 on UPMA — These outputs reflect the value specified in the UPMA when an external transfer to a slave is controlled by UPMA.                                                                                                                                                                                                                             |

| 33(23)                              |       |        |               | General-Purpose Line 2 and 3 on UPMB — These outputs reflect the value specified in the UPMB when an external transfer to a slave is controlled by UPMB.                                                                                                                                                                                                                             |

|                                     |       |        |               | Chip Select 2 and 3 — These outputs enable peripheral or memory devices at programmed addresses if they are appropriately defined. The double drive capability for $\overline{\text{CS2}}$ and $\overline{\text{CS3}}$ is independently defined for each signal in the SIUMCR.                                                                                                       |

| UPWAITA<br>GPL_A4                   | Hi-Z  | C1     | Bidirectional | User Programmable Machine Wait A — This input is sampled as defined by the user when an access to an external slave is controlled by the UPMA.                                                                                                                                                                                                                                       |

|                                     |       |        |               | General-Purpose Line 4 on UPMA — This output reflects the value specified in the UPMA when an external transfer to a slave is controlled by UPMA.                                                                                                                                                                                                                                    |

| UPWAITB<br>GPL_B4                   | Hi-Z  | B1     | Bidirectional | User Programmable Machine Wait B — This input is sampled as defined by the user when an access to an external slave is controlled by the UPMB.                                                                                                                                                                                                                                       |

|                                     |       |        |               | General-Purpose Line 4 on UPMB — This output reflects the value specified in the UPMB when an external transfer to a slave is controlled by UPMB.                                                                                                                                                                                                                                    |

| GPL_A5                              | High  | D3     | Output        | General-Purpose Line 5 on UPMA — This output reflects the value specified in the UPMA when an external transfer to a slave is controlled by UPMA. This signal can also be controlled by the UPMB.                                                                                                                                                                                    |

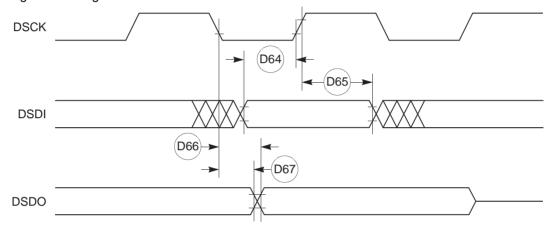

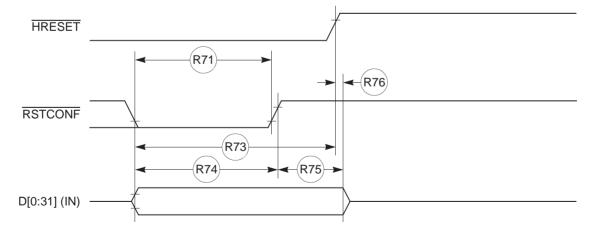

| PORESET                             | Hi-Z  | R2     | Input         | Power on Reset — When asserted, this input causes the TSPC860 to enter the power-on reset state.                                                                                                                                                                                                                                                                                     |

| RSTCONF                             | Hi-Z  | P3     | Input         | Reset Configuration — The TSPC860 samples this input while HRESET is asserted. If RSTCONF is asserted, the configuration mode is sampled in the form of the hard reset configuration word driven on the data bus. When RSTCONF is negated, the TSPC860 uses the default configuration mode. Note that the initial base address of internal registers is determined in this sequence. |

| HRESET                              | Low   | N4     | Open-drain    | Hard Reset — Asserting this open drain signal puts the TSPC860 in hard reset state.                                                                                                                                                                                                                                                                                                  |

Table 1. Signal Descriptions (Continued)

| Name              | Reset                                             | Number                | Туре                        | Description                                                                                                                                                                                                                                                                                                                            |

|-------------------|---------------------------------------------------|-----------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

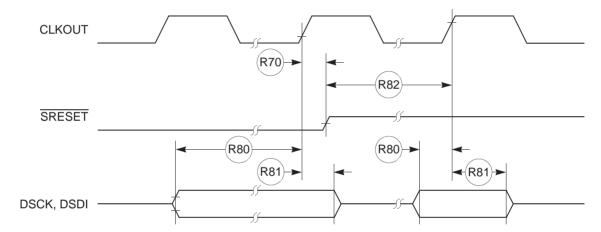

| SRESET            | Low                                               | P2                    | Open-drain                  | Soft Reset — Asserting this open drain line puts the TSPC860 in soft reset state.                                                                                                                                                                                                                                                      |

| XTAL              | Analog<br>Driving                                 | P1                    | Analog<br>Output            | This output is one of the connections to an external crystal for the internal oscillator circuitry.                                                                                                                                                                                                                                    |

| EXTAL             | Hi-Z                                              | N1                    | Analog Input<br>(3.3V only) | This line is one of the connections to an external crystal for the internal oscillator circuitry.                                                                                                                                                                                                                                      |

| XFC               | Analog<br>Driving                                 | T2                    | Analog Input                | External Filter Capacitance — This input is the connection pin for an external capacitor filter for the PLL circuitry.                                                                                                                                                                                                                 |

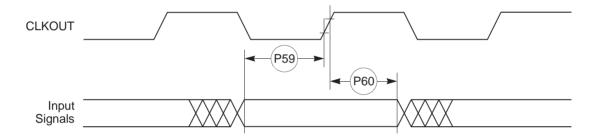

| CLKOUT            | High until<br>SPLL locked,<br>then<br>oscillating | W3                    | Output                      | Clock Out — This output is the clock system frequency.                                                                                                                                                                                                                                                                                 |

| EXTCLK            | Hi-Z                                              | N2                    | Input (3.3V<br>only)        | External Clock — This input is the external input clock from an external source.                                                                                                                                                                                                                                                       |

| TEXP              | High                                              | N3                    | Output                      | Timer Expired — This output reflects the status of PLPRCR[TEXPS].                                                                                                                                                                                                                                                                      |

| ALE_A             | Low                                               | K2                    | Output                      | Address Latch Enable A — This output is asserted when TSPC860 initiates an access to a region under the control of the PCMCIA interface to socket A.                                                                                                                                                                                   |

| CE1_A             | High                                              | В3                    | Output                      | Card Enable 1 Slot A — This output enables even byte transfers when accesses to PCMCIA Slot A are handled under the control of the PCMCIA interface.                                                                                                                                                                                   |

| CE2_A             | High                                              | А3                    | Output                      | Card Enable 2 Slot A — This output enables odd byte transfers when accesses to PCMCIA Slot A are handled under the control of the PCMCIA interface.                                                                                                                                                                                    |

| WAIT_A            | Hi-Z                                              | R3                    | Input                       | Wait Slot A — This input, if asserted low, causes a delay in the completion of a transaction on the PCMCIA controlled Slot A.                                                                                                                                                                                                          |

| WAIT_B            | Hi-Z                                              | R4                    | Input                       | Wait Slot B — This input, if asserted low, causes a delay in the completion of a transaction on the PCMCIA controlled Slot B.                                                                                                                                                                                                          |

| IP_A(0-1)         | Hi-Z                                              | T5, T4                | Input                       | Input Port A 0-1 — The TSPC860 monitors these inputs that are reflected in the PIPR and PSCR of the PCMCIA interface.                                                                                                                                                                                                                  |

| IP_A2<br>IOIS16_A | Hi-Z                                              | U3                    | Input                       | Input Port A 2 — The TSPC860 monitors these inputs; its value and changes are reported in the PIPR and PSCR of the PCMCIA interface.  I/O Device A is 16-Bits Ports Size — The TSPC860 monitors this input when a transaction under the control of the PCMCIA interface is initiated to an I/O region in socket A of the PCMCIA space. |

| IP_A(3-7)         | Hi-Z                                              | W2, U4,<br>U5, T6, T3 | Input                       | Input Port A 3-7 — The TSPC860 monitors these inputs; their values and changes are reported in the PIPR and PSCR of the PCMCIA interface.                                                                                                                                                                                              |

Table 1. Signal Descriptions (Continued)

| Name                               | Reset                                                                       | Number | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------|-----------------------------------------------------------------------------|--------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

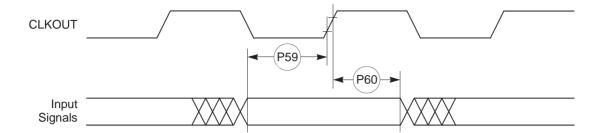

| ALE_B<br>DSCK/AT1                  | See Section "Signal States During Hardware Reset" on page 28                | J1     | Bidirectional<br>Three-state | Address Latch Enable B — This output is asserted when the TSPC860 initiates an access to a region under the control of the PCMCIA socket B interface.  Development Serial Clock — This input is the clock for the debug port interface.  Address Type 1 — The TSPC860 drives this bidirectional three-state line when it initiates a transaction on the external bus. When the transaction is initiated by the core, it indicates if the transfer is for user or supervisor state. This signal is not used for transactions initiated by external masters.                                                    |

| IP_B(0-1)<br>IWP(0-1)<br>VFLS(0-1) | See Section<br>"Signal<br>States During<br>Hardware<br>Reset" on<br>page 28 | H2, J3 | Bidirectional                | Input Port B 0-1 — The TSPC860 senses these inputs; their values and changes are reported in the PIPR and PSCR of the PCMCIA interface.  Instruction Watchpoint 0-1 — These outputs report the detection of an instruction watchpoint in the program flow executed by the core. Visible History Buffer Flushes Status — The TSPC860 outputs VFLS(0-1) when program instruction flow tracking is required. They report the number of instructions flushed from the history buffer in the core.                                                                                                                 |

| IP_B2<br>IOIS16_B<br>AT2           | Hi-Z                                                                        | J2     | Bidirectional<br>Three-state | Input Port B 2 — The TSPC860 senses this input; its value and changes are reported in the PIPR and PSCR of the PCMCIA interface.  I/O Device B is 16- Bits Port Size — The TSPC860 monitors this input when a PCMCIA interface transaction is initiated to an I/O region in socket B in the PCMCIA space.  Address Type 2 — The TSPC860 drives this bidirectional three-state signal when it initiates a transaction on the external bus. If the core initiates the transaction, it indicates if the transfer is instruction or data. This signal is not used for transactions initiated by external masters. |

| IP_B3<br>IWP2<br>VF2               | See Section "Signal States During Hardware Reset" on page 28                | G1     | Bidirectional                | Input Port B 3 — The TSPC860 monitors this input; its value and changes are reported in the PIPR and PSCR of the PCMCIA interface.  Instruction Watchpoint 2 — This output reports the detection of an instruction watchpoint in the program flow executed by the core.  Visible Instruction Queue Flush Status — The TSPC860 outputs VF2 with VF0/VF1 when instruction flow tracking is required. VFn reports the number of instructions flushed from the instruction queue in the core.                                                                                                                     |

| IP_B4<br>LWP0<br>VF0               | Hi-Z                                                                        | G2     | Bidirectional                | Input Port B 4 — The TSPC860 monitors this input; its value and changes are reported in the PIPR and PSCR of the PCMCIA interface.  Load/Store Watchpoint 0 — This output reports the detection of a data watchpoint in the program flow executed by the core.  Visible Instruction Queue Flushes Status — The TSPC860 outputs VF0 with VF1/VF2 when instruction flow tracking is required. VFn reports the number of instructions flushed from the instruction queue in the core.                                                                                                                            |

Table 1. Signal Descriptions (Continued)

| Name                  | Reset | Number | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|-------|--------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP_B5<br>LWP1<br>VF1  | Hi-Z  | J4     | Bidirectional                | Input Port B 5 — The TSPC860 monitors this input; its value and changes are reported in the PIPR and PSCR of the PCMCIA interface.  Load/Store Watchpoint 1 — This output reports the detection of a data watchpoint in the program flow executed by the core.  Visible Instruction Queue Flushes Status — The TSPC860 outputs VF1 with VF0 and VF2 when instruction flow tracking is required. VFn reports the number of instructions flushed from the instruction queue in the core.                                                                                                                                              |

| IP_B6<br>DSDI<br>AT0  | Hi-Z  | КЗ     | Bidirectional<br>Three-state | Input Port B 6 — The TSPC860 senses this input and its value and changes are reported in the PIPR and PSCR of the PCMCIA interface.  Development Serial Data Input — Data input for the debug port interface.  Address Type 0 — The TSPC860 drives this bidirectional three-state line when it initiates a transaction on the external bus. If high (1), the transaction is the CPM. If low (0), the transaction initiator is the CPU. This signal is not used for transactions initiated by external masters.                                                                                                                      |

| IP_B7<br>PTR<br>AT3   | Hi-Z  | H1     | Bidirectional<br>Three-state | Input Port B 7 — The TSPC860 monitors this input; its value and changes are reported in the PIPR and PSCR of the PCMCIA interface.  Program Trace — To allow program flow tracking, the TSPC860 asserts this output to indicate an instruction fetch is taking place.  Address Type 3 — The TSPC860 drives the bidirectional three-state signal when it starts a transaction on the external bus. When the core initiates a transfer, AT3 indicates whether it is a reservation for a data transfer or a program trace indication for an instruction fetch. This signal is not used for transactions initiated by external masters. |

| OP(0-1)               | Low   | L4, L2 | Output                       | Output Port 0-1 — The TSPC860 generates these outputs as a result of a write to the PGCRA register in the PCMCIA interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OP2<br>MODCK1<br>STS  | Hi-Z  | L1     | Bidirectional                | Output Port 2 — This output is generated by the TSPC860 as a result of a write to the PGCRB register in the PCMCIA interface.  Mode Clock 1 — Input sampled when PORESET is negated to configure PLL/clock mode.  Special Transfer Start — The TSPC860 drives this output to indicate the start of an external bus transfer or of an internal transaction in show-cycle mode.                                                                                                                                                                                                                                                       |

| OP3<br>MODCK2<br>DSDO | Hi-Z  | M4     | Bidirectional                | Output Port 3 — This output is generated by the TSPC860 as a result of a write to the PGCRB register in the PCMCIA interface.  Mode Clock 2 — This input is sampled at the PORESET negation to configure the PLL/clock mode of operation.  Development Serial Data Output — Output data from the debug port interface.                                                                                                                                                                                                                                                                                                              |

Table 1. Signal Descriptions (Continued)

| Name             | Reset | Number   | Туре                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-------|----------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BADDR30<br>REG   | Hi-Z  | K4       | Output                                     | Burst Address 30 — This output duplicates the value of A30 when the following is true:  • An internal master in the TSPC860 initiates a transaction on the external bus.  • An asynchronous external master initiates a transaction.  • A synchronous external master initiates a single beat transaction. The memory controller uses BADDR30 to increment the address lines that connect to memory devices when a synchronous external master or an internal master initiates a burst transfer. Register — When an internal master initiates an access to a slave under control of the PCMCIA interface, this signal duplicates the value of TSIZO/REG. When an external master initiates an access, REG is output by the PCMCIA interface (if it must handle the transfer) to indicate the space in the PCMCIA card being accessed. |

| BADDR(28-<br>29) | Hi-Z  | M3<br>M2 | Output                                     | Burst Address — Outputs that duplicate A(28-29) values when one of the following occurs:  • An internal master in the TSPC860 initiates a transaction on the external bus.  • An asynchronous external master initiates a transaction.  • A synchronous external master initiates a single beat transaction.  The memory controller uses these signals to increment the address lines that connect to memory devices when a synchronous external or internal master starts a burst transfer.                                                                                                                                                                                                                                                                                                                                          |

| ĀS               | Hi-Z  | L3       | Input                                      | Address Strobe — Input driven by an external asynchronous master to indicate a valid address on A(0-31). The TSPC860 memory controller synchronizes $\overline{\text{AS}}$ and controls the memory device addressed under its control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PA[15]<br>RXD1   | Hi-Z  | C18      | Bidirectional                              | General-Purpose I/O Port A Bit 15 — Bit 15 of the general-purpose I/O port A.  RXD1 — Receive data input for SCC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PA[14]<br>TXD1   |       | D17      | Bidirectional<br>(Optional:<br>Open-drain) | General-Purpose I/O Port A Bit 14 — Bit 14 of the general-purpose I/O port A.  TXD1 — Transmit data output for SCC1. TXD1 has an open-drain capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PA[13]<br>RXD2   |       | E17      | Bidirectional                              | General-Purpose I/O Port A Bit 13 — Bit 13 of the general-purpose I/O port A.  RXD2 — Receive data input for SCC2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PA[12]<br>TXD2   |       | F17      | Bidirectional<br>(Optional:<br>Open-drain) | General-Purpose I/O Port A Bit 12 — Bit 12 of the general-purpose I/O port A.  TXD2 — Transmit data output for SCC2. TXD2 has an open-drain capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PA[11]<br>L1TXDB |       | G16      | Bidirectional<br>(Optional:<br>Open-drain) | General-Purpose I/O Port A Bit 11 — Bit 11 of the general-purpose I/O port A.  L1TXDB — Transmit data output for the serial interface TDM port B. L1TXDB has an open-drain capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PA[10]<br>L1RXDB |       | J17      | Bidirectional                              | General-Purpose I/O Port A Bit 10 — Bit 10 of the general-purpose I/O port A.  L1RXDB — Receive data input for the serial interface TDM port B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 1. Signal Descriptions (Continued)

| Name                                         | Reset | Number | Туре                                       | Description                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------|-------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA[9]<br>L1TXDA                              |       | K18    | Bidirectional<br>(Optional:<br>Open-drain) | General-Purpose I/O Port A Bit 11 — Bit 9 of the general-purpose I/O port A.  L1TXDA — Transmit data output for the serial interface TDM port A.  L1TXDA has an open-drain capability.                                                                                                                         |

| PA[8]<br>L1RXDA                              |       | L17    | Bidirectional                              | General-Purpose I/O Port A Bit 8 — Bit 8 of the general-purpose I/O port A.  L1RXDA — Receive data input for the serial interface TDM port A.                                                                                                                                                                  |

| PA[7]<br>CLK1<br>TIN1<br>L1RCLKA<br>BRGO1    |       | M19    | Bidirectional                              | General-Purpose I/O Port A Bit 7 — Bit 7 of the general-purpose I/O port A.  CLK1 — One of eight clock inputs that can be used to clock SCCs and SMCs.  TIN1 — Timer 1 external clock.  L1RCLKA — Receive clock for the serial interface TDM port A.  BRGO1 — Output clock of BRG1.                            |

| PA[6]<br>CLK2<br>TOUT1<br>BRGCLK1            |       | M17    | Bidirectional                              | General-Purpose I/O Port A Bit 6 — Bit 6 of the general-purpose I/O port A.  CLK2 — One of eight clock inputs that can be used to clock SCCs and SMCs.  TOUT1 — Timer 1 output.  BRGCLK1 — One of two external clock inputs of the BRGs.                                                                       |

| PA[5]<br>CLK3<br>TIN2<br>L1TCLKA<br>BRGO2    |       | N18    | Bidirectional                              | General-Purpose I/O Port A Bit 5 — Bit 5 of the general-purpose I/O port A.  CLK3 — One of eight clock inputs that can be used to clock SCCs and SMCs.  TIN2 — Timer 2 external clock input.  L1TCLKA — Transmit clock for the serial interface TDM port A.  BRGO2 — Output clock of BRG2.                     |