### **General Description**

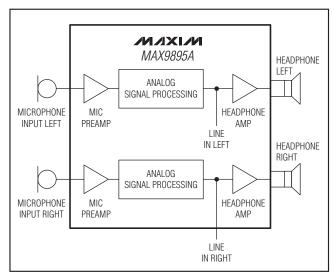

The MAX9895A is a complete audio subsystem for active noise-cancelling (ANC) stereo headsets. The device features three stages for each right and left channel. A microphone preamplifier, an analog sound processing block, and a headphone amplifier combine to create a simple and very flexible active noise-canceling system.

The MAX9895A features a feed-forward architecture. where outside microphones sense the ambient noise and on-board analog sound processing generates the compensation signal needed for noise reduction. This further supports the mechanical isolation of the headset by attenuating sound that leaks through the mechanics of the headphone.

The microphone preamplifiers feature programmable gain, allowing alignment of the microphone and driver tolerances and left-right channel matching. The headphone amplifiers are output capacitorless and can deliver 33mW into a  $16\Omega$  transducer.

The MAX9895A has three modes of operation: ANC on, PTL, and ANC off. The ANC-on mode demonstrates the noise-canceling performance of the device. PTL (pushto-listen) mode sends the microphone signals directly to the headphones to temporarily listen to the surroundings. ANC off disables noise-canceling, but allows use of the headphone amplifiers during music playback.

The MAX9895A is available in a space-saving WLP or TQFN package and is specified over the -40°C to +85°C extended temperature range.

### **Applications**

Noise-Cancelling Headphones/Headsets Headsets for Mobile Communication Mobile Phones Portable Gaming Devices E-Books

### **Features**

- ♦ 2.7V to 4.5V Operation

- **♦ Low Headphone Amplifier Noise**

- **♦ Low-Noise Microphone Preamplifiers with 2.2V Bias**

- ♦ Stereo 33mW into 16Ω Capacitorless Headphone **Amplifiers**

- ♦ Microphone Output Path Available for Speech **Transmission**

- ♦ Adjustable Microphone Gain by I<sup>2</sup>C Interface or **External Resistors**

- **♦ Low External Component Count**

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE | GAIN<br>(V/V) |

|--------------|----------------|-----------------|---------------|

| MAX9895AEWX+ | -40°C to +85°C | 36 WLP          | 1             |

| MAX9895AETL+ | -40°C to +85°C | 40 TQFN-EP*     | 1             |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### Simplified Block Diagram

Pin Configurations appear at end of data sheet.

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND                             | 0.3V to +6V        |

|----------------------------------------------------|--------------------|

| PVDD to PGND                                       | 0.3V to +6V        |

| PVDD to V <sub>DD</sub>                            | 0.1V to +0.1V      |

| CPVDD to PVDD                                      | Internally shorted |

| PGND to GND                                        | 0.1V to +0.1V      |

| SDA, SCL                                           | 0.3V to +6V        |

| LINEIN                                             | 0.3V to +6V        |

| Any Other Pin                                      |                    |

| Duration of Short Circuit Between HPOUT_           | , ,                |

| and GND                                            | Continuous         |

| <b>Duration of Short Circuit Between MICBIAS</b>   | }                  |

| and VDD, GND                                       | Continuous         |

| Duration of Short Circuit Between V <sub>MID</sub> |                    |

| and V <sub>DD</sub> , GND                          | Continuous         |

| Continuous Current into HPOUT                  | 200mA       |

|------------------------------------------------|-------------|

| Continuous Input Current (all other pins)      | ±20mA       |

| Continuous Power Dissipation ( $T_A = +70$ °C) |             |

| 36-Bump, 0.4mm-Pitch WLP Single-Layer Board    |             |

| (derate 17mW/°C above +70°C)                   | 1360mW      |

| Maximum Current per Bump (10k hrs at +120°C)   | 1.7A        |

| TQFN Package (derate 22mW/°C above +70°C)      | 1777mW      |

| ESD Protection, Human Body Model               | ±2kV        |

| Operating Temperature Range40°                 | °C to +85°C |

| Junction Temperature                           | +150°C      |

| Storage Temperature Range65°C                  | C to +150°C |

|                                                |             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{PVDD} = V_{CPVDD} = 3.3V, R_L = \infty, C_{VDD} = 10\mu F$  connected between  $V_{DD}$  and PGND,  $C_{BIAS} = 1\mu F$  connected between  $V_{BIAS}$  and GND,  $C_{FLY} = 1\mu F$  connected between C1P and C1N.  $C_{HOLD} = 1\mu F$  connected between  $V_{MID}$  and PGND,  $R_{PREIN} = 10k\Omega$ ,  $R_{PREFB} = 50k\Omega$ ,  $R_{MICBIAS} = 3.3k\Omega$ , MIC signal gain in ANC mode ANC\_GAIN = -11.5dB, MIC signal gain in PTL mode PTL\_GAIN = -5.5dB,  $V_{GAIN} = +1V/V$ ,  $T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note1)

| PARAMETER                             | SYMBOL            | CONDITIONS                                                          |      | TYP   | MAX  | UNITS |  |

|---------------------------------------|-------------------|---------------------------------------------------------------------|------|-------|------|-------|--|

| GENERAL                               |                   |                                                                     |      |       |      |       |  |

|                                       | V <sub>DD</sub>   |                                                                     |      |       |      |       |  |

| Supply Voltage Range                  | PVDD              | Inferred by PSRR test                                               | 2.7  | 3.3   | 4.5  | V     |  |

|                                       | CPVDD             |                                                                     |      |       |      |       |  |

|                                       |                   | ANC = on                                                            |      | 3.4   | 4.6  |       |  |

| Quiescent Supply Current              | I <sub>DD</sub>   | ANC = off, PTL = off                                                |      | 2.5   | 3.4  | mA    |  |

|                                       |                   | PTL = on                                                            |      | 3.4   | 4.6  |       |  |

| Shutdown Supply Current               | ISHDN             | $I^2C$ mode, $T_A = +25^{\circ}C$                                   |      |       | 12   | μΑ    |  |

| Internal Reference                    | V <sub>BIAS</sub> | Voltage on V <sub>BIAS</sub>                                        | 1.25 | 1.3   | 1.35 | V     |  |

| Charles Time a                        |                   | Input from LINEIN_                                                  |      | 37    |      |       |  |

| Startup Time                          | ton               | Input from MICIN_                                                   |      | 390   |      | ms    |  |

| Undervoltage Lockout                  | UVLO              | Falling threshold                                                   | 2.27 |       | 2.65 | V     |  |

| HEADPHONE OUTPUTS                     |                   |                                                                     |      |       |      |       |  |

| Line Input Resistance                 | RIN               | MAX9895A                                                            | 7    | 10    | 14   | kΩ    |  |

| Output Offset Voltage                 | Vos               | $T_A = +25^{\circ}C$                                                |      | 0.3   | ±3   | mV    |  |

| Total Harmonic Distortion plus        | THD+N             | $R_L = 32\Omega$ , $P_{OUT} = 10$ mW, $f = 1$ kHz from LINEIN_      |      | 0.002 |      | %     |  |

| Noise                                 | I HD+N            | $R_L = 16\Omega$ , $P_{OUT} = 10$ mW,<br>f = 1kHz from LINEIN_      |      | 0.002 |      |       |  |

| Barrar Organia Bairatian But          |                   | $V_{DD} = 2.5V \text{ to } 4.5V, T_A = +25^{\circ}C$                | 60   | 70    |      |       |  |

| Power-Supply Rejection Ratio (Note 2) | PSRR              | $f \le 1 \text{kHz}$ , $V_{\text{IN}} = 200 \text{mV}_{\text{P-P}}$ |      | 65    |      | dB    |  |

| (14010 2)                             |                   | $f = 10kHz$ , $V_{IN} = 200mV_{P-P}$                                |      | 55    |      |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{PVDD} = V_{CPVDD} = 3.3V, R_L = \infty, C_{VDD} = 10\mu F$  connected between  $V_{DD}$  and PGND,  $C_{BIAS} = 1\mu F$  connected between  $V_{BIAS}$  and GND,  $C_{FLY} = 1\mu F$  connected between C1P and C1N.  $C_{HOLD} = 1\mu F$  connected between  $V_{MID}$  and PGND,  $C_{RPREIN} = 10k\Omega$ ,  $C_{RPREFB} = 50k\Omega$ ,  $C_{RMICBIAS} = 3.3k\Omega$ , MIC signal gain in ANC mode ANC\_GAIN = -11.5dB, MIC signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ ,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode PTL\_GAIN = -5.5dB,  $C_{RMICBIAS} = 10k\Omega$ , which is a signal gain in PTL mode

| PARAMETER                           | SYMBOL            |                                    | CONDITIONS                                                                                       | MIN   | TYP   | MAX   | UNITS             |

|-------------------------------------|-------------------|------------------------------------|--------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

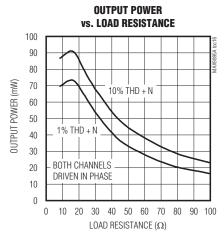

| Output Power                        | Роит              | $R_L = 16\Omega$ , (Note 3)        | THD+N = 1%, T <sub>A</sub> = +25°C                                                               | 20    | 38    |       | mW                |

|                                     |                   | $R_L = 32\Omega$ ,                 | THD+N = 1%, T <sub>A</sub> = +25°C                                                               |       | 26    |       |                   |

|                                     |                   | ANC = off,<br>BW = 20Hz            | -                                                                                                |       | 9     |       |                   |

| Output Noise Voltage                | V <sub>ON</sub>   | ANC = off,<br>A-weighted           |                                                                                                  |       | 6     |       | μV <sub>RMS</sub> |

|                                     |                   | ANC = on,                          | A-weighted                                                                                       |       | 6.5   |       |                   |

| Slew Rate                           | SR                |                                    |                                                                                                  |       | 0.2   |       | V/µs              |

| Maximum Capacitive Load             | CMAXLOAD          |                                    | ed oscillations<br>ce between HPOUT_ and V <sub>MID</sub> )                                      |       | 100   |       | рF                |

| Click-and-Pop Level                 | KCP               | Turn on                            | R <sub>L</sub> = 32Ω, peak voltage,<br>A-weighted, 32 samples/sec,                               |       | -73   |       | dBV               |

| ·                                   |                   | Turn off                           | $T_A = +25^{\circ}C \text{ (Note 4)}$                                                            |       | -72   |       |                   |

| _                                   |                   | f = 1kHz, F                        |                                                                                                  | 57    |       |       |                   |

| Crosstalk                           |                   | WLP                                |                                                                                                  |       | 70    |       | dB                |

| MICROPHONE INPUTS                   | •                 | •                                  |                                                                                                  |       |       |       | •                 |

| Preamplifier Feedback<br>Resistance | RPREFB            | External                           |                                                                                                  | 10    |       | 100   | kΩ                |

| Preamplifier Input Resistance       | RPREIN            | External                           |                                                                                                  | 1     |       | 10    | kΩ                |

| Input Bias Current                  | I <sub>BIAS</sub> | Measured                           | at MICIN, T <sub>A</sub> = +25°C                                                                 |       | 1     | 10    | nA                |

| Microphone Input Noise Voltage      | eN                | BW = 20Hz<br>measured              | z to 20kHz<br>at MICOUT_                                                                         |       | 6     |       | μV                |

| Minimum ANC Gain                    | ANCG_MIN          |                                    |                                                                                                  | -18.0 | -17.5 | -17.0 | dB                |

| Maximum ANC Gain                    | ANCG_MAX          | MICOLIT                            | a LIDOLIT                                                                                        | -6.0  | -5.5  | -5.0  | dB                |

| Minimum PTL Gain                    | PTLG_MIN          | MICOUI_1                           | o HPOUT_, measured at DC                                                                         | -12.0 | -11.5 | -11.0 | dB                |

| Maximum PTL Gain                    | PTLG_MAX          |                                    |                                                                                                  | 0     | 0.5   | 1     | dB                |

| ANC/PTL Gain Stepsize               | AG_STEP           | MICOUT_t                           | o HPOUT_, measured at DC                                                                         |       | 0.5   |       | dB                |

| OPA Offset                          |                   | Measured to V <sub>BIAS</sub>      | -30                                                                                              |       | +30   | mV    |                   |

| Maximum Capacitive Load             | CMAXLOAD          | Allowed ca<br>and all sign<br>SPC3 |                                                                                                  | 15    |       | pF    |                   |

| Dynamic Range                       | MICDYN            | 0                                  | I internal and external nodes of<br>er, signal processing, and filter<br>of to V <sub>BIAS</sub> |       | ±1    |       | V                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{PVDD} = V_{CPVDD} = 3.3V, R_L = \infty, C_{VDD} = 10\mu F$  connected between  $V_{DD}$  and PGND,  $C_{BIAS} = 1\mu F$  connected between  $V_{BIAS}$  and GND,  $C_{FLY} = 1\mu F$  connected between C1P and C1N.  $C_{HOLD} = 1\mu F$  connected between  $V_{MID}$  and PGND,  $R_{PREIN} = 10k\Omega$ ,  $R_{PREFB} = 50k\Omega$ ,  $R_{MICBIAS} = 3.3k\Omega$ , MIC signal gain in ANC mode ANC\_GAIN = -11.5dB, MIC signal gain in PTL mode PTL\_GAIN = -5.5dB,  $V_{GAIN} = +1V/V$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note1)

| PARAMETER                                       | SYMBOL                      | CONDITIONS                                                               | MIN | TYP      | MAX | UNITS                                 |

|-------------------------------------------------|-----------------------------|--------------------------------------------------------------------------|-----|----------|-----|---------------------------------------|

| Maximum Output Current                          | lout                        | Current capability of preamplifier, signal processing, and filter output |     | ±500     |     | μΑ                                    |

| PTL Attenuation                                 |                             | Attenuation from LINEIN_ to HPOUT_ in PTL mode                           |     | 40       |     | dB                                    |

| MICROPHONE BIAS (MICBIAS F                      | Pin)                        |                                                                          |     |          |     |                                       |

| MIC Bias Voltage                                | VMICBIAS                    | V <sub>DD</sub> = 3.3V; 100μA < I <sub>MICBIAS</sub> < 1mA               | 2.1 | 2.2      | 2.3 | V                                     |

| MIC Bias Current Limit                          | IMICLM                      |                                                                          |     | 35       |     | mA                                    |

| Maximum Capacitive Load                         | CMAXLOAD                    |                                                                          |     | 100      |     | рF                                    |

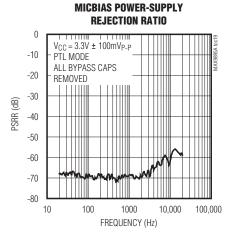

| MICBIAS PSRR                                    | MB_PSRR                     | V <sub>DD</sub> from 2.7V to 4.5V<br>f = 20kHz                           | 55  | 62<br>60 |     | dB                                    |

| MICBIAS Noise                                   | MB_N                        |                                                                          |     | 6        |     | μV                                    |

| CHARGE PUMP                                     |                             | 1                                                                        |     |          |     | · · · · · · · · · · · · · · · · · · · |

| Charge-Pump Frequency                           | fosc                        |                                                                          | 225 | 250      | 275 | kHz                                   |

| V <sub>MID</sub> Output Resistance              | R <sub>VMID</sub>           |                                                                          |     | 4        |     | Ω                                     |

| DIGITAL INPUT SDA (SCL Tied                     | to GND: I <sup>2</sup> C In | terface Disabled)                                                        | •   |          |     | •                                     |

| Input Leakage                                   | IL                          | $V_{SDA} = 0V \text{ to } 3.3V$ $T_A = +25^{\circ}C$                     |     |          | ±16 | μΑ                                    |

| Input Voltage High                              | VIH                         |                                                                          | 1.8 |          |     | V                                     |

| Input Voltage Low                               | V <sub>IL</sub>             |                                                                          |     |          | 0.8 | V                                     |

| SCL/SDA (I <sup>2</sup> C Interface Enabled     | )                           |                                                                          | •   |          |     | •                                     |

| Input Voltage High                              | VIH                         | 1.8V CMOS compatibility                                                  | 1.4 |          |     | V                                     |

| Input Voltage Low                               | VIL                         | 1.8V CMOS compatibility                                                  |     |          | 0.4 | V                                     |

| Input Hysteresis                                | VIHIST                      |                                                                          |     | 0.2      |     | V                                     |

| Input High Leakage Current                      | lін                         | $V_{IN} = 3V; T_A = +25^{\circ}C$                                        |     |          | ±1  | μΑ                                    |

| Input Low Leakage Current                       | IIL                         | $V_{IN} = 0$ ; $T_A = +25^{\circ}C$                                      |     |          | ±1  | μΑ                                    |

| Input Capacitance                               | CIN                         |                                                                          |     | 10       |     | рF                                    |

| Output Voltage Low                              | VoL                         | $I_{OL} = 3mA; T_A = +25$ °C                                             |     |          | 0.4 | V                                     |

| I <sup>2</sup> C INTERFACE                      |                             |                                                                          |     |          |     |                                       |

| Serial-Clock Frequency                          | fscl                        |                                                                          |     |          | 400 | kHz                                   |

| Bus Free Time Between STOP and START Conditions | tBUF                        |                                                                          | 1.3 |          |     | μs                                    |

| Hold Time (REPEATED) START<br>Condition         | tHD:STA                     |                                                                          | 0.6 |          |     | μs                                    |

| Setup Time for a REPEATED START Condition       | tsu:sta                     |                                                                          | 0.6 |          |     | μs                                    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{PVDD} = V_{CPVDD} = 3.3V, \ R_L = \infty, \ C_{VDD} = 10 \mu F \ connected \ between \ V_{DD} \ and \ PGND, \ C_{BIAS} = 1 \mu F \ connected \ between \ V_{BIAS} \ and \ GND, \ C_{FLY} = 1 \mu F \ connected \ between \ C1P \ and \ C1N. \ C_{HOLD} = 1 \mu F \ connected \ between \ V_{MID} \ and \ PGND, \ R_{PREIN} = 10 k\Omega, \ R_{PREFB} = 50 k\Omega, \ R_{MICBIAS} = 3.3 k\Omega, \ MIC \ signal \ gain \ in \ ANC \ mode \ ANC_GAIN = -11.5 dB, \ MIC \ signal \ gain \ in \ PTL \ mode \ PTL_GAIN = -5.5 dB, \ V_{GAIN} = +1 V/V, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25 °C.) \ (Note1)$

| PARAMETER                       | SYMBOL         | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|---------------------------------|----------------|------------|---------------------------|-----|-----|-------|

| SCL Pulse-Width Low             | tLOW           |            | 1.3                       |     |     | μs    |

| SCL Pulse-Width High            | tHIGH          |            | 0.6                       |     |     | μs    |

| Data Setup Time                 | tsu:dat        |            | 100                       |     |     | ns    |

| Data Hold Time                  | thd:dat        |            | 0                         |     | 900 | ns    |

| SDA and SCL Receiving Rise Time | t <sub>R</sub> | (Note 5)   | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Receiving Fall Time | tF             | (Note 5)   | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA Transmitting Fall Time      | tF             | (Note 5)   | 20 +<br>0.1C <sub>B</sub> |     | 250 | ns    |

| Setup Time for STOP Condition   | tsu,sto        |            | 0.6                       |     |     | μs    |

| Bus Capacitance                 | СВ             |            |                           |     | 400 | рF    |

| Pulse Width of Suppressed Spike | tsp            |            | 0                         |     | 50  | ns    |

Note 1: All devices are 100% production tested at  $T_A = +25$ °C. Specifications over temperature limits are guaranteed by design.

**Note 2:** PSRR at any frequency is limited by resistor matching (common-mode sense architecture used to reject the modulation on VMID).

Note 3: Output power is guaranteed by measuring the RDSON of all power MOSFETs (headphone driver and charge pump).

Note 4: Line inputs AC-coupled to GND.

Note 5: CB is in pF.

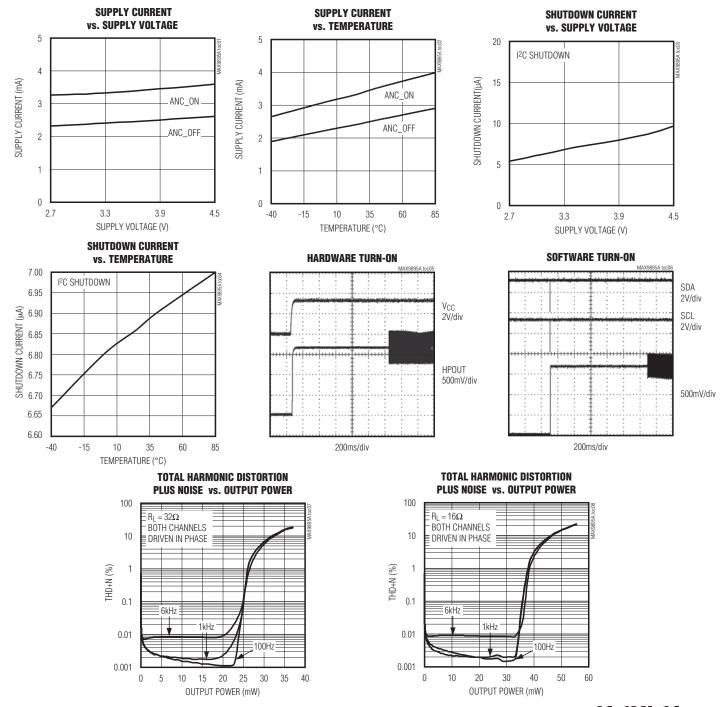

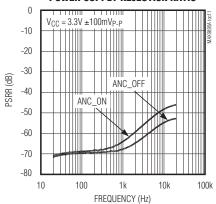

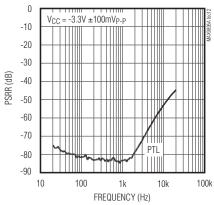

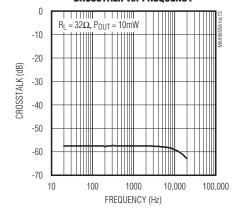

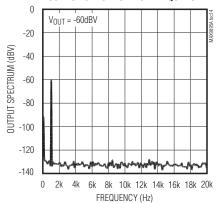

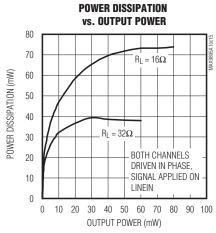

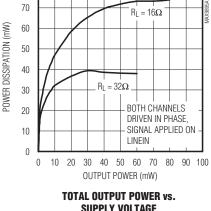

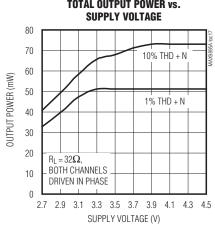

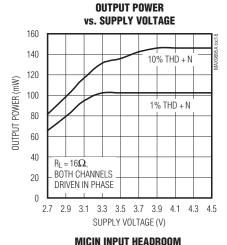

### **Typical Operating Characteristics**

$(V_{DD} = V_{PVDD} = V_{CPVDD} = 3.3V, R_L = \infty, C_{VDD} = 10 \mu F$  connected between  $V_{DD}$  and PGND,  $C_{BIAS} = 1 \mu F$  connected between  $V_{BIAS}$  and GND,  $C_{FLY} = 1 \mu F$  connected between C1P and C1N.  $C_{HOLD} = 1 \mu F$  connected between  $V_{MID}$  and GND,  $R_{PREIN} = 10 k\Omega$ ,  $R_{PREFB} = 10 k\Omega$ ,  $R_{MICBIAS} = 3.3 k\Omega$ , MIC signal gain in ANC mode ANC\_GAIN = -11.5dB, MIC signal gain in PTL mode PTL\_GAIN = -5.5dB, both outputs driven in phase,  $G_{AIN} = 10 k\Omega$ ,  $G_{AIN} =$

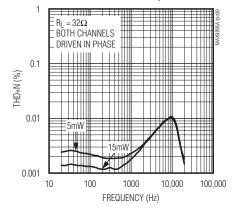

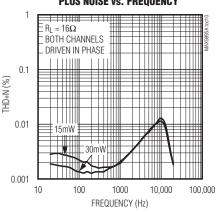

### Typical Operating Characteristics (continued)

$(V_{DD} = V_{PVDD} = V_{CPVDD} = 3.3V, R_L = \infty, C_{VDD} = 10\mu F$  connected between  $V_{DD}$  and PGND,  $C_{BIAS} = 1\mu F$  connected between  $V_{BIAS}$  and GND,  $C_{FLY} = 1\mu F$  connected between C1P and C1N.  $C_{HOLD} = 1\mu F$  connected between  $V_{MID}$  and GND,  $R_{PREIN} = 10k\Omega$ ,  $R_{PREFB} = 10k\Omega$ ,  $R_{MICBIAS} = 3.3k\Omega$ ,  $R_{MICBIAS} = 3.$

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY

### TOTAL HARMONIC DISTORTION PLUS NOISE vs. FREQUENCY

#### **POWER-SUPPLY REJECTION RATIO**

**POWER-SUPPLY REJECTION RATIO**

### CROSSTALK vs. FREQUENCY

#### **OUTPUT SPECTRUM vs. FREQUENCY**

### Typical Operating Characteristics (continued)

(V<sub>DD</sub> = V<sub>PVDD</sub> = V<sub>CPVDD</sub> = 3.3V, R<sub>L</sub> = ∞, C<sub>VDD</sub> = 10μF connected between V<sub>DD</sub> and PGND, C<sub>BIAS</sub> = 1μF connected between V<sub>BIAS</sub> and GND,  $C_{FLY} = 1\mu F$  connected between C1P and C1N.  $C_{HOLD} = 1\mu F$  connected between  $V_{MID}$  and GND,  $R_{PRFIN} = 10k\Omega$ ,  $R_{PREFB} = 10k\Omega$ ,  $R_{MICBIAS} = 3.3k\Omega$ , MIC signal gain in ANC mode ANC\_GAIN = -11.5dB, MIC signal gain in PTL mode PTL\_GAIN = -5.5dB, both outputs driven in phase, GAIN = +1V/V (MAX9895A)).

### \_\_\_\_Pin Description

| PIN  |     |                  | EUNOTION                                                                                                                                           |  |  |  |  |  |

|------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TQFN | WLP | NAME             | FUNCTION                                                                                                                                           |  |  |  |  |  |

| 1    | A6  | SPR1_L           | Left-Channel Signal Processing                                                                                                                     |  |  |  |  |  |

| 2    | C5  | MICOUT_L         | Left-Channel Microphone Preamplifier Output. Apply feedback resistor to set input gain. See the <i>Microphone Output</i> section for more details. |  |  |  |  |  |

| 3    | B6  | MICIN_L          | Left-Channel Microphone Input                                                                                                                      |  |  |  |  |  |

| 4    | C6  | MICBIAS          | Microphone Supply Voltage. Use separate left/right MICBIAS resistors.                                                                              |  |  |  |  |  |

| 5    | C4  | LINEIN_L         | Left-Channel Audio Line Input                                                                                                                      |  |  |  |  |  |

| 6    | D4  | LINEIN_R         | Right-Channel Audio Line Input                                                                                                                     |  |  |  |  |  |

| 7, 8 | D6  | GND              | Signal Ground (Reference for V <sub>BIAS</sub> , MICBIAS, and LINEIN)                                                                              |  |  |  |  |  |

| 9    | E6  | MICIN_R          | Right-Channel Microphone Input                                                                                                                     |  |  |  |  |  |

| 10   | D5  | MICOUT_R         | Right-Channel Microphone Preamplifier Output. Apply feedback resistor to set input gain.                                                           |  |  |  |  |  |

| 11   | F6  | SPR1_R           | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 12   | E5  | SPC1_R           | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 13   | F5  | SPC2_R           | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 14   | E4  | SPC3_R           | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 15   | F4  | SPC4_R           | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 16   | E3  | SPR2_R           | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 17   | F3  | VBIAS            | Internal Reference. Bypass V <sub>BIAS</sub> to GND with a 1µF capacitor. Used for MICIN and LINEIN.                                               |  |  |  |  |  |

| 18   | E2  | SPFC2_R          | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 19   | F2  | SPFC1_R          | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 20   | D2  | SPFO_R           | Right-Channel Signal Processing                                                                                                                    |  |  |  |  |  |

| 21   | F1  | HPOUT_R          | Right-Channel Headphone Output                                                                                                                     |  |  |  |  |  |

| 22   |     | V <sub>DD</sub>  |                                                                                                                                                    |  |  |  |  |  |

| 23   | E1  | PVDD             | Positive Supply Voltage                                                                                                                            |  |  |  |  |  |

| 24   |     | CPVDD            |                                                                                                                                                    |  |  |  |  |  |

| 25   | D1  | C1P              | Charge-Pump Flying Capacitor Positive                                                                                                              |  |  |  |  |  |

| 26   | C1  | C1N              | Charge-Pump Flying Capacitor Negative                                                                                                              |  |  |  |  |  |

| 27   | B1  | V <sub>MID</sub> | Charge-Pump Output Voltage. Connect to common return of headphone. Bypass V <sub>MID</sub> with a 1µF capacitor to PGND.                           |  |  |  |  |  |

| 28   |     | N.C.             | No Connection                                                                                                                                      |  |  |  |  |  |

| 29   | A1  | PGND             | Power Ground                                                                                                                                       |  |  |  |  |  |

| 30   | D3  | SDA/NC-MODE      | I <sup>2</sup> C Interface Data Line. Also used as MODE select in hardware mode (SCL = GND See Table 1.                                            |  |  |  |  |  |

| 31   | C3  | SCL              | I <sup>2</sup> C Interface Clock Line. Connect to GND for hardware mode.                                                                           |  |  |  |  |  |

| 32   | A2  | HPOUT L          | Left-Channel Headphone Output                                                                                                                      |  |  |  |  |  |

### **Pin Description**

| F    | PIN | NAME    | FUNCTION                                |  |  |  |  |

|------|-----|---------|-----------------------------------------|--|--|--|--|

| TQFN | WLP | INAIVIE | FUNCTION                                |  |  |  |  |

| 33   | C2  | SPFO_L  | Left-Channel Signal Processing          |  |  |  |  |

| 34   | B2  | SPFC1_L | Left-Channel Signal Processing          |  |  |  |  |

| 35   | А3  | SPFC2_L | Left-Channel Signal Processing          |  |  |  |  |

| 36   | В3  | SPR2_L  | Left-Channel Signal Processing          |  |  |  |  |

| 37   | A4  | SPC4_L  | Left-Channel Signal Processing          |  |  |  |  |

| 38   | B4  | SPC3_L  | Left-Channel Signal Processing          |  |  |  |  |

| 39   | A5  | SPC2_L  | Left-Channel Signal Processing          |  |  |  |  |

| 40   | B5  | SPC1_L  | Left-Channel Signal Processing          |  |  |  |  |

| _    | _   | EP      | Exposed Pad. Must be connected to PGND. |  |  |  |  |

### **Detailed Description**

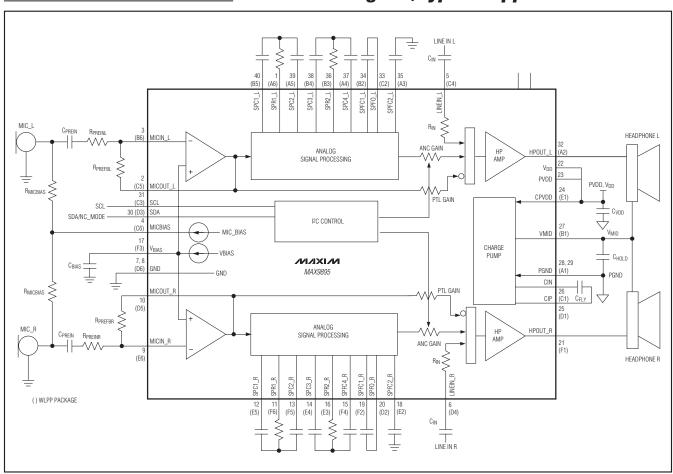

The MAX9895A is a complete audio subsystem for active noise-cancelling stereo headsets. The device features a microphone preamplifier, an analog sound processing block, and a headphone amplifier combining to create a simple and very flexible active noisecanceling system. The MAX9895A uses feed-forward architecture, creating a headphone signal that has the same amplitude, but opposite phase as outside noise that leaks through the mechanical isolation of the earphones. These two signals cancel each other and provide noise suppression at the ear. The device consists of an ultra-low noise microphone preamplifier to set input impedance and gain, followed by an analog signal processing block, and a capacitorless headphone amplifier. The headphone amplifier does not require the large output-coupling capacitors used by conventional single-supply headphone amplifiers, and can output 33mW into a  $16\Omega$  headphone. The product also features undervoltage lockout and comprehensive clickand-pop suppression circuitry. See the Functional Diagram/Typical Applications Circuit for further details.

#### **Modes of Operation**

The MAX9895A features three modes of operation; active noise canceling (ANC) on or off, and push-to-listen (PTL). The ANC-on mode provides full noise canceling and provides line-input mixing to the headphones. This allows music to be played while noise canceling is operational. The ANC-off mode disables the microphone preamplifiers and noise processing blocks, but allows the line inputs to operate normally. This gives flexibility to the design such that music can still be played through the headphones while noise canceling is inactive.

The PTL mode connects the microphone preamplifier directly to the headphone amplifier, bypassing the noise cancellation, and attenuates the line-input signal. PTL mode gives the user the option of listening to the surroundings without removing the headphones. See Table 1 for hardware mode settings.

### **Microphone Preamplifier**

The MAX9895A features an ultra-low noise microphone input preamplifier. Using an inverting op amp design with external input and feedback resistors allows flexibility in setting input impedance and gain. The microphone gain can be adjusted in two ways: adjust the feedback resistor in the preamplifier stage by use of a potentiometer or setting I<sup>2</sup>C registers using a microcontroller to adjust the gain after the analog processing stage.

#### Microphone Bias Supply

The MAX9895A provides a low-noise voltage bias designed for biasing electret condenser microphones (ECM). The bias output is regulated to 2.5V.

### Table 1. Mode Selection (in Hardware Mode)

| SDA LEVEL       | CONFIGURATION                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| GND             | (PTL Mode) LINEIN_ is attenuated, MICOUT_ signal is passed directly to the headphone driver without filtering and phase reversal. |

| Hi-Z            | ANC on                                                                                                                            |

| V <sub>DD</sub> | ANC off (only HP amps are active)                                                                                                 |

#### Microphone Output

The outputs of the microphone preamplifiers are provided to allow for external adjustment of the gain of the preamplifier and to provide a path for voice transmission (headset) applications.

#### **Programmable Gain**

The second gain stage can be programmed in 0.5dB steps to compensate for microphone and headphone sensitivity. This requires a microcontroller connected to the I<sup>2</sup>C bus, which operates in slave mode. An alternate solution for gain setting is to add a trim-pot to the feedback resistor of the microphone preamplifier. See the *Typical Application Circuit*.

### **Analog Signal Processing**

This block creates the noise cancellation signal. The signal processing block uses the output of the microphone preamp and external components to create a headphone signal that has the same amplitude, but opposite phase as outside noise that leaks through the mechanical isolation of the earphones, so both waves cancel each other. **Note:** The choice of external components depends on the headset characteristics. Please contact your local Maxim sales office for more information on determining the proper component values for the *Analog Signal Processing* section.

#### **Headphone Amplifier**

The stereo headphone amplifier is capable of delivering 33mW into  $16\Omega$  loads and has a gain (line in to headphone out) of 1V/V for the MAX9895AA. The input to the headphone amplifier is a linear sum of three signals: line in (external input), mic gain (output of analog signal processing block) and PTL gain (ANC bypass).

Unlike conventional single-supply, single-ended amplifiers, the MAX9895A headphone amplifier does not need large DC-blocking caps, as the outputs are referred to VCC/2, which is the bias output voltage of the amplifier. Conventional single-supply headphone amplifiers require large coupling capacitors to block the output DC bias from the headphone. The MAX9895A architecture uses a high-efficiency charge pump to create an internal midbias supply voltage (VMID). This keeps supply current low and allows the amplifier outputs to be connected directly to the headphones without the need for these large coupling capacitors.

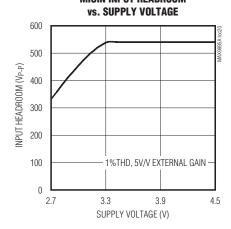

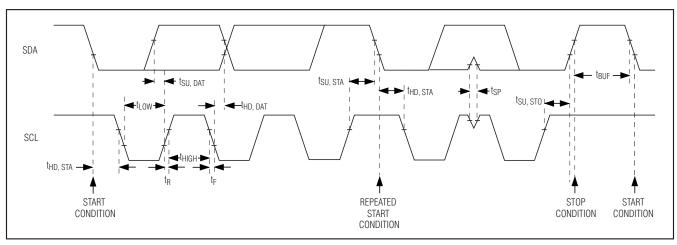

### Serial Interface

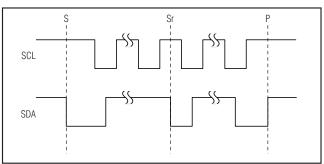

The MAX9895A features an I<sup>2</sup>C, 2-wire serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate communication between the MAX9895A and the master at clock rates up to 400kHz. Figure 1 shows the 2-wire interface timing diagram. The MAX9895A is a receive-only slave device relying on the master to generate the SCL signal. The MAX9895A cannot write to the SDA bus except to acknowledge the receipt of data from the master. The master, typically a microcontroller, generates SCL and initiates data transfer on the bus. If the serial interface is not used, the SCL pin must be tied to GND to disable this feature and allow the device to be used in hardware mode (no microcontroller).

A master device communicates to the MAX9895A by transmitting the proper address followed by the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) con-

Figure 1. 2-Wire Serial-Interface Timing Diagram

Figure 2. START, STOP, and REPEATED START Conditions

dition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.

The MAX9895A SDA line operates as both an input and an open-drain output. A pullup resistor, greater than  $500\Omega$ , is required on the SDA bus. The MAX9895A SCL line operates as an input only. A pullup resistor, greater than  $500\Omega$ , is required on SCL if there are multiple masters on the bus, or if the master in a single-master system has an open-drain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the MAX9895A from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

#### **Bit Transfer**

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section). SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

### **START and STOP Conditions**

SDA and SCL idle high when the bus is not in use. A master device initiates communication by issuing a START (S) condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP (P) condition is a low-to-high transition on SDA while SCL is high (Figure 2). A START condition from the master signals the beginning of transmission to the MAX9895A. The master terminates transmission and frees the bus by issuing a STOP condition. The bus remains active if a REPEATED START (Sr) condition is generated instead of a STOP condition.

### Early STOP Conditions

The MAX9895A recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition.

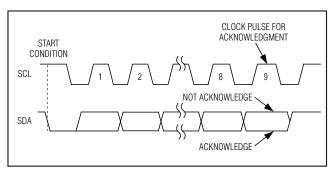

Figure 3. Acknowledge

#### Slave Address

The MAX9895A is available with 0x40 preset slave addresses. The address is defined as the seven most significant bits (MSBs) followed by the read/write (R/W) bit. The address is the first byte of information sent to the MAX9895A after the START condition. The MAX9895A is a slave device only capable of being written to. The sent R/W bit must always be a zero when configuring the MAX9895A.

The MAX9895A acknowledges the receipt of its address even if R/W is set to 1. However, the MAX9895A does not drive SDA. Addressing the MAX9895A with R/W set to 1 causes the master to receive all 1s regardless of the contents of the command register.

### Acknowledge

The acknowledge bit (ACK) is a clocked 9th bit that the MAX9895A uses to handshake receipt of each byte of data (see Figure 3). The MAX9895A pulls down SDA during the master-generated 9th clock pulse. The SDA line must remain stable and low during the high period of the acknowledge clock pulse. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master can reattempt communication.

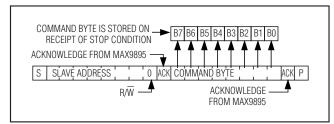

#### Write Data Format

A write to the MAX9895A includes transmission of a START (S) condition, the slave address with the R/W bit reset to 0, one byte of data to configure the command register, and a STOP (P) condition. Figure 4 illustrates the proper format for one frame.

The MAX9895A only accepts write data, but it acknowledges the receipt of its address byte with the R/W bit set high. The MAX9895A does not write to the SDA bus

Figure 4. Write Data Format Example

in the event that the R/W bit is set high. Subsequently, the master reads all 1s from the MAX9895A. Always reset the R/W bit to 0 to avoid this situation.

#### I<sup>2</sup>C-Enabled Software Mode

The MAX9895A can operate with or without an external microcontroller ( $\mu$ C). When a  $\mu$ C is present, commands are sent through the I²C protocol (SCL, SDA).

#### I<sup>2</sup>C-Disabled Hardware Mode

By tying SCL to ground, the I<sup>2</sup>C interface is disabled and the device operates in hardware mode. In this case, the SDA pin operates as a MODE select. Table 1 shows different configurations with the SDA level.

### \_Application Information

#### Input-Coupling Capacitor

The input capacitor ( $C_{IN}$ ), in conjunction with the input resistor ( $R_{IN}$ ), forms a highpass filter that removes the DC bias from an incoming signal (see the *Functional Diagram/Typical Applications Circuit*). The AC-coupling capacitor allows the device to bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Choose the CIN so that f-3dB is well below the lowest frequency of interest. Setting f-3dB too high affects the

device's low-frequency response. Use capacitors whose dielectrics have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, can result in increased distortion at low frequencies.

Apply same method for microphone input-coupling capacitor ( $C_{PREIN}$ ). The  $R_{IN}$  for microphone input is  $R_{PREIN}$ .

#### **Setting the Gains**

The gains of the microphone input preamplifiers are set through the feedback using the following equation:

$$A_V(V/V) = -(R_F/R_{IN})$$

In stand-alone control mode, the internal gain stage for MIC GAIN is fixed at 11.5dB and the PTL GAIN stage is fixed at -5.5dB. In software control mode (I<sup>2</sup>C mode), the internal gain stage stages, MIC GAIN and PTL GAIN, are programmable through the I<sup>2</sup>C registers. See the *Serial Interface* section for more information.

The LINE IN and HEADPHONE AMP stages each have fixed voltage gain of 0dB.

### **Charge-Pump Capacitor Selection**

Use ceramic capacitors with a low ESR for optimum performance. For optimal performance over the extended temperature range, select capacitors with an X7R dielectric. Table 2 lists suggested manufacturers.

#### **Layout and Grounding**

Proper layout and grounding are essential for optimum performance. Connect PGND and GND together at a single point on the PCB. Place the power-supply bypass capacitor and the charge-pump hold capacitor as close as possible to the MAX9895A. Route PGND and all traces that carry switching transients away from GND and the audio signal path. The thin QFN package features an exposed pad that improves thermal efficiency. Ensure that the exposed pad is electrically connected to PGND and is isolated from VDD, PVDD, and CPVDD.

**Table 2. Suggest Capacitor Manufacturers**

| SUPPLIER    | PHONE        | FAX          | WEBSITE               |

|-------------|--------------|--------------|-----------------------|

| Taiyo Yuden | 800-348-2496 | 847-925-0899 | www.t-yuden.com       |

| TDK         | 847-803-6100 | 847-390-4405 | www.component.tdk.com |

| Murata      | 770-436-1300 | 770-436-3030 | www.murata.com        |

### Table 3. I<sup>2</sup>C Register Table

| ADDRESS | TYPE | POR  | NAME           | 7 | 6                                      | 5 | 4                                 | 3                                  | 2   | 1       | 0      |

|---------|------|------|----------------|---|----------------------------------------|---|-----------------------------------|------------------------------------|-----|---------|--------|

| 0x00    | R/W  | 0x0B | ANC_GAIN_LEFT  | Χ | Χ                                      | Χ | ANC GAIN setting for LEFT CHANNEL |                                    |     |         | HANNEL |

| 0x01    | R/W  | 0x0B | ANC_GAIN_RIGHT | Χ | Χ                                      | Χ | ANG                               | ANC GAIN setting for RIGHT CHANNEL |     |         |        |

| 0x02    | R/W  | 0x0B | PTL_GAIN_LEFT  | Χ | X X PTL GAIN setting for LEFT CHANNEL  |   |                                   |                                    |     | HANNEL  |        |

| 0x03    | R/W  | 0x0B | PTL_GAIN_RIGHT | Χ | X X PTL GAIN setting for RIGHT CHANNEL |   |                                   |                                    |     | CHANNEL |        |

| 0x04    | R/W  | 0x00 | MODE           |   | X                                      |   |                                   | 0                                  | PTL | ANC     | SHDN   |

### Table 4. Gain Setting Register 0x00, 0x01, 0x02, 0x03

| HEX  | 0x00, 0x01<br>ANC GAIN [dB] | HEX        | 0x00, 0x01<br>ANC GAIN [dB] | HEX  | 0x00, 0x01<br>ANC GAIN [dB] |  |  |

|------|-----------------------------|------------|-----------------------------|------|-----------------------------|--|--|

| 0x00 | -6.0                        | 0x08       | -10.0                       | 0x10 | -14.0                       |  |  |

| 0x01 | -6.5                        | 0x09       | -10.5                       | 0x11 | -14.5                       |  |  |

| 0x02 | -7.0                        | 0x0A       | -11.0                       | 0x12 | -15.0                       |  |  |

| 0x03 | -7.5                        | 0x0B (POR) | -11.5                       | 0x13 | -15.5                       |  |  |

| 0x04 | -8.0                        | 0x0C       | -12.0                       | 0x14 | -16.0                       |  |  |

| 0x05 | -8.5                        | 0x0D       | -12.5                       | 0x15 | -16.5                       |  |  |

| 0x06 | -9.0                        | 0x0E       | -13.0                       | 0x16 | -17.0                       |  |  |

| 0x07 | -9.5                        | 0x0F       | -13.5                       | 0x17 | -17.5                       |  |  |

| HEX  | 0x02, 0x03<br>PTL GAIN [dB] | HEX        | 0x02, 0x03<br>PTL GAIN [dB] | HEX  | 0x02, 0x03<br>PTL GAIN [dB] |  |  |

| 0x00 | -0.0                        | 0x08       | -4.0                        | 0x10 | -8.0                        |  |  |

| 0x01 | -0.5                        | 0x09       | -4.5                        | 0x11 | -8.5                        |  |  |

| 0x02 | -1.0                        | 0x0A       | -5.0                        | 0x12 | -9.0                        |  |  |

| 0x03 | -1.5                        | 0x0B (POR) | -5.5                        | 0x13 | -9.5                        |  |  |

| 0x04 | -2.0                        | 0x0C       | -6.0                        | 0x14 | -10.0                       |  |  |

| 0x05 | -2.5                        | 0x0D       | -6.5                        | 0x15 | -10.5                       |  |  |

| 0x06 | -3.0                        | 0x0E       | -7.0                        | 0x16 | -11.0                       |  |  |

| 0x07 | -3.5                        | 0x0F       | -7.5                        | 0x17 | -11.5                       |  |  |

### Table 5. Mode Register 0x04

| BIT | NAME | POR                                                               | FUNCTION                                                               |

|-----|------|-------------------------------------------------------------------|------------------------------------------------------------------------|

| 0   | SHDN | 0                                                                 | 0: Shut down<br>1: Play                                                |

| 1   | ANC  | O: Noise cancelling on 1: Noise cancelling off (microphone muted) |                                                                        |

| 2   | PTL  | 0                                                                 | 0: LINEIN routed to HPOUT 1: LINEIN attenuated; MICOUT routed to HPOUT |

**Table 6. Source Select**

| INPUT         | MODE                                                  |                   |                                                              |  |  |  |  |  |

|---------------|-------------------------------------------------------|-------------------|--------------------------------------------------------------|--|--|--|--|--|

| INPUT         | ANC ON                                                | ANC OFF           | PTL                                                          |  |  |  |  |  |

| Microphone In | NC mode, inverting, gain defined by I2C REG 01 and 02 | Muted             | Noninverting, gain defined by I <sup>2</sup> C REG 03 and 04 |  |  |  |  |  |

| Line In       | Noninverting, 0db                                     | Noninverting, 0dB | Attenuated                                                   |  |  |  |  |  |

### Functional Diagram/Typical Applications Circuit

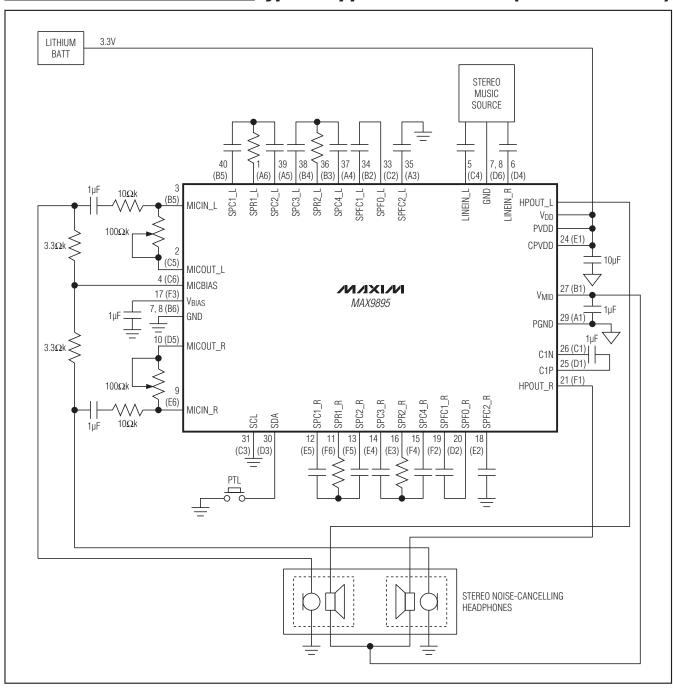

### Typical Applications Circuit (Hardware Mode)

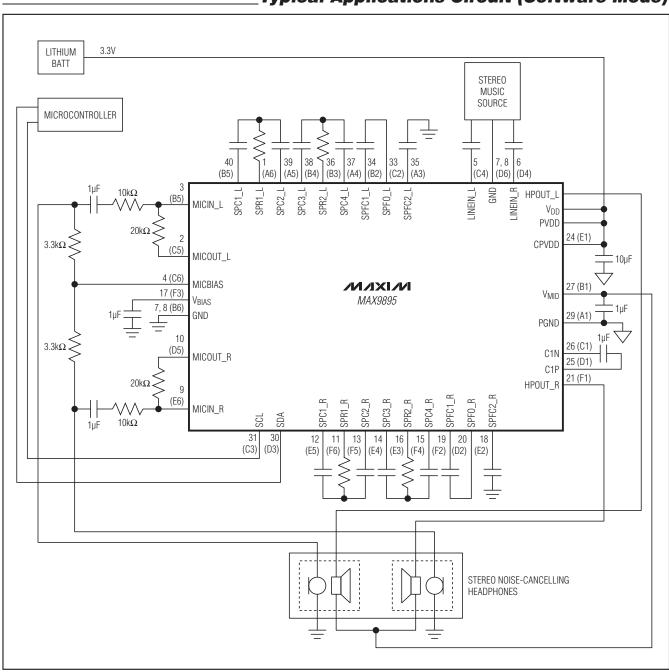

**Typical Applications Circuit (Software Mode)**

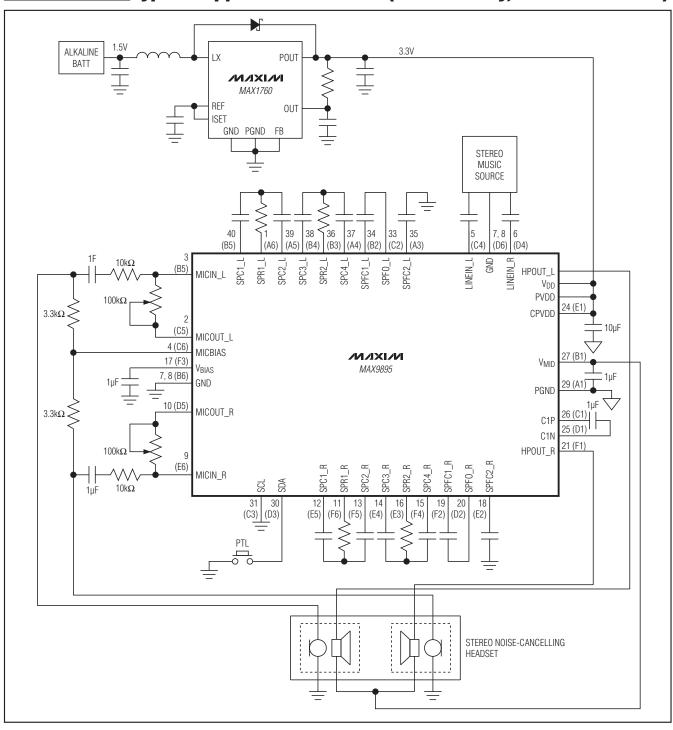

### Typical Applications Circuit (AAA Battery, Hardware Mode)

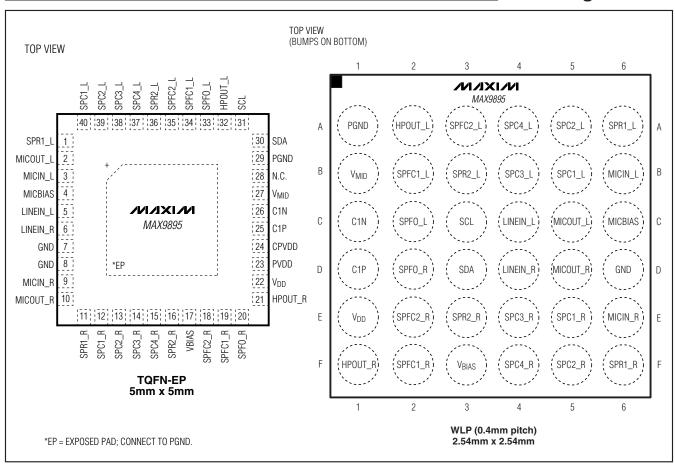

### **Pin Configurations**

\_\_\_\_\_Chip Information

PROCESS: BiCMOS

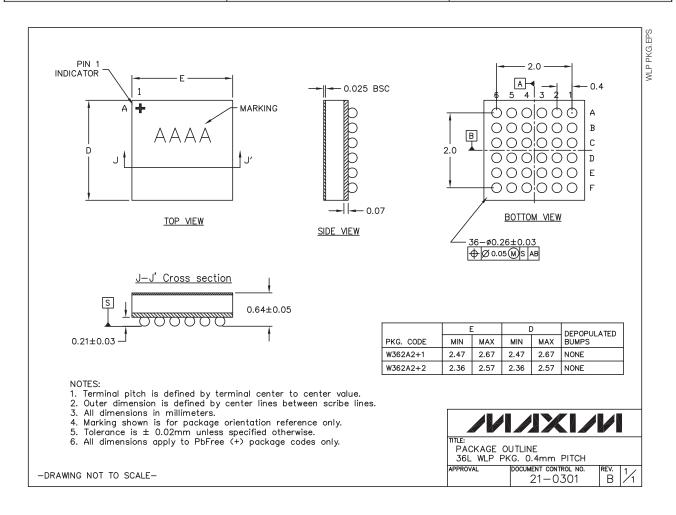

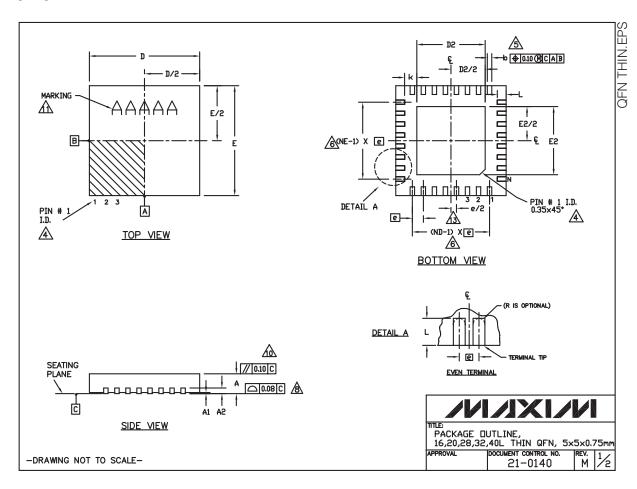

### **Package Information**

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/package">www.maxim-ic.com/package</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 36 WLP       | W362A2+2     | <u>21-0301</u> |

| 40 TQFN      | T4055+1      | <u>21-0140</u> |

### **Package Information (continued)**

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

### Package Information (continued)

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| COMMON DIMENSIONS |                |      |           |      |           |      |           |      |      |           |      |      |      |      |      |

|-------------------|----------------|------|-----------|------|-----------|------|-----------|------|------|-----------|------|------|------|------|------|

| PKG.              | 16L 5x5        |      | 20L 5x5   |      | 28L 5x5   |      | 32L 5x5   |      |      | 40L 5x5   |      |      |      |      |      |

| SYMBOL            | MIN. NOM. MAX. |      | MIN.      | NDM. | MAX.      | MIN. | NOM.      | MAX. | MIN. | NDM.      | MAX. | MIN. | NOM. | MAX. |      |

| Α                 | 0.70           | 0.75 | 0.80      | 0.70 | 0.75      | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70 | 0.75 | 0.80 |

| A1                | 0              | 0.02 | 0.05      | 0    | 0.02      | 0.05 | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 | 0    | 0.02 | 0.05 |

| A2                | 0.20 REF.      |      | 0.20 REF. |      | 0.20 REF. |      | 0.20 REF. |      |      | 0.20 REF. |      |      |      |      |      |

| b                 | 0.25           | 0.30 | 0.35      | 0.25 | 0.30      | 0.35 | 0.20      | 0.25 | 0.30 | 0.20      | 0.25 | 0.30 | 0.15 | 0.20 | 0.25 |

| D                 | 4.90           | 5.00 | 5.10      | 4.90 | 5.00      | 5.10 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 | 4.90 | 5.00 | 5.10 |

| E                 | 4.90           | 5.00 | 5.10      | 4.90 | 5.00      | 5.10 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 | 4.90 | 5.00 | 5.10 |

| e                 | 0.80 BSC.      |      | 0.65 BSC. |      | 0.50 BSC. |      | 0.50 BSC. |      |      | 0.40 BSC. |      |      |      |      |      |

| k                 | 0.25           | -    | -         | 0.25 | _         | _    | 0.25      | -    | -    | 0.25      | -    | -    | 0.25 | -    | _    |

| L                 | 0.30           | 0.40 | 0.50      | 0.45 | 0.55      | 0.65 | 0.45      | 0.55 | 0.65 | 0.30      | 0.40 | 0.50 | 0.30 | 0.40 | 0.50 |

| N                 | 16             |      | 20        |      | 28        |      | 32        |      |      | 40        |      |      |      |      |      |

| ND                | 4              |      | 5         |      | 7         |      | 8         |      | 10   |           |      |      |      |      |      |

| NE                | 4              |      | 5         |      | 7         |      | 8         |      |      | 10        |      |      |      |      |      |

| JEDEC             | WHHB           |      | WHHC      |      | WHHD-1    |      | WHHD-2    |      |      |           |      |      |      |      |      |

- DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE

- ⚠ DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN

- 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR T2855-3, T2855-6, T4055-1 AND T4055-2.

- √O₂ WARPAGE SHALL NOT EXCEED 0.10 mm.

- 11. MARKING IS FOR PACKAGE DRIENTATION REFERENCE ONLY.

- NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- △3 LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "e", ±0.05.

- 14. ALL DIMENSIONS APPLY TO BOTH LEADED (-) AND PHEREE (+) PKG. CODES.

-DRAWING NOT TO SCALE-

| EXPOSED PAD VARIATIONS |           |      |      |      |      |      |  |  |

|------------------------|-----------|------|------|------|------|------|--|--|

| PKG.                   |           | D2   |      | E2   |      |      |  |  |

| CODES                  | MIN. NOM. |      | MAX. | MIN. | NDM. | MAX. |  |  |

| T1655-2                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655-3                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T1655-4                | 2.19      | 2.29 | 2.39 | 2.19 | 2.29 | 2.39 |  |  |

| T165N-1                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-3                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-4                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T2055-5                | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2055MN-5              | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-3                | 3.15      | 3.25 | 3.35 | 3.15 | 3,25 | 3.35 |  |  |

| T2855-4                | 2.60      | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-5                | 2.60      | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-6                | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T2855-7                | 2.60      | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |

| T2855-8                | 3.15      | 3.25 | 3.35 | 3.15 | 3,25 | 3.35 |  |  |

| T2855N-1               | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |

| T3255-3                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-4                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255M-4               | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255-5                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T3255N-1               | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |

| T4055-1                | 3.40      | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

| T4055-2                | 3.40      | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

| T4055N-1               | 3.40      | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

| T4055MN-1              | 3.40      | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |

PACKAGE DUTLINE,

16,20,28,32,40L THIN QFN, 5x5x0.75mm

21-0140

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.