### **General Description**

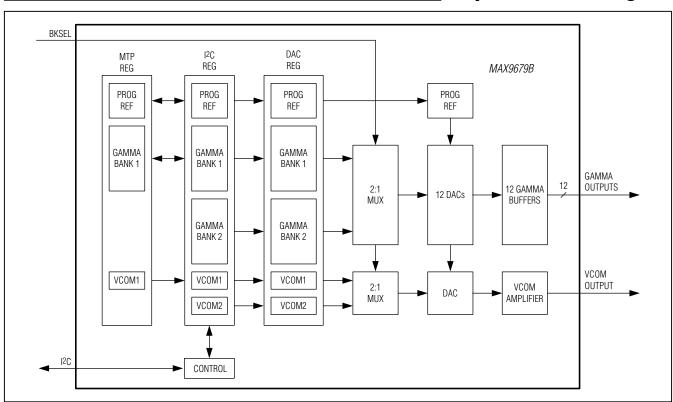

The MAX9679B provides multiple programmable reference voltages for gamma correction in TFT LCDs and a programmable reference voltage for VCOM adjustment. All gamma and VCOM reference voltages have a 10-bit digital-to-analog converter (DAC) and high-current buffer, which reduces the recovery time of the output voltages when critical levels and patterns are displayed. A programmable internal reference sets the full-scale voltage of the DACs.

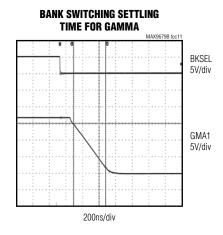

Two independent sets of gamma curves and VCOM codes can be stored in the IC's volatile memory; BKSEL signal selects between the two sets.

The IC has multiple-time programmable (MTP) memory to store gamma and VCOM codes on the chip, eliminating the need for external EEPROM.

\_Applications

TFT LCDs

#### **Features**

- ♦ 12 Channels of Programmable Gamma Voltages with 10-Bit Resolution

- ♦ Programmable VCOM Voltage with 10-Bit Resolution

- **♦ Programmable Reference for DACs**

- Multiple-Time Programmable Memory to Store Gamma and VCOM Codes

- Switching Between Two Gamma Curves and VCOM Voltages

- AVDD1, AVDD2, and AVDD\_AMP Supplies to Reduce Heat

- ♦ I2C Interface (1MHz Fast-Mode Plus)

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX9679BETG+ | -40°C to +85°C | 24 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### Simplified Block Diagram

<sup>\*</sup>EP = Exposed pad.

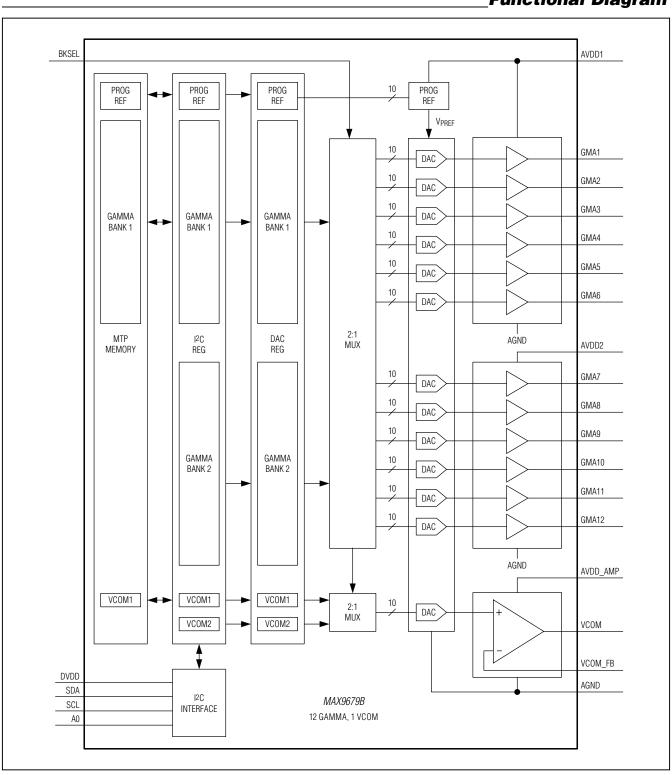

### **Functional Diagram**

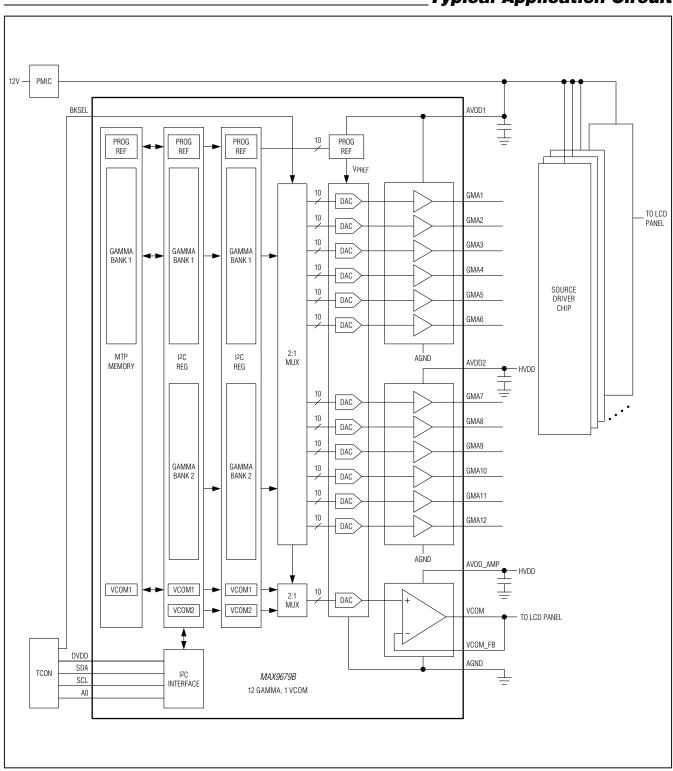

**Typical Application Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages are with respect to A | GND.)                            |

|-------------------------------------|----------------------------------|

| Supply Voltages                     |                                  |

| AVDD1, AVDD2, AVDD_AMP              | 0.3V to +22V                     |

| DVDD                                | 0.3V to +4V                      |

| Outputs                             |                                  |

| GMA1-GMA6                           | 0.3V to (VAVDD1 + 0.3V)          |

| GMA7-GMA12                          | 0.3V to (VAVDD2 + 0.3V)          |

| VCOM                                | -0.3V to (VAVDD_AMP + 0.3V)      |

| Inputs                              |                                  |

| SDA, SCL, A0, BKSEL                 | 0.3V to +6V                      |

| VCOM_FB                             | $-0.3V$ to (VAVDD_AMP + $0.3V$ ) |

| Continuous Current                                    |               |

|-------------------------------------------------------|---------------|

| SDA, SCL                                              | ±20mA         |

| GMA1-GMA8                                             | ±200mA        |

| VCOM                                                  | ±600mA        |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

| TQFN Multilayer Board                                 |               |

| (derate 25.6mW/°C above +70°C)                        | 2051.3mW      |

| Junction Temperature                                  |               |

| Operating Temperature Range                           | 40°C to +85°C |

| Storage Temperature Range                             |               |

| Lead Temperature (soldering, 10s)                     | +300°C        |

| Soldering Temperature (reflow)                        | +260°C        |

|                                                       |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

TOFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )........39°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )............6°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(VAVDD1 = 18V, VAVDD2 = VAVDD\_AMP = 9V, VDVDD = 3.3V, VAGND = 0V, VCOM = VCOM\_FB, programmable reference code = 905, no load, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)$

| PARAMETER                                       | SYMBOL                          | CONDITIONS                | MIN | TYP  | MAX | UNITS |

|-------------------------------------------------|---------------------------------|---------------------------|-----|------|-----|-------|

| SUPPLIES                                        |                                 |                           |     |      |     |       |

| AVDD1 Analog Supply Voltage<br>Range            | V <sub>A</sub> VDD1             | Guaranteed by PSRR        | 9   |      | 20  | V     |

| AVDD2 Analog Supply Voltage<br>Range            | V <sub>AVDD2</sub>              | Guaranteed by PSRR        | 6   |      | 20  | V     |

| AVDD_AMP Analog Supply<br>Voltage Range         | VAVDD_AMP                       | Guaranteed by PSRR        | 9   |      | 20  | V     |

| Digital Supply Voltage                          | V <sub>D</sub> V <sub>D</sub> D |                           | 2.7 |      | 3.6 | V     |

| AVDD1 Analog Quiescent<br>Current               | I <sub>AVDD1</sub>              |                           |     | 7    | 11  | mA    |

| AVDD2 Quiescent Current                         | lavdd2                          |                           |     | 6    | 9   | mA    |

| AVDD_AMP Quiescent Current                      | IAVDD_AMP                       |                           |     | 5    | 8   | mA    |

| Digital Quiescent Current                       | IDVDD                           | No SCL or SDA transitions |     | 1.5  | 3   | mA    |

| Thermal Shutdown                                |                                 |                           |     | +160 |     | °C    |

| Thermal-Shutdown Hysteresis                     |                                 |                           |     | 15   |     | °C    |

| Analog Supply Voltage Range for Programming MTP |                                 |                           | 12  |      | 20  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(VAVDD1 = 18V, VAVDD2 = VAVDD\_AMP = 9V, VDVDD = 3.3V, VAGND = 0V, VCOM = VCOM\_FB, programmable reference code = 905, no load, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                       | SYMBOL    | CONDITIONS                                                                                      | MIN   | TYP   | MAX   | UNITS |

|---------------------------------|-----------|-------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| PROGRAMMABLE REFERENC           | E (VPREF) |                                                                                                 |       |       |       |       |

| Full-Scale Voltage              |           | Referred to output, T <sub>A</sub> = +25°C                                                      | 19.96 | 19.98 | 20.00 | V     |

| Resolution                      |           |                                                                                                 | 10    |       |       | Bits  |

| Integral Nonlinearity Error     |           | $T_A = +25$ °C, 336 $\leq$ reference code $\leq$ 1007                                           |       | 0.5   | 1     | LSB   |

| Differential Nonlinearity Error |           | T <sub>A</sub> = +25°C, 336 ≤ reference code ≤ 1007                                             |       | 0.5   | 1     | LSB   |

| DAC                             |           |                                                                                                 |       |       |       |       |

| Resolution                      |           |                                                                                                 | 10    |       |       | Bits  |

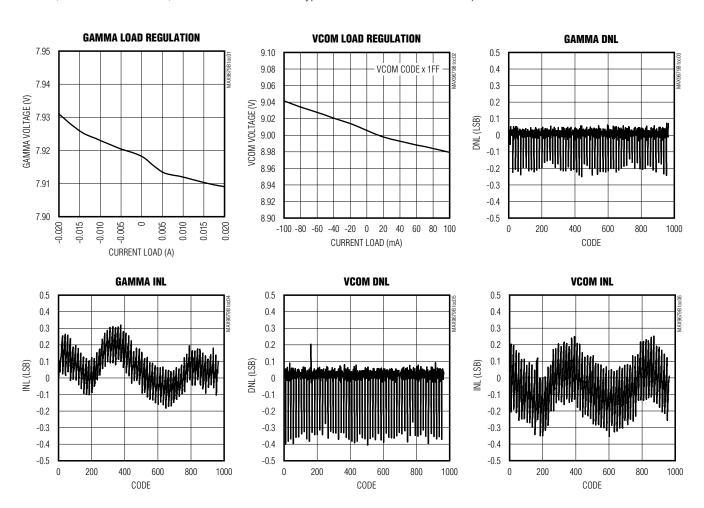

| Integral Nonlinearity Error     |           | TA = +25°C, 16 ≤ code ≤ 1008 for gamma, 256 ≤ code ≤ 1008 for VCOM                              |       | 0.5   | 1     | LSB   |

| Differential Nonlinearity Error |           | TA = $+25$ °C, $16 \le \text{code} \le 1008$ for gamma, $256 \le \text{code} \le 1008$ for VCOM |       | 0.5   | 1     | LSB   |

| GAMMA                           |           |                                                                                                 |       |       |       |       |

| Short-Circuit Current           |           | Output connected to either supply rail                                                          |       | 200   |       | mA    |

| Total Output Error              |           | T <sub>A</sub> = +25°C, code = 768 for<br>GMA1-GMA6 and code = 256 for GMA7-<br>GMA12           |       | 40    |       | mV    |

| Load Regulation                 |           | -5mA ≤ I <sub>LOAD</sub> ≤ +5mA, code = 768 for<br>GMA1-GMA6 and code = 256 for<br>GMA7-GMA12   |       | 0.5   |       | mV/mA |

| Low Output Voltage              |           | Sinking 4mA, referred to lower supply rail                                                      |       | 0.15  | 0.2   | V     |

| High Output Voltage             |           | Sourcing 4mA, referred to upper supply rail                                                     | -0.2  | -0.15 |       | V     |

|                                 |           | GMA1-GMA6, code = 768, VAVDD1 = 9V<br>to 20V; GMA7-GMA12, code = 256,<br>VAVDD2 = 5V to 20V     | 60    | 90    |       | 10    |

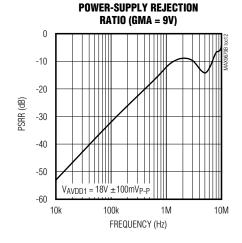

| Power-Supply Rejection Ratio    |           | GMA1-GMA6, code = 768,<br>frequency = 120kHz; GMA7-GMA12,<br>code = 256, frequency = 120kHz     |       | 40    |       | - dB  |

| Output Resistance               |           | Buffer is disabled                                                                              |       | 78    |       | kΩ    |

| Maximum Capacitive Load         |           | Placed directly at output                                                                       |       | 150   |       | pF    |

| Noise                           |           | RMS noise (10MHz bandwidth)                                                                     |       | 375   |       | μV    |

| VCOM OUTPUT (VCOM)              |           |                                                                                                 |       |       |       |       |

| Short-Circuit Current           |           | Output connected to either VCOM amplifier supplies                                              |       | 600   |       | mA    |

| Total Output Error              |           | T <sub>A</sub> = +25°C, code = 256,<br>VAVDD_AMP = 9V and 20V                                   |       | 40    |       | mV    |

| Load Regulation                 |           | -80mA ≤ I <sub>LOAD</sub> ≤ +80mA, code = 256                                                   |       | 0.5   |       | mV/mA |

| Low Output Voltage              |           | Sinking 10mA, referred to lower supply rail                                                     |       | 0.15  | 0.2   | V     |

| High Output Voltage             |           | Sourcing 10mA, referred to upper supply rail                                                    | -0.2  | -0.15 |       | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAVDD1 = 18V, VAVDD2 = VAVDD\_AMP = 9V, VDVDD = 3.3V, VAGND = 0V, VCOM = VCOM\_FB, programmable reference code = 905, no load, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)$

| PARAMETER                    | SYMBOL                                       | CONDITIONS                                   | MIN | TYP | MAX  | UNITS |

|------------------------------|----------------------------------------------|----------------------------------------------|-----|-----|------|-------|

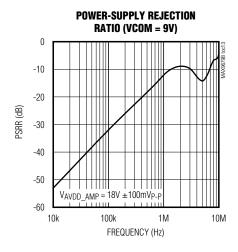

| Dower Supply Dejection Datio |                                              | 9V ≤ V <sub>AVDD_AMP</sub> ≤ 20V, code = 256 | 60  | 90  |      | dB    |

| Power-Supply Rejection Ratio |                                              | Frequency = 120kHz, code = 256               |     | 40  |      | ub ub |

| Maximum Capacitive Load      | Capacitive Load Placed directly at output 50 |                                              |     | рF  |      |       |

| Slew Rate                    |                                              |                                              | 100 |     | V/µs |       |

| Bandwidth                    |                                              | $R_L = 10k\Omega$ , $C_L = 50pF$             |     | 60  |      | MHz   |

| Noise                        |                                              | RMS noise (10MHz bandwidth)                  |     | 375 |      | μV    |

Note 2: 100% production tested at  $T_A = +25$ °C. Specifications over temperature limits are guaranteed by design.

#### **DIGITAL I/O CHARACTERISTICS**

(VDVDD = 3.3V, VAGND = 0V, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)

| PARAMETER                            | SYMBOL                            | CONDITIONS                        | MIN            | TYP   | MAX           | UNITS |

|--------------------------------------|-----------------------------------|-----------------------------------|----------------|-------|---------------|-------|

| Input High Voltage                   | VIH                               |                                   | 0.7 x<br>DVDD  |       |               | V     |

| Input Low Voltage                    | VIL                               |                                   |                |       | 0.3 x<br>DVDD | V     |

| Hysteresis of Schmitt Trigger Inputs | VHYS                              |                                   | 0.05 x<br>DVDD |       |               | V     |

| Low-Level Output Voltage             | V <sub>OL</sub>                   | Open drain, ISINK = 3mA           | 0              |       | 0.4           | V     |

| Low-Level Output Current             | loL                               | V <sub>OL</sub> = 0.4V            | 20             |       |               | mA    |

| Input Leakage Current                | I <sub>IH</sub> , I <sub>IL</sub> | V <sub>IN</sub> = 0 or DVDD       | -10            | +0.01 | +10           | μΑ    |

| Input Capacitance                    |                                   |                                   |                | 5     |               | рF    |

| Power-Down Input Current             | IIN                               | DVDD = 0, V <sub>IN</sub> = 1.98V | -10            |       | +10           | μΑ    |

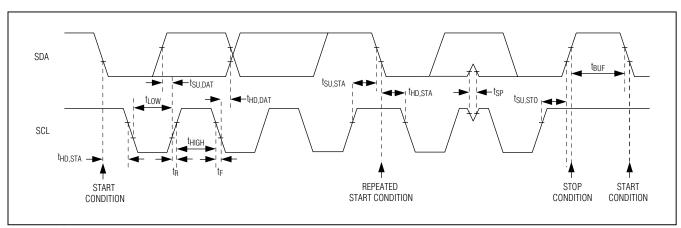

#### **I2C TIMING CHARACTERISTICS**

(VDVDD = 3.3V, VAGND = 0V, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)

| PARAMETER                                 | SYMBOL         | CONDITIONS                                            | MIN  | TYP | MAX  | UNITS |

|-------------------------------------------|----------------|-------------------------------------------------------|------|-----|------|-------|

| Serial-Clock Frequency                    | fscl           |                                                       | 0    |     | 1000 | kHz   |

| Hold Time (REPEATED) START Condition      | tHD,STA        | After this period, the first clock pulse is generated | 0.26 |     |      | μs    |

| SCL Pulse-Width Low                       | tLOW           |                                                       | 0.5  |     |      | μs    |

| SCL Pulse-Width High                      | tHIGH          |                                                       | 0.26 |     |      | μs    |

| Setup Time for a REPEATED START Condition | tsu,sta        |                                                       | 0.26 |     |      | μs    |

| Data Hold Time                            | thd,dat        | I <sup>2</sup> C-bus devices                          | 0    |     |      | ns    |

| Data Setup Time                           | tsu,dat        |                                                       | 50   |     |      | ns    |

| SDA and SCL Receiving Rise Time           | t <sub>R</sub> |                                                       |      |     | 120  | ns    |

| SDA and SCL Receiving Fall Time           | tF             |                                                       |      |     | 120  | ns    |

| SDA Transmitting Fall Time                | tF             |                                                       |      |     | 120  | ns    |

### **I2C TIMING CHARACTERISTICS (continued)**

(VDVDD = 3.3V, VAGND = 0V, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)

| PARAMETER                                       | SYMBOL  | CONDITIONS | MIN  | TYP | MAX | UNITS |

|-------------------------------------------------|---------|------------|------|-----|-----|-------|

| Setup Time for STOP Condition                   | tsu,sto |            | 0.26 |     |     | μs    |

| Bus Free Time Between STOP and START Conditions | tBUF    |            | 0.5  |     |     | μs    |

| Bus Capacitance                                 | Св      |            |      |     | 550 | pF    |

| Data Valid Time                                 | tvd;dat |            |      | 0.4 |     | μs    |

| Data Valid Acknowledge Time                     | tvd;ack |            |      | 0.4 |     | μs    |

| Pulse Width of Suppressed Spike                 | tsp     |            | 0    |     | 50  | ns    |

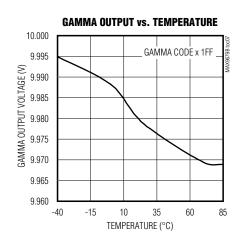

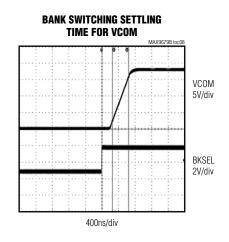

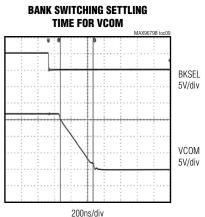

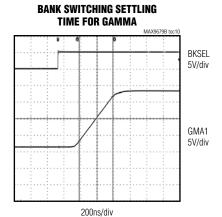

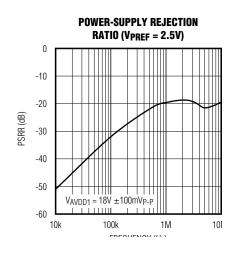

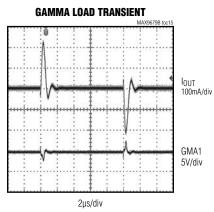

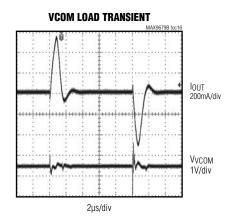

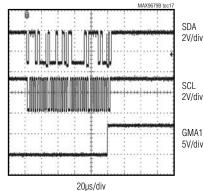

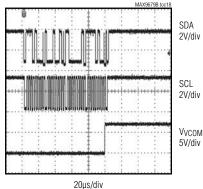

### **Typical Operating Characteristics**

(VAVDD1 = 18V, VAVDD2 = VAVDD\_AMP = 9V, VDVDD = 3.3V, VAGND = 0V, VCOM = VCOM\_FB, programmable reference code = 905, no load, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.)

### Typical Operating Characteristics (continued)

(VAVDD1 = 18V, VAVDD2 = VAVDD\_AMP = 9V, VDVDD = 3.3V, VAGND = 0V, VCOM = VCOM\_FB, programmable reference code = 905, no load, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.)

### Typical Operating Characteristics (continued)

$(V_{AVDD1} = 18V, V_{AVDD2} = V_{AVDD\_AMP} = 9V, V_{DVDD} = 3.3V, V_{AGND} = 0V, VCOM = VCOM\_FB$ , programmable reference code = 905, no load,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

#### **GAMMA PROGRAM TO OUTPUT DELAY**

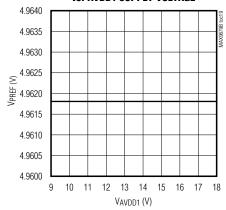

### PROGRAMMABLE REFERENCE vs. AVDD1 SUPPLY VOLTAGE

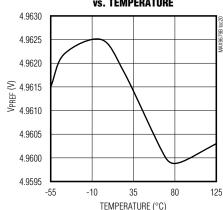

### PROGRAMMABLE REFERENCE vs. TEMPERATURE

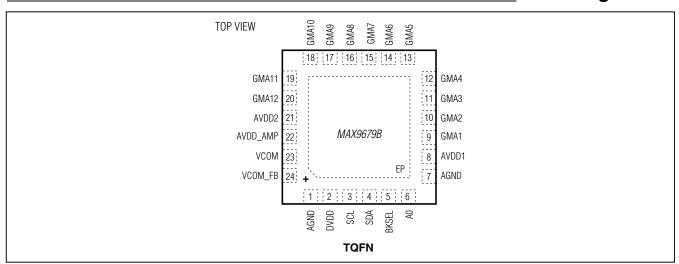

### **Pin Configuration**

### **Pin Description**

| PIN  | NAME     | FUNCTION                                                                                                                  |

|------|----------|---------------------------------------------------------------------------------------------------------------------------|

| 1, 7 | AGND     | Analog Ground                                                                                                             |

| 2    | DVDD     | Digital Power Supply. Bypass DVDD with a 0.1µF capacitor to AGND.                                                         |

| 3    | SCL      | I <sup>2</sup> C-Compatible Serial-Clock Input                                                                            |

| 4    | SDA      | I <sup>2</sup> C-Compatible Serial-Data Input/Output                                                                      |

| 5    | BKSEL    | Bank Select Logic Input. Selects which bank of volatile registers are switched through to the DACs.                       |

| 6    | A0       | I <sup>2</sup> C-Compatible Device Address Bit 0 (Input)                                                                  |

| 8    | AVDD1    | Analog Power Supply 1. The buffers for GMA1 through GM6 operate from AVDD1. Bypass AVDD1 with a 0.1µF capacitor to AGND.  |

| 9    | GMA1     | Gamma DAC Analog Output 1                                                                                                 |

| 10   | GMA2     | Gamma DAC Analog Output 2                                                                                                 |

| 11   | GMA3     | Gamma DAC Analog Output 3                                                                                                 |

| 12   | GMA4     | Gamma DAC Analog Output 4                                                                                                 |

| 13   | GMA5     | Gamma DAC Analog Output 5                                                                                                 |

| 14   | GMA6     | Gamma DAC Analog Output 6                                                                                                 |

| 15   | GMA7     | Gamma DAC Analog Output 7                                                                                                 |

| 16   | GMA8     | Gamma DAC Analog Output 8                                                                                                 |

| 17   | GMA9     | Gamma DAC Analog Output 9                                                                                                 |

| 18   | GMA10    | Gamma DAC Analog Output 10                                                                                                |

| 19   | GMA11    | Gamma DAC Analog Output 11                                                                                                |

| 20   | GMA12    | Gamma DAC Analog Output 12                                                                                                |

| 21   | AVDD2    | Analog Power Supply 2. The buffers for GMA7 through GM12 operate from AVDD2. Bypass AVDD2 with a 0.1µF capacitor to AGND. |

| 22   | AVDD_AMP | Power Supply for VCOM Amplifier. Bypass AVDD_AMP with a 0.1µF capacitor to AGND.                                          |

| 23   | VCOM     | VCOM Output                                                                                                               |

| 24   | VCOM_FB  | Feedback for VCOM Amplifier. VCOM_FB is the negative input terminal of the VCOM operational amplifier.                    |

| _    | EP       | Exposed Pad. EP is internally connected to AGND. EP must be connected to AGND.                                            |

### **Detailed Description**

The MAX9679B combines gamma, VCOM, and the DAC reference voltage into a single chip. All the output voltages are programmable. Power sequencing is well behaved since a single chip generates all the various reference voltages needed for the LCD panel.

Previous generations of programmable gamma chips required an external reference voltage for the digital-to-analog converters (DACs). This IC integrates a programmable reference voltage (VPREF) for the DACs, eliminating the need for an external reference voltage. Accuracy of the full-scale programmable reference voltage is  $\pm 0.1\%$ , and resolution is 10 bits. Both the DC and AC power-supply rejection of the programmable reference voltage is extremely high since it is powered from an internal linear regulator.

The gamma outputs are divided into an upper bank (GMA1–GMA6) that is powered from AVDD1 and a lower bank (GMA7–GMA12) that is powered from AVDD2. AVDD1 is the analog supply voltage for the LCD panel. AVDD2 can be connected to the same supply as AVDD1. If the IC's heat generation needs to be reduced, AVDD2 can be connected to a lower voltage such as 12V (input voltage to the LCD panel) or HVDD (half of the AVDD1 supply).

The VCOM operational amplifier operates from AVDD\_AMP. Similar to AVDD2, AVDD\_AMP can be connected to AVDD1, 12V, or HVDD. Peak VCOM output current is 600mA. The negative input terminal of the VCOM operational amplifier is available for applications that require external push-pull transistors.

The IC contains nonvolatile, multiple-time programmable memory that can store the gamma, VCOM, and the programmable reference codes.

The interface and control of the IC are completely digital. Functions that are not real-time such as gamma and VCOM are set through the I<sup>2</sup>C interface. Real-time functions, such as the switching of the gamma and VCOM, are done through the dedicated logic input signal BKSEL.

#### Programmable Reference

The IC has an internal programmable reference, which when referred to the output, has a full-scale voltage of 20V (±0.1%). The reference voltage is calculated using the following equation:

$V_{PREF} = (20V \times CODE)/2^{N}$

where CODE is the numeric value stored in register address and N is the bits of resolution. For the IC, N = 10 and CODE ranges from 0 to 1023.

Note that VPREF cannot be 20V because the maximum value of CODE is always one LSB less than the full-scale voltage. When the programmable reference code is 1023, then VPREF is:

$V_{PREF} = (20V \times 1023)/2^{10} = 19.98V$

#### 10-Bit Digital-to-Analog Converters

VPREF sets the full-scale output of the DACs. Determine the output voltages using the following equations:

$V_{GMA} = (V_{PREF} \times CODE)/2^{N}$  $V_{VCOM} = (V_{PREF} \times CODE)/2^{N}$

where CODE is the numeric value of the DAC's binary input code and N is the bits of resolution. For the IC, N = 10 and CODE ranges from 0 to 1023.

Note that the DAC can never output VPREF because the maximum value of CODE is always one LSB less than the reference. For example, if VPREF = 16V and the DAC CODE is 1023, then the gamma output voltage is:

$V_{GMA} = (16V \times 1023)/2^{10} = 15.98438V$

#### **Gamma Buffers**

The gamma buffers can typically source or sink 4mA of DC current within 200mV of the supplies.

The source drivers can kick back a great deal of current to the buffer outputs during a horizontal line change or a polarity switch. The DAC output buffers can source/sink 200mA of peak transient current to reduce the recovery time of the output voltages when critical levels and patterns are displayed.

#### **VCOM Amplifier**

The operational amplifier attached to the VCOM DAC holds the VCOM voltage stable while providing the ability to source and sink 600mA into the backplane of a TFT-LCD panel. The operational amplifier can directly drive the capacitive load of the TFT-LCD backplane without the need for a series resistor in most cases. The VCOM amplifier has current limiting on its output to protect its bond wires.

If the application requires more than 600mA, buffer the output of the VCOM amplifier with a MAX9650, a VCOM power amplifier. The MAX9650 can source or sink 1.3A of current.

### **Switching Gamma and VCOM**

The IC can keep two independent sets of gamma and VCOM codes in volatile memory ( ).

The BKSEL signal determines which set of gamma and VCOM codes is driven out (Table 2).

### Multiple-Time Programmable (MTP) Memory

MTP memory, which is a form of nonvolatile memory, stores the DAC code values even when the chip is not powered. When the chip is powered up, the code values are automatically transferred from MTP memory to the I<sup>2</sup>C registers. See the *Power-On Reset (POR)/Power-Up* section for more details. The user can program DAC codes into MTP memory up to 100 times.

#### Power-On Reset (POR)/Power-Up

The POR circuit that monitors DVDD ensures that all I<sup>2</sup>C registers are reset to their MTP values upon power-up or POR. Once DVDD rises above 2.4V (typ), the POR circuit releases the I<sup>2</sup>C registers and the values stored in MTP are loaded. To ensure proper MTP loading at POR, the DVDD ramp-up needs to be within 25ms from 1.5V to 2.4V. Should DVDD drop to less than 1.5V typical, then the contents of the registers can no longer be guaranteed and a reset is generated. When DVDD rises back above the POR voltage, the values stored in MTP are loaded back into the I<sup>2</sup>C registers. The transfer time of the MTP registers to I<sup>2</sup>C registers is 300µs typical and is less than 400µs in the worst case. During this time, AVDD should not be powered up, and the I<sup>2</sup>C does

Table 1. Registers in Each of the Two Independent Sets

| REGISTERS IN SET 1 | REGISTERS IN SET 2 |

|--------------------|--------------------|

| GMA1BK1            | GMA1BK2            |

| GMA2BK1            | GMA2BK2            |

| GMA3BK1            | GMA3BK2            |

| GMA4BK1            | GMA4BK2            |

| GMA5BK1            | GMA5BK2            |

| GMA6BK1            | GMA6BK2            |

| GMA7BK1            | GMA7BK2            |

| GMA8BK1            | GMA8BK2            |

| GMA9BK1            | GMA9BK2            |

| GMA10BK1           | GMA10BK2           |

| GMA11BK1           | GMA11BK2           |

| GMA12BK1           | GMA12BK2           |

| VCOM1              | VCOM2              |

| VCOM1MIN           | VCOM2MIN           |

| VCOM1MAX           | VCOM2MAX           |

not acknowledge any commands. The I<sup>2</sup>C only starts acknowledging commands after all registers have been loaded from MTP.

#### **Thermal Shutdown**

The IC features thermal-shutdown protection with temperature hysteresis. When the die temperature reaches +165°C, all of the gamma outputs and the VCOM output are disabled. When the die cools down by 15°C, the outputs are enabled again.

### **Register and Bit Descriptions**

The IC has both volatile memory and also nonvolatile MTP memory. The volatile memory structure has I<sup>2</sup>C registers and DAC registers (see the *Functional Diagram*). The I<sup>2</sup>C master must first write data into the I<sup>2</sup>C registers of the IC before the data can be moved into the DAC registers (or MTP memory). The advantage of having the I<sup>2</sup>C registers serve as a data buffer for the IC is that data can be transferred in a parallel operation from the I<sup>2</sup>C registers to the DAC registers, and so the entire gamma curve is essentially updated instantaneously rather than serially on a point-by-point basis.

The volatile memory stores two independent sets of gamma curves and VCOM codes. The first set consists of gamma codes from bank 1, VCOM1 code, VCOM1MIN code, and VCOM1MAX code. The second set consists of gamma codes from bank 2, VCOM2 code, VCOM2MIN code, and VCOM2MAX code. In addition, volatile memory stores the programmable reference code.

Table 2. BKSEL Logic Table

| OUTPUT | BKSEL = LOW | BKSEL = HIGH |

|--------|-------------|--------------|

| GMA1   | GMA1BK1     | GMA1BK2      |

| GMA2   | GMA2BK1     | GMA2BK2      |

| GMA3   | GMA3BK1     | GMA3BK2      |

| GMA4   | GMA4BK1     | GMA4BK2      |

| GMA5   | GMA5BK1     | GMA5BK2      |

| GMA6   | GMA6BK1     | GMA6BK2      |

| GMA7   | GMA7BK1     | GMA7BK2      |

| GMA8   | GMA8BK1     | GMA8BK2      |

| GMA9   | GMA9BK1     | GMA9BK2      |

| GMA10  | GMA10BK1    | GMA10BK2     |

| GMA11  | GMA11BK1    | GMA11BK2     |

| GMA12  | GMA12BK1    | GMA12BK2     |

| VCOM   | VCOM1       | VCOM2        |

The nonvolatile MTP memory stores all the data except for the second set of gamma curves and VCOM codes. During power-up, the codes in the MTP memory are transferred into the I<sup>2</sup>C and DAC registers.

Each memory location whether in nonvolatile or volatile memory holds a 10-bit word. Two bytes must be read or written through the I<sup>2</sup>C interface for every register. Table 3 shows the register map. The same register address and register name exists in the MTP memory bank, I<sup>2</sup>C register bank, and the DAC register bank. The write

control bits determine into which memory location the data is stored.

#### **Register Description**

Only the 10 least significant bits (LSBs) are written to the registers (Table 4). During a write operation, the write control bits (the two MSBs) are stripped from the incoming data stream and are used to determine whether the MTP or DAC registers are updated (Table 5). Note the I<sup>2</sup>C registers are only 10 bits.

Table 3. Register Map

| REGISTER<br>ADDRESS | REGISTER<br>NAME | REGISTER DESCRIPTION | POWER-ON<br>RESET VALUE | MTP FACTORY INITIALIZATION VALUE |

|---------------------|------------------|----------------------|-------------------------|----------------------------------|

| 0x00                | GMA1BK1          | Gamma 1 of Bank 1    | 0x200                   | 0x200                            |

| 0x01                | GMA2BK1          | Gamma 2 of Bank 1    | 0x200                   | 0x200                            |

| 0x02                | GMA3BK1          | Gamma 3 of Bank 1    | 0x200                   | 0x200                            |

| 0x03                | GMA4BK1          | Gamma 4 of Bank 1    | 0x200                   | 0x200                            |

| 0x04                | GMA5BK1          | Gamma 5 of Bank 1    | 0x200                   | 0x200                            |

| 0x05                | GMA6BK1          | Gamma 6 of Bank 1    | 0x200                   | 0x200                            |

| 0x06                | GMA7BK1          | Gamma 7 of Bank 1    | 0x200                   | 0x200                            |

| 0x07                | GMA8BK1          | Gamma 8 of Bank 1    | 0x200                   | 0x200                            |

| 0x08                | GMA9BK1          | Gamma 9 of Bank 1    | 0x200                   | 0x200                            |

| 0x09                | GMA10BK1         | Gamma 10 of Bank 1   | 0x200                   | 0x200                            |

| 0x0A                | GMA11BK1         | Gamma 11 of Bank 1   | 0x200                   | 0x200                            |

| 0x0B                | GMA12BK1         | Gamma 12 of Bank 1   | 0x200                   | 0x200                            |

| 0x0C                | Reserved         | _                    | 0x000                   | _                                |

| 0x0D                | Reserved         | _                    | 0x000                   | _                                |

| 0x0E                | Reserved         | _                    | 0x000                   | _                                |

| 0x0F                | Reserved         | _                    | 0x000                   | _                                |

| 0x10                | Reserved         | _                    | 0x000                   | _                                |

| 0x11                | Reserved         | _                    | 0x000                   | _                                |

| 0x12                | VCOM1            | Common voltage 1     | 0x200                   | 0x200                            |

| 0x13                | Reserved         | _                    | 0x000                   | _                                |

| 0x14                | Reserved         | _                    | 0x000                   | _                                |

| 0x15                | Reserved         | _                    | 0x000                   | _                                |

| 0x16                | Reserved         | _                    | 0x000                   | _                                |

| 0x17                | Reserved         | _                    | 0x000                   | _                                |

| 0x18                | VCOM1MIN         | Minimum VCOM1 value  | 0x000                   | 0x000                            |

| 0x19                | VCOM1MAX         | Maximum VCOM1 value  | 0x3FF                   | 0x3FF                            |

| 0x1A                | Reserved         | _                    | 0x000                   | _                                |

| 0x1B                | Reserved         | _                    | 0x000                   | _                                |

| 0x1C                | Reserved         | _                    | 0x000                   | _                                |

| 0x1D                | Reserved         | _                    | 0x000                   | _                                |

| 0x1E                | Reserved         |                      | 0x000                   | _                                |

**Table 3. Register Map (continued)**

| REGISTER<br>ADDRESS | REGISTER<br>NAME | REGISTER DESCRIPTION           | POWER-ON<br>RESET VALUE | MTP FACTORY INITIALIZATION VALUE |

|---------------------|------------------|--------------------------------|-------------------------|----------------------------------|

| 0x1F                | VPREF            | Programmable reference voltage | 0x200                   | 0x200                            |

| 0x20                | GMA1BK2          | Gamma 1 of Bank 2              | 0x200                   |                                  |

| 0x21                | GMA2BK2          | Gamma 2 of Bank 2              | 0x200                   |                                  |

| 0x22                | GMA3BK2          | Gamma 3 of Bank 2              | 0x200                   |                                  |

| 0x23                | GMA4BK2          | Gamma 4 of Bank 2              | 0x200                   |                                  |

| 0x24                | GMA5BK2          | Gamma 5 of Bank 2              | 0x200                   |                                  |

| 0x25                | GMA6BK2          | Gamma 6 of Bank 2              | 0x200                   |                                  |

| 0x26                | GMA7BK2          | Gamma 7 of Bank 2              | 0x200                   |                                  |

| 0x27                | GMA8BK2          | Gamma 8 of Bank 2              | 0x200                   |                                  |

| 0x28                | GMA9BK2          | Gamma 9 of Bank 2              | 0x200                   |                                  |

| 0x29                | GMA10BK2         | Gamma 10 of Bank 2             | 0x200                   |                                  |

| 0x2A                | GMA11BK2         | Gamma 11 of Bank 2             | 0x200                   |                                  |

| 0x2B                | GMA12BK2         | Gamma 12 of Bank 2             | 0x200                   |                                  |

| 0x2C                | VCOM2            | Common voltage 2               | 0x200                   |                                  |

| 0x2D                | VCOM2MIN         | Minimum VCOM2 value            | 0x000                   |                                  |

| 0x2E                | VCOM2MAX         | Maximum VCOM2 value            | 0x3FF                   |                                  |

**Table 4. Register Description**

|          |             |     | _   |     |     |     |     |    |    |    |    |    |    |    |    |    |    |

|----------|-------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| REG      | REG<br>ADDR | B15 | B14 | B13 | B12 | B11 | B10 | В9 | В8 | В7 | В6 | В5 | В4 | В3 | B2 | B1 | ВО |

| GMA1BK1  | 0x00        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA2BK1  | 0x01        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA3BK1  | 0x02        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA4BK1  | 0x03        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA5BK1  | 0x04        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA6BK1  | 0x05        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA7BK1  | 0x06        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA8BK1  | 0x07        | W1  | WO  | Χ   | Χ   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA9BK1  | 0x08        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA10BK1 | 0x09        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA11BK1 | 0x0A        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA12BK1 | 0x0B        | W1  | WO  | Х   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| Reserved | 0x0C        | _   | _   | _   | _   | _   | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| Reserved | 0x0D        | _   | _   | _   | _   | _   | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| Reserved | 0x0E        | _   | _   | _   | _   | _   | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| Reserved | 0x0F        | _   | _   | _   | _   |     | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| Reserved | 0x10        | _   |     |     |     |     |     | _  | _  | _  |    |    |    | _  |    |    | _  |

| Reserved | 0x11        | _   |     | _   | _   | _   | _   | _  | _  |    |    | _  |    |    |    | _  |    |

| VCOM1    | 0x12        | W1  | WO  | Χ   | Х   | Х   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

**Table 4. Register Description (continued)**

| REG      | REG<br>ADDR | B15 | B14 | B13 | B12 | B11 | B10 | В9 | В8 | В7 | В6 | В5 | В4 | В3 | B2 | B1 | В0 |

|----------|-------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Reserved | 0x13        | _   | _   | _   | _   | _   | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| Reserved | 0x14        | _   | _   | _   | _   | _   | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| Reserved | 0x15        | _   | _   | _   | _   | _   | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| Reserved | 0x16        | _   | _   |     | _   | _   | _   | _  | _  | _  | _  |    |    |    | _  | _  | _  |

| Reserved | 0x17        | _   | _   |     | _   | _   | _   | _  | _  | _  | _  | _  | _  | _  | _  | _  | _  |

| VCOM1MIN | 0x18        | W1  | W0  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| VCOM1MAX | 0x19        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| Reserved | 0x1A        | _   | _   |     | _   | _   | _   | _  | _  | _  | _  |    | _  |    | _  | _  |    |

| Reserved | 0x1B        |     |     | I   |     | _   | _   | _  | _  | _  | _  | l  | l  |    | l  | _  | _  |

| Reserved | 0x1C        | _   | _   |     | _   | _   | _   | _  | _  | _  | _  |    |    | _  |    | _  | _  |

| Reserved | 0x1D        |     |     | I   | _   | _   | _   | _  | _  | _  | _  |    | -  |    | -  | _  | _  |

| Reserved | 0x1E        | _   | _   |     | _   | _   | _   | _  | _  | _  | _  |    | _  | _  | _  | _  | _  |

| VPREF    | 0x1F        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA1BK2  | 0x20        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA2BK2  | 0x21        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA3BK2  | 0x22        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA4BK2  | 0x23        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA5BK2  | 0x24        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA6BK2  | 0x25        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA7BK2  | 0x26        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA8BK2  | 0x27        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA9BK2  | 0x28        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA10BK2 | 0x29        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA11BK2 | 0x2A        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| GMA12BK2 | 0x2B        | W1  | W0  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| VCOM2    | 0x2C        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| VCOM2MIN | 0x2D        | W1  | WO  | Χ   | Χ   | Χ   | Х   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| VCOM2MAX | 0x2E        | W1  | WO  | Χ   | Χ   | Χ   | Χ   | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

**Table 5. Write Control Bits**

| W1 | W0 | ACTION                                                                                                                                                  |

|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | No update.                                                                                                                                              |

| 0  | 1  | MTP registers get updated when the current I <sup>2</sup> C register has finished updating. See the <i>Nonvolatile Memory</i> section for more details. |

| 1  | 0  | All DAC registers get updated when the current I <sup>2</sup> C register has finished updating (end of B0).                                             |

| 1  | 1  | No update.                                                                                                                                              |

### VCOM Programmable Range (VCOMMIN and VCOMMAX)

The IC features a programmable range for VCOM1 and VCOM2. VCOM1MIN and VCOM1MAX registers provide low and high limits for the VCOM1 register. At the factory, VCOM1MIN is set to 0 and VCOM1MAX is set to 1023 (default values) to provide the full rail-to-rail programmable range for VCOM1. Later, the user can define their own limits by programming VCOM1MIN and VCOM1MAX registers and MTP.

VCOM1 register values are limited to the defined range. If the VCOM1 register accidentally gets programmed with a value higher than VCOM1MAX, it automatically gets locked to the VCOM1MAX value. The I<sup>2</sup>C bus does acknowledge and receive the data sent on the bus; however, internally the part recognizes that the value is outside of the range and adjusts it accordingly. The same scenario is true if the value programming VCOM1 is below VCOM1MIN.

VCOM2MIN and VCOM2MAX have a similar relationship with VCOM2.

#### Memory

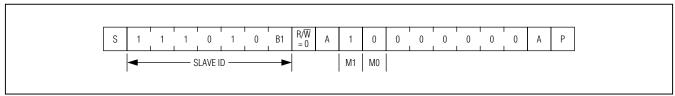

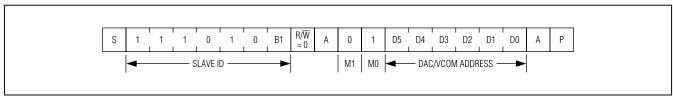

The IC includes both volatile memory (I<sup>2</sup>C registers and DAC registers) and nonvolatile memory (MTP registers). It is possible to write to each single volatile memory register from a MTP register individually or to write to all at once through memory write bits (M1, M0), which are the

two MSBs of the register address byte. Table 6 shows the memory write bits. Set both M1 and M0 to low or high when writing to or reading from the I<sup>2</sup>C registers through the I<sup>2</sup>C bus.

#### **Volatile Memory**

The IC features a double-buffered register structure with the I<sup>2</sup>C registers as the first buffer and the DAC registers as the second buffer. The benefit is that the I<sup>2</sup>C registers can be updated without updating the DAC registers. After the I<sup>2</sup>C registers have been updated, the value or values in the I<sup>2</sup>C registers can be transferred all at the same time to the DAC registers.

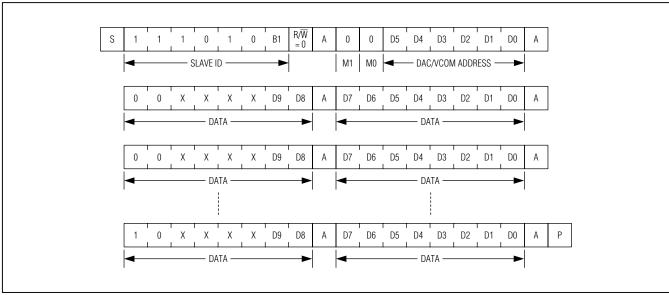

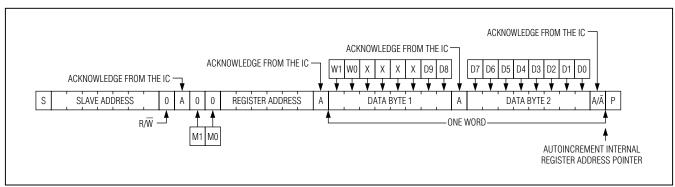

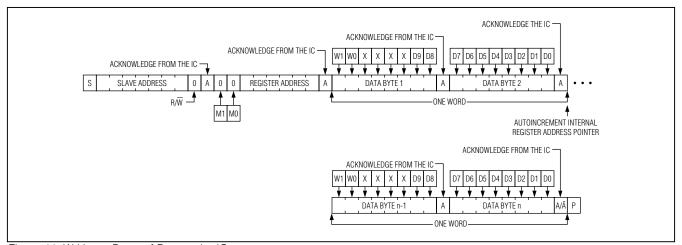

Figure 1 shows how to program a single DAC register. The output voltage is updated after sending LSB (D0). It is possible to write to multiple I2C registers first, then update the output voltage of all channels simultaneously, as shown in Figure 2. In this mode, it is possible for the I2C master to write to all registers of the IC (gamma, VCOM, and programmable reference) in one communication. In that case, the value programmed on addresses 0x0C-0x11, 0x13-0x17, 0x1A-0x1E, and 0x20-0x2E are meaningless. However, the IC does send an acknowledge bit for each of the two bytes on any of these addresses. The control bits (W1, W0) shown in Figure 12 are set in a way that all DACs are programmed to their desired value with no changes to the output voltages until the LSB of the last DAC is received and then all the channels update simultaneously.

**Table 6. Memory Write Bits**

| M1 | МО | ACTION                                                                                     |

|----|----|--------------------------------------------------------------------------------------------|

| 0  | 0  | None.                                                                                      |

| 0  | 1  | Only the addressed I <sup>2</sup> C registers and DAC registers get set to the MTP values. |

| 1  | 0  | All I2C registers and DAC registers get set to the MTP values.                             |

| 1  | 1  | None.                                                                                      |

Figure 1. Single DAC Programming

Figure 2. Multiple (or All) DACs Programming

#### **Nonvolatile Memory**

The IC is able to write to nonvolatile memory (MTP) of any single DAC/VCOM register in a single or burst I<sup>2</sup>C transaction. This memory can be written to at least 100 times.

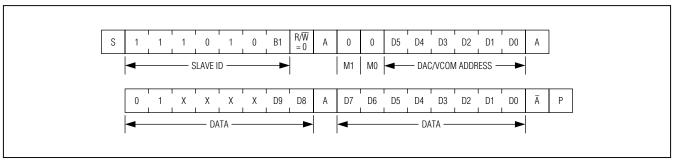

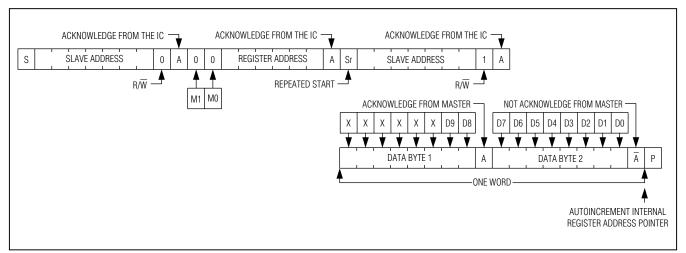

Figure 3 shows a single write to a MTP address. The control bits are set in a way that the MTP register is updated at the end of LSB (D0).

Figure 4 shows how to program multiple MTP registers in one communication transition. Similar to programming the volatile memory, the first 2 bytes of data correspond to the DAC/VCOM address specified by the master on the previous byte and the following 2 bytes of data correspond to the next address and so on. In this configuration, all the MTP registers are programmed at the same time following the LSB of the last set of data byte. The last set of data bytes is different than the previous bytes because bit 15 and bit 14 are 0b0 and 0b1, respectively. If, for some reason, the master issues a stop condition before sending the last two bytes of the data with appropriate values of bit 15 (0b0) and bit 14 (0b1), then none of the MTP registers are updated.

Programming the MTP registers also updates the DAC registers and consequently the output voltages. Similar to multiple volatile memory programming, the update

only occurs after the LSB of the last byte is received. All the outputs are programmed and updated simultaneously; however, depending on the number of MTP registers: it takes 31ms to 500ms to store the values into the nonvolatile memory. During this time, the IC is not available on the I<sup>2</sup>C bus and any communication from the master should be delayed until the MTP is programmed. Any attempt from the I<sup>2</sup>C master to talk to the IC is not acknowledged.

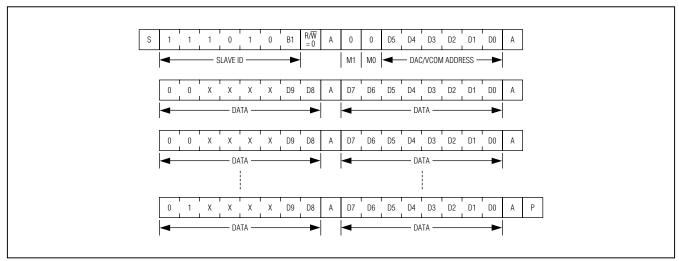

#### **General and Single Acquire Commands**

It is possible to update all the DAC outputs to the previously stored MTP values with one special command. Set the 2 MSB bits (M1 and M0) of the register address to 0b10 to set all the I $^2$ C registers, DAC registers and the output voltages to the values of MTP (Figure 5).

The IC ignores the rest of the register address in this case.

It is also possible to update the I<sup>2</sup>C register, DAC register and DAC output voltage of only one channel from the MTP. Set the 2 MSB bits (M1 and M0) of the DAC/VCOM address to 0b01 (Figure 6) to move a specific value from MTP into the I<sup>2</sup>C register and DAC register of a single channel.

Figure 3. Single MTP Programming

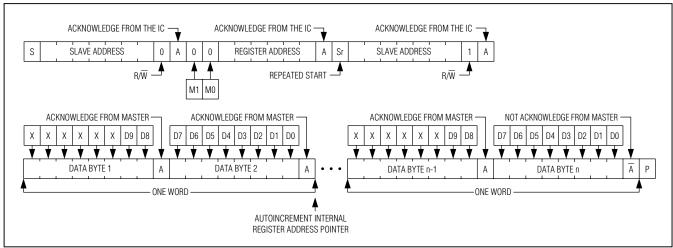

Figure 4. Multiple MTP Programming

Figure 5. General Acquire Command to Updated All Outputs with MTP

Figure 6. Single Acquire Command to Updated One Output with MTP

Figure 7. I<sup>2</sup>C Interface Timing Diagram

#### I2C Serial Interface

The IC features an I2C/SMBus™-compatible, 2-wire serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate communication between the devices and the master at clock rates up to 1MHz. Figure 7 shows the 2-wire interface timing diagram. The master generates SCL and initiates data transfer on the bus. A master device writes data to the devices by transmitting the proper slave address followed by the register address and then the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted to the MAX9679B is 8 bits long and is followed by an acknowledge clock pulse. A master reading data from the devices transmits the proper slave address followed by a series of nine SCL pulses. The devices transmit data on SDA in sync with the master-generated SCL pulses. The master acknowledges receipt of each byte of data. Each read sequence is framed by a START (S) or REPEATED START (Sr) condition, a not acknowledge, and a STOP (P) condition. SDA operates as both an input and an open-drain output. A pullup resistor, typically greater than  $500\Omega$ , is required on the SDA bus. SCL operates as only an input. A pullup resistor, typically greater than  $500\Omega$ , is required on SCL if there are multiple masters on the bus, or if the master in a single-master system has an open-drain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the devices from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

#### Bit Transfer

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals. See the *START and STOP Conditions* section. SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

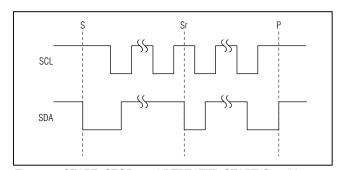

#### **START and STOP Conditions**

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START (S) condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP (P) condition is a low-to-high transition on SDA while SCL is high (Figure 8).

A START condition from the master signals the beginning of a transmission to the IC. The master terminates transmission, and frees the bus, by issuing a STOP condition. The bus remains active if a REPEATED START (Sr) condition is generated instead of a STOP condition.

Figure 8. START, STOP, and REPEATED START Conditions

#### **Early STOP Conditions**

The IC recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition. For proper operation, do not send a STOP condition during the same SCL high pulse as the START condition.

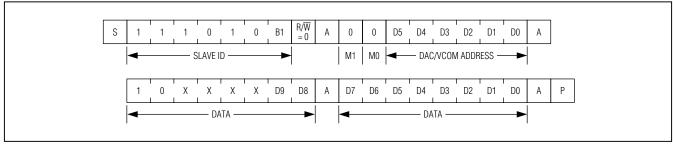

#### Slave Address

The slave address is defined as the 7 most significant bits (MSBs) followed by the read/write (R/W) bit. Set the R/W bit to 1 to configure the IC to read mode. Set the R/W bit to 0 to configure the IC to write mode. The address is the first byte of information sent to the IC after the START condition. The IC's slave address is configured with A0. Table 7 shows the possible addresses for the IC.

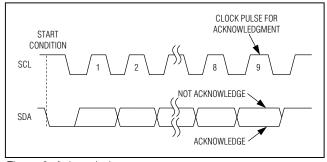

#### **Acknowledge**

The acknowledge bit (ACK) is a clocked 9th bit that the IC uses to handshake receipt of each byte of data when in write mode (Figure 9).

#### **Table 7. Slave Address**

| Α0   | READ ADDRESS   | WRITE ADDRESS  |

|------|----------------|----------------|

| AGND | E9h (11101001) | E8h (11101000) |

| DVDD | EBh (11101011) | EAh (11101010) |

Figure 9. Acknowledge

The IC pulls down SDA during the entire master-generated ninth clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master may retry communication. The master pulls down SDA during the ninth clock cycle to acknowledge receipt of data when the IC is in read mode. An acknowledge is sent by the master after each read byte to allow data transfer to continue. A not acknowledge is sent when the master reads the final byte of data from the IC, followed by a STOP condition.

#### **Write Data Format**

A write to the IC consists of transmitting a START condition, the slave address with the R/W bit set to 0, one data byte of data to configure the internal register address pointer, one word (2 bytes) of data or more, and a STOP condition.

Figure 10 illustrates the proper frame format for writing one word of data to the IC. Figure 11 illustrates the frame format for writing n-bytes of data to the IC.

The slave address with the R/W bit set to 0 indicates that the master intends to write data to the IC. The IC acknowledges receipt of the address byte during the master-generated 9th SCL pulse.

The second byte transmitted from the master configures the IC's internal register address pointer. The IC's internal address pointer consists of the six least significant bits (LSB) of the second byte. The 2 MSBs of the second byte (M1 and M0) are set to 00b when writing to the internal registers. See the *Memory* section for more details. The pointer tells the IC where to write the next byte of data. An acknowledge pulse is sent by the IC upon receipt of the address pointer data when writing to the

Figure 10. Writing a Word of Data to the IC

DAC registers. When writing to the MTP, a not acknowledge is sent from the IC after the master writes the final byte of data, followed by a STOP condition.

The third and fourth bytes sent to the IC contain the data that is written to the chosen register and which type of register it writes to, volatile (DAC) or nonvolatile memory (MTP). See the *Nonvolatile Memory* section for more details. An acknowledge pulse from the IC signals receipt of each data byte. The address pointer autoincrements to the next register address after receiving every other data byte. This autoincrement feature allows a master to write to sequential register address locations within one continuous frame. The master signals the end of transmission by issuing a STOP condition. If data is written into register address 0x2E, the address pointer

autoincrements to 0xFF and stays at 0xFF until the master writes a new value into the register address pointer.

#### **Read Data Format**

The master presets the address pointer by first sending the IC's slave address with the R/W bit set to 0 followed by the register address with M1 and M0 set to 00 after a START condition. The IC acknowledges receipt of its slave address and the register address by pulling SDA low during the 9th SCL clock pulse. A REPEATED START condition is then sent followed by the slave address with the R/W bit set to 1. The IC transmits the contents of the specified register. Transmitted data is valid on the rising edge of the master-generated serial clock (SCL). The address pointer autoincrements after every other read

Figure 11. Writing n-Bytes of Data to the IC

Figure 12. Reading One Indexed Word of Data from the IC

Figure 13. Reading n Bytes of Indexed Data from the IC

data byte. This autoincrement feature allows all registers to be read sequentially within one continuous frame. A STOP condition can be issued after any number of read data bytes. If a STOP condition is issued followed by another read operation, the first data byte to be read is from the register address location set by the previous transaction and not 0x00, and subsequent reads autoincrement the address pointer until the next STOP condition. Attempting to read from register addresses higher than 0x2E results in repeated reads from a dummy register containing all one data. The master acknowledges receipt of each read byte during the acknowledge clock pulse. The master must acknowledge all correctly received bytes except the last byte. The final byte must be followed by a not acknowledge from the master and then a STOP condition. Figure 12 and Figure 13 illustrate the frame format for reading data from the IC.

### Applications Information

#### **Power Sequencing**

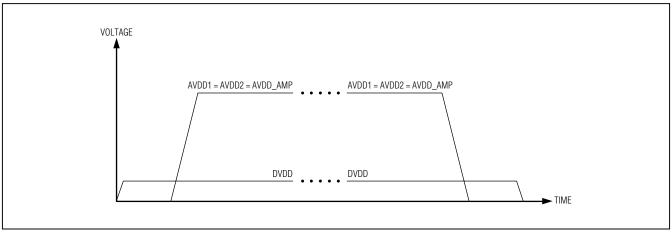

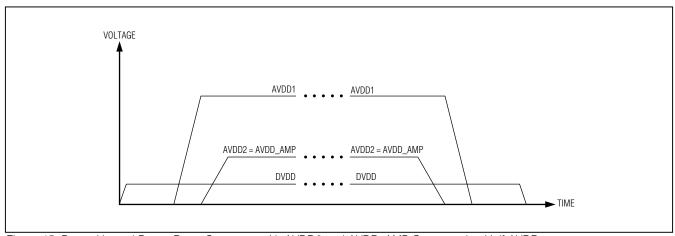

AVDD1, AVDD2, AVDD\_AMP, and DVDD are independent of each other and can be powered up and powered down in any sequence. However, output voltages are only guaranteed to power up in a well-behaved manner when DVDD is powered up first and powered down last (Figure 14 and Figure 15). Connecting AVDD2 and AVDD\_AMP to half AVDD supply reduces the temperature of the IC.

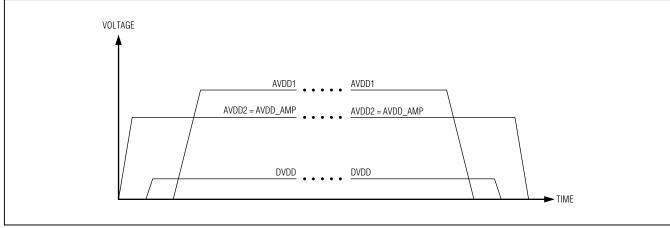

If AVDD2 and AVDD\_AMP are connected to the 12V supply to the LCD module because a half AVDD supply is not available, then Figure 16 shows the power-up and

power-down sequence. The gamma and VCOM outputs are close to ground until AVDD1 is greater than its power-on reset voltage because AVDD1 is used to power the internal voltage reference.

#### **PCB Layout and Grounding**

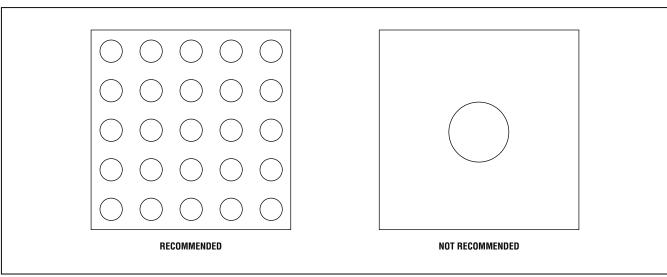

If the IC is mounted using reflow soldering or waver soldering, the ground vias for the exposed pad should have a finished hole size of at least 14 mils to ensure adequate wicking of soldering onto the exposed pad. If the IC is mounted using solder mask technique, the vias requirement does not apply. In either case, the exposed pad on the TQFN package is electrically connected to both digital and analog grounds through a low thermal resistance path to ensure adequate heat dissipation. Do not route traces under these packages. The layout of the exposed pad should have multiple small vias over a single large via as shown in Figure 17.

Thermal resistance between top and ground layers can be optimized with multiple small vias, and it is recommended to have a plated via with 15 mils diameter. The via should be flooded with solder for good thermal performance.

#### **Power-Supply Bypassing**

The IC operates from a single 9V to 20V analog supply (AVDD) and a 2.7V to 3.6V digital supply (DVDD). Bypass AVDD to AGND with 0.1 $\mu$ F and 10 $\mu$ F capacitors in parallel. Use an extensive ground plane to ensure optimum performance. Bypass DVDD to AGND with a 0.1 $\mu$ F capacitor. The 0.1 $\mu$ F bypass capacitors should be as close as possible to the device. Refer to the MAX9679B Evaluation Kit for a proven PCB layout.

Figure 14. Conventional Power-Up and Power-Down Sequence

Figure 15. Power-Up and Power-Down Sequence with AVDD2 and AVDD\_AMP Connected to Half AVDD

Figure 16. Power-Up and Power-Down Sequence with AVDD2 and AVDD\_AMP Connected to 12V

Figure 17. Multiple Small Vias are Recommended over a Single Large Via in the PCB Layout

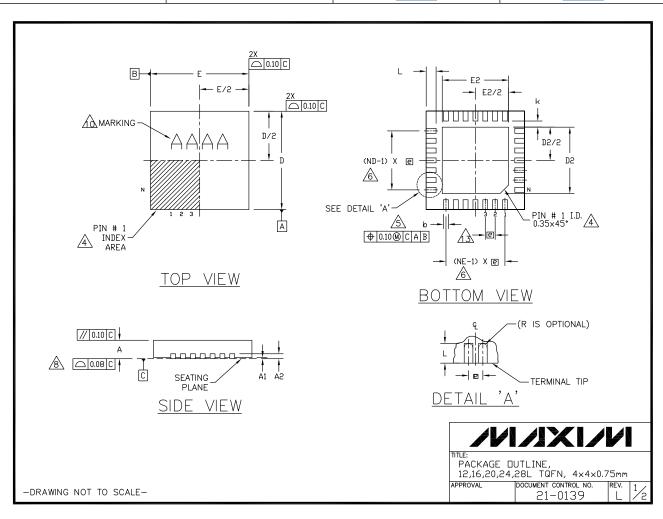

### **Package Information**

For the latest package outline information and land patterns (footrprints), go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | PACKAGE CODE | LAND PATTERN NO. |

|--------------|--------------|--------------|------------------|

| 24 TQFN      | T2444M+1     | 21-0139      | 90-0068          |

### Package Information (continued)

For the latest package outline information and land patterns (footrprints), go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

|               |            |           |      |           | CDN    | 1MDN      | DIM     | IENS      | IDNS |         |           |      |          |      |      |

|---------------|------------|-----------|------|-----------|--------|-----------|---------|-----------|------|---------|-----------|------|----------|------|------|

| PKG           | G 12L 4×4  |           |      | 16L 4×4   |        |           | 20L 4×4 |           |      | 24L 4×4 |           |      | 28L 4×4  |      |      |

| REF.          | MIN.       | NDM.      | MAX. | MIN.      | NDM.   | MAX.      | MIN.    | N□M.      | MAX. | MIN.    | N□M.      | MAX. | MIN.     | N□M. | MAX. |

| Α             | 0.70       | 0.75      | 0.80 | 0.70      | 0.75   | 0.80      | 0.70    | 0.75      | 0.80 | 0.70    | 0.75      | 0.80 | 0.70     | 0.75 | 0.80 |

| A1            | 0.0        | 0.02      | 0.05 | 0.0       | 0.02   | 0.05      | 0.0     | 0.02      | 0.05 | 0.0     | 0.02      | 0.05 | 0.0      | 0.02 | 0.05 |

| A2            | 2 0.20 REF |           |      | 0         | .20 RE | F         | 0       | .20 RE    | F    | 0       | 20 RE     | F    | 0.20 REF |      |      |

| b             | 0.25       | 0.30 0.35 |      | 0.25      | 0.30   | 0.35      | 0.20    | 0.25      | 0.30 | 0.18    | 0.23      | 0.30 | 0.15     | 0.20 | 0.25 |

| D             | 3.90       | 4.00      | 4.10 | 3.90      | 4.00   | 4.10      | 3.90    | 4.00      | 4.10 | 3.90    | 4.00      | 4.10 | 3.90     | 4.00 | 4.10 |

| Ε             | 3.90       | 4.00      | 4.10 | 3.90      | 4.00   | 4.10      | 3.90    | 4.00      | 4.10 | 3.90    | 4.00      | 4.10 | 3.90     | 4.00 | 4.10 |

| е             | (          | .80 BS    | C.   | 0.65 BSC. |        | 0.50 BSC. |         | 0.50 BSC. |      |         | 0.40 BSC. |      |          |      |      |

| k             | 0.25       | -         | -    | 0.25      | -      | -         | 0.25    | -         | -    | 0.25    | -         | -    | 0.25     | -    | -    |

| L             | 0.45       | 0.55      | 0.65 | 0.45      | 0.55   | 0.65      | 0.45    | 0.55      | 0.65 | 0.30    | 0.40      | 0.50 | 0.30     | 0.40 | 0.50 |

| N             |            | 12        |      |           | 16     |           |         | 20        |      | 24      |           |      |          | 28   |      |

| ND            | 3          |           |      | 4         |        |           | 5       |           |      | 6       |           |      | 7        |      |      |

| NE            |            | 3         |      |           | 4      |           |         | 5         |      |         | 6         |      |          | 7    |      |

| Jedec<br>Var. | dec WGGB   |           |      |           | WGGC   |           | WGGD-1  |           |      | WGGD-2  |           |      | WGGE     |      |      |

| EXP       | EXPOSED PAD VARIATIONS |              |      |      |      |      |  |  |  |  |  |  |

|-----------|------------------------|--------------|------|------|------|------|--|--|--|--|--|--|

| PKG.      |                        | DS           |      |      | E2   |      |  |  |  |  |  |  |

| CODES     | MIN.                   | N. NOM. MAX. |      | MIN. | N□M. | MAX. |  |  |  |  |  |  |

| T1244-3   | 1.95                   | 2.10         | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |

| T1244-4   | 1.95                   | 2.10         | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |

| T1644-3   | 1.95                   | 2.10         | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |

| T1644-4   | 1.95                   | 2.10         | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |

| T2044-2   | 1.95                   | 2.10         | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |

| T2044-3   | 1.95                   | 2.10         | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |

| T2444-2   | 1.95                   | 2.10         | 2.25 | 1.95 | 2.10 | 2.25 |  |  |  |  |  |  |

| T2444-3   | 2.45                   | 2.60         | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |  |  |

| T2444-4   | 2.45                   | 2.60         | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |  |  |

| T2444N-4  | 2.45                   | 2.60         | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |  |  |

| T2444M-1  | 2.45                   | 2.60         | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |  |  |

| T2444MK-1 | 2.45                   | 2.60         | 2.63 | 2.45 | 2.60 | 2.63 |  |  |  |  |  |  |

| T2844-1   | 2.50                   | 2.60         | 2.70 | 2.50 | 2.60 | 2.70 |  |  |  |  |  |  |

| T2844N-1  | 2.65                   | 2.70         | 2.75 | 2.65 | 2.70 | 2.75 |  |  |  |  |  |  |

| DIMENSION VARIATIONS |      |      |      |      |      |      |      |      |      |  |

|----------------------|------|------|------|------|------|------|------|------|------|--|

| PKG.                 |      | D2   |      |      | E2 L |      |      |      |      |  |

| CODE                 | MIN. | NDM. | MAX. | MIN. | N□M. | MAX. | MIN. | N□M. | MAX. |  |

| T2044-4              | 2.85 | 2.90 | 2.95 | 2.85 | 2.90 | 2.95 | 0.25 | 0.30 | 0.35 |  |

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES

- N IS THE TOTAL NUMBER OF TERMINALS.

- 📤 THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND 0.30mm FROM TERMINAL TIP.

- MIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25mm AND (

ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- 8. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- 9. DRAWING CONFORMS TO JEDEC MUZZU, EXCEPT FOR LEGANMARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. COPLANARITY SHALL NOT EXCEED 0.08mm.

- WARPAGE SHALL NOT EXCEED 0.10mm.

- LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION 'e', ±0.05.

- 14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 15. MATERIAL MUST COMPLY WITH BANNED AND RESTRICTED SUBSTANCES SPEC # 10-0131.

- 16. ALL DIMENSIONS ARE THE SAME FOR LEADED (-) & PhFREE (+) PACKAGE CODES.

-DRAWING NOT TO SCALE-

PACKAGE DUTLINE 12,16,20,24,28L TQFN, 4×4×0.75mm

DOCUMENT CONTROL NO. 21-0139

### Revision History

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 8/12     | Initial release | _       |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.