# iCE65<sup>™</sup> P-Series Ultra Low-Power mobileFPGA<sup>™</sup> Family

SiliconBlue

**Data Sheet**

# April 22, 2011 (1.31)

High-density, ultra low-power single-chip, SRAM mobileFPGA family specifically designed for hand-held applications and long battery life

# Integrated Phase-Locked Loop (PLL)

- Clock multiplication/division for display, serializer/deserializer (SerDes), and memory interface applications

- Up to 533 MHz PLL Output

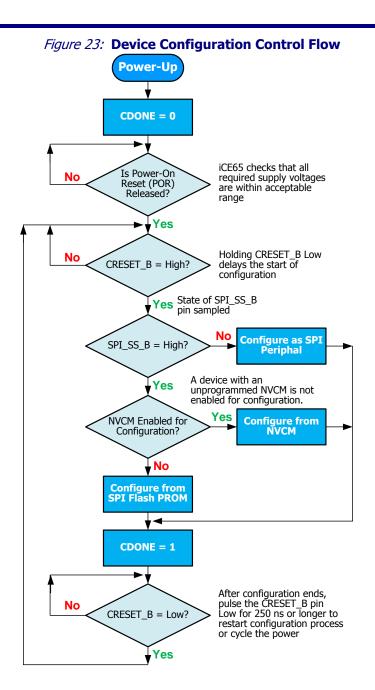

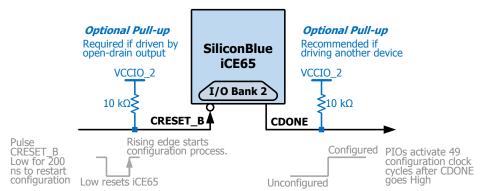

- Reprogrammable from a variety of methods and sources

- Self configuration from external, commodity SPI serial Flash PROM

- Slave configuration by a processor using SPI-like serial interface in as little as 20 us.

- Self configuration from embedded, secure Nonvolatile Configuration Memory (NVCM)

- ideal for volume production

- superior design security: no exposed data

- Proven, high-volume 65 nm, low-power CMOS technology

# Flexible programmable logic and programmable interconnect fabric

- Over 12K look-up tables (LUT4) and flip-flops

- Low-power logic and interconnect

# Flexible I/O pins to simplify system interfaces

- Up to 174 programmable I/O pins

- Four independently-powered I/O banks; support for 3.3V, 2.5V, 1.8V, and 1.5V voltage standards

- LVCMOS, MDDR, LVDS, and SubLVDS I/O standards

Plentiful, fast, on-chip 4Kbit RAM blocks

- Low-cost, space-efficient packaging options

- ◆ DiePlus<sup>™</sup> known-good die (KGD) options available

- Complete iCEcube<sup>™</sup> development system

- ♦ Windows<sup>®</sup> and Linux<sup>®</sup> support

- ◆ VHDL and Verilog logic synthesis

- Place and route software

- Design and IP core libraries

- Low-cost iCEman65P development board

# Table 1: iCE65P Ultra Low-Power Programmable Logic Family Summary

|                                  | iCE65P04 | iCE65P08 | iCE65P12 |  |  |  |

|----------------------------------|----------|----------|----------|--|--|--|

| Logic Cells (LUT + Flip-Flop)    | 3,520    |          |          |  |  |  |

| Approximate System Gate Count    | 200K     |          |          |  |  |  |

| Typical Equivalent Macrocells    | 2,700    |          |          |  |  |  |

| RAM4K Memory Blocks              | 20       |          |          |  |  |  |

| RAM4K RAM bits                   | 80K      |          |          |  |  |  |

| Phase-Locked Loops (PLLs)        | 1        |          |          |  |  |  |

| Configuration bits (maximum)     | 533 Kb   |          |          |  |  |  |

| Core Operating Current at 0 KHz  | 45 µA    |          |          |  |  |  |

| Maximum Programmable I/O Pins    | 174      |          |          |  |  |  |

| Maximum Differential Input Pairs | 20       |          |          |  |  |  |

# **Overview**

The SiliconBlue Technologies iCE65P P-Series programmable logic family is specifically designed to deliver the lowest static and dynamic power consumption of any comparable CPLD or FPGA device. iCE65P FPGAs are designed specifically for cost-sensitive, high-volume applications. iCE65P FPGA are fully user-programmable and can self-configure from a configuration image stored in on-chip, nonvolatile configuration memory (NVCM) or stored in an external commodity SPI serial Flash PROM or downloaded from an external processor over an SPI-like serial port.

The three iCE65P components, highlighted in Table 1, deliver from approximately 3,500 to 12,000 logic cells and flipflops while consuming a fraction of the power of comparable programmable logic devices. Each iCE65P device includes between 20 or more RAM blocks, each with 4Kbits of storage, for on-chip data storage and data buffering.

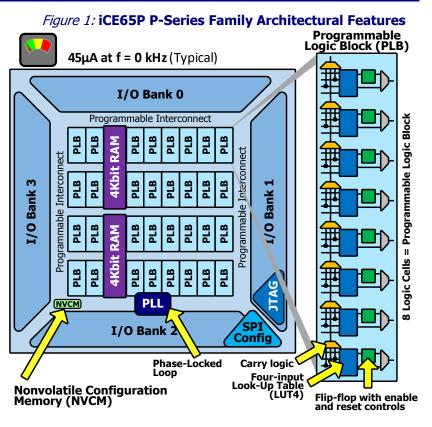

As pictured in Figure 1, each iCE65P device consists of five primary architectural elements.

- An array of Programmable Logic Blocks (PLBs)

- Each PLB contains eight Logic Cells (LCs); each Logic Cell consists of ...

- A fast, four-input look-up table (LUT4) capable of implementing any combinational logic function of up to four inputs, regardless of complexity

- A 'D'-type flip-flop with an optional clock-enable and set/reset control

- Fast carry logic to accelerate arithmetic functions such as adders, subtracters, comparators, and counters.

- Common clock input with polarity control, clock-enable input, and optional set/reset control input to the PLB is shared among all eight Logic Cells

- Two-port, 4Kbit RAM blocks (RAM4K)

- 256x16 default configuration; selectable data width using programmable logic resources

- Simultaneous read and write access; ideal for FIFO memory and data buffering applications

- RAM contents pre-loadable during configuration

- Four I/O banks with independent supply voltage, each with multiple Programmable Input/Output (PIO) blocks

- LVCMOS I/O standards and LVDS outputs supported in all banks

- ♦ I/O Bank 3 supports additional SSTL, MDDR, LVDS, and SubLVDS I/O standards

- One or more Phase-Locked Loops (PLL)

- Very low power

- Clock multiplication and division

- Phase shifting in fixed 90° increments

- Static or dynamic phase shifting

- Programmable interconnections between the blocks

- Flexible connections between all programmable logic functions

- Eight dedicated low-skew, high-fanout clock distribution networks

# **Packaging Options**

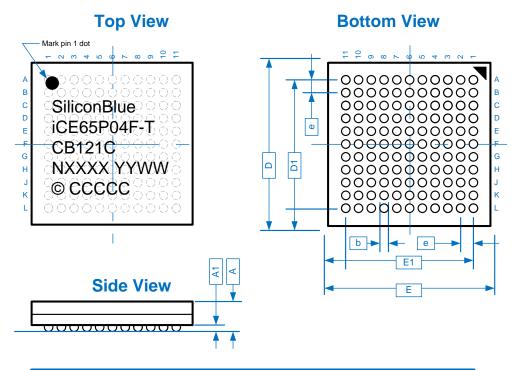

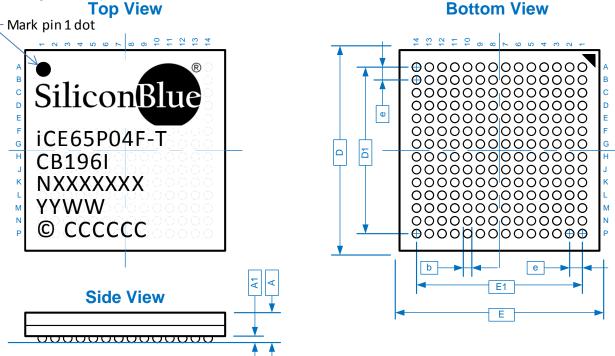

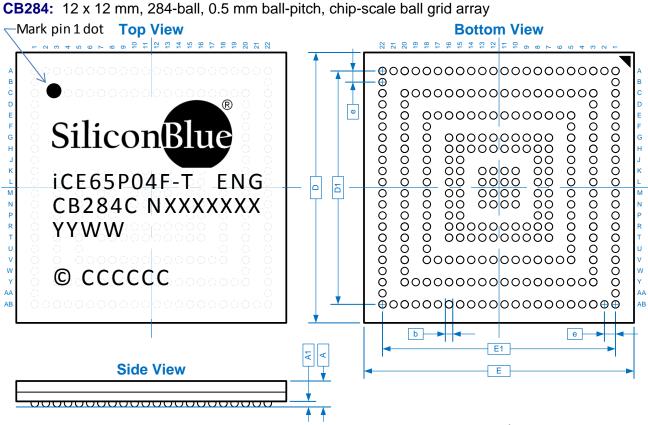

iCE65P components are available in a variety of package options to support specific application requirements. The available options, including the number of available user-programmable I/O pins (PIOs), are listed in Table 2. Fully-tested Known-Good Die (KGD) DiePlus<sup>™</sup> are available for die stacking and highly space-conscious applications. All iCE65P devices are provided exclusively in Pb-free, RoHS-compliant packages.

| Package                 | Board Area<br>(mm)    | Package<br>Code | Ball/Lead Pitch<br>(mm) | iCE65P04        | iCE65P08 | iCE65P12 |  |

|-------------------------|-----------------------|-----------------|-------------------------|-----------------|----------|----------|--|

| 121-ball chip-scale BGA | 6 x 6                 | CB121           |                         | 95 <i>(13)</i>  |          |          |  |

| 196-ball chip-scale BGA | 8 x 8                 | CB196           | 0.5                     | 148 <i>(18)</i> |          |          |  |

| 284-ball chip-scale BGA | 12 x 12               | CB284           |                         | 174 <i>(20)</i> |          |          |  |

| DiePlus known good die  | See die data<br>sheet | DI              | —                       | 174 <i>(20)</i> |          |          |  |

#### Table 2: iCE65P Family Packaging Options, Maximum I/O per Package

Feature-rich versions of the end application mount a larger iCE65P device on the circuit board. Low-end versions mount a smaller iCE65P device.

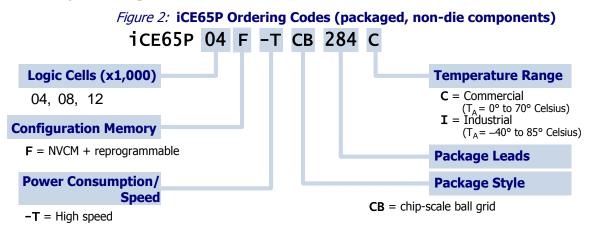

# **Ordering Information**

Figure 2 describes the iCE65P ordering codes for all packaged components. See the separate DiePlus data sheets when ordering die-based products.

iCE65P devices come standard in the higher speed "-T" version.

iCE65P devices are available in two operating temperature ranges, one for typical commercial applications, the other with an extended temperature range for industrial and telecommunications applications. The ordering code also specifies the device package option, as described further in Table 2.

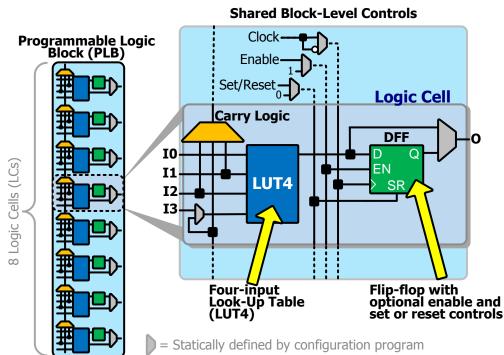

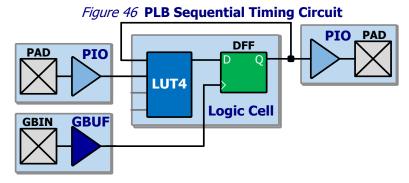

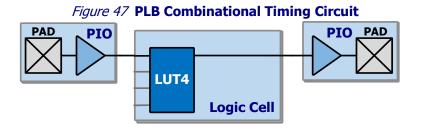

# Programmable Logic Block (PLB)

Generally, a logic design for an iCE65P component is created using a high-level hardware description language such as Verilog or VHDL. The SiliconBlue Technologies development software then synthesizes the high-level description into equivalent functions built using the programmable logic resources within each iCE65P device. Both sequential and combinational functions are constructed from an array of Programmable Logic Blocks (PLBs). Each PLB contains eight Logic Cells (LCs), as pictured in Figure 3, and share common control inputs, such as clocks, reset, and enable controls.

PLBs are connected to one another and other logic functions using the rich Programmable Interconnect resources.

# Logic Cell (LC)

Each iCE65P device contains thousands of Logic Cells (LCs), as listed in Table 1. Each Logic Cell includes three primary logic elements, shown in Figure 3.

- A four-input Look-Up Table (LUT4) builds any combinational logic function, of any complexity, of up to four inputs. Similarly, the LUT4 element behaves as a 16x1 Read-Only Memory (ROM). Combine and cascade multiple LUT4s to create wider logic functions.

- A 'D'-style Flip-Flop (DFF), with an optional clock-enable and reset control input, builds sequential logic functions. Each DFF also connects to a global reset signal that is automatically asserted immediately following device configuration.

- Carry Logic boosts the logic efficiency and performance of arithmetic functions, including adders, subtracters, comparators, binary counters and some wide, cascaded logic functions.

The output from a Logic Cell is available to all inputs to all eight Logic Cells within the Programmable Logic Block. Similarly, the Logic Cell output feeds into the **Error! Reference source not found.** fabric to connect to other eatures on the iCE65P device.

# Look-Up Table (LUT4)

The four-input Look-Up Table (LUT4) function implements any and all combinational logic functions, regardless of complexity, of between zero and four inputs. Zero-input functions include "High" (1) and "Low" (0). The LUT4 function has four inputs, labeled I0, I1, I2, and I3. Three of the four inputs are shared with the Carry Logic function, as shown in Figure 3. The bottom-most LUT4 input connects either to the I3 input or to the Carry Logic output from the previous Logic Cell.

The output from the LUT4 function connects to the flip-flop within the same Logic Cell. The LUT4 output or the flip-flop output then connects to the programmable interconnect.

For detailed LUT4 internal timing, see Table 57.

#### **'D'-style Flip-Flop (DFF)**

The 'D'-style flip-flop (DFF) optionally stores state information for the application.

# Figure 3: Programmable Logic Block and Logic Cell

The flip-flop has a data input, 'D', and a data output, 'Q'. Additionally, each flip-flop has up to three control signals that are shared among all flip-flops in all Logic Cells within the PLB, as shown in Figure 3. Table 3 describes the behavior of the flip-flop based on inputs and upon the specific DFF design primitive used or synthesized.

| Table 3: `D'-Style Flip-Flop Behavior |                                            |                       |   |     |     |        |        |

|---------------------------------------|--------------------------------------------|-----------------------|---|-----|-----|--------|--------|

| DFF                                   |                                            | Flip-Flop             |   | Inp | uts |        | Output |

| Primitive                             | Operation                                  | Mode                  | D | EN  | SR  | CLK    | Q      |

| All                                   | Cleared Immediately after<br>Configuration |                       | Х | х   | Х   | Х      | 0      |

|                                       | Hold Present Value<br>(Disabled)           | х                     | Х | 0   | Х   | Х      | Q      |

|                                       | Hold Present Value (Static<br>Clock)       |                       | Х | х   | Х   | 1 or 0 | Q      |

|                                       | Load with Input Data                       |                       | D | 1*  | 0*  | 1      | D      |

| SB_DFFR                               | Asynchronous Reset                         | Asynchronous<br>Reset | Х | х   | 1   | Х      | 0      |

| SB_DFFS                               | Asynchronous Set                           | Asynchronous<br>Set   | Х | х   | 1   | Х      | 1      |

| SB_DFFSR                              | Synchronous Reset                          | Synchronous<br>Reset  | Х | 1*  | 1   | 1      | 0      |

| SB_DFFSS                              | Synchronous Set                            | Synchronous<br>Set    | Х | 1*  | 1   | 1      | 1      |

# X = don't care, $\uparrow$ = rising clock edge (default polarity), 1\* = High or unused, 0\* = Low or unused

The CLK clock signal is not optional and is shared among all flip-flops in a Programmable Logic Block. By default, flip-flops are clocked by the rising edge of the PLB clock input, although the clock polarity can be inverted for all the flip-flops in the PLB.

The CLK input optionally connects to one of the following clock sources.

- The output from any one of the eight Global Buffers, or

- A connection from the general-purpose interconnect fabric

The EN clock-enable signal is common to all Logic Cells in a Programmable Logic Block. If the enable signal is not used, then the flip-flop is always enabled. This condition is indicated as "1\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

Similarly, the SR set/reset signal is common to all Logic Cells in a Programmable Logic Block. If not used, then the flip-flop is never set/reset, except when cleared immediately after configuration or by the Global Reset signal. This condition is indicated as "0\*" in Table 3. The asterisk indicates that this is the default state if the control signal is not connected in the application.

Each flip-flop has an additional control that defines its set or reset behavior. As defined in the configuration image, the control defines whether the set or reset operation is synchronized to the active CLK clock edge or whether it is completely asynchronous.

- The SB\_DFFR and SB\_DFFS primitives are asynchronously controlled, solely by the SR input. If the SR input is High, then an SB\_DFFR primitive is asynchronously reset and an SB\_DFFS primitive is asynchronously set.

- The SB\_DFFSR and SB\_DFFRSS primitives are synchronously controlled by both the SR input and the clock input. If the SR input is High at a rising edge of the clock input, then an SB\_DFFSR primitive is synchronously reset and an SB\_DFFSS primitive is synchronously set.

The LUT4 output or the flip-flop output then connects to the programmable interconnect.

Because of the shared control signals, the design software can pack flip-flops with common control inputs into a single PLB block, as described by Table 4. There are eight total packing options.

| Table 4: Flip-flop Packing/Sharing within a PLB |                   |                          |                                          |  |  |  |

|-------------------------------------------------|-------------------|--------------------------|------------------------------------------|--|--|--|

| Group                                           | Active Clock Edge | Clock Enable             | Set or Reset Control<br>(Sync. or Async) |  |  |  |

| 1                                               | $\uparrow$        |                          | None                                     |  |  |  |

| 2                                               | $\checkmark$      | None (always enabled)    | none                                     |  |  |  |

| 3                                               | $\uparrow$        | None (always enabled)    | PLB set/reset control                    |  |  |  |

| 4                                               | $\checkmark$      |                          | PLB set/reset control                    |  |  |  |

| 5                                               | $\uparrow$        |                          | None                                     |  |  |  |

| 6                                               | $\checkmark$      | Selective (controlled by | None                                     |  |  |  |

| 7                                               | $\uparrow$        | PLB clock enable)        | PLB set/reset control                    |  |  |  |

| 8                                               | $\checkmark$      |                          | FLD SELFESEL CONTION                     |  |  |  |

For detailed flip-flop internal timing, see Table 57.

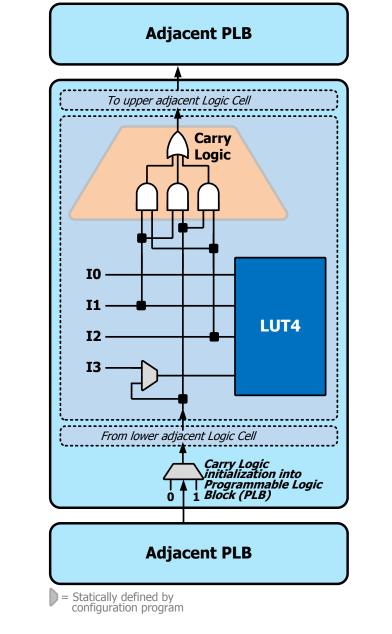

# **Carry Logic**

The dedicated Carry Logic within each Logic Cell primarily accelerates and improves the efficiency of arithmetic logic such as adders, accumulators, subtracters, incrementers, decrementers, counters, ALUs, and comparators. The Carry Logic also supports wide combinational logic functions.

$$COUT = I1 \bullet I2 + CIN \bullet I1 + CIN \bullet I2$$

[Equation 1]

Equation 1 and Figure 4 describe the Carry Logic structure within a Logic Cell. The Carry Logic shares inputs with the associated Look-Up Table (LUT4). The LUT4's II and I2 inputs directly feed the Carry Logic; inputs I0 and I3 do not. A signal cascades between Logic Cells within the Programmable Logic Block. The carry input from the previous adjacent Logic Cell optionally provides an alternate input to the LUT4 function, supplanting the I3 input.

# Low-Power Disable

To save power and prevent unnecessary signal switching, the Carry Logic function within a Logic Cell is disabled if not used. The output of a Logic Cell's Carry Logic is forced High.

# PLB Carry Input and Carry Output Connections

As shown in Figure 4, each Programmable Logic Block has a carry input signal that can be initialized High, Low, or come from the carry output signal from PLB immediately below.

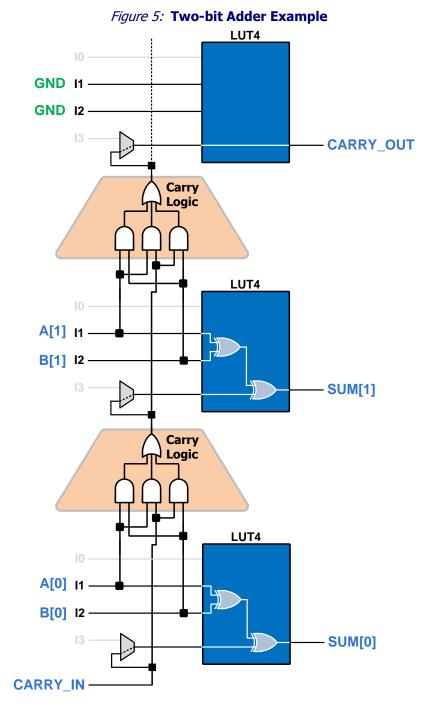

Similarly, the Carry Logic output from the Programmable Logic Block connects to the PLB immediately above, which allows the Carry Logic to span across multiple PLBs in a column. As shown in Figure 5, the Carry Logic chain can be tapped mid-way through a chain or a PLB by feeding the value through a LUT4 function.

# Adder Example

Figure 5 shows an example design that uses the Carry Logic. The example is a 2-bit adder, which can be expanded into an adder of arbitrary size. The LUT4 function within a Logic Cell is programmed to calculate the sum of the two input values and the carry input,  $A[i] + B[i] + CARRY_IN[i-1] = SUM[i]$ .

The Carry Logic generates the carry value to feed the next bit in the adder. The calculated carry value replaces the I3 input to the next LUT4 in the upper Logic Cell.

If required by the application, the carry output from the final stage of the adder is available by passing it through the final LUT4.

Figure 4: Carry Logic Structure within a Logic Cell and between PLBs

# Implementing Subtracters, Decrementers

As mentioned earlier, the Carry Logic generates a High output whenever the sum of I1 + I2 + CARRY\_IN generates a carry. The Carry Logic does not specifically have a subtract mode. To implement a subtract function or decrement function, logically invert either the II or I2 input and invert the initial carry input. This performs a 2s complement subtract operation.

(1.31, 22-APR-2011)

8

# Programmable Input/Output Block (PIO)

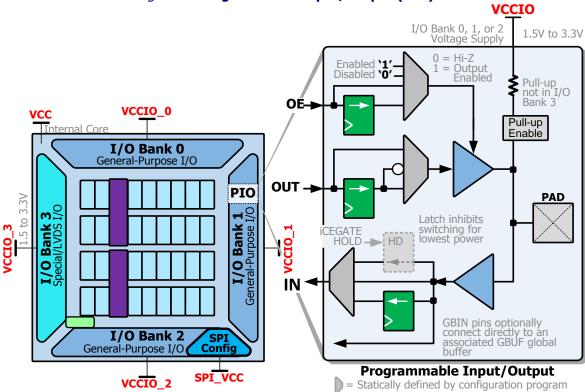

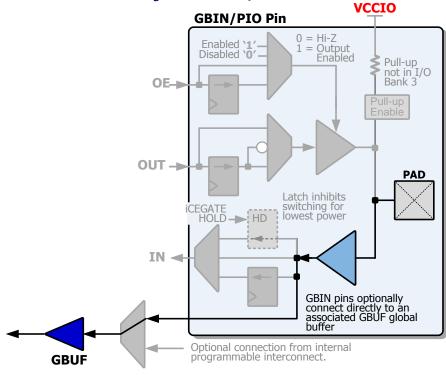

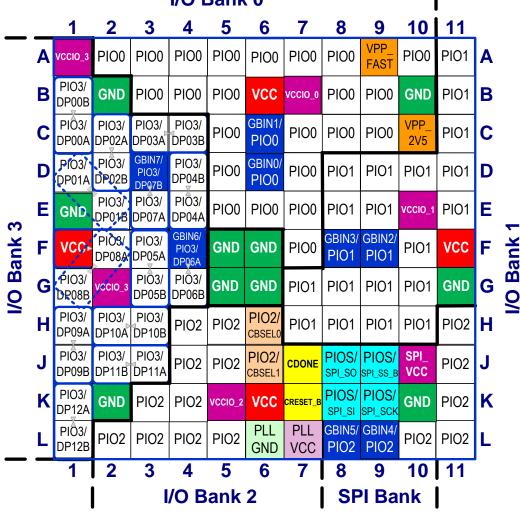

Programmable Input/Output (PIO) blocks surround the periphery of the device and connect external components to the Programmable Logic Blocks (PLBs) and RAM4K blocks via programmable interconnect. Individual PIO pins are grouped into one of four I/O banks, as shown in Figure 6. I/O Bank 3 has additional capabilities, including LVDS differential I/O and the ability to interface to Mobile DDR memories.

Figure 6 also shows the logic within a PIO pin. When used in an application, a PIO pin becomes a signal input, an output, or a bidirectional I/O pin with a separate direction control input.

# Figure 6: Programmable Input/Output (PIO) Pin

#### I/O Banks

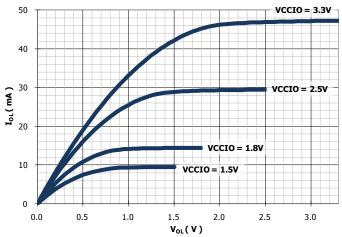

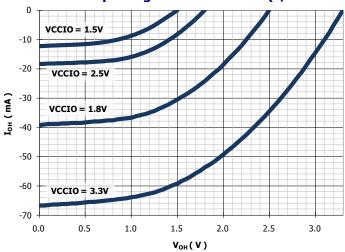

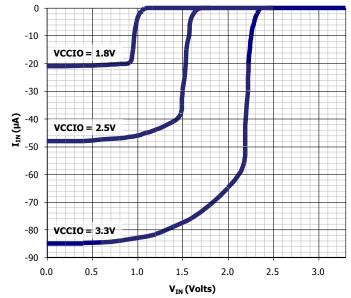

PIO blocks are organized into four separate I/O banks, each with its own voltage supply input, as shown in Table 5. The voltage applied to the VCCIO pin on a bank defines the I/O standard used within the bank. Table 53 and Table 54 describe the I/O drive capabilities and switching thresholds by I/O standard. I/O Bank 3, along the left edge of the die, is different than the others and supports specialized I/O standards.

Because each I/O bank has its own voltage supply, iCE65P components become the ideal bridging device between different interface standards. For example, the iCE65P device allows a 1.8V-only processor to interface cleanly with a 3.3V bus interface. The iCE65P device replaces external voltage translators.

| Table 5: Supported Voltages by 1/O Bank |              |              |      |      |      |              |  |

|-----------------------------------------|--------------|--------------|------|------|------|--------------|--|

| Bank                                    | Device Edge  | Supply Input | 3.3V | 2.5V | 1.8V | 1.5V         |  |

| 0                                       | Тор          | VCCIO_0      | Yes  | Yes  | Yes  | Outputs only |  |

| 1                                       | Right        | VCCIO_1      | Yes  | Yes  | Yes  | Outputs only |  |

| 2                                       | Bottom       | VCCIO_2      | Yes  | Yes  | Yes  | Outputs only |  |

| 3                                       | Left         | VCCIO_3      | Yes  | Yes  | Yes  | Yes          |  |

| SPI                                     | Bottom Right | SPI_VCC      | Yes  | Yes  | Yes  | No           |  |

# Table 5: Supported Voltages by I/O Bank

If not connected to an external SPI PROM, the four pins associated with the SPI Master Configuration Interface can be used as PIO pins, supplied by the SPI\_VCC input, essentially forming a fifth "mini" I/O bank. If using an SPI Flash PROM, then connect SPI\_VCC to 3.3V.

Table 6 highlights the available I/O standards when using an iCE65P device, indicating the drive current options, and in which bank(s) the standard is supported. I/O Banks 0, 1, 2 and SPI interface support the same standards. I/O Bank 3 has additional capabilities, including support for MDDR memory standards and LVDS differential I/O.

| <br>Table 6: I/O Standards for I/O Banks 0, 1, 2 and SPI Interface Bank |                |                    |                |  |  |  |

|-------------------------------------------------------------------------|----------------|--------------------|----------------|--|--|--|

| I/O Standard                                                            | Supply Voltage | Drive Current (mA) | Attribute Name |  |  |  |

| 5V Input Tolerance                                                      | 3.3V           | N/A                | N/A            |  |  |  |

| LVCMOS33                                                                | 3.3V           | ±11                |                |  |  |  |

| LVCMOS25                                                                | 2.5V           | ±8                 | SB LVCMOS      |  |  |  |

| LVCMOS18                                                                | 1.8V           | ±5                 | 3B_LVCMOS      |  |  |  |

| LVCMOS15 outputs                                                        | 1.5V           | ±4                 |                |  |  |  |

#### \_ - - - - -

# I/O Bank 3

I/O Bank 3, located along the left edge of the die, has additional special I/O capabilities to support memory components and differential I/O signaling (LVDS). Table 7 lists the various I/O standards supported by I/O Bank 3. The SSTL2 and SSTL18 I/O standards require the VREF voltage reference input pin which is only available on the CB284 package. Also see Table 54 for electrical characteristics.

| Table 7: I/O Standards for I/O Bank 3 Only |         |                        |                    |                  |  |  |  |

|--------------------------------------------|---------|------------------------|--------------------|------------------|--|--|--|

|                                            | Supply  | VREF Pin (CB284 or iCE | Target             |                  |  |  |  |

| I/O Standard                               | Voltage | DiCE) Required?        | Drive Current (mA) | Attribute Name   |  |  |  |

| LVCMOS33                                   | 3.3V    | No                     | ±8                 | SB_LVCMOS33_8    |  |  |  |

|                                            |         | No                     | ±16                | SB_LVCMOS25_16   |  |  |  |

| LVCMOS25                                   | 2.5V    |                        | ±12                | SB_LVCMOS25_12   |  |  |  |

| LVCHO325                                   | 2.30    |                        | ±8                 | SB_LVCMOS25_8    |  |  |  |

|                                            |         |                        | ±4                 | SB_LVCMOS25_4    |  |  |  |

|                                            |         | No                     | ±10                | SB_LVCMOS18_10   |  |  |  |

| LVCMOS18                                   | 1.8V    |                        | ±8                 | SB_LVCMOS18_8    |  |  |  |

| LVCMUSIO                                   | 1.0V    |                        | ±4                 | SB_LVCMOS18_4    |  |  |  |

|                                            |         |                        | ±2                 | SB_LVCMOS18_2    |  |  |  |

| LVCMOS15                                   | 1.5V    | No                     | ±4                 | SB_LVCMOS15_4    |  |  |  |

|                                            | 1.5V    |                        | ±2                 | SB_LVCMOS15_2    |  |  |  |

| SSTL2_II                                   | 2.5V    | Yes                    | ±16.2              | SB_SSTL2_CLASS_2 |  |  |  |

| SSTL2_I                                    | 2.5V    |                        | ±8.1               | SB_SSTL2_CLASS_1 |  |  |  |

| SSTL18_II                                  | 1.0\/   | Yes                    | ±13.4              | SB_SSTL18_FULL   |  |  |  |

| SSTL18_I                                   | 1.8V    |                        | ±6.7               | SB_SSTL18_HALF   |  |  |  |

|                                            |         | No                     | ±10                | SB_MDDR10        |  |  |  |

| MDDR                                       | 1.8V    |                        | ±8                 | SB_MDDR8         |  |  |  |

| UDUK                                       | 1.00    |                        | ±4                 | SB_MDDR4         |  |  |  |

|                                            |         |                        | ±2                 | SB_MDDR2         |  |  |  |

| LVDS                                       | 2.5V    | No                     | N/A                | SB_LVDS_INPUT    |  |  |  |

Table 8 lists the I/O standards that can co-exist in I/O Bank 3, depending on the VCCIO\_3 voltage.

| Table 8: Compatible I/O Standards in I/O Bank 3 |               |                  |                 |                 |  |  |  |  |

|-------------------------------------------------|---------------|------------------|-----------------|-----------------|--|--|--|--|

| VCCIO_3 Voltage                                 | 3.3V          | 2.5V             | 1.8V            | 1.5V            |  |  |  |  |

| Compatible I/O                                  | SB_LVCMOS33_8 | Any SB_LVCMOS25  | Any SB_LVCMOS18 | Any SB_LVCMOS15 |  |  |  |  |

| Standards                                       |               | SB_SSTL2_Class_2 | SB_SSTL18_FULL  |                 |  |  |  |  |

|                                                 |               | SB_SSTL2_Class_1 | SB_SSTL18_HALF  |                 |  |  |  |  |

|                                                 |               | SB_LVDS_INPUT    | SB_MDDR10       |                 |  |  |  |  |

|                                                 |               |                  | SB_MDDR8        |                 |  |  |  |  |

|                                                 |               |                  | SB_MDDR4        |                 |  |  |  |  |

|                                                 |               |                  | SB_MDDR2        |                 |  |  |  |  |

|                                                 |               |                  | SB_LVDS_INPUT   |                 |  |  |  |  |

#### Programmable Output Drive Strength

Each PIO in I/O Bank 3 offers programmable output drive strength, as listed in Table 8. For the LVCMOS and MDDR I/O standards, the output driver has settings for static drive currents ranging from 2 mA to 16 mA output drive current, depending on the I/O standard and supply voltage.

The SSTL18 and SSTL2 I/O standards offer full- and half-strength drive current options

#### **Differential Inputs and Outputs**

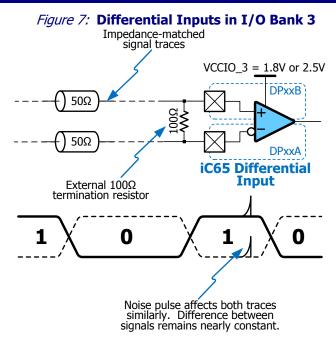

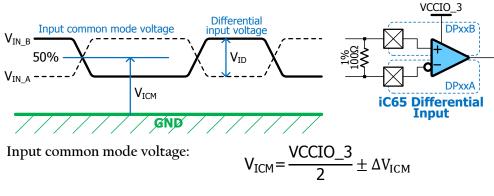

All PIO pins support "single-ended" I/O standards, such as LVCMOS. However, iCE65P FPGAs also support differential I/O standards where a single data value is represented by two complementary signals transmitted or received using a pair of PIO pins. The PIO pins in I/O Bank 3 support Low-Voltage Differential Swing (LVDS) and SubLVDS inputs as shown in Figure 7. Differential outputs are available in all four I/O banks.

#### Differential Inputs Only on I/O Bank 3

Differential receivers are required for popular applications such as LVDS and LVPECL clock inputs, camera interfaces, and for various telecommunications standards.

Specific pairs of PIO pins in I/O Bank 3 form a differential input. Each pair consists of a DPxxA and DPxxB pin, where "xx" represents the pair number. The DPxxB receives the true version of the signal while the DPxxA receives the complement of the signal. Typically, the resulting signal pair is routed on the printed circuit board (PCB) with matched 50 $\Omega$  signal impedance. The differential signaling, the low voltage swing, and the matched signal routing are ideal for communicating very-high frequency signals. Differential signals are generally also more tolerant of system noise and generate little EMI themselves.

The LVDS input circuitry requires 2.5V on the VCCIO\_3 voltage supply. Similarly, the SubLVDS input circuitry requires 1.8V on the VCCIO\_3 voltage supply. For electrical specifications, see "Differential Inputs" on page 75.

Each differential input pair requires an external 100  $\Omega$  termination resistor, as shown in Figure 7.

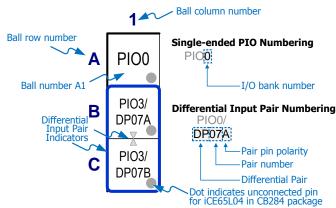

The PIO pins that make up a differential input pair are indicated with a blue bounding box in the footprint diagrams and in the pinout tables.

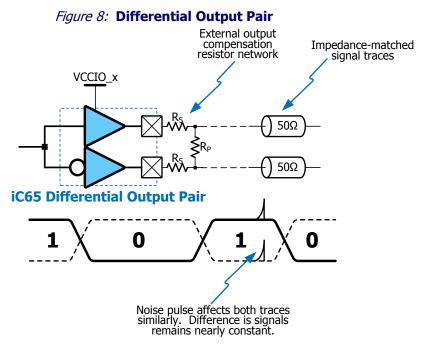

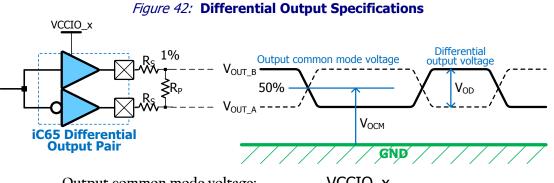

# Differential Outputs in Any Bank

Differential outputs are built using a pair of single-ended PIO pins as shown in Figure 8. Each differential I/O pair requires a three-resistor termination network to adjust output characteristic to match those for the specific differential I/O standard. The output characteristics depend on the values of the parallel resistors (RP) and series resistor (RS). Differential outputs must be located in the same I/O tile.

For electrical characteristics, see "Differential Outputs" on page 75.

The PIO pins that make up a differential output pair are indicated with a blue bounding box in the in the tables in "Die Cross Reference" starting on page 67.

# SiliconBlue

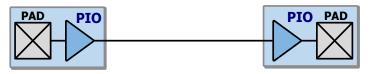

#### **Input Signal Path**

As shown in Figure 6, a signal from a package pin optionally feeds directly into the device, or is held in an input register. The input signal connects to the programmable interconnect resources through the IN signal. Table 9 describes the input behavior, assuming that the output path is not used or if a bidirectional I/O, that the output driver is in its high-impedance state (Hi-Z). Table 9 also indicates the effect of the Power-Saving I/O Bank iCEgate Latch and the Input Pull-Up Resistors on I/O Banks 0, 1, and 2.

See Input and Output Register Control per PIO Pair for information about the registered input path.

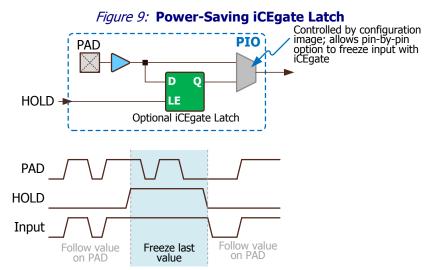

#### Power-Saving I/O Bank iCEgate Latch

To save power, the optional iCEgate latch can selectively freeze the state of individual, non-registered inputs within an I/O bank. Registered inputs are effectively frozen by their associated clock or clock-enable control. As shown in Figure 9, the iCEgate HOLD control signal captures the external value from the associated asynchronous input. The HOLD signal prevents switching activity on the PIO pad from affecting internal logic or programmable interconnect. Minimum power consumption occurs when there is no switching. However, individual pins within the I/O bank can bypass the iCEgate latch and directly feed into the programmable interconnect, remaining active during low-power operation. This behavior is described in Table 9. The decision on which asynchronous inputs use the iCEgate feature and which inputs bypass it is determined during system design. In other words, the iCEgate function is part of the source design used to create the iCE65P configuration image.

#### Table 9: PIO Non-Registered Input Operations

|                                             | HOLD          | Bitstream   | n Setting   | PAD       | IN                         |

|---------------------------------------------|---------------|-------------|-------------|-----------|----------------------------|

|                                             |               | Controlled  | Input Pull- |           | Input Value to             |

| Operation                                   | iCEgate Latch | by iCEgate? | Up Enabled? | Pin Value | Interconnect               |

| Data Input                                  | 0             | Х           | Х           | PAD       | PAD Value                  |

| Pad Floating, No Pull-up                    | 0             | Х           | No          | Z         | (Undefined)                |

| Pad Floating, Pull-up                       | 0             | Х           | Yes         | Z         | 1                          |

| Data Input, Latch<br>Bypassed               | Х             | No          | Х           | PAD       | PAD Value                  |

| Pad Floating, No Pull-up,<br>Latch Bypassed | Х             | No          | No          | Z         | (Undefined)                |

| Pad Floating, Pull-up,<br>Latch Bypassed    | Х             | No          | Yes         | Z         | 1                          |

| Low Power Mode, Hold<br>Last Value          | 1             | Yes         | Х           | Х         | Last Captured<br>PAD Value |

There are four iCEgate HOLD controls, one per each I/O bank. The iCEgate HOLD control input originates within the interconnect fabric, near the middle of the I/O edge. Consequently, the HOLD signal is optionally controlled externally through a PIO pin or from other logic within the iCE65P device.

For best possible performance, the global buffer inputs (GBIN[7:-0]) connect directly to the their associated global buffers (GBUF[7:0]), bypassing the PIO logic and iCEgate circuitry as shown in Figure 6. Consequently, the direct GBIN-to-GBUF connection cannot be blocked by the iCEgate circuitry. However, it is possible to use iCEgate to block PIO-to-GBUF clock connections.

For additional information on using the iCEgate feature, please refer to the following application note.

AN002: Using iCEgate Blocking for Ultra-Low Power www.siliconbluetech.com/media/AN2iCEGATErevl.l.pdf

# Input Pull-Up Resistors on I/O Banks 0, 1, and 2

The PIO pins in I/O Banks 0, 1, and 2 have an optional input pull-up resistor. Pull-up resistors are not provided in I/O Bank 3.

During the iCE65P configuration process, the input pull-up resistor is unconditionally enabled and pulls the input to within a diode drop of the associated I/O bank supply voltage (VCCIO\_#). This prevents any signals from floating on the circuit board during configuration.

After iCE65P configuration is complete, the input pull-up resistor is optional, defined by a configuration bit. The pull-up resistor is also useful to tie off unused PIO pins. The SiliconBlue iCEcube development software defines all unused PIO pins in I/O Banks 0, 1 and 2 as inputs with the pull-up resistor turned on.

The pull-up resistor value depends on the VCCIO voltage applied to the bank, as shown in Table 52.

# No Input Pull-up Resistors on I/O Bank 3

The PIO pins associated with I/O Bank 3 do not have an internal pull-up resistor. To minimize power consumption, tie unused PIO pins in Bank 3 to a known logic level or drive them as a disabled high-impedance output.

# Input Hysteresis

Inputs typically have about 50 mV of hysteresis, as indicated in Table 52.

# **Output and Output Enable Signal Path**

As shown in Figure 6, a signal from programmable interconnect feeds the OUT signal on a Programmable I/O pad. This output connects either directly to the associated package pin or is held in an optional output flip-flop. Because all flip-flops are automatically reset after configuration, the output from the output flip-flop can be optionally inverted so that an active-Low output signal is held in the disabled (High) state immediately after configuration.

Similarly, each Programmable I/O pin has an output enable or three-state control called OE. When OE = High, the OUT output signal drives the associated pad, as described in Table 10. When OE = Low, the output driver is in the high-impedance (Hi-Z) state. The OE output enable control signal itself connects either directly to the output buffer or is held in an optional register. The output buffer is optionally permanently enabled or permanently disabled, either to unconditionally drive output signals, or to allow input-only signals.

| <i>Table 10:</i> <b>PIO Output Operations (non-registered operation, no inversions)</b> |

|-----------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------|

|                   | OUT         | OE     |      |

|-------------------|-------------|--------|------|

| Operation         | Data Output | Enable | PAD  |

| Three-State       | Х           | 0      | Hi-Z |

| Drive Output Data | OUT         | 1*     | OUT  |

X = don't care,  $1^* = High or unused$ , Hi-Z = high-impedance, three-stated, floating.

See Input and Output Register Control per PIO Pair for information about the registered input path.

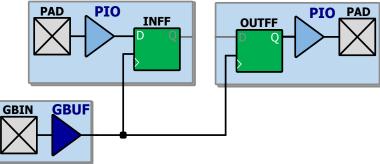

# Input and Output Register Control per PIO Pair

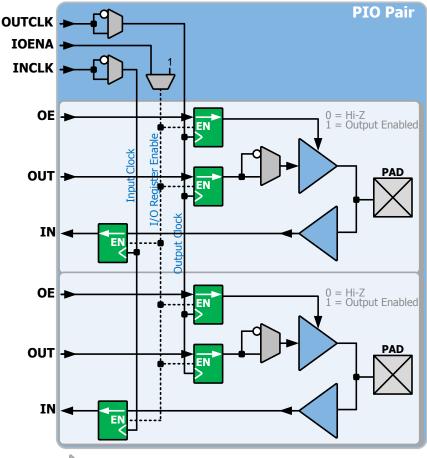

PIO pins are grouped into pairs for synchronous control. Registers within pairs of PIO pins share common input clock, output clock, and I/O clock enable control signals, as illustrated in Figure 10. The combinational logic paths are removed from the drawing for clarity.

The INCLK clock signal only controls the input flip-flops within the PIO pair.

The OUTCLK clock signal controls the output flip-flops and the output-enable flip-flops within the PIO pair.

If desired in the iCE65P application, the INCLK and OUTCLK signals can be connected together using Error! eference source not found..

The IOENA clock-enable input, if used, enables all registers in the PIO pair, as shown in Figure 10. By default, the registers are always enabled.

Before laying out your printed-circuit board, run the design through the iCEcube development software to verify that your selected pinout complies with these I/O register pairing requirements. See tables in "Die Cross Reference" starting on page 67.

= Statically defined by configuration program

The pairing of PIO pairs is most evident in the tables in "Die Cross Reference" starting on page 67.

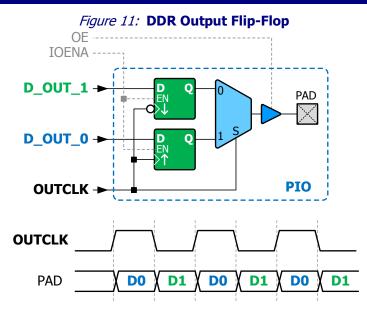

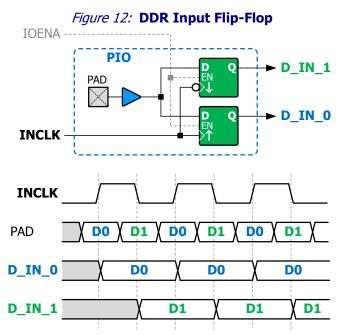

# Double Data Rate (DDR) Flip-Flops

Each individual PIO pin optionally has two sets of double data rate (DDR) flip-flops; one input pair and one output pair. Figure 11 demonstrates the functionality of the output DDR flip-flop. Two signals from within the iCE65P device drive the DDR output flip-flop. The D\_OUT\_0 signal is clocked by the rising edge of the OUTCLK signal while the D\_OUT\_1 signal is clocked by the falling edge of the OUTCLK signal, assuming no optional clock polarity inversion. Internally, the two individual flip-flops are multiplexed together before the data appears at the pad, effectively doubling the output data rate.

Similarly, Figure 12 demonstrates the DDR input flip-flop functionality. A double data rate (DDR) signal arrives at the pad. Internally, one value is clocked by the rising edge of the INCLK signal and another value is clocked by the falling edge of the INCLK signal. The DDR data stream is effectively de-multiplexed within the PIO pin and presented to the programmable interconnect on D\_IN\_0 and D\_IN\_1.

The DDR flip-flops provide several design advantages. Internally within the iCE65P device, the clock frequency is half the effective external data rate. The lower clock frequency eases internal timing, doubling the clock period, and slashes the clock-related power in half.

#### **Global Routing Resources**

### **Global Buffers**

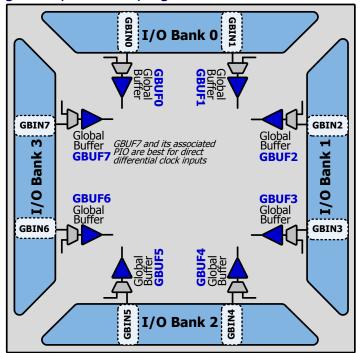

Each iCE65P component has eight global buffer routing connections, illustrated in Figure 13.

There are eight high-drive buffers, connected to the eight low-skew, global lines. These lines are designed primarily for clock distribution but are also useful for other high-fanout signals such as set/reset and enable signals. The global buffers originate either from the Global Buffer Inputs (GBINx) or from programmable interconnect. The associated GBINx pin represents the best pin to drive a global buffer from an external source. However, the application with an iCE65P FPGA can also drive a global buffer via any other PIO pin or from internal logic using the programmable interconnect.

If not used in an application, individual global buffers are turned off to save power.

Table 11 lists the connections between a specific global buffer and the inputs on a Programmable Logic Block (PLB). All global buffers optionally connect to all clock inputs. Any four of the eight global buffers can drive logic inputs to a PLB. Even-numbered global buffers optionally drive the Reset input to a PLB. Similarly, odd-numbered buffers optionally drive the PLB clock-enable input.

| Table 11: Global Buffer (GBUF) Connections to Programmable Logic Block (PLB) |                 |       |              |       |  |  |  |

|------------------------------------------------------------------------------|-----------------|-------|--------------|-------|--|--|--|

| Global Buffer                                                                | LUT Inputs      | Clock | Clock Enable | Reset |  |  |  |

| GBUF0                                                                        | Yes, any 4 of 8 | Yes   | Yes          | No    |  |  |  |

| GBUF1                                                                        | GBUF buffers    | Yes   | No           | Yes   |  |  |  |

| GBUF2                                                                        |                 | Yes   | Yes          | No    |  |  |  |

| GBUF3                                                                        |                 | Yes   | No           | Yes   |  |  |  |

| GBUF4                                                                        |                 | Yes   | Yes          | No    |  |  |  |

| GBUF5                                                                        |                 | Yes   | No           | Yes   |  |  |  |

| GBUF6                                                                        |                 | Yes   | Yes          | No    |  |  |  |

| GBUF7                                                                        |                 | Yes   | No           | Yes   |  |  |  |

Table 12 and Table 13 list the connections between a specific global buffer and the inputs on a Programmable I/O (PIO) pair. Although there is no direct connection between a global buffer and a PIO output, such a connection is possible by first connecting through a PLB LUT4 function. Again, all global buffers optionally drive all clock inputs. However, even-numbered global buffers optionally drive the clock-enable input on a PIO pair.

| Table 12: ICE05P04: Global Buffer (GBUF) Connections to Programmable 1/0 (PIO) Pair |                       |             |              |              |  |  |

|-------------------------------------------------------------------------------------|-----------------------|-------------|--------------|--------------|--|--|

| Global Buffer                                                                       | Output<br>Connections | Input Clock | Output Clock | Clock Enable |  |  |

| GBUF0                                                                               | No (connect through   | Yes         | Yes          | No           |  |  |

| GBUF1                                                                               | PLB LUT)              | Yes         | Yes          | Yes          |  |  |

| GBUF2                                                                               |                       | Yes         | Yes          | No           |  |  |

| GBUF3                                                                               |                       | Yes         | Yes          | Yes          |  |  |

| GBUF4                                                                               |                       | Yes         | Yes          | No           |  |  |

| GBUF5                                                                               |                       | Yes         | Yes          | Yes          |  |  |

| GBUF6                                                                               |                       | Yes         | Yes          | No           |  |  |

| GBUF7                                                                               |                       | Yes         | Yes          | Yes          |  |  |

# Table 12: iCE65P04: Global Buffer (GBUF) Connections to Programmable I/O (PIO) Pair

# Table 13: iCE64L08: Global Buffer (GBUF) Connections to Programmable I/O (PIO) Pair

| Global Buffer | Output<br>Connections | Input Clock | Output Clock | Clock Enable |

|---------------|-----------------------|-------------|--------------|--------------|

| GIODAI DUITEI | Connections           | Input Clock | Output Clock |              |

| GBUF0         | No (connect through   | Yes         | Yes          | Yes          |

| GBUF1         | PLB LUT)              | Yes         | Yes          | No           |

| GBUF2         |                       | Yes         | Yes          | Yes          |

| GBUF3         |                       | Yes         | Yes          | No           |

| GBUF4         |                       | Yes         | Yes          | Yes          |

| GBUF5         |                       | Yes         | Yes          | No           |

| GBUF6         |                       | Yes         | Yes          | Yes          |

| GBUF7         |                       | Yes         | Yes          | No           |

# Global Buffer Inputs

The iCE65P component has eight specialized GBIN/PIO pins that are optionally direct inputs to the global buffers, offering the best overall clock characteristics. As shown in Figure 14, each GBIN/PIO pin is a full-featured I/O pin but also provides a direct connection to its associated global buffer. The direct connection to the global buffer bypasses the iCEgate input-blocking latch and other PIO input logic. These special PIO pins are allocated two to an I/O Bank, a total of eight. These pins are labeled GBIN0 through GBIN7, as shown in Figure 13 and the pin locations for each GBIN input appear in Table 14.

| Global                    |          | Package Code  |               |               |

|---------------------------|----------|---------------|---------------|---------------|

| Buffer<br>Input<br>(GBIN) | I/O Bank | `Р04<br>СВ121 | `P04<br>CB196 | `P04<br>CB284 |

| GBINO                     | 0        | D6            | A7            | E10           |

| <b>GBIN1</b>              | 0        | C6            | E7            | E11           |

| GBIN2                     | 1        | F9            | F10           | L18           |

| <b>GBIN3</b>              | L        | F8            | G12           | K18           |

| GBIN4                     | 2        | L9            | L7            | V12           |

| GBIN5                     | Z        | L8            | P5            | V11           |

| GBIN6                     | 2        | F4            | H1            | M5            |

| GBIN7                     | 3        | D3            | G1            | L5            |

#### Table 14: Global Buffer Input Ball Number by Package

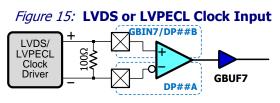

#### Differential Global Buffer Input

All eight global buffer inputs support single-ended I/O standards such as LVCMOS. Global buffer GBUF7 in I/O Bank 3 also provides an optional direct SubLVDS, LVDS, or LVPECL differential clock input, as shown in Figure 15. The GBIN7 and its associated differential I/O pad accept a differential clock signal. A 100  $\Omega$  termination resistor is required across the two pads. Optionally, swap the outputs from the LVDS or LVPECL clock driver to invert the clock as it enters the iCE65P device.

Table 15 lists the pin or ball numbers for the differential global buffer input by package style. Although this differential input is the only one that connects directly to a global buffer, other differential inputs can connect to a global buffer using general-purpose interconnect, with slightly more signal delay.

| <i>Table 15:</i> Differential Global Buffer Input Ball Number by Package |          |                                          |       |       |

|--------------------------------------------------------------------------|----------|------------------------------------------|-------|-------|

| Differential Global                                                      |          | Package Code           `P04         `P04 |       |       |

| Buffer Input                                                             |          |                                          |       |       |

| (GBIN)                                                                   | I/O Bank | CB121                                    | CB196 | CB284 |

| GBIN7/DPxxB                                                              | 2        | D3                                       | G1    | L5    |

| DPxxA                                                                    | 5        | E3                                       | G2    | L3    |

# T 11 15 D.C.

### Automatic Global Buffer Insertion, Manual Insertion

The iCEcube development software automatically assigns high-fanout signals to a global buffer. However, to manual insert a global buffer input/global buffer (GBIN/GBUF) combination, use the SB\_IO\_GB primitive. To insert just a global buffer (GBUF), use the SB\_GB primitive.

#### Global Hi-Z Control

The global high-impedance control signal, GHIZ, connects to all I/O pins on the iCE65P device. This GHIZ signal is automatically asserted throughout the configuration process, forcing all user-I/O pins into their high-impedance state. Similarly, the PIO pins can be forced into their high-impedance state via the JTAG controller.

#### **Global Reset Control**

The global reset control signal connects to all PLB and PIO flip-flops on the iCE65P device. The global reset signal is automatically asserted throughout the configuration process, forcing all flip-flops to their defined wake-up state. For PLB flip-flops, the wake-up state is always reset, regardless of the PLB flip-flop primitive used in the application. See Table 3 for more information.

The PIO flip-flops are always reset during configuration, although the output flip-flop can be inverted before leaving the iCE65P device, as shown in Figure 10.

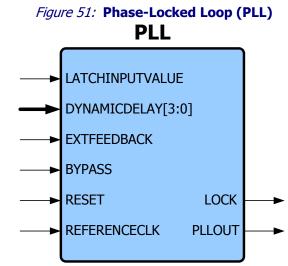

# Phase-Locked Loop (PLL)

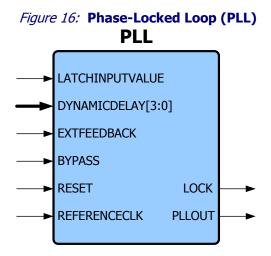

To support a variety of display, imager, and memory interface applications, the iCE65P FPGA family includes an ultra-low power Phase Locked Loop (PLL), as shown in Figure 16. The iCEcube development software provides three PLL macro variants, depending on whether the clock originates inside the FPGA or from an external source, and whether only the PLL output connects to a global buffer, or whether both the PLL output and the clock input pad, as described in Table 16.

| Table 16: PLL Macro Types |              |            |                      |  |  |

|---------------------------|--------------|------------|----------------------|--|--|

| PLL Macro Name            | Clock Input  | GBUF       | GBUF                 |  |  |

| SB_PLL_CORE               | FPGA routing | PLL output | N/A                  |  |  |

| SB_PLL_PAD                | PAD          | PLL output | N/A                  |  |  |

| SB_PLL_2_PAD              | PAD          | PLL output | Clock input from pad |  |  |

The PLL provides the following functions for the iCE65P application.

- Generates a new output clock frequency

- ♦ Clock multiplication

- ♦ Clock division

- Clock scaling to maximize performance or to minimize power consumption

- De-skews or phase-aligns an output clock to the input reference clock.

- ◆ Faster input setup time

- Faster clock-to-output time

- Corrects output clock to have nearly a 50% duty cycle, which is important for Double Data Rate (DDR) applications.

- Optionally phase shifts the output clock relative to the input reference clock.

- Optimal data sampling within the available bit period

- ◆ Fixed quadrant phase shifting at 0°, 90°, 180°, and 270°.

- Optional fine delay adjustments of up to 2.5 ns (nominal) in 165 ps increments (nominal).

### Signals

Table 17 lists the signal names, direction, and function of each connection to the PLL. Some of the signals have an associated attribute or property, listed in Table 18.

| Signal Name        | Direction | Description                                                                                                                                                          |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCECLK       | Input     | Input reference clock                                                                                                                                                |

| RESET              | Input     | Reset                                                                                                                                                                |

| BYPASS             | Input     | When FEEDBACK_PATH is set to SIMPLE, the BYPASS control selects which<br>clock signal connects to the PLLOUT output.<br>0 = PLL generated signal<br>1 = REFERENCECLK |

| EXTFEEDBACK        | Input     | External feedback input to PLL. Enabled when FEEDBACK_PATH attribute set to EXTERNAL.                                                                                |

| DYNAMIC_DELAY[3:0] | Input     | Fine delay adjustment control inputs. Enabled when<br>DELAY_ADJUSTMENT_MODE set to DYNAMIC                                                                           |

| LATCHINPUTVALUE    | Input     | When enabled, forces the PLL into low-power mode; PLL output held static at last input clock value. Set ENABLE ICEGATE_PORTA and PORTB to '1' to enable.             |

| PLLOUT             | Output    | Output from the Phase-Locked Loop (PLL). Connects to programmable interconnect and has optimal connections to global clock buffers GBUF4 and GBUF5.                  |

| LOCK               | Output    | When High, indicates that the PLL output is phase aligned or locked to the input reference clock.                                                                    |

#### Table 17: PLL Signals

# **Attributes/Properties**

Table 18 lists the attributes or properties associated with the PLL and the allowable settings for each attribute.

| Table 18: PLL Attributes and Settings |                                                                                                        |                 |                                                                                                                     |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Attribute/Property                    | Description                                                                                            | Setting         | Description                                                                                                         |  |  |

| FEEDBACK_PATH                         | Selects the feedback path                                                                              | SIMPLE          | Feedback directly from VCO                                                                                          |  |  |

|                                       | to the PLL                                                                                             | DELAY           | Feedback from VCO through fine<br>delay adjustment                                                                  |  |  |

|                                       |                                                                                                        | PHASE_AND_DELAY | Feedback from VCO through the<br>fine delay adjustment and phase<br>shifter; feedback is further divided<br>by four |  |  |

|                                       |                                                                                                        | EXTERNAL        | Feedback from EXTFEEDBACK input                                                                                     |  |  |

| DELAY_ADJUSTMENT_MODE                 | Selects the control input for<br>the fine delay adjustment.<br>Delays the PLLOUT output                | FIXED           | Delay controlled by<br>FIXED_DELAY_ADJUSTMENT<br>setting                                                            |  |  |

|                                       | nominally by ( <i>n</i> +1) • 150<br>ps                                                                | DYNAMIC         | Delay controlled by current value of<br>DYNAMIC_DELAY[3:0]                                                          |  |  |

| FIXED_DELAY_ADJUSTMENT                | Sets the constant value for<br>the fine delay adjustment<br>when DELAY_ADJUSTMENT<br>mode set to FIXED | 0, 1,, 15       | Delays the PLLOUT output by specified setting                                                                       |  |  |

| PLL_OUT_PHASE                         | Controls the phase<br>alignment of the PLLOUT                                                          | NONE            | Phase alignment disabled, no duty-<br>cycle correction                                                              |  |  |

|                                       | output relative to the input                                                                           | 0deg            | 0° phase shift (no phase shift)                                                                                     |  |  |

|                                       | reference clock; see Figure                                                                            | 90deg           | 90° phase shift (quarter cycle shift)                                                                               |  |  |

|                                       | 18                                                                                                     | 180deg          | 180° phase shift (half-cycle shift)                                                                                 |  |  |

|                                       |                                                                                                        | 270deg          | 270° phase shift (three-quarter cycle shift)                                                                        |  |  |

| DIVR                                  | Divider value for the input clock                                                                      | 0, 1,, 15       | These attributes control the PLL output frequency. See Equation 2                                                   |  |  |

| DIVF                                  | Divider value for feedback                                                                             | 0, 1,, 63       | and Equation 3 and the Frequency                                                                                    |  |  |

| DIVQ                                  | Divider value for the VCO output, generates PLLOUT                                                     | 0, 1,, 5        | Synthesis spreadsheet.                                                                                              |  |  |

| RANGE                                 | Controls the PLL operating range                                                                       | 0, 1,, 7        |                                                                                                                     |  |  |

| ENABLE_ICEGATE                        | Enables iCEgate to disable                                                                             | 0               | GBUF disabled                                                                                                       |  |  |

|                                       | GBUF transitions                                                                                       | 1               | GBUF enabled                                                                                                        |  |  |

# **Clock Input Requirements**

For proper operation, the PLL requires ...

- A stable monotonic (single frequency) reference clock input.

- The reference clock input must be within the input clock frequency range,  $F_{REF}$ , specified in Table 60.

- The reference clock must have a duty cycle that meets the requirement specified in Table 60.

- The jitter on the reference input clock must not exceed the limits specified in Table 60.

# **PLL Output Requirements**

The PLL output clock, PLLOUT requires the following restrictions.

- The PLLOUT output frequency must be within the limits specified in Table 60.

- The PLLOUT output is not valid or stable until the PLL's LOCK output remains High.

### **Voltage Controlled Oscillator Supply Inputs**

The phase-locked loop (PLL) uses separate analog supply inputs for the voltage-controlled oscillator (VCO).

| Table 19: PLL Supply Ball Numbers by Package |              |       |       |  |  |

|----------------------------------------------|--------------|-------|-------|--|--|

|                                              | Package Code |       |       |  |  |

| ColdBoot Select                              | CB121        | CB196 | CB284 |  |  |

| PLLGND                                       | L6           | M6    | Y9    |  |  |

| PLLVCC                                       | L7 N6 Y10    |       |       |  |  |

Table 10. DLL Commission Dall Normalisme has Dealer as

#### **Clock Multiplication and Division**

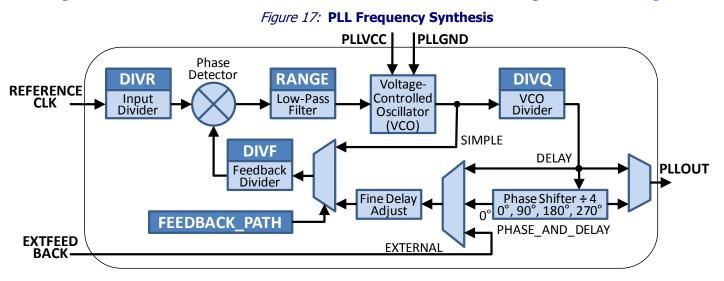

The PLL optionally multiplies and/or divides the input reference clock to generate a PLLOUT output clock of another frequency. The output frequency depends on the frequency of the REFERENCLK input clock and the settings for the DIVR, DIVF, DIVQ, RANGE, and FEEDBACK\_PATH attribute settings, as indicated in Figure 17.

The PLL's phase detector and Voltage Controlled Oscillator (VCO) synthesize a new output clock frequency based on the attribute settings. The VCO is an analog circuit and has independent voltage supply and ground connections labeled PLLVCC and PLLGND.

The simplest method to determine the optimal settings for a specific application is to use the Frequency Synthesis Spreadsheet

# PLLOUT Frequency for All Modes Except FEEDBACK\_PATH = SIMPLE

For all the FEEDBACK\_PATH modes, except SIMPLE, the PLLOUT frequency is the result of Equation 2.

$$F_{PLLOUT} = \frac{F_{REFERNCECLK} \bullet (DIVF+1)}{DIVR+1}$$

[Equation 2]

#### PLLOUT Frequency for FEEDBACK\_PATH = SIMPLE

If the SIMPLE feedback mode, the PLL feedback signal taps directly from the output of the VCO, before the final divider stage. Consequently, the PLL output frequency has an additions divider step, DIVQ, contributed by the final divider step as shown in Equation 3. (DIVF, DIVQ and DIVR are binary)

$$F_{PLLOUT} = \frac{F_{REFERNCECLK} \bullet (DIVF+1)}{2^{(DIVQ)} \bullet (DIVR+1)}$$

[Equation 3]

#### **Fixed Quadrant Phase Shift**

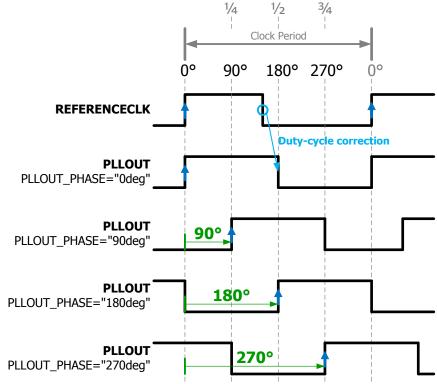

The PLL optional phase feature shifts the PLLOUT output by a specified quadrant or quarter clock cycle as shown in Figure 18 and Table 20. The quadrant phase shift option is only available when the FEEDBACK\_PATH attribute is set to PHASE\_AND\_DELAY.

|              | Table 20: PLL Phase Shift Options                        |      |                     |  |  |  |

|--------------|----------------------------------------------------------|------|---------------------|--|--|--|

| PLLOUT_PHASE | PLLOUT_PHASE Duty Cycle Correction Phase Shift (Degrees) |      |                     |  |  |  |

| NONE         | No                                                       | 0°   | None                |  |  |  |

| 0deg         | Yes                                                      | 0°   | None                |  |  |  |

| 90deg        | 90deg Yes                                                |      | Quarter Cycle       |  |  |  |

| 180deg       | Yes                                                      | 180° | Half Cycle          |  |  |  |

| 270deg       | Yes                                                      | 270° | Three-quarter Cycle |  |  |  |

Unlike the Fine Delay Adjustment, the quadrant phase shifter always shifts by a fixed phase angle. The resulting phase shift, measured in delay, depends on the clock period and the PLLOUT\_PHASE phase shift setting, as shown in Equation 4.

$$Delay = \frac{Phase\_Shift}{360^{\circ}} \bullet Clock\_Period \qquad [Equation 4]$$

# **Fine Delay Adjustment**

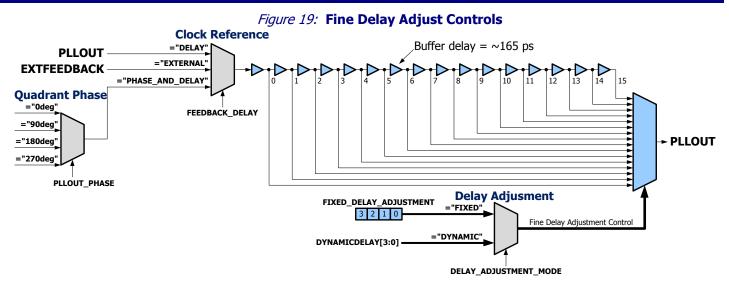

As shown in Figure 19, the PLL provides an optional fine delay adjustment that controls the delay of the PLLOUT output relative to the input reference clock, to an external feedback signal, or relative to the selected quadrant phase shifted clock. The delay is adjusted by selecting one or more of the 16 delay taps. Each tap is approximately 165 ps.

The fine delay adjustment option is available when the FEEDBACK\_PATH attribute is set to DELAY, PHASE\_AND\_DELAY, or EXTERNAL, as shown in Figure 19 and Figure 17.

# Fine Adjustment Control

The number of delay taps is controlled either statically using the FIXED\_DELAY\_ADJUSTMENT option or dynamically by the application using the PLL's DYNAMIC\_DELAY[3:0] inputs, as described in Table 21.

| Table 21: Fine Delay Adjustment Control |                                          |  |  |  |

|-----------------------------------------|------------------------------------------|--|--|--|

| DELAY_ADJUSTMENT_MODE Setting           | Adjustment Control                       |  |  |  |

| FIXED                                   | FIXED_DELAY_ADJUSTMENT attribute setting |  |  |  |

| DYNAMIC                                 | DYNAMIC_DELAY[3:0] control inputs        |  |  |  |

# Fine Adjustment Delay

The resulting nominal fine adjustment delay value is shown in Equation 5, where **n** is either the value of the FIXED\_DELAY\_ADJUSTMENT attribute setting or the dynamic binary value presented on the DYNAMIC\_DELAY[3:0] inputs. The actual delay varies slightly due to the slight differences in the delay tap buffer delay.

Fine Delay Adjustment *(nominal)* =

$$(n + 1) \cdot 165$$

ps [Equation 5]

# Phase Angle Equivalent

I

The fine delay adjustment feature always injects an actual delay value, not a fixed phase angle like the Fixed Quadrant Phase Shift feature. Use Equation 6 to convert the fine adjustment delay to a resulting phase angle.

$$Phase_Shift = \frac{Fine_Delay_Adjustment}{Clock_Period} \bullet 360^{\circ}$$

[Equation 6]

#### Low Power Mode

The phase-lock loop (PLL) has low operating power by default. The PLL can be dynamically disabled to further reduce power. The low-power mode must first be enabled by setting the ENABLE\_ICEGATE attribute to 'I'. Once enabled, use the LATCHINPUTVALUE to control the PLL's operation, as shown in Table 22. The PLL must reacquire the input clock and LOCK when LATCHINPUTVALUE returns from 'I' to '0', external feedback is used and path goes out into the fabric.

| ENABLE_ICEGATE<br>Attribute | LATCHINPUTVALUE<br>Input | Function                                                       |

|-----------------------------|--------------------------|----------------------------------------------------------------|

| 0                           | Don't care               | PLL is always enabled                                          |

| 4                           | 0                        | PLL is enabled and operating                                   |

| 1                           | 1                        | PLL is in low-power mode; PLLOUT output holds last clock state |

# Table 22: PLL LATCHINPUTVALUE Control

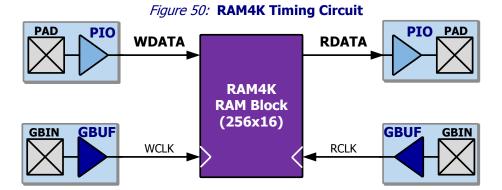

# RAM

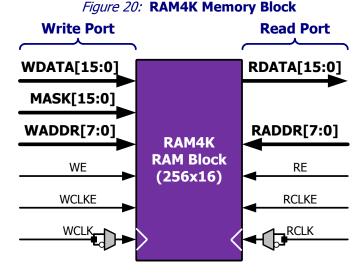

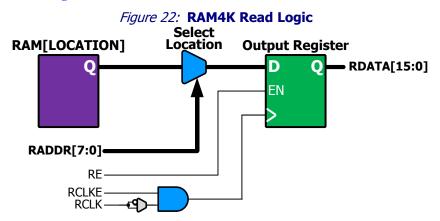

Each iCE65P device includes multiple high-speed synchronous RAM blocks (RAM4K), each 4Kbit in size. As shown in Table 23 a single iCE65P integrates between 16 to 96 such blocks. Each RAM4K block is generically a 256-word deep by 16-bit wide, two-port register file, as illustrated in Figure 20. The input and output connections, to and from a RAM4K block, feed into the programmable interconnect resources.

Table 23: RAM4K Blocks per Device

| Device   | RAM4K Blocks | Default<br>Configuration | RAM Bits per Block | Block RAM Bits |

|----------|--------------|--------------------------|--------------------|----------------|

| iCE65P04 | 20           | 256 x 16                 | 4K<br>(4,096)      | 80K            |

Using programmable logic resources, a RAM4K block implements a variety of logic functions, each with configurable input and output data width.

- Random-access memory (RAM)

- Single-port RAM with a common address, enable, and clock control lines

- Two-port RAM with separate read and write control lines, address inputs, and enable

- Register file and scratchpad RAM

- First-In, First-Out (FIFO) memory for data buffering applications

- Circuit buffer

- A 256-deep by 16-wide ROM with registered outputs, contents loaded during configuration

- ♦ Sixteen different 8-input look-up tables

- Function or waveform tables such as sine, cosine, etc.

- Correlators or pattern matching operations

- Counters, sequencers

As pictured in Figure 20, a RAM4K block has separate write and read ports, each with independent control signals. Table 24 lists the signals for both ports. Additionally, the write port has an active-Low bit-line write-enable control; optionally mask write operations on individual bits. By default, input and output data is 16 bits wide, although the data width is configurable using programmable logic and, if needed, multiple RAM4K blocks.

The WCLK and RCLK inputs optionally connect to one of the following clock sources.

- The output from any one of the eight Global Buffers, or

- A connection from the general-purpose interconnect fabric

The data contents of the RAM4K block are optionally pre-loaded during iCE65P device configuration. If the RAM4K blocks are not pre-loaded during configuration, then the resulting configuration bitstream image is smaller. However, if an uninitialized RAM4K block is used in the application, then the application must initialize the RAM contents to guarantee the data value.

See Table 59 for detailed timing information.

#### Signals

Table 24 lists the signal names, direction, and function of each connection to the RAM4K block. See also Figure 20.

| Table 24: RAM4K Block RAM Signals |           |                                                                                               |  |  |

|-----------------------------------|-----------|-----------------------------------------------------------------------------------------------|--|--|

| Signal Name                       | Direction | Description                                                                                   |  |  |

| WDATA[15:0]                       | Input     | Write Data input.                                                                             |  |  |

| MASK[15:0]                        | Input     | Masks write operations for individual data bit-lines.<br>0 = Write bit; $1 =$ Don't write bit |  |  |

| WADDR[7:0]                        | Input     | Write Address input. Selects one of 256 possible RAM locations.                               |  |  |

| WE                                | Input     | Write Enable input.                                                                           |  |  |

| WCLKE                             | Input     | Write Clock Enable input.                                                                     |  |  |

| WCLK                              | Input     | Write Clock input. Default rising-edge, but with falling-edge option.                         |  |  |

| RDATA[15:0]                       | Output    | Read Data output.                                                                             |  |  |

| RADDR[7:0]                        | Input     | Read Address input. Selects one of 256 possible RAM locations.                                |  |  |

| RE                                | Input     | Read Enable input.                                                                            |  |  |

| RCLKE                             | Input     | Read Clock Enable input.                                                                      |  |  |

| RCLK                              | Input     | Read Clock input. Default rising-edge, but with falling-edge option.                          |  |  |

# Table 24: RAM4K Block RAM Signals

#### Write Operations

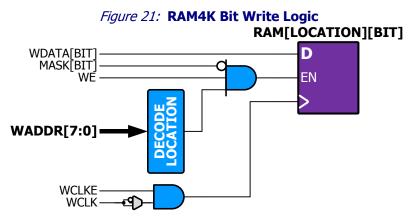

Figure 21 shows the logic involved in writing a data bit to a RAM location. Table 25 describes various write operations for a RAM4K block. By default, all RAM4K write operations are synchronized to the rising edge of WCLK although the clock is invertible as shown in Figure 21.

When the WCLKE signal is Low, the clock to the RAM4K block is disabled, keeping the RAM in its lowest power mode.

|           | Table 25: RAM4K Write Operations |                                                 |         |        |        |       |                     |  |  |

|-----------|----------------------------------|-------------------------------------------------|---------|--------|--------|-------|---------------------|--|--|

|           | WDATA[15:0]                      | WDATA[15:0] MASK[15:0] WADDR[7:0] WE WCLKE WCLK |         |        |        |       |                     |  |  |

|           |                                  |                                                 |         | Write  | Clock  |       |                     |  |  |

| Operation | Data                             | Mask Bit                                        | Address | Enable | Enable | Clock | <b>RAM Location</b> |  |  |

| Disabled  | Х                                | Х                                               | Х       | Х      | Х      | 0     | No change           |  |  |

| Disabled  |                                  |                                                 |         |        | 0      | Х     | No change           |  |  |

| Disabled  | Х                                | Х                                               | Х       | 0      | Х      | Х     | No change           |  |  |

| Write     | WDATA[i]                         | MASK[i] = 0                                     | WADDR   | 1      | 1      | 1     | RAM[WADDR][i]       |  |  |

| Data      |                                  |                                                 |         |        |        |       | = WDATA[i]          |  |  |

| Masked    | Х                                | MASK[i] = 1                                     | WADDR   | 1      | 1      | 1     | RAM[WADDR][i]       |  |  |

| Write     |                                  |                                                 |         |        |        |       | = No change         |  |  |

To write data into the RAM4K block, perform the following operations.

- Supply a valid address on the WADDR[7:0] address input port

- Supply valid data on the WDATA[15:0] data input port

- To write or mask selected data bits, set the associated MASK input port accordingly. For example, write operations on data bit D[i] are controlled by the associated MASK[i] input.

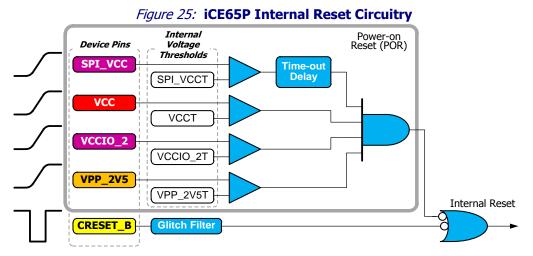

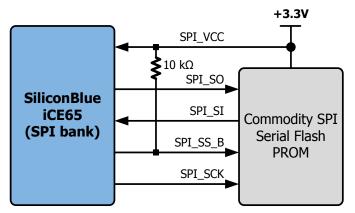

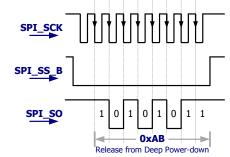

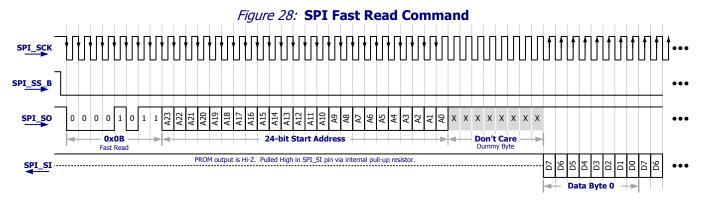

- MASK[i] = 0: Write operations are enabled for data line WDATA[i]