### **Dual 20V N-Channel Power MOSFET**

### **GWS9294**

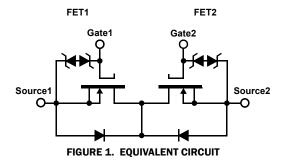

The GWS9294 is a dual 20V,  $12m\Omega$ , N-channel power MOSFET used for Li-ion battery protection. It is offered in a 2mmx2mm MLPD with a very low thickness profile, 1mm maximum thickness. The device has extremely high power density, reducing the board size of the Li-ion battery power system. Designed for handheld devices with a high level of ESD protection.

| PRODUCT SUMMARY                            |                        |      |         |  |  |

|--------------------------------------------|------------------------|------|---------|--|--|

| $V_{(BR)DSS}$ $I_D = 250\mu A$ 20V Minimum |                        |      |         |  |  |

| r <sub>DS(ON)</sub>                        | V <sub>GS</sub> = 4.5V | 12mΩ | Typical |  |  |

#### **Features**

- · Monolithic dual MOSFET

- Low r<sub>DS(ON)</sub> in a small footprint

- · Ultra low gate charge and figure of merit

- MLPD 2mmx2mm package

- · Low thermal resistance

### **Applications**

- · Li-ion battery protection

- · Portable devices, cell phones, PDA

- · Rated for short-circuit and overcurrent protection

- . Integrated gate diodes provide ESD protection of 2.5kV HBM

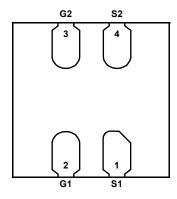

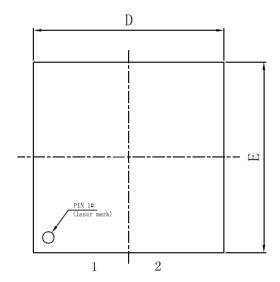

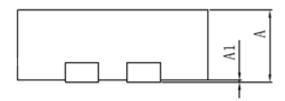

FIGURE 2. MLPD BOTTOM SIDE

# **Ordering Information**

| PART NUMBER | PART MARKING | TEMP RANGE (°C) | PACKAGE<br>(RoHS Compliant) |

|-------------|--------------|-----------------|-----------------------------|

| GWS9294     | 94           | -55 to +150     | 4 Ld QFN                    |

# **Pin Configuration**

GWS9294 (4 LD QFN) BOTTOM VIEW

# **Pin Descriptions**

| PIN# | PIN NAME  | DESCRIPTION    |

|------|-----------|----------------|

| 1    | S1        | Source of FET1 |

| 2    | G1        | Gate of FET1   |

| 3    | G2        | Gate of FET2   |

| 4    | <b>S2</b> | Source of FET2 |

### Absolute Maximum Ratings (Note 1)

| Drain-to-Source Voltage (VDS)             |

|-------------------------------------------|

| Gate-to-Source Voltage (V <sub>GS</sub> ) |

| Drain Current (I <sub>D</sub> ) (Note 2)  |

| T <sub>A</sub> = +25 °C                   |

| T <sub>A</sub> = +70 °C                   |

| Drain Current (Rthj <sub>Foot</sub> )     |

| T <sub>F</sub> = +25°C                    |

| Pulsed Drain Current (I <sub>DM</sub> )   |

| ESD Rating                                |

| Human Body Model                          |

#### **Thermal Information**

| Thermal Resistance (Typical)                           | $\theta_{JA}(^{\circC/W})$ | $\theta_{JF}(^{\circ}C/W)$ |

|--------------------------------------------------------|----------------------------|----------------------------|

| t ≤10s                                                 | 35                         |                            |

| Steady State                                           | 85                         | 16                         |

| Maximum Power Dissipation (PD) (Note 2)                |                            |                            |

| T <sub>A</sub> = +25°C                                 | / (10s) 1.47W              | (Steady State)             |

| T <sub>A</sub> = +70°C                                 |                            |                            |

| Junction and Storage Temperature Range (T <sub>J</sub> | , T <sub>stg</sub> )5!     | 5°C to +150°C              |

| Pb-Free Reflow Profile                                 |                            | see <u>TB493</u>           |

|                                                        |                            |                            |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 1.  $T_J = +25$  °C unless otherwise noted.

- 2. Surface mounted on FR4 board.

#### **Electrical Characteristics** T<sub>J</sub> = +25°C unless otherwise noted

| SYMBOL               | PARAMETER                                                              | TEST CONDITIONS                                       | MIN<br>(Note 3) | TYP (Note 4) | MAX<br>(Note 3) | UNIT |

|----------------------|------------------------------------------------------------------------|-------------------------------------------------------|-----------------|--------------|-----------------|------|

| STATIC               |                                                                        | ·                                                     | •               | '            |                 |      |

| V <sub>(BR)SSS</sub> | Drain-to-Source Breakdown Voltage                                      | V <sub>GS</sub> = 0V, I <sub>D</sub> = 250μA          | 20              |              |                 | V    |

| Isss                 | Zero Gate Voltage Drain Current                                        | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 20V           |                 |              | 1               | μΑ   |

| I <sub>GSS</sub>     | Gate Body Leakage                                                      | $V_{DS} = 0V V_{GS} = \pm 8V$                         |                 |              | ±10             | μΑ   |

| V <sub>GS(th)</sub>  | Gate Threshold Voltage                                                 | $V_{DS} = V_{GS}$ , $I_D = 1mA$                       | 0.5             | 0.6          | 1.5             | V    |

| r <sub>DS(ON)</sub>  | Drain-to-Source On-State Resistance (Note 5) (per MOSFET)              | V <sub>GS</sub> = 4.5V, I <sub>D</sub> = 6.5A         | 6               | 12           | 13              | mΩ   |

|                      |                                                                        | V <sub>GS</sub> = 4.0V, I <sub>D</sub> = 6.5A         | 7               | 13           | 14              | mΩ   |

|                      |                                                                        | V <sub>GS</sub> = 3.1V, I <sub>D</sub> = 6.0A         | 8               | 14           | 18              | mΩ   |

|                      |                                                                        | V <sub>GS</sub> = 2.5V, I <sub>D</sub> = 5.5A         | 9               | 16           | 20              | mΩ   |

| r <sub>SS(ON)</sub>  | Source-to-Source On-State Resistance (Note 5) (both MOSFETs in series) | V <sub>GS</sub> = 4.5V, I <sub>D</sub> = 6.5A         | 12              | 24           | 26              | mΩ   |

|                      |                                                                        | V <sub>GS</sub> = 4.0V, I <sub>D</sub> = 6.5A         | 13              | 25           | 28              | mΩ   |

|                      |                                                                        | V <sub>GS</sub> = 3.1V, I <sub>D</sub> = 6.0A         | 16              | 28           | 35              | mΩ   |

|                      |                                                                        | V <sub>GS</sub> = 2.5V, I <sub>D</sub> = 5.5A         | 17              | 32           | 40              | mΩ   |

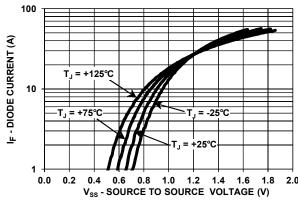

| V <sub>SD</sub>      | Source-to-Drain Diode Voltage                                          | V <sub>GS</sub> = 0, I <sub>S</sub> = 6.5A            | 0.5             | 0.8          | 1               | V    |

| DYNAMIC              |                                                                        |                                                       |                 |              |                 |      |

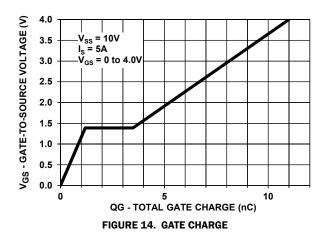

| Qg                   | Total Gate Charge                                                      | $V_{DS} = 10V, I_D = 5.0A, V_{GS} = 4.0V$             |                 | 11           |                 | nC   |

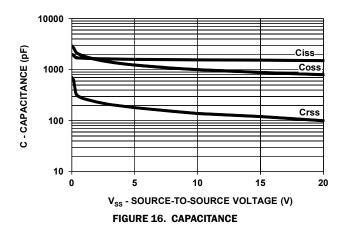

| C <sub>iss</sub>     | Input Capacitance                                                      | V <sub>DS</sub> = 10V, V <sub>GS</sub> = 0V, f = 1MHz |                 | 900          |                 | pF   |

| C <sub>oss</sub>     | Output Capacitance                                                     |                                                       |                 | 300          |                 | pF   |

| C <sub>rss</sub>     | Reverse Transfer Capacitance                                           |                                                       |                 | 150          |                 | pF   |

#### NOTES:

- 3. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 4. Typical values are for  $T_A = +25$ °C.

- 5. Good Kelvin measurement required.

Submit Document Feedback 3 intersil FN8786.1

December 22, 2015

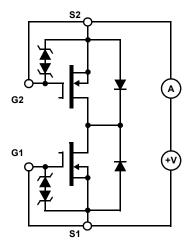

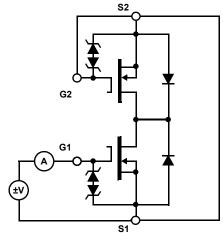

# **Test Circuit Examples for Measuring FET1 Key Parameters**

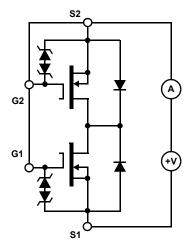

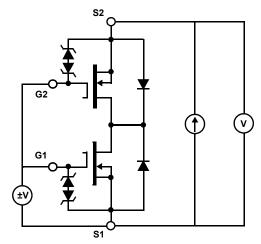

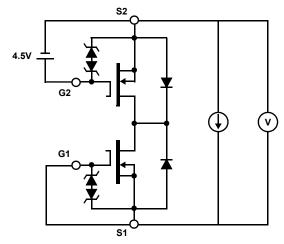

FIGURE 3.  $I_{\rm SSS}$  TEST CIRCUIT

FIGURE 4.  $I_{GSS}$  TEST CIRCUIT

FIGURE 5.  $V_{GS(th)}$  TEST CIRCUIT

FIGURE 6.  $r_{SS(ON)}$  TEST CIRCUIT

FIGURE 7.  $V_{\text{FS-S}}$  TEST CIRCUIT

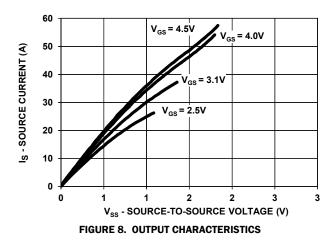

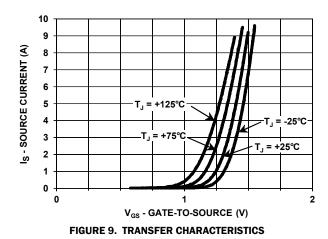

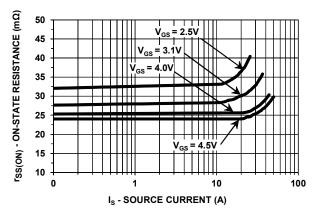

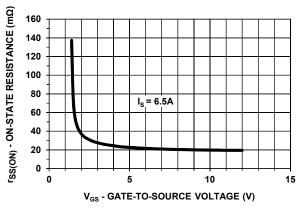

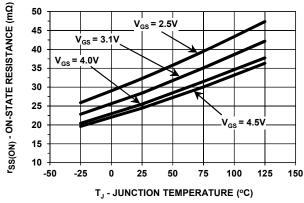

## **Typical Performance Curves**

FIGURE 10. SOURCE-TO-SOURCE ON-STATE RESISTANCE vs SOURCE CURRENT

FIGURE 11. SOURCE-TO-SOURCE ON-STATE RESISTANCE vs GATE-TO-SOURCE VOLTAGE

FIGURE 12. SOURCE-TO-SOURCE ON-STATE RESISTANCE vs

JUNCTION TEMPERATURE

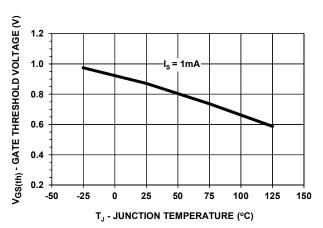

FIGURE 13. GATE THRESHOLD VOLTAGE vs JUNCTION TEMPERATURE

## Typical Performance Curves (Continued)

FIGURE 15. SOURCE-TO-SOURCE DIODE FORWARD VOLTAGE

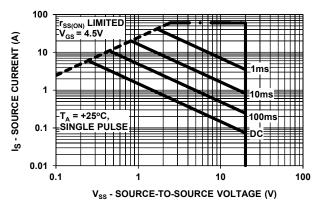

FIGURE 17. MAXIMUM RATED FORWARD BIASED SAFE OPERATING

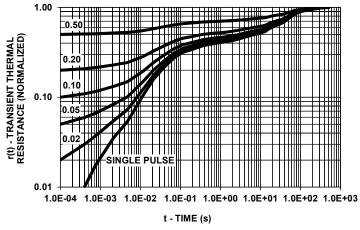

FIGURE 18. TRANSIENT THERMAL RESPONSE, JUNCTION-TO-AMBIENT

Submit Document Feedback 6 FN8786.1 intersil

### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE              | REVISION | CHANGE                                                                               |  |

|-------------------|----------|--------------------------------------------------------------------------------------|--|

| December 22, 2015 | FN8786.1 | Added "Note 1. T <sub>J</sub> = +25°C unless otherwise noted." to Abs Max on page 3. |  |

| October 30, 2015  | FN8786.0 | Initial release.                                                                     |  |

### **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Submit Document Feedback FN8786 1 intersil December 22, 2015

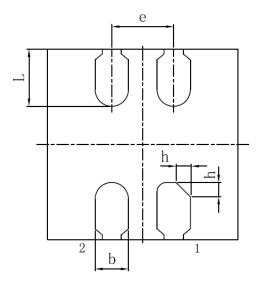

## **Package Outline and Dimensions**

| Pin | Node     |

|-----|----------|

| 1   | Source 1 |

| 2   | Gate 1   |

| 3   | Gate 2   |

| 4   | Source 2 |

| Symbol | Min            | Nom  | Max   |  |

|--------|----------------|------|-------|--|

| A      | 0.70           |      | 1.00  |  |

| A1     |                | 0.02 | 0.05  |  |

| b      | 0.275          |      | 0.400 |  |

| D      | 2.00 BSC       |      |       |  |

| Е      | 2.00 BSC       |      |       |  |

| e      | 0.65 BSC       |      |       |  |

| L      | 0.55 0.60 0.65 |      |       |  |

| h      | 0.10           | 0.15 | 0.20  |  |

All dimensions in mm

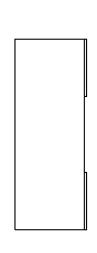

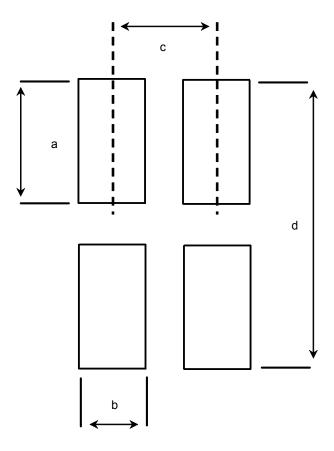

## **Mounting Pad Layout and Dimensions**

| Symbol | Min      | Nom   | Max   |

|--------|----------|-------|-------|

| a      | 0.788    | 0.838 | 0.888 |

| b      | 0.358    | 0.381 | 0.404 |

| С      | 0.65 BSC |       |       |

| d      | 2.22     | 2.365 | 2.50  |

All dimensions in mm