# Intel® 88CO196EC CHMOS 16-Bit Microcontroller

# **Datasheet**

# **Product Features**

- 256 Kbytes on-chip flash program memory

- 40 MHz operation

- Optional clock quadrupler

- Programmable clock output signal (CLKOUT)

- 2 Mbytes of linear address space

- 1.25 Kbytes of register RAM

- 2.75 Kbytes of code RAM

- · Register-to-register architecture

- Stack overflow/underflow monitor with user-defined upper and lower stack pointer boundary limits

- Two peripheral interrupt handlers (PIHs) provide direct hardware handling of up to 45 interrupts

- Up to 59 I/O port pins

- Full-duplex serial port with dedicated baud-rate generator

- Enhanced synchronous serial I/O unit (SSIO)

- 16 10-bit A/D channels with auto-scan mode and dedicated results registers

- Controller area network (CAN) 2.0 networking protocol

- Serial debug unit provides read and write access to code RAM with no CPU overhead

- Chip-select unit (CSU)

- Three chip-select pins

- Dynamic demultiplexed/multiplexed address/data bus for each chip-select

- Programmable wait states

(0, 1, 2, or 3) for each chip-select

- Programmable bus width (8- or 16-bit) for each chip-select

- Programmable address range for each chip-select

- Event processor array (EPA)

- Two flexible 16-bit timer/counters

- Five high-speed capture/compare channels with a lock feature for noise filtering

- 10 enhanced high-speed capture/compare channels with period and duty cycle measurement capability, as well as a lock feature for noise filtering

- Complete system development support

- Packaging

- 132-pin PQFP

- Temperature Offerings

- Commercial (0C 70C)

- Extended (-40C 85C)

The Intel<sup>®</sup> 88CO196EC CHMOS 16-Bit Microcontroller is the first member of the MCS<sup>®</sup>96 family of microcontrollers to integrate flash memory on-chip. The Intel® 88CO196EC, with its integrated flash memory, brings a new level of integration that offers embedded system designers cost-effective solutions.

Order Number: 273970-002 August, 2004

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 88CO196EC CHMOS 16-Bit Microcontroller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xocale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © February, 2004, Intel Corporation

| 1.0            | Produc   | t Overview                                                         |    |

|----------------|----------|--------------------------------------------------------------------|----|

|                | 1.1      | Nomenclature Overview                                              | 8  |

| 2.0            | Pinout.  |                                                                    | 9  |

| 3.0            | Signals  |                                                                    | 11 |

| 4.0            | Addres   | s Map                                                              | 21 |

| 5.0            | Electric | al Characteristics                                                 | 23 |

|                | 5.1      | DC Characteristics                                                 | 23 |

| 6.0            | Explana  | ation of AC Symbols                                                | 25 |

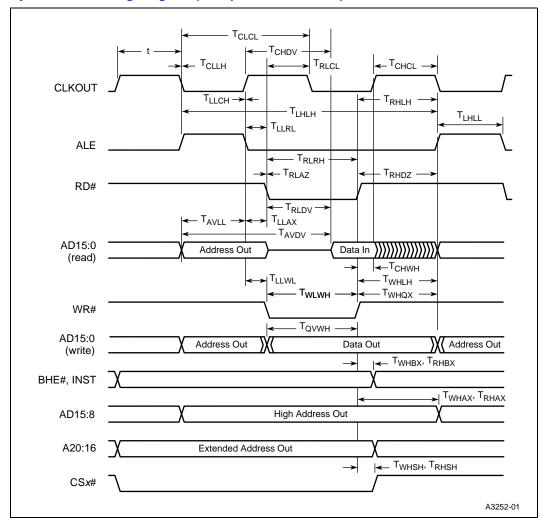

|                | 6.1      | AC Characteristics — Multiplexed Bus Mode                          | 26 |

|                | 6.2      | AC Characteristics — Demultiplexed Bus Mode                        |    |

|                | 6.3      | Deferred Bus Timing Mode                                           |    |

|                | 6.4      | AC Characteristics — Serial Port, Mode 0                           |    |

|                | 6.5      | AC Characteristics — Synchronous Serial Port                       |    |

|                | 6.6      | AC Characteristics — Serial Debug Unit                             |    |

|                | 6.7      | A/D Sample and Conversion Times                                    |    |

|                |          | 6.7.1 AC Characteristics — A/D Converter, 10-Bit Mode              |    |

|                |          | 6.7.2 AC Characteristics — A/D Converter, 8-Bit Mode               |    |

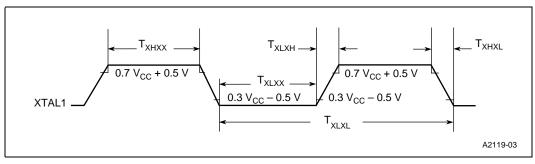

|                | 6.8      | External Clock Drive                                               |    |

|                | 6.9      | Test Output Waveforms                                              |    |

|                | 6.10     | Flash Memory Erase Performance                                     |    |

| 7.0            | Therma   | al Characteristics                                                 | 43 |

| <b>Figures</b> |          |                                                                    |    |

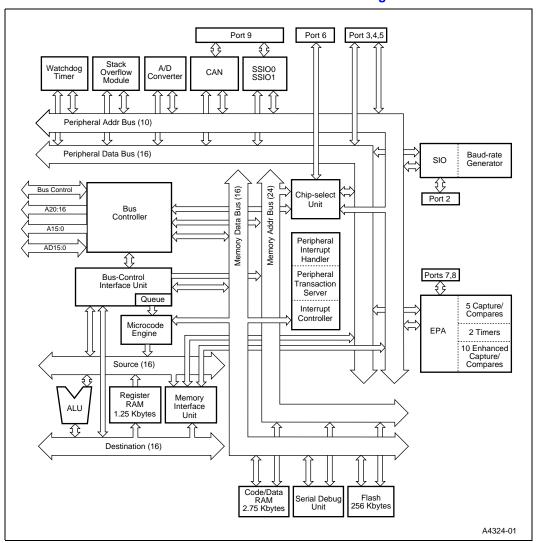

|                | 1        | Intel® 88CO196EC CHMOS 16-Bit Microcontroller Block Diagram        | 7  |

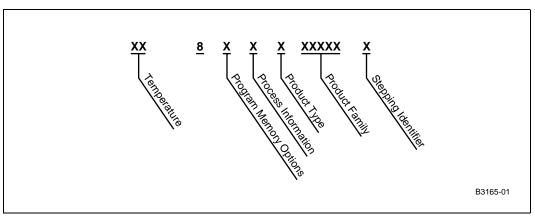

|                | 2        | Product Nomenclature                                               |    |

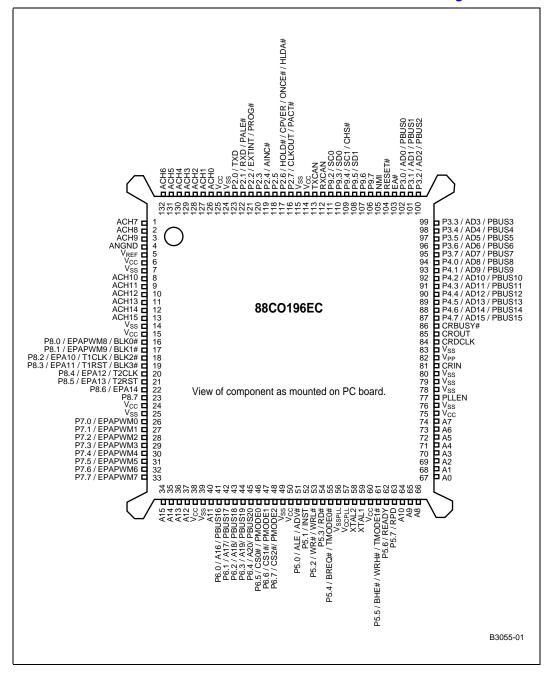

|                | 3        | Intel® 88CO196EC CHMOS 16-Bit Microcontroller 132-Pin PQFP Package | 9  |

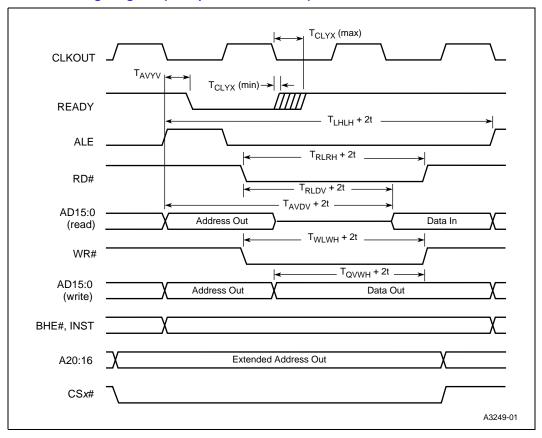

|                | 4        | System Bus Timing Diagram (Multiplexed Bus Mode)                   | 28 |

|                | 5        | READY Timing Diagram (Multiplexed Bus Mode)                        |    |

|                | 6        | System Bus Timing Diagram (Demultiplexed Bus Mode)                 |    |

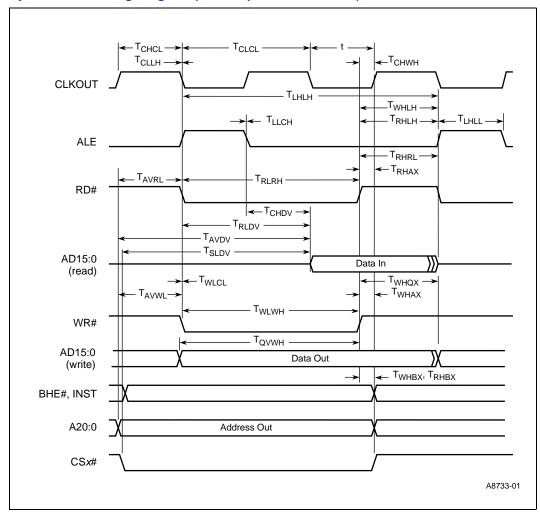

|                | 7        | READY Timing Diagram (Demultiplexed Bus Mode)                      |    |

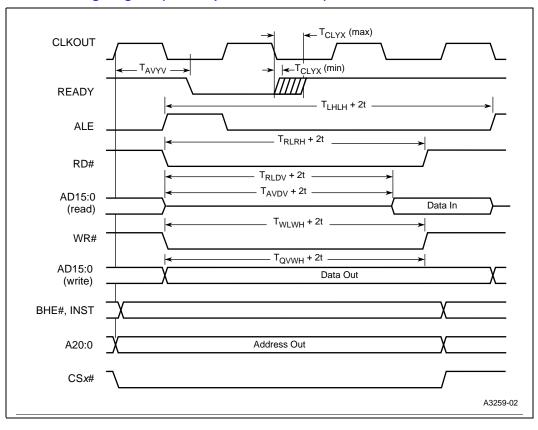

|                | 8        | Deferred Bus Mode Timing Diagram                                   |    |

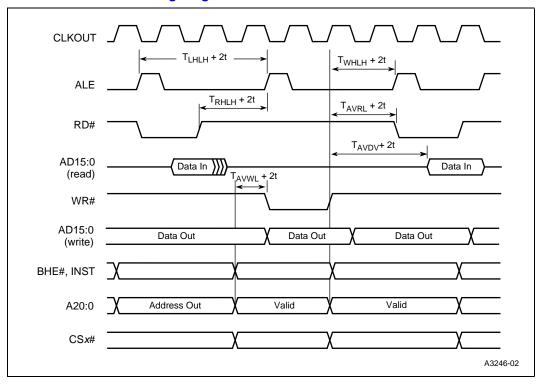

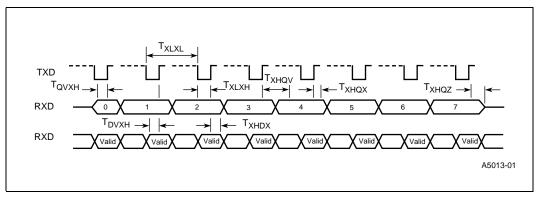

|                | 9        | Serial Port Waveform — Mode                                        |    |

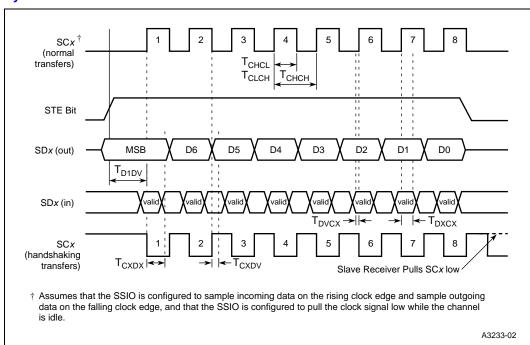

|                | 10       | Synchronous Serial Port                                            |    |

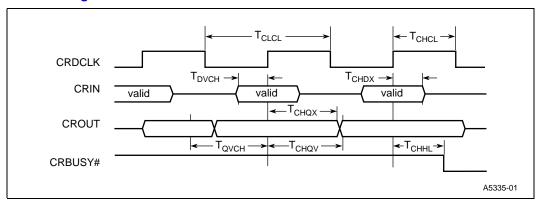

|                | 11       | Serial Debug Unit                                                  |    |

|                | 12       | External Clock Drive Waveforms                                     |    |

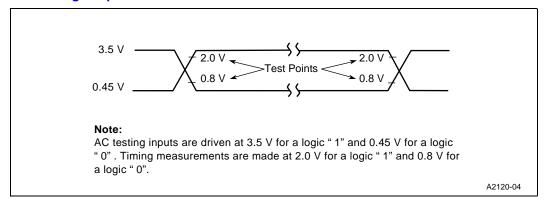

|                | 13       | AC Testing Output Waveforms                                        |    |

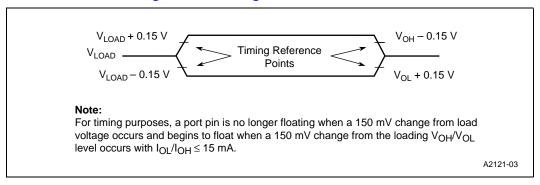

|                | 14       | Float Waveforms During 5.0 Volt Testing                            | 42 |

# **Tables**

| 1  | Description of Product Nomenclature                                 | 8  |

|----|---------------------------------------------------------------------|----|

| 2  | Intel® 88CO196EC CHMOS 16-Bit Microcontroller                       |    |

|    | 132-Pin PQFP Package Pin Assignments                                | 10 |

| 3  | Signal Descriptions                                                 |    |

| 4  | Intel® 88CO196EC CHMOS 16-Bit Microcontroller Address Map           | 21 |

| 5  | DC Characteristics at V <sub>cc</sub> = 4.75 V – 5.25 V             | 23 |

| 6  | AC Timing Symbol Definitions                                        | 25 |

| 7  | AC Characteristics, Multiplexed Bus Mode                            |    |

| 8  | AC Characteristics, Demultiplexed Bus Mode                          | 30 |

| 9  | Serial Port Timing — Mode 0 <sup>†</sup>                            | 35 |

| 10 | Synchronous Serial Port Timing                                      | 36 |

| 11 | Serial Debug Unit Timing                                            | 37 |

| 12 | 10-bit A/D Operating Conditions                                     |    |

| 13 | 10-Bit Mode A/D Characteristics Over Specified Operating Conditions | 39 |

| 14 | 8-Bit A/D Operating Conditions                                      | 40 |

| 15 | 8-Bit Mode A/D Characteristics Over Specified Operating Conditions  | 40 |

| 16 | External Clock Drive                                                |    |

| 17 | Flash Memory Erase Performance                                      | 42 |

| 18 | Thermal Characteristics                                             |    |

|    |                                                                     |    |

# Revision History

| Date          | Revision | Description                                                                                                                                              |

|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2004 | 001      | Initial release                                                                                                                                          |

| August 2004   | 002      | To address the fact that many of the package prefix variables have changed, all package prefix variables in this document are now indicated with an "x". |

# 1.0 Product Overview

Figure 1. Intel® 88CO196EC CHMOS 16-Bit Microcontroller Block Diagram

The Intel® 88CO196EC CHMOS 16-Bit Microcontroller is highly integrated with an enhanced peripheral set. The integrated CAN 2.0 networking protocol provides for efficient communication to a high-speed CAN bus. The serial debug unit (SDU) provides system debug and development capabilities. The SDU can set a single hardware breakpoint. In addition, the SDU provides read and write access to code RAM through a high-speed, dedicated serial link. A stack overflow/underflow monitor assists in code development by causing a nonmaskable interrupt if the stack pointer crosses a user-defined boundary. The 16-channel A/D converter supports an auto-scan mode that operates with no CPU overhead. Each A/D channel has a dedicated result register. The EPA supports high-speed event captures and output compares with 15 programmable, high-speed channels.

# 1.1 Nomenclature Overview

# Figure 2. Product Nomenclature

# Table 1. Description of Product Nomenclature

| Parameter           | Options | Description                                                                                            |

|---------------------|---------|--------------------------------------------------------------------------------------------------------|

| Temperature Options | x<br>x  | Commercial temperature range (0° C to 70° C case)<br>Extended temperature range (–40° C to 85° C case) |

| Program-Memory      | х       | Internal flash memory                                                                                  |

| Process Information | С       | CHMOS                                                                                                  |

| Product Type        | 0       | Standard Embedded Product                                                                              |

| Product Family      | 196EC   |                                                                                                        |

| Device Speed        | no mark | 40 MHz                                                                                                 |

# 2.0 Pinout

Figure 3. Intel® 88CO196EC CHMOS 16-Bit Microcontroller 132-Pin PQFP Package

Table 2. Intel® 88CO196EC CHMOS 16-Bit Microcontroller 132-Pin PQFP Package Pin Assignments

| Pin | Name                   | Pin | Name                   | Pin | Name                   |

|-----|------------------------|-----|------------------------|-----|------------------------|

| 1   | ACH7                   | 45  | P6.4/A20/PBUS20        | 89  | P4.5/AD13/PBUS13       |

| 2   | ACH8                   | 46  | P6.5/CS0#/PMODE0       | 90  | P4.4/AD12/PBUS12       |

| 3   | ACH9                   | 47  | P6.6/CS1#/PMODE1       | 91  | P4.3/AD11/PBUS11       |

| 4   | ANGND                  | 48  | P6.7/CS2#/PMODE2       | 92  | P4.2/AD10/PBUS10       |

| 5   | V <sub>REF</sub>       | 49  | V <sub>SS</sub>        | 93  | P4.1/AD9/PBUS9         |

| 6   | V <sub>CC</sub>        | 50  | V <sub>CC</sub>        | 94  | P4.0/AD8/PBUS8         |

| 7   | V <sub>SS</sub>        | 51  | P5.0/ALE/ADV#          | 95  | P3.7/AD7/PBUS7         |

| 8   | ACH10                  | 52  | P5.1/INST              | 96  | P3.6/AD6/PBUS6         |

| 9   | ACH11                  | 53  | P5.2/WR#/WRL#          | 97  | P3.5/AD5/PBUS5         |

| 10  | ACH12                  | 54  | P5.3/RD#               | 98  | P3.4/AD4/PBUS4         |

| 11  | ACH13                  | 55  | P5.4/BREQ#/TMODE0#     | 99  | P3.3/AD3/PBUS3         |

| 12  | ACH14                  | 56  | V <sub>SSPLL</sub>     | 100 | P3.2/AD2/PBUS2         |

| 13  | ACH15                  | 57  | V <sub>CCPLL</sub>     | 101 | P3.1/AD1/PBUS1         |

| 14  | V <sub>SS</sub>        | 58  | XTAL2                  | 102 | P3.0/AD0/PBUS0         |

| 15  | V <sub>CC</sub>        | 59  | XTAL1                  | 103 | EA#                    |

| 16  | P8.0/EPAPWM8/BLK0#     | 60  | V <sub>CC</sub>        | 104 | RESET#                 |

| 17  | P8.1/EPAPWM9/BLK1#     | 61  | P5.5/BHE#/WRH#/TMODE1# | 105 | NMI                    |

| 18  | P8.2/EPA10/T1CLK/BLK2# | 62  | P5.6/READY             | 106 | P9.7                   |

| 19  | P8.3/EPA11/T1RST/BLK3# | 63  | P5.7/RPD               | 107 | P9.6                   |

| 20  | P8.4/EPA12/T2CLK       | 64  | A10                    | 108 | P9.5/SD1               |

| 21  | P8.5/EPA13/T2RST       | 65  | A9                     | 109 | P9.4/SC1/CHS#          |

| 22  | P8.6/EPA14             | 66  | A8                     | 110 | P9.3/SD0               |

| 23  | P8.7                   | 67  | A0                     | 111 | P9.2/SC0               |

| 24  | V <sub>CC</sub>        | 68  | A1                     | 112 | RXCAN                  |

| 25  | V <sub>SS</sub>        | 69  | A2                     | 113 | TXCAN                  |

| 26  | P7.0/EPAPWM0           | 70  | A3                     |     | V <sub>CC</sub>        |

| 27  | P7.1/EPAPWM1           | 71  | A4                     | 115 | V <sub>SS</sub>        |

| 28  | P7.2/EPAPWM2           | 72  | A5                     | 116 | P2.7/CLKOUT/PACT#      |

| 29  | P7.3/EPAPWM3           | 73  | A6                     | 117 | P2.6/HLDA#/ONCE#/CPVER |

| 30  | P7.4/EPAPWM4           | 74  | A7                     | 118 | P2.5 HOLD#             |

| 31  | P7.5/EPAPWM5           | 75  | V <sub>CC</sub>        | 119 | P2.4/AINC#             |

| 32  | P7.6/EPAPWM6           | 76  | V <sub>SS</sub>        | 120 | P2.3                   |

| 33  | P7.7/EPAPWM7           | 77  | PLLEN                  | 121 | P2.2/EXTINT/PROG#      |

| 34  | A15                    | 78  | V <sub>SS</sub>        | 122 | P2.1/RXD/PALE#         |

| 35  | A14                    | 79  | V <sub>SS</sub>        |     | P2.0/TXD               |

| 36  | A13                    | 80  | V <sub>SS</sub>        | 124 | V <sub>SS</sub>        |

| 37  | A12                    | 81  | CRIN                   | 125 | V <sub>CC</sub>        |

| 38  | V <sub>CC</sub>        | 82  | V <sub>PP</sub>        | l   | ACH0                   |

| 39  | V <sub>SS</sub>        | 83  | V <sub>SS</sub>        | 127 |                        |

| 40  | A11                    | 84  | CRDCLK                 |     | ACH2                   |

| 41  | P6.0/A16/PBUS16        | 85  | CROUT                  |     | ACH3                   |

| 42  | P6.1/A17/PBUS17        | 86  | CRBUSY#                | 130 | ACH4                   |

| 43  | P6.2/A18/PBUS18        | 87  | P4.7/AD15/PBUS15       | 131 |                        |

| 44  | P6.3/A19/PBUS19        | 88  | P4.6/AD14/PBUS14       | 132 | ACH6                   |

# 3.0 Signals

# Table 3. Signal Descriptions (Sheet 1 of 9)

| A15:0  O System Address Bus These address pins provide address bits 0–15 during the entire external memory cycle during both multiplexed and dermultiplexed bus modes.  Address Pins 16–20 These address bits 16–20 during the entire external memory cycle during both multiplexed and dermultiplexed bus modes.  Address Pins 16–20 These address bits 16–20 during the entire external memory cycle during both multiplexed and dermultiplexed bus modes, supporting extended addressing of the 2-Mbyte address space.  NOTE: Internally, there are 24 address bits; however, only 21 external address pins (A20:0) are implemented. The internal address space is 16 Mbytes (000000–FFFFFFH). The microcontroller resets to FF2080H in internal address space is 2 Mbytes (000000–FFFFFFH). The microcontroller resets to FF2080H in internal memory.  A20:16 share package pins with P6.4:0 and PBUS20:16.  ACH15:0  Analog Channels These signals are analog inputs to the A/D converter. The ANGND and V <sub>REF</sub> pins must be connected for the A/D converter to function.  Address/Data Lines The function of these pins depends on the bus width and mode.  16-bit Multiplexed Bus Mode:  AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode:  AD15:0 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle.  16-bit Demultiplexed Mode:  AD15:0 drive or receive data during the entire bus cycle.  AD15:0 drive or receive data during the entire bus cycle.  AD15:0 drive or receive data during the entire bus cycle.  AD7:0 drive or receive data during the entire bus cycle.  AD7:0 drive or receive data during the entire bus cycle.  AD7:0 drive or receive data during the entire bus cycle.  AD7:0 drive or receive data during the entire bus cycle.  AD7:0 drive or receive data during the entire bus cycle.  AD7:0 drive or receive data during the entire bus cycle in progress and is returned high as soon as th | Name      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Pins 16–20 These address pins provide address bits 16–20 during the entire external memory cycle during both multiplexed and demultiplexed bus modes, supporting extended addressing of the 2-Mbyte address bits; however, only 21 external address spins (A20:0) are implemented. The internal address space is 2 Mbytes (000000–FFFFFFH) and the external address space is 2 Mbytes (000000–FFFFFFH). The microcontroller resets to FF2080H in internal memory or 1F2080H in external memory.  A20:16 share package pins with P6.4:0 and PBUS20:16.  ACH15:0  I Analog Channels These signals are analog inputs to the A/D converter. The ANGND and V <sub>REF</sub> pins must be connected for the A/D converter to function.  Address/Data Lines The function of these pins depends on the bus width and mode.  16-bit Multiplexed Bus Mode: AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  AD15:0 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  AD15:0 drive or receive data during the entire bus cycle.  AD15:0 drive or receive data during the entire bus cycle.  AD15:0 drive or receive data during the entire bus cycle. AD15:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle. AD7:0 drive or receive data during the entire bus cycle is progress and is returned high as soon as the bus cycle completes. AD7:0 drive or receive data during the entire bus cycle is in progress and is retu |           |      | System Address Bus                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A20:16           | A15:0     | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A20:16  A20:16  A20:16  A20:16 in expension of the part of the par           |           |      | Address Pins 16–20                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ACH15:0  I Analog Channels These signals are analog inputs to the A/D converter. The ANGND and V <sub>REF</sub> pins must be connected for the A/D converter to function.  Address/Data Lines The function of these pins depends on the bus width and mode.  16-bit Multiplexed Bus Mode: AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle. 8-bit Multiplexed Bus Mode: AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–17 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the entire bus cycle.  8-bit Demultiplexed Mode: AD15:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus. AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes. An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write, JAINC# is sampled after each location is programmed or dumped. If AINC# is                                | A20:16    | 0    | cycle during both multiplexed and demultiplexed bus modes, supporting extended addressing of the 2-Mbyte address space.  NOTE: Internally, there are 24 address bits; however, only 21 external address pins (A20:0) are implemented. The internal address space is 16 Mbytes (000000–FFFFFFH) and the external address space is 2 Mbytes (000000–1FFFFFH). The microcontroller resets to FF2080H in internal memory or 1F2080H in external memory. |

| ACH15:0  I These signals are analog inputs to the A/D converter. The ANGND and V <sub>REF</sub> pins must be connected for the A/D converter to function.  Address/Data Lines The function of these pins depends on the bus width and mode.  16-bit Multiplexed Bus Mode:  AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode:  AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Demultiplexed Mode:  AD15:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AlNC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                            |           |      | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                                                                                                                                                                                                                                                                                                                                                                                                             |

| The ANGND and V <sub>REF</sub> pins must be connected for the A/D converter to function.  Address/Data Lines The function of these pins depends on the bus width and mode.  16-bit Multiplexed Bus Mode:  AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode:  AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the entire bus cycle.  8-bit Demultiplexed Mode:  AD15:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AlNC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                               | ACI 145.0 | ١.,  |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address/Data Lines The function of these pins depends on the bus width and mode.  16-bit Multiplexed Bus Mode:  AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode:  AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the entire bus cycle.  8-bit Demultiplexed Mode:  AD15:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sassred, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                            | ACH 15.0  | ı    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| The function of these pins depends on the bus width and mode.  16-bit Multiplexed Bus Mode:  AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode:  AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle.  16-bit Demultiplexed Mode:  AD15:0 drive or receive data during the entire bus cycle.  8-bit Demultiplexed Mode:  AD7:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AlNC# is sampled after each location is programmed or dumped. If AlNC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                             |           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode:  AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle.  16-bit Demultiplexed Mode:  AD15:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is saserted, the address is incremented and the next data word is programmed or dumped. If AINC# is                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AD15:0 drive address bits 0–15 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.  8-bit Multiplexed Bus Mode:  AD15:8 drive address bits 8–15 during the entire bus cycle. AD7:0 drive address bits 0–7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle and drive or receive data during the second half of the bus cycle.  16-bit Demultiplexed Mode:  AD15:0 drive or receive data during the entire bus cycle.  8-bit Demultiplexed Mode:  AD7:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                          |           |      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AD15:0  I/O  I/O  I/O  I/O  I/O  I/O  I/O  I/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AD15:0    I/O   bits 0-7 during the first half of the bus cycle and drive or receive data during the second half of the bus cycle.    16-bit Demultiplexed Mode: AD15:0 drive or receive data during the entire bus cycle.   8-bit Demultiplexed Mode: AD7:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.   AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.     Address Valid   This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.   An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.    Auto Increment   During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |      | receive data during the second half of the bus cycle.                                                                                                                                                                                                                                                                                                                                                                                               |

| ADV# ADV# shares a package pin with P5.0 and ALE.  AINC#  AD15:0 drive or receive data during the entire bus cycle.  8-bit Demultiplexed Mode:  AD7:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses.  ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory.  ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AD15:0    | I/O  | bits 0-7 during the first half of the bus cycle and drive or receive data during the                                                                                                                                                                                                                                                                                                                                                                |

| ADV#  ADV#  O  8-bit Demultiplexed Mode:  AD7:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses.  ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |      | 16-bit Demultiplexed Mode:                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AD7:0 drive or receive data during the entire bus cycle. AD15:8 drive the data that is currently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |      | AD15:0 drive or receive data during the entire bus cycle.                                                                                                                                                                                                                                                                                                                                                                                           |

| ADV#  ADV#  I scurrently on the high byte of the internal bus.  AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.  Address Valid  This active-low output signal is asserted only during external memory accesses.  ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory.  ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ADV#  Address Valid  This active-low output signal is asserted only during external memory accesses.  ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory.  ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADV#  O  This active-low output signal is asserted only during external memory accesses. ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |      | AD15:8 share package pins with P4.7:0. AD7:0 share package pins with P3.7:0.                                                                                                                                                                                                                                                                                                                                                                        |

| ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is returned high as soon as the bus cycle completes.  An external latch can use this signal to demultiplex the address from the address/data bus. A decoder can also use this signal to generate chip selects for external memory. ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |      | Address Valid                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bus. A decoder can also use this signal to generate chip selects for external memory.  ADV# shares a package pin with P5.0 and ALE.  Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADV#      | 0    | ADV# indicates that valid address information is available on the system address/data bus. The signal remains low while a valid bus cycle is in progress and is                                                                                                                                                                                                                                                                                     |

| Auto Increment  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |      | bus. A decoder can also use this signal to generate chip selects for external memory.                                                                                                                                                                                                                                                                                                                                                               |

| AINC#  During slave programming, this active-low input enables the auto-increment feature. (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AINC#  I  (Auto increment allows reading or writing of sequential flash memory locations, without requiring address transactions across the programming bus for each read or write.) AINC# is sampled after each location is programmed or dumped. If AINC# is asserted, the address is incremented and the next data word is programmed or dumped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |