## Intel 8255x 10/100 Mbps Ethernet Controller Family

**Open Source Software Developer Manual**

January 2003

Information in this document is provided in connection with Intel<sup>®</sup> products. This specification, the Intel 8255x 10/100 Mbps Ethernet Controller Family Open Source Software Developer Manual, is provided "as is" with no warranties whatsoever, including any warranty of merchantability, noninfringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample. Intel products are not intended for use in medical, life saving, life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 82557, 82558, 82559, 82550, and 82551 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. It is intended to enable the maintenance of the open source Intel<sup>®</sup> PRO/100 drivers for the Intel<sup>®</sup> PRO/100 family of adapters. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document. Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © 2003, Intel Corporation.

\* Other product and corporate names may be trademarks of other companies and are used only for explanation and to the owners' benefit, without intent to infringe.

# int<sub>el</sub>. Contents

| 1 | Introd                   | luction.                                                                                                                                                                             |                                                                                                                                                                                                                                     | 1                                                                                               |

|---|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|   | 1.1<br>1.2               | Docum<br>1.2.1                                                                                                                                                                       | ent Conventions<br>Device References                                                                                                                                                                                                | 2<br>2                                                                                          |

|   |                          | 1.2.2<br>1.2.3<br>1.2.4                                                                                                                                                              | Numbering<br>Signal Name Representation<br>Memory Alignment Terminology                                                                                                                                                             | 2                                                                                               |

| 2 | Adapt                    | ter and                                                                                                                                                                              | Controller Overview                                                                                                                                                                                                                 |                                                                                                 |

|   | 2.1<br>2.2               | Adapte                                                                                                                                                                               | r Block Diagram<br>st Ethernet MAC Features<br>82557 Features<br>82558 Features                                                                                                                                                     | 5<br>6<br>6                                                                                     |

|   | 2.3                      | 2.2.3<br>Workine                                                                                                                                                                     | 82559, 82550, 82551, and 82562 Features<br>g with the Physical Layer                                                                                                                                                                |                                                                                                 |

| 3 | Powe                     |                                                                                                                                                                                      | jement Interface                                                                                                                                                                                                                    |                                                                                                 |

| - | 3.1<br>3.2<br>3.3<br>3.4 | Low Po<br>Device<br>Power                                                                                                                                                            | wer Mode Requirements<br>Power States<br>Management Registers<br>peration                                                                                                                                                           | 9<br>9<br>9                                                                                     |

| 4 | PCI In                   | terface                                                                                                                                                                              |                                                                                                                                                                                                                                     | 11                                                                                              |

|   | 4.1                      | $\begin{array}{r} 4.1.1\\ 4.1.2\\ 4.1.3\\ 4.1.4\\ 4.1.5\\ 4.1.6\\ 4.1.7\\ 4.1.8\\ 4.1.9\\ 4.1.10\\ 4.1.11\\ 4.1.12\\ 4.1.13\\ 4.1.15\\ 4.1.15\\ 4.1.16\\ 4.1.17\\ 4.1.18\end{array}$ | Expansion ROM Base Address Register (Offset 30)<br>The Capabilities Pointer (Offset 34)<br>Interrupt Line (Offset 3C)<br>Interrupt Pin (Offset 3D)<br>Max_Lat / Min_Gnt (Offset 3E)<br>Power Management PCI Configuration Registers | $\begin{array}{c} 12\\ 12\\ 12\\ 13\\ 14\\ 14\\ 15\\ 16\\ 16\\ 17\\ 17\\ 18\\ 18\\ \end{array}$ |

|   | 4.2                      | PCI Co<br>4.2.1<br>4.2.2<br>4.2.3                                                                                                                                                    | mmand Usage<br>Memory Write and Invalidate<br>Read Align<br>Odd Byte Alignment Support                                                                                                                                              | 22<br>23                                                                                        |

| 5 | EEP  | ROM Inte       | erface                                                     | 25  |

|---|------|----------------|------------------------------------------------------------|-----|

| 6 | Host | Softwar        | re Interface                                               | 27  |

|   | 6.1  | The Sh         | nared Memory Architecture                                  | 27  |

|   | 6.2  | Initializ      | ring the LAN Controller                                    |     |

|   |      | 6.2.1          | LAN Controller Addressing Format                           |     |

|   | 6.3  |                | Iling the Device                                           |     |

|   |      | 6.3.1          | Control / Status Registers (CSR)                           |     |

|   |      | 6.3.2          | System Control Block (SCB)                                 |     |

|   |      | 6.3.3          | PORT Interface                                             |     |

|   |      | 6.3.4          | EEPROM Control Register                                    |     |

|   |      | 6.3.5          | Management Data Interface Control Register                 |     |

|   |      | 6.3.6          | Receive Byte Count Register                                |     |

|   |      | 6.3.7          | Early Receive Interrupt                                    |     |

|   |      | 6.3.8          | Flow Control Register                                      |     |

|   |      | 6.3.9          | Power Management Driver Register                           |     |

|   |      | 6.3.10         | 5                                                          |     |

|   | 6.4  | 6.3.11         | General Status Register                                    |     |

|   | 6.4  | 6.4.1          | d Memory Structures<br>Action Commands and Operating Modes |     |

|   |      | 6.4.1<br>6.4.2 | Specific Action Commands                                   |     |

|   |      | 6.4.2<br>6.4.3 | Receive Operation                                          |     |

|   | 6.5  |                | and Unit and Receive Unit Operation                        |     |

|   | 0.0  | 6.5.1          | Starting and Completing Control Commands                   |     |

|   |      | 6.5.2          | Generating and acknowledging interrupts                    |     |

|   |      | 6.5.3          | Command Unit Control                                       |     |

|   |      | 6.5.4          | Receive Unit Control                                       |     |

|   |      | 6.5.5          | Updating SCB Status                                        |     |

|   | 6.6  |                | Control                                                    |     |

|   |      | 6.6.1          | PHY Based Flow Control                                     |     |

|   |      | 6.6.2          | Frame Based Flow Control                                   |     |

|   |      | 6.6.3          | Priority Aware Frame Based Flow Control                    |     |

|   |      | 6.6.4          | Half Duplex Flow Control                                   |     |

|   | 6.7  | Collisio       | on Backoff Modification in Switched Environments           |     |

| 7 | Phys | sical Lay      | ver Interface                                              |     |

|   | 7.1  |                | gement Data Interface (MDI)                                |     |

|   | 7.2  |                | egister Set                                                |     |

|   | 1.2  | 7.2.1          | Control Register: Register 0                               |     |

|   |      | 7.2.2          | Status Register: Register 1                                |     |

|   |      | 7.2.3          | Identification Registers: Registers 2 and 3                |     |

|   |      | 7.2.4          | Auto-Negotiation Advertisement Register: Register 4        |     |

|   |      | 7.2.5          | Auto-Negotiation Link Partner Ability Register: Register 5 |     |

|   |      | 7.2.6          | Auto-Negotiation Expansion Register: Register 6            |     |

|   | 7.3  |                | 2555 Specific Registers                                    |     |

|   |      | 7.3.1          | Status and Control Register: Register 16                   |     |

|   |      | 7.3.2          | Special Control Register: Register 17                      |     |

|   |      | 7.3.3          | Clock Synthesis Test and Control Register: Register 18     |     |

|   |      | 7.3.4          | 100BASE-TX Receive False Carrier Counter: Register 19      | 124 |

|   |      | 7.3.5          | 100Base-TX Receive Disconnect Counter: Register 20         | 124 |

|   |      |                |                                                            |     |

|     | 7.3.6   | 100BASE-TX Receive Error Frame Counter: Register 21 |     |

|-----|---------|-----------------------------------------------------|-----|

|     | 7.3.7   | Receive Symbol Error Counter: Register 22           |     |

|     | 7.3.8   | 100BASE-TX Receive EOF Error Counter: Register 23   | 125 |

|     | 7.3.9   | 10BASE-T Receive EOF Error Counter: Register 24     |     |

|     | 7.3.10  | · · · · · · · · · · · · · · · · · · ·               |     |

|     | 7.3.11  | Equalizer Control and Status Register: Register 26  |     |

|     | 7.3.12  | Special Control Register: Register 27               |     |

| 7.4 |         | legotiation Functionality                           |     |

|     | 7.4.1   | Description                                         |     |

|     | 7.4.2   | Parallel Detection                                  | 129 |

| 7.5 | Vendo   | r-Specific PHY Programming                          | 130 |

|     | 7.5.1   | Intel 82555 TX PHY                                  | 130 |

|     | 7.5.2   | 82558 and 82559 Embedded PHY Unit                   | 130 |

| Pro | grammin | g Recommendations                                   | 133 |

| 8.1 | Adapte  | er Initialization                                   |     |

|     | 8.1.1   |                                                     |     |

|     | 8.1.2   | PHY Detection and Initialization                    |     |

|     | 8.1.3   | NOS Specific Initialization                         | 134 |

| 8.2 | Transn  | nit Processing                                      | 134 |

| 8.3 |         | Reception                                           |     |

| 8.4 | Interru | pt Processing                                       |     |

|     |         |                                                     |     |

## Appendices

| Α | Wake-up Functionality                | 137 |

|---|--------------------------------------|-----|

| В | 82550 and 82551 Specific Information | 153 |

## Figures

8

|    |                                            | _  |

|----|--------------------------------------------|----|

| 1  | 82557 Network Interface Card Block Diagram |    |

| 2  | Command Register                           | 12 |

| 3  | Command Register                           | 13 |

| 4  | Cache Line Size                            | 14 |

| 5  | Base Address Register for Memory Mapping   | 15 |

| 6  | Base Address Register for I/O Mapping      | 15 |

| 7  | Expansion ROM Base Address Register        | 17 |

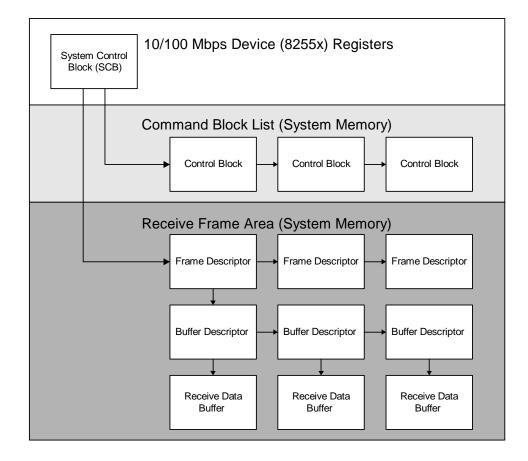

| 8  | 8255x Memory Architecture                  | 28 |

| 9  | SCB Status Word                            | 34 |

| 10 | SCB Command Word                           |    |

| 11 | Self-Test Results Format                   | 43 |

| 12 | EEPROM Control Register                    |    |

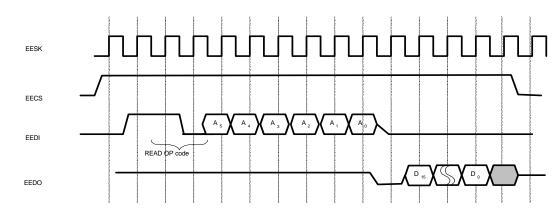

| 13 | EEPROM Read Timing Diagram                 | 48 |

| 14 | General Action Command Format              | 58 |

| 15 | NOP Command Format                         | 59 |

| 16 | Individual Address Setup Command Format    | 60 |

| 17 | Configure Command Format                   | 61 |

| 18 | Multicast Setup Command Format             | 80 |

| 19 | Transmit Command Format                    | 81 |

|    |                                            |    |

| 20 | Transmit Buffer Descriptor      |  |

|----|---------------------------------|--|

| 21 | Load Microcode Command Format   |  |

| 22 | Dump Command Format             |  |

|    | Diagnose Command Format         |  |

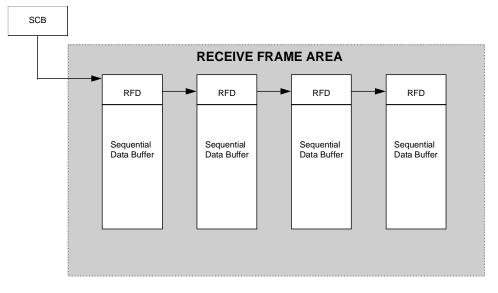

|    | Simplified Memory Structure     |  |

| 25 | Receive Frame Descriptor Format |  |

| 26 | Management Frame Structure      |  |

|    | Command Block Structure         |  |

## Tables

| 1  | PCI Configuration Space                          | .11  |

|----|--------------------------------------------------|------|

| 2  | Device and Revision ID                           | . 13 |

| 3  | Base Address Register Summary                    | .16  |

| 4  | Power Management Capabilities                    | . 18 |

| 5  | Power Management Control/Status Register         | . 20 |

| 6  | Power Consumption / Dissipation Reporting        | .21  |

| 7  | Generated PCI Commands                           |      |

| 8  | Reset Commands                                   |      |

| 9  | Device Addressing Formats                        | . 30 |

| 10 | Alignment Requirements for 8255x Data Structures | . 31 |

| 11 | Control / Status Register                        | . 32 |

| 12 | System Control Block                             | .34  |

| 13 | SCB Status Word Bits Descriptions                | . 35 |

| 14 | SCB Command Word Bits Descriptions               | . 37 |

| 15 | SCB General Pointer for the CU Command           | . 39 |

| 16 | Statistical Counters                             | . 40 |

| 17 | Port Register Location                           | . 42 |

| 18 | Port Selection Function                          |      |

| 19 | Dump Wake-up Data Structure                      | . 44 |

| 20 | EEPROM Control Register Locations                |      |

| 21 | EEPROM Control Register Bits Definitions         |      |

| 22 | EEPROM Opcode Summary (64-register EEPROM)       | . 46 |

| 23 | MDI Control Register Location                    |      |

| 24 | Management Data Pins                             | . 49 |

| 25 | MDI Control Register Bits                        | . 50 |

| 26 | Receive Byte Count Register Location             | .51  |

| 27 | Early Receive Interrupt Register Location        |      |

| 28 | Flow Control Registers Location                  |      |

| 29 | Flow Control Threshold Values                    | . 54 |

| 30 | Power Management Driver Register Location        |      |

| 31 | Power Management Driver Register                 |      |

| 32 | General Control Register Location                |      |

| 33 | General Control Register                         |      |

| 34 | General Status Register Location                 | . 56 |

| 35 | General Status Register                          | . 56 |

| 36 | Operation Codes                                  | .57  |

| 37 | 82557 Configuration Byte Map                     | . 62 |

| 38 | 82558 Configuration Byte Map                     |      |

| 39 | 82559 Configuration Byte Map                     | . 64 |

#### Contents

# intel®

| 40 | 82557 Dual-Port FIFO Settings                         | 65  |

|----|-------------------------------------------------------|-----|

| 41 | 82558 and 82559 Dual-Port FIFO Settings               | 66  |

| 42 | Extended Statistics Functionality                     |     |

| 43 | Pre-amble Length                                      | 73  |

| 44 | 82558 B-step Configuration Block ARP Frame IP Address | 74  |

| 45 | 82558 B-step ARP Frame IP Address Mapping             | 75  |

| 46 | Full Duplex Functionality                             | 77  |

| 47 | Dump Data Bytes (0-79)                                | 90  |

| 48 | Dump Data Dwords (20-148)                             | 93  |

| 49 | RFD Status Bit Descriptions                           |     |

| 50 | Actual Count in Header RFD                            |     |

| 51 | CU Control Commands: Actions at Acceptance Time       | 105 |

| 52 | CU Activities Performed at the End of Execution       |     |

| 53 | RU Control Commands: Actions at Acceptance Time       |     |

| 54 | Flow Control Frame Format                             |     |

| 55 | Flow Control Configuration Bits                       |     |

| 56 | MDI Register Set                                      |     |

| 57 | 82555 MDI Register Set                                |     |

| 58 | 24-bit OUI Identification Number                      |     |

| 59 | MDI Identification Registers 2 and 3: PHY ID Encoding |     |

| 60 | LED Switch Control                                    |     |

| 61 | Technology Ability Field Bit Assignments              |     |

| 62 | Technology Priority                                   |     |

| 63 | Fixed Wake-up Configuration Bits                      |     |

| 64 | 82559 Port Commands                                   | 148 |

| 65 | Dump Data Structure                                   | 149 |

| 66 | IPCB Structure                                        | 153 |

| 67 | IP Activation Bits (Byte 13)                          |     |

| 68 | IP Activation Bits (Byte 12)                          | 153 |

| 69 | IPCB Fields                                           |     |

| 70 | IPCB Structure Checksum Offload                       |     |

| 71 | IPCB Structure Large Send                             | 160 |

## **Revision History**

| Date         | Revision | Description      |

|--------------|----------|------------------|

| January 2003 | 1.0      | Initial release. |

|              |          |                  |

# intel® Introduction

This document is intended for use as a software technical reference manual for the Intel<sup>®</sup> 10/100 Mbps Fast Ethernet controller family, which includes the 82557, 82558, 82559, 82550, and 82551, as well as the 82562 Platform LAN Connect device. It also contains information for several PCI LAN adapters based on these devices: Intel<sup>®</sup> EtherExpress<sup>TM</sup> PRO/100+, Intel<sup>®</sup> EtherExpress<sup>TM</sup> PRO/100B, and Intel<sup>®</sup> EtherExpress<sup>TM</sup> PRO/100B, and Intel<sup>®</sup> EtherExpress<sup>TM</sup> PRO/10+.

## 1.1 Scope

This manual is intended to be used as a technical reference for software and test engineers developing device drivers or related software for adapters or systems using the Intel<sup>®</sup> 82557, 82558, 82559, 82550, or 82551 Fast Ethernet controllers or the Intel<sup>®</sup> 82562 Platform LAN Connect (PLC) device. It contains reference information about the controllers as well as other information that may be required by software developers (such as PHY information, EEPROM contents, PCI scanning, etc.). Since this document uses many examples and contains sample code fragments, it is assumed that the reader has a fundamental understanding of device driver programming and a working knowledge of both C programming language and x86 assembler programming language. Familiarity with at least one industry standard network operating system (NOS) device driver interface (for example, Network Driver Interface Specification [NDIS] or ODI) is also helpful.

The Intel<sup>®</sup> 10/100 Mbps Fast Ethernet Controller Family includes the following devices in successive order.

| Device | Notes                                                                                                   |

|--------|---------------------------------------------------------------------------------------------------------|

| 82557  | First generation Intel® 10/100 Mbps Fast Ethernet Controller (includes MAC unit only)                   |

| 82558  | Second generation Intel® 10/100 Mbps Fast Ethernet Controller (includes MAC and an integrated PHY unit) |

| 82559  | Third generation Intel® 10/100 Mbps Fast Ethernet Controller (includes both a MAC and PHY unit)         |

| 82550  | Intel® 10/100 Mbps Fast Ethernet Controller (includes both MAC and PHY)                                 |

| 82551  | Intel® 10/100 Mbps Fast Ethernet Controller (includes both MAC and PHY)                                 |

In general, the Intel family of Fast Ethernet controllers are similar. All family members share the same core hardware and software interface. The later generation components have a higher integration and include support for miscellaneous features (for example, manageability). Since the different generations of Fast Ethernet controllers are highly similar, this manual documents the functionality of all devices and details the differences between the devices. It is intended to be used as a tool to maintain and develop software for all devices in the Intel family of Fast Ethernet controllers.

## 1.2 Document Conventions

#### 1.2.1 Device References

This document encompasses information for all members of the Intel Fast Ethernet controllers: 82551, 82550, 82559, 82558, 82557 and the 82562.

The document convention, "8255x," will be used to refer to all devices. In addition, there are specific references to the 82557 throughout this manual that pertains to all 8255x devices. Device-specific differences and exceptions will be documented.

#### 1.2.2 Numbering

Decimal, binary, and hexadecimal numbers are used through the manual. They will be designated as follows:

- Decimal numbers: Decimal numbers will not be followed by a suffix.

- Binary numbers: Binary numbers (base 2) will be followed by a "b" (for example, 01b).

- **Hexadecimal numbers:** Hexadecimal numbers (base 16) will be followed with the suffix "h" (for example, 1Ch). Hexadecimal numbers may also be noted with a prefix of "0x" (for example, 0x1c).

#### 1.2.3 Signal Name Representation

Signals that are active in a low logic state when asserted are followed by the pound sign (#). For example, FRAME# is asserted low by the master during a transaction. It is asserted low at the start and duration of a transaction and de-asserted during the final data phase.

Signals that are not followed by a pound sign are active in a high logic state when asserted. For example, the IDSEL signal is asserted high when the 82559 during PCI read and write transactions.

## 1.2.4 Memory Alignment Terminology

The 8255x data structures have special memory alignment requirements. This implies that the starting physical address of a data structure must be aligned as specified. The following terms are used for this purpose:

- **Byte alignment:** Byte alignment implies that the physical addresses can be odd or even. Examples: 0FECBD9A1h or 02345ADC6h

- Word alignment: Word alignment implies that physical addresses must be aligned on even boundaries. In other words, the last nibble of the address may only end in 0h, 2h, 4h, 6h, 8h, Ah, Ch, or Eh.

Example: 0FECBD9A2h

• **Dword alignment:** Dword alignment implies that the physical addresses may only be aligned on 4-byte boundaries. In other words, the last nibble of the address may only end in 0h, 4h, 8h, or Ch.

Example: 0FECBD9A8h

• **Paragraph alignment:** Paragraph alignment implies that the physical addresses may only be aligned on 16-byte boundaries. In other words, the last nibble must be a 0. Example: 02345ADC0h

Introduction

# intel®

Adapters based on an Intel<sup>®</sup> 8255x device support the ANSI/IEEE 802.3u standard for 100BASE-TX (100 Mbps operation) and 10BASE-T (10 Mbps operation).

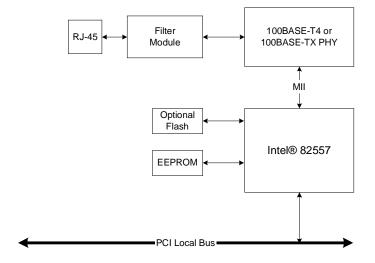

## 2.1 Adapter Block Diagram

The main components of Intel Fast Ethernet adapters are:

- A Fast Ethernet Media Access Controller (MAC), such as the 8255x, is the core component. The MAC supports the Fast Ethernet ANSI/IEEE 802.3u standard.

- A Physical Layer (PHY) interface device is also required. The 82558, 82559, 82550, and 82551 components have an integrated PHY that supports 100BASE-TX and 10BASE-T. Adapters based on the 82557 must include an appropriate PHY component for their design.

- A serial EEPROM is required to hold the adapter's individual Ethernet node address and other configuration information including fixed PCI configuration parameters.

The adapters are based on 100BASE-TX specifications. 100BASE-TX is a specific scheme designed for use over 2 pairs of Category 5 unshielded twisted-pair cable. 100BASE-TX defines a signaling scheme for 100 Mbps and provides compatibility with the existing 10 Mbps IEEE 802.3 10BASE-T signaling standard. Since only 2-wire pairs are used, TX technology allows full duplex operation at 100 Mbps. The Intel 82555 is one possible TX solution.

The block diagram below illustrates an Intel<sup>®</sup> PRO/100B adapter configuration based on the 82557 MAC with a TX or T4 PHY.

#### Figure 1. 82557 Network Interface Card Block Diagram

## 2.2 Intel Fast Ethernet MAC Features

#### 2.2.1 82557 Features

- Glueless 32-bit, zero wait state PCI bus master interface compliant with PCI Specification, Revision 2.1.

- 10 and 100 Mbps support in compliance with IEEE 802.3 10BASE-T and 802.3u 100BASE-TX.

- Fast back-to-back transmit interframe spacing (IFS) of 960 ns in 100 Mbps networks and 9.6 µs in 10 Mbps networks.

- On-chip Control/Status Register (CSR) incorporating the System Control Block (SCB).

- Simple and flexible packet support with Dynamic transmit chaining.

- Packed Transmit Buffer Descriptors (TBDs).

- Early transmit complete indication.

- Simple receive packet support allows early receive interrupt support for concurrent processing (in simplified mode).

- IEEE Media Independent Interface (MII) compliant PHY interface other MII compliant PHYs.

- Full and half duplex transmit and receive capability.

- Separate on-chip receive and transmit FIFOs.

- On-chip network management counters.

- EEPROM support.

- Optional Flash ROM support (256 Kbytes or 1 Mbyte).

#### 2.2.2 82558 Features

For the most part, the 82558 is a superset of the 82557. In addition to incorporating the features of the 82557, it also includes the following:

- Backward compatible to 82557 software.

- Integrated 100BASE-TX PHY.

- IEEE 802.3u auto-negotiation support in 10BASE-T, 100BASE-TX, full duplex and full duplex flow control configurations.

- Auto-polarity correction for 10BASE-T.

- Optimized PCI interface with support for the memory write and invalidate PCI command.

- Automatic read of EEPROM (programmable ID).

- IEEE 802.3x flow control capable.

- PHY based flow control support when the internal 100BASE-TX PHY is used.

- Advanced Configuration and Power Interface (ACPI) Specification and PCI Power Management Specification compliant.

- Remote power up support (for Magic Packet\*).

• Optional Flash support up to 64 Kbytes. (The 82557 is capable of larger Flash size support.)

#### 2.2.3 82559, 82550, 82551, and 82562 Features

The 82559, 82550, and 82551 devices are supersets of the 82557 and 82558. However, the 82559 does not support PHY based flow control as the 82558 did. The new 82559 features are:

- Backward compatible to the 82557 and 82558 software.

- Low power 3.3 V device:

- Clockrun protocol support.

- System Management Bus (SMB) support.

- Wired for Management support (WfM).

- Expanded Wake on LAN capabilities.

- 128 Kbytes Flash size support. (The 82558 only supported a 64 Kbyte Flash.)

- Thin ball grid array (BGA) 15 x 15 mm package.

#### 2.2.3.1 82559ER Features

The 82559ER is a member of the 82559 Fast Ethernet controllers. It is a subset of the 82559. However, the 82559ER does not support:

- SMB.

- Wake on Magic Packet\*.

## 2.3 Working with the Physical Layer

The 82557 contains an IEEE MII compliant interface to a MII compliant PHY, allowing connections to 10/100 Mbps networks. Software communicates to a MII compliant device through the 82557 by using the its Management Data Interface (MDI) port.

The 82558, 82559, 82550 and 82551 contain an embedded PHY module. Although the PHY is internal for these devices, software still communicates to the PHY unit through the MDI port.

For 10/100 Mbps connections, the 82557 can be used in conjunction with the Intel<sup>®</sup> 82555. For 10 Mbps only connections, the 82557 can be interfaced to the Intel<sup>®</sup> 82503 serial interface, while maintaining software compatibility to 100 Mbps solutions. The 82558 and later devices do not have a 10 Mbps only interface as the 82557. However, it is possible to interface these devices with a 10 Mbps only MII device.

Adapter and Controller Overview

# intel®

The 82557 has no power management support. The 82558 added support for the Advanced Configuration and Power Interface (ACPI) Specification and limited support for Wake on LAN (WOL). The 82558 B-step upgraded and expanded the WOL capability, while the 82559 expanded and simplified the WOL functionality even more.

## 3.1 Low Power Mode Requirements

The 82558, 82559, 82550, and 82551 adhere to the emerging power management standards as defined in:

- PCI Bus Power Management Interface Specification, Revision 1.0.

- Advanced Configuration and Power Interface Specification (ACPI), Rev 1.0; December 22, 1996.

- Device Class Power Management Reference Specification Network Device Class, Revision 1.0.

These three specifications define how a PCI network device can be controlled in an OS Directed Power Management (OSPM) environment. These devices all adhere to these specifications. Additionally, they support bus isolation within the chip and Wake on LAN (WOL) capabilities.

## 3.2 Device Power States

Currently, operating systems only support the D0 and D3 power states. However, starting with the 82558, the Intel Fast Ethernet controller family supports all four power states as defined in the PCI Power Management Specification. These power states are named D0, D1, D2 and D3. D0 is the maximum powered state, and D3, the minimum powered state.

## 3.3 Power Management Registers

The 82558, 82559, 82550, and 82551 support power management registers:

- Power Management Capability Pointer (Cap\_Ptr)

- Power Management Capabilities (PMC)

- Power Management Control/Status Register (PMCSR)

- Power Management Driver Register (PMDR)

The first three registers are located in PCI configuration space and are defined in the PCI Power Management Specification. It is part of the device CSR, which is mapped into system memory and I/O space.

## 3.4 Link Operation

In the D0 state, the device maintains an active link. The 82558 B-step (refer to Table 2, "Device and Revision ID" on page 13) and later devices also maintain an active link in the D3 state if PME is enabled and the device has power. This implies:

- **10BASE-T Mode:** The device expects a normal clock input on the X1 and X2 pins. It expects to receive normal reception on the Receive Differential Positive and Receive Differential Negative signals (RDP/RDN pair). The device will not transmit on the Transmit Differential Positive and Transmit Differential Negative signals (TDP/TDN pair).

- **100BASE-TX Mode:** The device expects a normal clock input on the X1 and X2 pins and to receive normal reception on the RDP/RDN pair. It transmits a continuous idle stream on the TDP/TDN pair, as required by the 100BASE-TX standard. The 82558 does not transmit frames on the link.

- Auto-Negotiation: If the link fails while the device is in the D1 state, it performs the normal auto-negotiation protocol in order to re-establish the link. For the 82558 B-step, if the link fails in the D3 state and PME is enabled and the device has power, the device will attempt to use the normal auto-negotiation protocol in order to re-establish the link. If the link fails on the 82559 in the D3 state and PME is enabled and the device has power, the 82559 will go into a deep power down state, rather than trying to re-establish the link with the auto-negotiation protocol.

During the D3 power state, the 82558 A-step does not maintain an active link. The 82558 B-step and later generation devices do not maintain a link in D3 if PME is disabled or if the device does not have power.

# intel® PCI Interface

#### **PCI Configuration Space** 4.1

One of the most important functions for enabling superior configurability and ease of use is the ability to relocate PCI devices in the address spaces. By default PCI devices support "Plug and Play." When the system is powered on, device independent software (usually the system BIOS) determines present devices, builds an address map, and assigns non-conflicting resources to those devices. The device independent software accomplishes this configuration task by writing to the PCI configuration space of each individual PCI device.

The 8255x supports 16 Dwords of Type 0 Configuration Space Header, as defined in the PCI Specification, Revision 2.1. The 82259 and 82558 also support a small section in the device specific configuration space. The configuration space is depicted below. The registers that are not identical between the devices are shaded.

| Byte Offset<br>(hexadecimal) | Byte 3                                                               | Byte 2                                    | Byte 1              | Byte 0          |  |  |

|------------------------------|----------------------------------------------------------------------|-------------------------------------------|---------------------|-----------------|--|--|

| 0                            | Device ID                                                            | ·                                         | Vendor ID           |                 |  |  |

| 4                            | Status Register                                                      |                                           | Command Register    |                 |  |  |

| 8                            | Class Code (200000h)                                                 |                                           |                     | Revision ID     |  |  |

| С                            | BIST                                                                 | Header Type                               | Latency Timer       | Cache Line Size |  |  |

| 10                           | CSR Memory Mapped                                                    | Base Address Register                     |                     |                 |  |  |

| 14                           | CSR I/O Mapped Base                                                  | e Address Register                        |                     |                 |  |  |

| 18                           | Flash Memory Mapped                                                  | Flash Memory Mapped Base Address Register |                     |                 |  |  |

| 1C                           | Description                                                          |                                           |                     |                 |  |  |

| 20                           |                                                                      |                                           |                     |                 |  |  |

| 24                           | Reserved                                                             |                                           |                     |                 |  |  |

| 28                           |                                                                      |                                           |                     |                 |  |  |

| 2C                           | Subsystem ID                                                         |                                           | Subsystem Vendor ID |                 |  |  |

| 30                           | Expansion ROM Base                                                   | Address Register                          |                     |                 |  |  |

| 34                           | Reserved                                                             |                                           |                     | Cap_Ptr         |  |  |

| 38                           | Reserved                                                             |                                           |                     |                 |  |  |

| 3C                           | Max_Latency (FFh) Min_Grant (FFh) Interrupt Pin (01h) Interrupt Line |                                           |                     |                 |  |  |

| DC                           | Power Management Capabilities Next Item Pointer Capability ID        |                                           |                     | Capability ID   |  |  |

| E0                           | Reserved Data Power Management CSR                                   |                                           |                     | SR              |  |  |

#### Table 1. PCI Configuration Space

#### 4.1.1 Vendor ID (Offset 0)

This field identifies the device manufacturer. For the 82557 B-step this field equals 8086h. For the 82557 C-Step, 82558, and 82559, this field is automatically loaded from the EEPROM at power on or upon the assertion of PCI reset. If the EEPROM is not present or invalid, this value defaults to 8086h.

#### 4.1.2 Device ID (Offset 2)

This field uniquely identifies the device. For the 82557 B-step this field is 1229h. For the 82557 C-Step, 82558, and 82559, this field is automatically loaded from the EEPROM at power on or upon the assertion of PCI reset. If the EEPROM is not present or invalid, this value defaults to 1229h for the 82558 and 82559. The 82559ER does not load the Device ID from the EEPROM and will always equal 1209h.

#### 4.1.3 Command Register (Offset 4)

The Command Register provides control over the device's ability to generate and respond to CPU cycles. Its layout is shown below. The shaded bits are not used and are hard-wired to 0.

#### Figure 2. Command Register

| 15 1     | 0 | 9            | 0 |

|----------|---|--------------|---|

| Reserved |   | Command Bits |   |

| Bits  | Initial<br>Value | Description                                                                                                                                                         |  |  |  |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15:10 | 0                | Reserved.                                                                                                                                                           |  |  |  |

| 9     | 0                | Fast back-to-back enable.                                                                                                                                           |  |  |  |

| 8     | х                | SERR# enable.                                                                                                                                                       |  |  |  |

| 7     | 0                | Vait cycle enable.                                                                                                                                                  |  |  |  |

| 6     | х                | Parity error response                                                                                                                                               |  |  |  |

| 5     | 0                | Palette snoop enable.                                                                                                                                               |  |  |  |

| 4     | х                | Memory write and invalidate (MWI) enable.<br><b>NOTE:</b> More information regarding the MWI command is located in Section 4.2.1,<br>"Memory Write and Invalidate". |  |  |  |

| 3     | 0                | Special cycle monitoring.                                                                                                                                           |  |  |  |

| 2     | х                | Mastering enable.                                                                                                                                                   |  |  |  |

| 1     | х                | Memory access enable.                                                                                                                                               |  |  |  |

| 0     | х                | I/O access enable.                                                                                                                                                  |  |  |  |

## 4.1.4 Status Register (Offset 6)

The Status Register is used to record status information for PCI bus related events. Its layout is shown below. The shaded bits are not used and are hard-wired to 0.

#### Figure 3. Command Register

| 15          | 4 | 3        | 0 |

|-------------|---|----------|---|

| Status Bits |   | Reserved |   |

| Bits | Initial<br>Value                          | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15   | х                                         | Detected parity error.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 14   | х                                         | Signaled system error.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 13   | х                                         | Received master abort.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 12   | х                                         | Received target abort.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 11   | 0                                         | Signaled target abort.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 10:9 | 01                                        | DEVSEL timing (indicates minimum timing).                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 8    | х                                         | Data parity reported.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 7    | 1                                         | Fast back-to-back capable.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 6    | 0                                         | UDF supported.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 5    | 0                                         | 66 MHz capable.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 4    | 1 (82559<br>and<br>82558)<br>0<br>(82557) | Capabilities list. This bit indicates whether the device implements a list of new capabilities such as PCI Power Management. If it is set, the Cap_Ptr register in the PCI Configuration Space points to the location of the first item in the Capabilities List.<br><b>NOTE:</b> This bit is set to 1 for the 82559 and 82558 if it is not disabled by the EEPROM. It is always equal to 0 for the 82557. |  |  |  |

| 3:0  | 0                                         | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

## 4.1.5 Revision (Offset 8)

This register specifies a device specific revision identifier. For the 82557 C-Step, 82558, and 82559, this field may be automatically loaded from the EEPROM at power on or upon the assertion of a PCI reset. The default revision register values for the various devices are:

#### Table 2.Device and Revision ID

| Device       | Revision ID | PCI Revision<br>Supported | Intel Driver<br>Supported |

|--------------|-------------|---------------------------|---------------------------|

| 82557 A-Step | 01h         | 2.0                       | Yes                       |

| 82557 B-Step | 02h         | 2.0                       | Yes                       |

| 82557 C-Step | 03h         | 2.1                       | No                        |

| 82558 A-Step | 04h         | 2.1                       | Yes                       |

| 82558 B-Step | 05h         | 2.1                       | Yes                       |

| 82559 A-Step | 06h         | 2.1                       | No                        |

| 82559 B-Step | 07h         | 2.1                       | No                        |

| 82559 C-Step | 08h         | 2.2                       | Yes                       |

#### Table 2. Device and Revision ID

| Device         | Revision ID   | PCI Revision<br>Supported | Intel Driver<br>Supported |

|----------------|---------------|---------------------------|---------------------------|

| 82559ER A-Step | 09h           | 2.2                       | Yes                       |

| 82550          | 0Ch, 0Dh, 0Eh | 2.2                       | Yes                       |

| 82551          | 0Fh, 10h      | 2.2                       | Yes                       |

#### 4.1.6 Class Code (Offset 9)

The class code, 020000h, identifies the device as an Ethernet adapter.

## 4.1.7 Cache Line Size (Offset C)

This register specifies the system cache line size in units of 32-bit words and can be read or written to. The system BIOS or OS should initialize this register at power on or after a PCI reset.

The 82557 does not support Memory Write and Invalidate (MWI) and therefore returns 0 when this register is read. The 82258 and 82559 support the MW I command and must support this register. The 82558 and 82559 can only support cache line sizes of 8 and 16 Dwords. Any value other than 8 or 16 written to the register is ignored, and the device does not use the MWI command. If a value other than 8 or 16 is written into the Cache Line Size (CLS) register, the device returns all zeroes when the CLS register is read.

#### Figure 4. Cache Line Size

| 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---|---|---|----|----|---|---|---|

| 0 | 0 | 0 | RW | RW | 0 | 0 | 0 |

Bit 3 is set to 1 only if the value 00001000b (8) is written to this register. Bit 4 is set to 1 only if the value 00010000b (16) is written to this register. All other bits are read only and will return 0 on read.

#### 4.1.8 Latency Timer (Offset D)

This register specifies, in units of PCI bus clocks, the minimum time that a bus master can retain ownership of the bus. This value is set by the PCI bus arbitrator based on the values in the maximum latency (Max\_Lat) and Maximum Grant (Max\_Gnt) registers.

#### 4.1.9 Header Type (Offset E)

This byte field identifies the layout of the second part of the predefined configuration space header and if the device is a multi-function component. The 82557 and 82558 are both single function devices and have this register hard-coded to 00h. For the 82559, the value of this register is determined by a bit in the EEPROM. This register should read 00h for a standard Ethernet adapter, 00h.

## 4.1.10 Built in Self Test (Offset F)

This optional register is used for control and status of Built in Self Test (BIST). This register is hard-wired to 0 indicating that the devices do not support BIST.

Three base address registers are supported by the 8255x:

- CSR Memory Mapped Base Address Register (BAR 0 at offset 10)

- CSR I/O Mapped Base Address Register (BAR 1 at offset 14)

- Flash Memory Mapped Base Address Register (BAR 2 at offset 18)

Two request memory mapped resources, and the third, I/O mapping. Each register is 32 bits wide. The least significant bit in each base address register determines whether it represents an I/O or memory space. The figures below illustrate layouts for I/O and memory mapped base address registers. After determining which resources will be used, the power-up software maps the I/O and memory controllers into available locations and continues with the power up. To perform the mapping in a device independent manner, the base registers are placed in the predefined header portion of configuration space. Device drivers access this configuration space to determine the mapping of a particular device.

#### Figure 5. Base Address Register for Memory Mapping

| 32           | 4 | 3                  | 0 |

|--------------|---|--------------------|---|

| Base Address |   | Configuration Bits |   |

| Bits | Initial<br>Value | Description                                                                                                                                                                                                  |  |  |  |  |

|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 31:4 | х                | e Address.                                                                                                                                                                                                   |  |  |  |  |

| 3    | х                | etchable.                                                                                                                                                                                                    |  |  |  |  |

| 2:1  | x                | <ul> <li>00 = Locate address anywhere in 32-bit address space.</li> <li>01 = Locate address below 1 MByte.</li> <li>10 = Locate address anywhere in 64-bit address space.</li> <li>11 = Reserved.</li> </ul> |  |  |  |  |

| 0    | 0                | lemory space indicator.                                                                                                                                                                                      |  |  |  |  |

NOTE: Bit 0 in all base registers is read-only and used to determine whether the register maps into memory or I/O space. Base registers mapping to memory space must return a 0 in bit 0, and base registers mapping to I/O space, a 1.

#### Figure 6. Base Address Register for I/O Mapping

| 32           | 2 | 1        | 0 |

|--------------|---|----------|---|

| Base Address |   | Reserved | 1 |

**NOTE:** Base registers that map into I/O space are always 32 bits with bit 0 hard wired to a 1, bit 1 is reserved and must return 0 on reads, and the other bits are used to map the device into I/O space.

The number of upper bits that a device actually implements depends on how much of the address space the device responds to. A device that wants a 1 Mbyte memory address space would set the most significant 12 bits of the base address register to be configurable, setting the other bits to 0.

The 8255x requires one BAR for I/O mapping and one BAR for memory mapping of these registers anywhere within the 32-bit memory address space. The driver determines which BAR (I/ O or Memory) is used to access the Control/Status Registers. However, both are always requested by the device.

One BAR is also required to map the accesses to an optional Flash memory. The 82557 implements this register regardless of the presence or absence of a Flash chip on the adapter. The 82558 and 82559 only implement this register if a bit is set in the EEPROM. The size of the space requested by this register is 1Mbyte, and it is always mapped anywhere in the 32-bit memory address space.

*Note:* Although the 82558 only supports up to 64 Kbytes of Flash memory and the 82559 only supports 128 Kbytes of Flash memory, 1 Mbyte of address space is still requested. Software should not access Flash addresses above 64 Kbytes for the 82558 or 128 Kbytes for the 82559 because Flash accesses above the limits are aliased to lower addresses. Table 3 describes the implementation of the base address registers.

| Register<br>Location | Description                                                                                                                                                                                                                                                      |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10h                  | Memory space for the device Control/Status Registers. The size of this space is 4 Kbytes and it is mapped anywhere in the 32-bit memory address space. It is marked as pre-fetchable. Software should not assume that this memory will be granted below 1 Mbyte. |

| 14h                  | I/O space for the device Control/Status Registers. The size of this space is 32 bytes.                                                                                                                                                                           |

| 18h                  | Memory space for FLASH buffer accesses. The size of this space is 1Mbyte. It is mapped anywhere in the 32-bit address space and is not pre-fetchable.                                                                                                            |

| 1Ch - 27h            | Reserved.                                                                                                                                                                                                                                                        |

#### Table 3. Base Address Register Summary

#### 4.1.11 Subsystem ID (Offset 2C)

This register uniquely identifies the add-in adapter or subsystem where the PCI device resides. It provides a mechanism to distinguish different adapters that use the same PCI controller. For the 82557 B-step this field equals 0000h. For the 82557 C-Step and later devices, this field is loaded from the EEPROM at power on or upon the assertion of PCI reset. If the EEPROM is not present or invalid, this value defaults to 0000h.

#### 4.1.12 Subsystem Vendor ID (Offset 2E)

This register uniquely identifies the add-in adapter or subsystem where the PCI device resides. It provides a mechanism to distinguish the vendor of a adapter from the vendor of the PCI controller used on the adapter. For the 82557 B-step this field is 0000h. For the 82557 C-Step and later devices, this field is automatically loaded from the EEPROM at power on or upon the assertion of PCI reset. If the EEPROM is not present or invalid, this value defaults to 0000h.

## 4.1.13 Expansion ROM Base Address Register (Offset 30)

The 8255x provides an interface to a local Flash device (or EEPROM) which may be used as an expansion ROM. A 32-bit Expansion ROM Base Address Register at offset 30h in the PCI Configuration Space is defined to handle the address and size information for boot-time access to

the Flash. The 82557 implements this register regardless of the presence or absence of a Flash component on the adapter. For the 82558 and later Fast Ethernet controllers, this register is only implemented if a bit is set in the EEPROM.

The register functions exactly like a 32-bit base address register except that the encoding (and usage) of the bottom bits is different. The upper 21 bits correspond to the upper 21 bits of the expansion ROM base address. The 8255x only allow an expansion ROM to be mapped on a 1 Mbyte boundary. Therefore, only the most significant 12 bits are configurable to indicate the 1 Mbyte size requirement (as with the Flash Memory Mapped BAR, the 82558 and 82559 request a 1 Mbyte mapping even though the maximum Flash size allowed with those devices is 65 Kbytes). The format of the register is shown in the figure below.

#### Figure 7. Expansion ROM Base Address Register

| 32   |         |  | 20 | 19 1                         | 0  |  |

|------|---------|--|----|------------------------------|----|--|

| Read | / Write |  |    | Reserved (all bits set to 0) | En |  |

Bit 0 in the register is used to control whether or not the device accepts accesses to its expansion ROM. When this bit is reset, the devices expansion ROM address space is disabled. This bit is programmed at initialization time by the system BIOS. The Memory Space bit in the Command register has precedence over the Expansion ROM Base Address Enable bit. A device responds to accesses to its expansion ROM only if both the Memory Space bit and the Expansion ROM Base Address Enable bit are set to 1 (it is reset to 0 upon PCI reset).

#### 4.1.14 The Capabilities Pointer (Offset 34)

This an 8-bit field that provides an offset in the device PCI Configuration Space for the location of the first item in the Capabilities Linked List. The Power Management Interface documentation specifies this linked list to provide access to all appropriate device information in the implementation of the ACPI.

For the 82257, this register is hard-wired to 0 since it does not support power management.

For the 82558 this register is set to DCh if power management is enabled in the EEPROM. If power management is disabled, then this register is set to 0.

For the 82559 and later Intel Fast Ethernet controllers, this register is hard-wired to DCh.

## 4.1.15 Interrupt Line (Offset 3C)

The Interrupt Line register is an 8-bit register used to communicate interrupt line routing information. This register is configurable by the system BIOS or OS. POST software writes the routing information into this register as it initializes and configures the system. The value in this register specifies which system interrupt controller input the device interrupt pin is connected to. Device drivers and operating systems use this information to determine priority and vector information.

## 4.1.16 Interrupt Pin (Offset 3D)

The Interrupt Pin register specifies which interrupt pin the device (or device function) uses. This register is always set to a 1, indicating that INTA# is used.

## 4.1.17 Max\_Lat / Min\_Gnt (Offset 3E)

These registers specify the device settings for Latency Timer values. For both registers, the value specifies a period of time in units of <sup>1</sup>/<sub>4</sub> microsecond. Min\_Gnt is used to specify the burst length period the device needs assuming a clock rate of 33 MHz. Max\_Lat is used to specify how often the device needs to gain access to the PCI bus. The values of these registers are 8h (2  $\mu$ S) for Min\_Gnt and 18h (6  $\mu$ S) for Max\_Lat.

#### 4.1.18 Power Management PCI Configuration Registers

#### 4.1.18.1 Capability Identifier (Offset DC)

The Capability Identifier signals this item in the capability linked list as the PCI Power Management registers. The PCI Power Management registers have been assigned the ID of 01h. Since power management is not implemented in the 82557, this register is hard-coded to 0 for that device. For the 82558 and later devices, this read only register returns 01h.

#### 4.1.18.2 Next Item Pointer (Offset DD)

The Next Item Pointer register describes the location of the next item in the capability list. Since power management is the last item in the list, this register is set to 0.

#### 4.1.18.3 Power Management Capabilities (Offset DE)

The Power Management Capabilities (PMC) register is a 16-bit read-only register, which provides information on the capabilities of the device related to power management. Since power management is not implemented in the 82557, this register is hard-coded to 0 for that device. For the 82558 and later devices, this register returns values according to the chart below.

| Bit   | Default Value                                         | R / W | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31.27 | 82558A: 00011<br>82558B, 82559:<br>no auxiliary power | RO    | <b>PME_Support.</b> This five bit field indicates the power states in which the device may assert PME#. A value of 0b for any bit indicates that the function is not capable of asserting the PME# signal while in that power state.                                                                                                                                                                                            |

|       | - 01111<br>with auxiliary<br>power - 11111            |       | The 82558 A-step supports wake-up from D0 and D1. The 82558<br>B-step and 82559 support wake-up from D0, D1, D2 and D3 <sub>hot</sub> if no<br>auxiliary power is present and from all power states if auxiliary<br>power exists.                                                                                                                                                                                               |

| 26    |                                                       | RO    | <b>D2_Support.</b> If this bit is set, this function supports the D2 Power Management State. All devices must support the D0 and D3 states. The 82559 and later devices support the D2 Power Management State.                                                                                                                                                                                                                  |

| 25    | 1                                                     | RO    | <b>D1_Support.</b> If this bit is set, this function supports the D1 Power Management State. The 82558 and later devices supports the D1 Power Management State.                                                                                                                                                                                                                                                                |

| 24    | 82558A: 1<br>82558B: 0<br>82559: 0                    | RO    | <b>FullClk.</b> If this bit is set, this function requires a full speed clock at all times when it is in the D0 state in order to perform its function. If this bit is cleared, the function only requires a full speed PCI clock while actually transferring data so dynamic clock control may be used. The 82558 A-step requires a full speed clock at all times when it is in the D0 state in order to perform its function. |

#### Table 4. Power Management Capabilities

| Bit   | Default Value                                                                           | R / W | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|-----------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23    | 0                                                                                       | RO    | Reserved. This field is not used by the 8255x.                                                                                                                                                                                                                                                                                                                                                           |

| 22    | 82558: 0<br>82559:<br>no auxiliary power<br>- 0<br>with auxiliary<br>power - 1          | RO    | <b>AUX_Current.</b> If the device is connected to an auxiliary power supply, the 82559 reports a "1" to indicate that it consume less than 250 mA from the 3.3 Vaux pin while in the D3 <sub>cold</sub> state. This bit is a reflection of bit 31.                                                                                                                                                       |

| 21    | 1                                                                                       | RO    | <b>DSI.</b> The Device Specific Initialization bit indicates whether special initialization of this function is required (beyond the standard PCI configuration header) before the generic class device driver is able to use it. Device specific initialization is required for the 82558 and 82559 after a D3 to D0 transition.                                                                        |

| 20    | 82558A: 0<br>82558B, 82559:<br>no auxiliary power<br>- 0<br>with auxiliary<br>power - 1 | RO    | Auxiliary Power Source<br>This bit is only meaningful if PMCSR bit 31 ( $D3_{cold}$ supporting<br>PME) equals 1. When this bit also equals 1, it indicates that support<br>for PME# in $D3_{cold}$ requires an auxiliary power supply. The 82558<br>B-step and 82559 require auxiliary power for wake up from the<br>$D3_{cold}$ state. Therefore this bit is set to 1 if auxiliary power is<br>present. |

| 19    | 0                                                                                       | RO    | <b>PME Clock.</b> When this bit is 1, it indicates that the PME# generation logic requires its host PCI bus to maintain a free-running PCI clock. When this bit is 0, it indicates that no host bus clock is required for the function to generate PME#. The 82558 and later generation devices do not require a clock to generate PME# and return 0.                                                    |

| 81:16 | 001                                                                                     | RO    | <b>Version.</b> This field specifies to software how to interpret the PMC and PMCSR registers. A value of 001b indicates that the device complies with the Revision 1.0 of the PCI Power Management Interface Specification.                                                                                                                                                                             |

#### Table 4. Power Management Capabilities

#### 4.1.18.4 Power Management Control/Status (Offset E0)

The Power Management Control/Status Register (PMCSR) is used to determine and change the current power state of the device. It also allows for the control of the power management interrupts in a standard way. Since power management is not implemented in the 82557, this register is hard-coded to 0 for that device. For the 82558 and later devices this register acts according to the chart below.

| Bit   | Value at Reset                                                                           | R / W         | Description                                                                                                                                                                                                                                                                |