# RISCore32300™ Family System Controller Chip

#### IDT79RC32134

### RISController

#### **Features**

- RC32300-family System Controller

- Direct connection between RC32364 and RC32134

- Up to 75 MHz operation

- Drives latched address bus to memory and peripherals

- Direct control of optional external data buffers

- Programmable system watch-dog timers

- Big or Little endian support

#### Interrupt Control

- Provides services for internal and external sources

- Allows status of each interrupt to be read and masked

- Three general purpose 32-bit timer/counters

- Programmable IO (PIO)

- Input/Output/Interrupt source

- Individually programmable

- ◆ SDRAM/EDODRAM Controller (32-bit memory only)

- 4 banks, non-interleaved, 256 MB total

- Automatic refresh generation

#### UART Interface

- Two 16550 Compatible UARTs

- Baud rate support up to 1.5M

- ◆ 8/16/32-bit boot PROM support

- Boundary Scan JTAG Interface (IEEE Std. 1149.1 compatible)

- Memory & Peripheral Controller

- 6 banks, up to 8MB per bank

- 8/16/ or 32-bit interface per bank

- Supports Flash ROM, SRAM, dual-port memory, and peripheral devices

- Intel or Motorola style IO supports external wait-state generation

#### 4 DMA Channels

- 4 general purpose DMA, each with Endianness swappers and byte lane data alignment

- Any channel can be used for PCI

- Supports memory-to-memory, memory-to-I/O,memory-to-PCI, PCI-to-PCI, I/O-to-I/O transfers, and I/O support of scatter/gather

- Supports chaining via linked lists of records

- Supports unaligned transfers

- Supports burst transfers

- Programmable burst size

#### PCI Bridge

- 32-bit PCI, up to 33 MHz

- Revision 2.1 compliant

- Target and master

- Host or satellite

- Three slot PCI arbiter, on-chip

- Serial EEPROM support, for loading configuration registers

- 3.3V core operation

- 3.3V I/O operation with 5V tolerant I/O

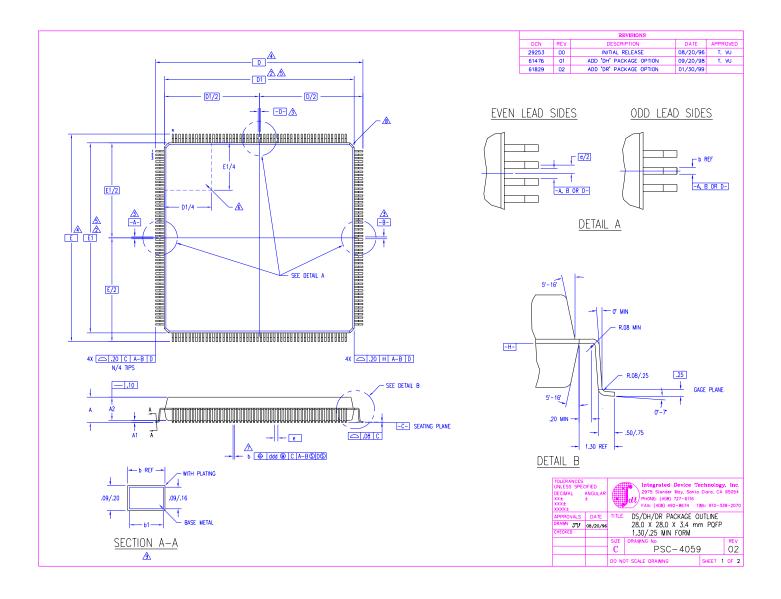

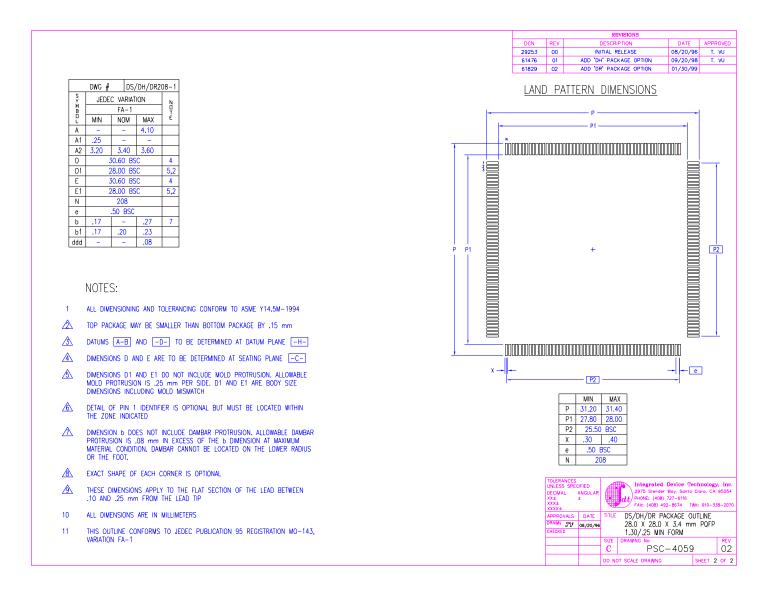

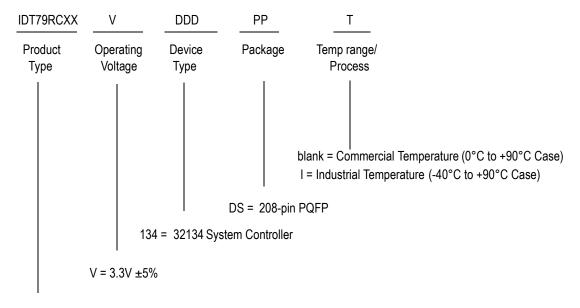

- 208 pin PQFP package

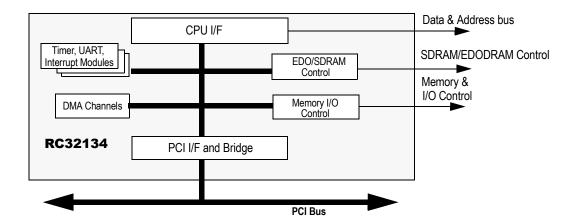

### **Block Diagram**

© 2000 Integrated Device Technology, Inc.

The IDT logo is a registered trademark. RC64145, RC64474, RC64475, RC32134, RC4600, RC4600, RC4650, RC4700, RC3041, RC3051, RC3052, RC3081, RISController, and RISCore are trademarks of Integrated Device Technology, Inc.

### **Description**

The IDT79RC32134 is a high performance system controller chip that supports IDT's RISCore32300 CPU family. The RC32134 offers a direct connection to IDT's RC32364 32-bit embedded microprocessor. The RC32134 provides the system logic for boot memory, main memory, I/O, and PCI. It also includes on-chip peripherals such as DMA channels, reset circuitry, interrupts, timers, and UARTs. Together, the RC32364 CPU and the RC32134 system controller form a complete CPU subsystem for embedded designs.

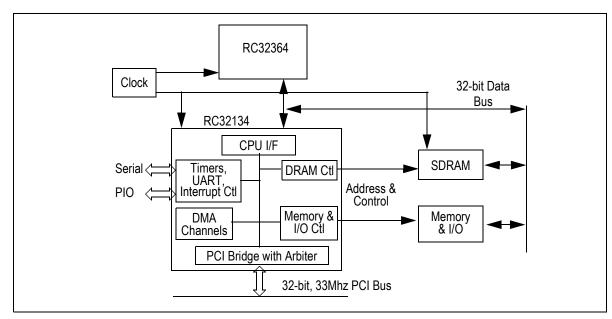

Figure 1 illustrates the typical system implementation, based on the RC32364 CPU and the RC32134 system controller. The RC32134 interfaces directly to the RC32364 and provides all of the necessary control and address signals to drive the external memory and I/O. Note that, depending on the loading of the CPU data bus, external data buffers could be used to reduce the loading and isolate different memory regions. As illustrated in the system block diagram, the memory and I/O data path is external to the RC32134.

#### **Device Overview**

The RC32134 interfaces directly to the RC32364's system bus. The RC32134 latches the address from the RC32364 internally and decodes it to detect which memory, I/O, or on-chip peripheral is being accessed, per the internal address map of the RC32134. The RC32134 generates all necessary control signals and address buses to the external memory and I/O. For main memory, I/O, on-chip peripherals, registers, and PCI, the RC32134 divides the physical address space into 14 different regions.

The data path for the local memory and peripherals (with the exception of PCI) is external to the RC32134. The data path from the PCI bus

and from the internal peripherals and registers is internal to the RC32134.

**Memory Controller.** The Memory Controller on the RC32134 provides all of the address buses and control signals for interfacing the RC32364 CPU to standard SRAM, PROM, FLASH, and I/O and includes the boot PROM interface. The memory controller provides six individual chip selects and supports 8,16, and 32-bit wide memory and I/Os. Two chip selects have highly configurable memory address ranges, allowing selection of various memory types and widths to be supported. The RC32134 provides controls for optional external data transceivers for systems that require fast signalling with large loads.

**SDRAM Controller.** The SDRAM controller optimization provides higher throughput while using available DRAM technology. The SDRAM control register directly manages four banks of 32-bit physical non-interleaved memory. Each bank is 32-bits wide and supports a maximum of 64 MB per bank. Total memory support is 256 MB. The SDRAM controller has a built in refresh generator.

**EDO DRAM Controller.** The RC32134 EDO DRAM Controller supports up to 4 banks of non-interleaved 32-bit wide EDO DRAMs. Most of the EDO DRAM pins are shared with the SDRAM controller, and as such, the two operations can not be simultaneously enabled. Selection between SDRAM or EDO DRAM is made at boot-time through system software operations. The EDO supports 256 MB total of EDO DRAM. The EDO controller has a built in refresh generator.

**PCI Interface.** To transfer data between main memory and the PCI bus, the RC32134 incorporates a PCI interface. At reset time the PCI interface can be configured as either a host or satellite interface. The PCI interface supports 32-bit PCI at up to 33MHz and is PCI Specification, Revision 2.1 compliant.

Figure 1 System Block Diagram

As a PCI master, the RC32134 can generate memory, I/O, or configuration cycles for direct local-to-PCI bus accesses. The PCI interface incorporates a 3-slot PCI bus arbiter, which includes fixed and round robin arbitration modes.

As a PCI target, the RC32134 allows access to its internal registers and to the RISCore32300 local bus through the PCI I/O read and write, or Memory read and write commands. The RC32134 PCI interface supports swapping little endian data to big endian, when the CPU subsystem is configured as a big endian system. For more information on the PDCI interface, please refer to the PCI Specification, Revision 2.1.

**DMA Controller.** Four general purpose DMA channels move data between source and destination ports. Source and destination ports can be system memory, PCI or I/O devices. Any of the four channels can be used for PCI initiator reads or writes. All four channels support a descriptor structure, to allow efficient data scatter/gather. The DMA controller supports swapping of data between big and little endian memory and I/O subsystems by memory region. It also supports quadword burst transfers. All external 16 and 8-bit memory I/Os are treated as memory-mapped, word-aligned devices.

**Expansion Interrupt Controller.** The Expansion Interrupt Controller provides the interrupt logic for software to analyze the various RC32134 generated system interrupts and adds to the control already provided through the CP0 registers of the RC32364. Each system interrupt is registered and the pending status provided through this feature. The pending status can then be used to automatically generate a hardware interrupt to the CPU via individual mask bits. The pending interrupt status can also be optionally set or cleared by a direct software write.

PIO. Programmable I/O (PIO) pins are provided on the RC32134 so that any unused peripheral pins can be programmed for use as general purpose discrete I/O pins. These PIO pins can be software programmed as bidirectional lines, allowing pin values to be software programmed in output mode and software readable while in the input mode. The PIO pins can also be used as a source of interrupts to the CPU. Maximum Interfacing flexibility is thus provided without requiring extensive modifications to the board.

**UART.** The RC32134 incorporates two 16550 (an enhanced version of the 16450) compatible UARTs. To relieve the CPU of software overhead, the 16550 UART can be put into FIFO mode, allowing execution of either 16450 or 16550 compatible software. Two sets of 16-byte FIFOs are enabled during the 16550 mode: one set in the receive data path and one set in the transmit data path. A baud rate generator is included that divides the system clock by 1 to 64K and provides a 16X clock for driving the transmitter and receiver logic.

**Timers/Counters.** Three on-chip 32-bit general purpose Timers are provided on the RC32134. Each timer consists of both a count and a compare register. The count register resets to zero and then counts upward until it equals the compare register. When the count and compare registers are equal, the TC\_n output is asserted and the count is then reset to zero.

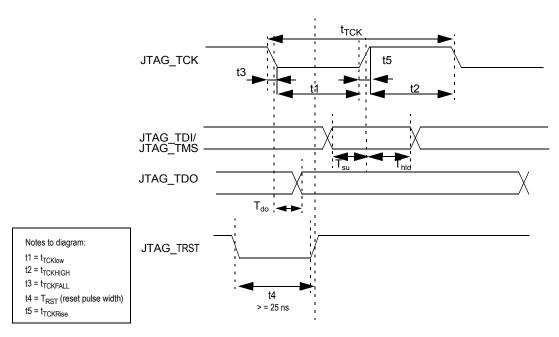

**JTAG.** Board-level manufacturing debugging is facilitated through implementation of a fully compliant IEEE std. 1149.1 JTAG Boundary Scan interface.

#### **Thermal Considerations**

The RC32134 is guaranteed in a case temperature range of 0°C to +90°C, for commercial temperature devices; - 40°C to +90°C for industrial temperature devices. The speed (power) of the device and airflow conditions affect the equivalent ambient temperature conditions that will meet this specification. The equivalent allowable ambient temperature, Ta, can be calculated using the thermal resistance from case to ambient ( $\oslash$ Ca) of the given package. The following equation relates ambient and case temperatures:

$$TA = TC - P * \varnothing CA$$

where P is the maximum power consumption at hot temperature, calculated by using the maximum Icc specification for the device. Typical values for  $\varnothing$ CA at various airflows are shown in Table 1

|                  | Ø <b>c</b> a |     |     |     |     |      |  |  |

|------------------|--------------|-----|-----|-----|-----|------|--|--|

| Airflow (ft/min) | 0            | 200 | 400 | 600 | 800 | 1000 |  |  |

| 208 PQFP         | 18           | 14  | 11  | 9   | 8   | 7    |  |  |

Table 1 Thermal Resistance (∅CA) at Various Airflows

### **Revision History:**

July 21, 1999:

Changed the following: Thermal Resistance values; Table 2, Pin Descriptions; Logic diagram - RC32134; Clock parameter temperature from 85 to 90 degrees; AC timing characteristics - RC32134; DC electrical characteristics; Power consumption - RC32134; Absolute maximum ratings diagram; Pin-out 208-PQFP table; RC32134 alternate signal functions.

**September 2, 1999:** Corrected package drawing from 144-pin to 208-pin.

**November 1, 1999**: Removed Maximum column from Power Consumption table.

**November 9, 1999**: Moved pin 208 (sdram\_245\_oe\_n) from Low drive to High drive in DC Electrical Characteristics Table.

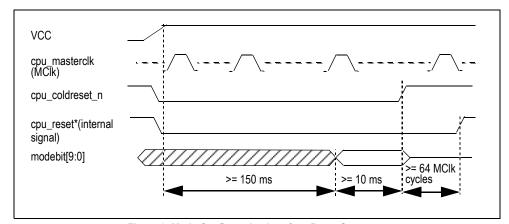

**April 28, 2000**: Added Mode Configuration Interface Reset Sequence figure on page 14.

#### January 6, 2000:

- Reordered Alternate Signals for the PIO Interface in Table 2 and changed pci eeprom mdi to pci eeprom mdo.

- Switched alternate pin signals for pci\_eeprom\_mdo and pci\_eeprom\_mdi in PCI Interface section of Table 2.

- Switched alternate pin signals for uart\_rx and uart\_tx in UART Interface section of Table 2.

- In RC32134 Alternate Signal Functions table, changed pin designations under Alt #1 column for pins 22 - 29.

- Changed 64145 references to 32134 in the Note section of the AC Timing Characteristics table.

- Updated the User Manual Timing Diagram Reference column in the AC Timing Characteristics table.

March 20, 2000: Changed PCI speed to 33 MHz.

**June 20, 2000**: Values were revised for three local memory/peripheral bus signals in the AC Timing Characteristics table.

**July 12, 2000**: Revised Tsu and ThId symbol numbers in UART section of AC Timing Characteristics table and revised reference to timing diagram.

**April 9, 2001**: In the Local Memory/Peripheral bus section of the AC Timing Characteristics table, deleted cpu\_coldreset\_n associated with Tsu4.

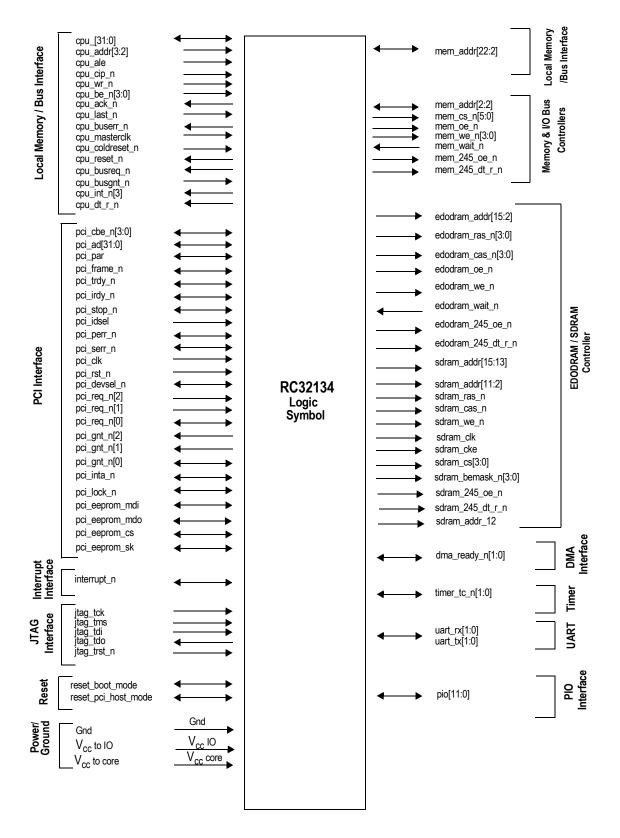

### **Pin Description Table**

The following table lists the pins provided on the RC32134. Note that several pins are multiplexed and have been assigned alternate functions. These pins are designated and defined accordingly throughout this table. Also note that those pin names followed by \_n are active-low signals.

| Pin Name           | Туре        | Alternate Signal(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|--------------------|-------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Local Memory and P | eripheral F | Pins                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| cpu_ad[31:0]       | 1/0         | Not applicable      | CPU Address/Data Bus  This is the RC32134's primary multiplexed and bidirectional address and data bus. The RC32134 latches this bus internally and uses it to generate the necessary address lines to the external memory and peripherals. If the transaction is a write, the CPU then drives data on cpu_ad(31:0). During CPU generated transactions, the CPU drives Address(31:4) into the cpu_ad bus, during its address phase. During DMA generated transactions (or RC32134 internal register reads), the address phase is unused and the chip drives data during a write. |  |  |  |  |  |

| cpu_addr[3:2]      | I           | Not applicable      | CPU LSB Address Bus  During CPU generated transactions, the CPU drives Address(3:2) onto the cpu_addr bus. The RC32134 does not internally use the cpu_addr bus during the data phase. However, 8- or 16-bit memory or I/O systems must attach these two pins instead of mem_addr(3:2).                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| cpu_ale            | I           | Not applicable      | CPU Address Latch Enable During CPU generated transactions, this signal indicates that the cpu_ad (31:0) is driving a valid address and can be latched internally by the RC32134.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| cpu_cip_n          | I           | Not applicable      | CPU Cycle In Progress  During CPU generated transactions, this active-low signal indicates that a bus transaction is active.  An external pullup resistor is required.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| cpu_wr_n           | I           | Not applicable      | CPU Write Status  During CPU generated transactions, this active-low signal indicates whether or not a write is occurring. If a write is not occurring, then the implication is that a read is in progress.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| cpu_be_n[3:0]      | I           | Not applicable      | CPU Byte Enable Bus During CPU generated transactions, these active-low signals indicate which byte lanes are in use.  Note: The table below indicates which cpu_be_n signal corresponds to which byte lane, whether or not the system is in big or little endian mode                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                    |             |                     | Data Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                    |             |                     | cpu_be_n[0] 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                    |             |                     | cpu_be_n[1] 15:8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                    |             |                     | cpu_be_n[2] 23:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                    |             |                     | cpu_be_n[3] 31:24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| cpu_ack_n          | 0           | Not applicable      | CPU Acknowledge During CPU generated transactions, this active-low signal is generated by the RC32134 to indicate that the present data have been accepted.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| cpu_last_n         | I           | Not applicable      | CPU Last Data  During CPU generated transactions, this active-low signal indicates during the data phase that the present data is the last data.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| cpu_buserr_n       | 0           | Not applicable      | CPU Bus Error  During both CPU and DMA generated transactions, this active-low signal indicates that a bus error has occurred. This signal can also be optionally attached to an interrupt line.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

Table 2 RC32134 Pin Descriptions (Page 1 of 8)

| Pin Name        | Туре | Alternate Signal(s)                                        | Description                                                                                                                                                                                                                                                                                                                        |                                              |                                         |                        |  |  |  |

|-----------------|------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------|------------------------|--|--|--|

| cpu_masterclk   | I    | sdram_clk                                                  | CPU Master System Clock Provides the basic system clock. This clock must be the same clock that is provided to the RC32364 and also, if used, to SDRAM.                                                                                                                                                                            |                                              |                                         |                        |  |  |  |

| cpu_coldreset_n | I    | Not applicable                                             | CPU Cold Reset This active-low signal is asserted to the RC32364 CPU and RC32134 after $V_{\rm cc}$ becomes valid on the initial power-up. The Reset initialization vectors, for both the RC32364 and the RC32134, are latched by cold reset.                                                                                      |                                              |                                         |                        |  |  |  |

| cpu_reset_n     | 0    | Not applicable                                             | CPU Warm Reset This active-low signal is a secondary reset signal asserted to the CPU at least 256 clocks after cold reset, allowing, for instance, stabilization of RC32364's PLL.                                                                                                                                                |                                              |                                         |                        |  |  |  |

| cpu_busreq_n    | 0    | Not applicable                                             | CPU Bus Request This active-low signal requests the CPU bus from the RC32364, for instance, by RC32134 to perform a DMA operation.                                                                                                                                                                                                 |                                              |                                         |                        |  |  |  |

| cpu_busgnt_n    | I    | Not applicable                                             | CPU Bus Grant This active-low signal is a CPU bus grant from the RC32364, indicating that the local CPU bus has been released to the RC32134.                                                                                                                                                                                      |                                              |                                         |                        |  |  |  |

| cpu_int_n       | 0    | interrupt_n                                                | CPU Interrupt This active-low signal is an interrupt indication to the CPU from RC32134's Interrupt Controller. Note: This pin is typically hooked up to the CPU's interrupt 3.                                                                                                                                                    |                                              |                                         |                        |  |  |  |

| cpu_dt_r_n      | 0    | mem_245_dt_r_n,<br>sdram_245_dt_r_n,<br>edodram_245_dt_r_n | CPU Direction Transmit/Receive This active-low signal controls the DT/R pin of an optional FCT245 transceiver bank. It is asserted during DMA read operations. This signal is tri-stated during CPU accesses (when the CPU owns the bus) and driven during DMA generated accesses. Note: An external pull-up resistor is required. |                                              |                                         |                        |  |  |  |

| PCI Interface   |      |                                                            |                                                                                                                                                                                                                                                                                                                                    |                                              |                                         |                        |  |  |  |

| pci_ad[31:0]    | I/O  | Not applicable                                             | PCI Multiplexed Address/Data Bus<br>This address is driven by the Bus Ma<br>the Bus Master during writes; or the                                                                                                                                                                                                                   | aster during                                 |                                         |                        |  |  |  |

| pci_cbe_n[3:0]  | I/O  | Not applicable                                             | PCI Multiplexed Command/Byte E The Command bus (active high) is d The Byte Enable bus (active low) is d Note: The table below indicates which not the system is in big or little endia                                                                                                                                             | driven by the<br>driven by the<br>ich cpu_be | e Bus Master durii<br>ne Bus Master dur | ing the data phase(s). |  |  |  |

|                 |      |                                                            |                                                                                                                                                                                                                                                                                                                                    |                                              | Data Bits                               |                        |  |  |  |

|                 |      |                                                            | pc                                                                                                                                                                                                                                                                                                                                 | ci_be[0]                                     | 7:0                                     |                        |  |  |  |

|                 |      |                                                            | pc                                                                                                                                                                                                                                                                                                                                 | ci_be[1]                                     | 15:8                                    |                        |  |  |  |

|                 |      |                                                            | pc                                                                                                                                                                                                                                                                                                                                 | ci_be[2]                                     | 23:16                                   |                        |  |  |  |

|                 |      |                                                            | рс                                                                                                                                                                                                                                                                                                                                 | ci_be[3]                                     | 31:24                                   |                        |  |  |  |

| pci_par         | I/O  | Not applicable                                             | PCI Parity This signal indicates even parity of the pci_ad[31:0] bus and is driven by the Bus Master during Address and Write Data phases. During the Read data phase, this signal is driven by the Bus Slave.                                                                                                                     |                                              |                                         |                        |  |  |  |

| pci_frame_n     | I/O  | Not applicable                                             | PCI Frame Negated  This active-low signal is driven by the Bus Master and indicates the duration of a PCI transfer. Assertion indicates the beginning of a bus transaction. De-assertion indicates the last data.                                                                                                                  |                                              |                                         |                        |  |  |  |

Table 2 RC32134 Pin Descriptions (Page 2 of 8)

| Pin Name     | Туре | Alternate Signal(s) | Description                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|--------------|------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| pci_trdy_n   | I/O  | Not applicable      | PCI Target Ready Negated This active-low signal is driven by the Bus Slave and indicates that the current data can complete (the bus slave can accept/drive data).                                                                                                                                                                                                                        |  |  |  |

| pci_irdy_n   | I/O  | Not applicable      | PCI Initiator Ready Negated Driven by the Bus Master, this active-low signal indicates that the current data can complete (PCI initiator is ready to accept/drive data).                                                                                                                                                                                                                  |  |  |  |

| pci_stop_n   | I/O  | Not applicable      | PCI Stop Negated Driven by the Bus Slave this active-low signal terminates the current bus transaction.                                                                                                                                                                                                                                                                                   |  |  |  |

| pci_idsel    | I    | pci_req_n[2]        | PCI Initialization Device Select  Host mode: pci_req_n[2] is an input indicating a request from an external device.  Satellite mode: used as pci_idsel pin which selects this device during a configuration read or writ                                                                                                                                                                  |  |  |  |

| pci_perr_n   | I/O  | Not applicable      | PCI Parity Error Negated Driven by the receiving Bus Agent 2 clocks after the data is received, if a parity error occurs.                                                                                                                                                                                                                                                                 |  |  |  |

| pci_serr_n   | I/O  | Not applicable      | System Error Driven by any agent, this active-low signal indicates an address parity error, data parity during a Scial Cycle command, or any other system error. An external 2.7K (5V) ohm or 8.2K (3.3V) ohm pup resistor is required, per the PCI revision 2.1 specifications.                                                                                                          |  |  |  |

| pci_clk      | I    | Not applicable      | PCI Clock Clock for PCI bus transactions that uses the rising edge for all timing references. Note that th clock does not need to be synchronized to the cpu_masterclk.                                                                                                                                                                                                                   |  |  |  |

| pci_rst_n    | I    | Not applicable      | PCI Reset Negated In Host mode, this active-low signal resets all PCI related logic. In Satellite mode, with boot from PCI mode, this signal resets all PCI related logic and also asserts the warm reset, cpu_rst_n, to the RC32134. and the RC32364.                                                                                                                                    |  |  |  |

| pci_devsel_n | I/O  | Not applicable      | PCI Device Select Negated  This active-low signal is driven by the target to indicate that the target has decoded the present address as a target address.                                                                                                                                                                                                                                |  |  |  |

| pci_req_n[2] | I    | pci_idsel           | PCI Bus Request #2 Negated  This is an active-low signal that in Host mode is an input indicating a request from an external device. In Satellite mode pci_req_n[2] is used as the pci_idsel pin, which selects this device during a configuration read or write.                                                                                                                         |  |  |  |

| pci_req_n[1] | I    | Not applicable      | PCI Bus Request #1 Negated In Host mode, pci_req_n[1] is an input indicating a request from an external device. In Satellite mode pci_req_n[1] is unused.                                                                                                                                                                                                                                 |  |  |  |

| pci_req_n[0] | I/O  | Not applicable      | PCI Bus Request #0 Negated In Host mode, this active-low signal is an input indicating a request from an external device. In Satel-lite mode, pci_req_n[0] is an output indicating a request from this device.                                                                                                                                                                            |  |  |  |

| pci_gnt_n[2] | 0    | pci_inta_n          | PCI Bus Grant #2 Negated In Host mode, this active-low signal is an output indicating a grant to an external device. In Satellite mode, pci_gnt_n[2] is used as the pci_inta_n output pin. An external 5k ohm pull-up resistor is required, per the PCI revision 2.1 specifications.  Note: In host mode, int_n[1] on the RC32364 can be used for a pci_inta_n input and pci_int[d:c:b]_n |  |  |  |

| pci_gnt_n[1] | 0    | pci_eeprom_cs       | uses int_n[5:4:2] on the RC32364 Bus Interface.  PCI Bus Grant #1 Negated In Host mode, this active-low signal is an output indicating grants to external devices. In Satellite mode, pci_gnt_n[1] is used as the pci_eeprom_cs output pin for Serial Chip Select, for loading PCI Configuration Registers in the RC32134 Reset Initialization Vector PCI boot mode.                      |  |  |  |

Table 2 RC32134 Pin Descriptions (Page 3 of 8)

| Pin Name            | Туре | Alternate Signal(s)                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|---------------------|------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| pci_gnt_n[0]        | I/O  | Not applicable                                              | PCI Bus Grant #0 Negated In Host mode, this active-low signal is an output indicating a grant to an external device. In Satellite mode, pci_gnt_n[0] is an input indicating a grant to this device.                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| pci_inta_n          | I/O  | pci_gnt_n[2]                                                | PCI Interrupt #A Negated In Host mode,pci_gnt_n[2] is an output indicating a grant to an external device. In Satellite mode, pci_gnt_n[2] is used as the pci_inta_n output pin. An external pull-up is required, per the PCI revision 2.1 specifications.                                                                                                                                                                                          |  |  |  |  |  |  |

|                     |      |                                                             | Note: In host mode, int_n[1] on the RC32364 can be used for a pci_inta_n input and pci_int[d:c:b]_ uses int_n[5:4:2] on the RC32364 Bus Interface.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| pci_lock_n          | I    | Not applicable                                              | PCI Lock Negated This active-low signal is driven by the Bus Master and indicates that an exclusive operation is occurring.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| pci_eeprom_mdo      | I/O  | pio[11]                                                     | PCI EEPROM Master Data Out In Serial mode, this signal is an output pin from RC32134 that connects as an Input to a Serial Chip for the Serial data input stream. In PCI satellite mode, it is an output pin from RC32134 that connects as an Input to a Serial Chip for the Serial data input stream for loading PCI Configuration Registers in the RC32134 Reset Initialization Vector PCI boot mode. This pin is also multiplexed as a PIO pin. |  |  |  |  |  |  |

| pci_eeprom_mdi      | I/O  | pio[8]                                                      | PCI EEPROM Master Data In The Serial mode provides an input pin to RC32134 from the Output of a Serial Chip for the Serial data output stream. The PCI satellite mode provides an input pin to RC32134 from the Output of a Serial Chip for the Serial data output stream, for PCI Configuration Registers in the RC32134 Reset Initialization Vector PCI boot mode. This pin is also multiplexed as a PIO pin.                                    |  |  |  |  |  |  |

| pci_eeprom_cs       | I/O  | pci_gnt_n[1]                                                | PCI EEPROM Chip Select Host mode: pci_gnt_n[1] is an output indicating grants to external devices. Satellite mode: Used as pci_eeprom_cs output pin for SPI Chip Select for loading PCI Configuration Registers in the RC32134 Reset Initialization Vector PCI boot mode.                                                                                                                                                                          |  |  |  |  |  |  |

| pci_eeprom_sk       | I/O  | pio[10]                                                     | PCI EEPROM Serial Clock Serial mode: Output pin for Serial Clock. PCI satellite mode: Output pin for Serial Clock for loading PCI Configuration Registers in the RC32134 Reset Initialization Vector PCI boot mode. This pin is also multiplexed as a PIO pin.                                                                                                                                                                                     |  |  |  |  |  |  |

| Memory/I/O Controll | er   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| mem_addr[22:2]      | I/O  | edodram_addr[15:2]<br>sdram_addr[15:13]<br>sdram_addr[11:2] | Memory Address Bus These signals provide the Memory or DRAM address, during a Memory or DRAM bus transaction. During each word data, the address increments either in linear or sub-block ordering, depending on the transaction type. For 32-bit system, use mem_addr[3:2] for the least significant address bits [3:2]. For 8 or 16-bit wide ports, to provide the least significant address bits [3:0], use cpu_addr[3:2] and cpu_be_n[1:0].    |  |  |  |  |  |  |

|                     |      |                                                             | mem_addr subsets                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                     |      |                                                             | mem_addr[22:20] I/O reset_boot_mode[1:0] reset_pci_host_mode                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                     |      |                                                             | mem_addr[15:2]                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| mem_cs_n[5:0]       | 0    | Not applicable                                              | Memory Chip Select Negated This active-low signal indicates that a Memory or I/O Bank is actively selected.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

Table 2 RC32134 Pin Descriptions (Page 4 of 8)

0

0

0

sdram bemask n[3:0]

sdram\_ras\_n, sdram 245 oe n

sdram\_we\_n

mem\_wait\_n

edodram cas n[3:0]

edodram\_oe\_n

edodram\_we\_n

edodram\_wait\_n

| Pin Name           | Туре | Alternate Signal(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mem_oe_n           | 0    | Not applicable      | Memory Output Enable Negated This active-low signal indicates that either a Memory or I/O Bank can output its data lines onto the cpu_ad bus.                                                                                                                                                                                                                                                                           |

| mem_we_n[3:0]      | 0    | Not applicable      | Memory Write Enable Negated Bus These active-low signals indicate which bytes are to be written during a memory or I/O transaction.                                                                                                                                                                                                                                                                                     |

| mem_wait_n         | 1    | edo_dram_wait_n     | Memory Wait Negated In MEM, IOI, IOM modes this active-low signal allows external wait-states to be injected during the last cycle before data is sampled. In DPM (dual-port) mode, this signal allows dual-port busy signal to restart memory transaction.                                                                                                                                                             |

| mem_245_oe_n       | 0    | Not applicable      | Memory FCT245 Output Enable Negated This active-low signal controls output enable to optional FCT245 transceiver bank by asserting during both reads and writes to a memory or I/O bank.                                                                                                                                                                                                                                |

| mem_245_dt_r_n     | 0    | cpu_dt_r_n          | Memory FCT245 Direction Xmit/Rcv Negated Uses the cpu_dt_r_n pin.                                                                                                                                                                                                                                                                                                                                                       |

| EDODRAM Controlle  | r    |                     |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| edodram_addr[15:2] | 0    | mem_addr[15:2]      | Edodram_addr/sdram_addr mode  These are output signals that provide a DRAM address during a DRAM transaction. The DRAM address multiplexes between Row and Column Addresses. During each word data, the column address increments either in linear or sub-block ordering, depending on the type of transaction. Allows an external memory debug emulator to inject wait-states. For more detail, see the user's manual. |

| edodram_ras_n[3:0] | 0    | sdram_cs_n[3:0]     | DRAM Row Address Strobe Negated Bus SDRAM mode: Provides chip select to each SDRAM bank. EDODRAM mode: Used as edodram_ras_n[3:0] pins to provide a RAS signal for each EDODRAM                                                                                                                                                                                                                                         |

#### **DRAM EDO Output Enable Negated**

**DRAM Column Address Strobe Negated Bus**

bank.

DRAM banks.

In the EDODRAM mode, this active-low signal provides an output enable signal for reads for particular OE types of EDODRAM. This signal also controls the output enable to an optional FCT245 transceiver bank by asserting during both reads and writes to any DRAM bank. This signal also controls the output enable to each EDO DRAM chip. Alternatively, because the EDODRAM controller always uses Early Writes and CAS controlled non-interleaved Reads, the OE\_n pin, on each EDO DRAM chip, can simply be tied to ground. The SDRAM RAS mode is a control signal to all SDRAM banks. In SDRAM mode, this signal controls the output enable to an optional FCT245 transceiver bank by asserting during both reads and writes to any DRAM bank. **DRAM EDO Write Enable Negated**

In the EDODRAM mode these signals are used as edodram\_cas\_n[3:0] to provide a CAS signal for each byte lane. In the SDRAM mode, these signals provide byte enables for each byte lane of all

In EDODRAM mode, this active-low signal is used as the edodram\_we\_n pin to provide a write enable signal for EDODRAM. Write enable is valid at all times and high during refresh. In SDRAM mode, this signal provides the SDRAM WE control signal to all SDRAM banks.

#### **DRAM Wait Negated**

In the EDO DRAM mode, this active-low signal allows external wait-states to be injected at any time during the EDO DRAM cycle. In the MEM, IOI, IOM modes, this active-low signal allows external wait-states to be injected during the last cycle before data is sampled. The DPM (dual-port) mode allows the dual-port busy signal to restart memory transactions.

Table 2 RC32134 Pin Descriptions (Page 5 of 8)

| Pin Name           | Туре | Alternate Signal(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| edodram_245_oe_n   | 0    | sdram_245_oe_n      | DRAM FCT245 Output Enable Negated In the SDRAM mode this active-low signal controls the output enable to an optional FCT245 transceiver bank by asserting during both reads and writes to any DRAM bank. In the EDODRAM mode this signal controls the output enable to an optional FCT245 transceiver bank by asserting during both reads and writes to any DRAM bank. This signal also controls the output enable to each EDO DRAM chip. Alternatively, because the EDODRAM controller always uses Early Writes and CAS controlled non-interleaved Reads, the OE_n pin, on each EDO DRAM chip, can simply be tied to ground |

| edodram_245_dt_r_n | 0    | cpu_dt_r_n          | DRAM/Mem FCT245 Direct Xmit/Rcv Negated  This active-low signal controls the DT/R pin of an optional FCT245 transceiver bank. It is asserted during DMA read operations. This signal is tri-stated during CPU accesses (when the CPU owns the bus) and drives during DMA generated accesses.                                                                                                                                                                                                                                                                                                                                 |

| sdram_addr[15:13]<br>sdram_addr[11:2] | 0 | mem_addr[15:13]<br>mem_addr[11:2] | SDRAM Address Bus These signals are outputs providing a DRAM address during a DRAM transaction. The DRAM address multiplexes between Row and Column Addresses. During each word data, the column address increments either in linear or sub-block ordering, depending on the type of transaction.                                                                                                                                                                                                                                                                                       |

|---------------------------------------|---|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sdram_addr_12                         | 0 | PIO[9]                            | SDRAM Address line 12 This SDRAM address is dedicated to the SDRAM and multiplexes between the row address; and during the precharge command, the "all bank" indicator.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| sdram_ras_n                           | 0 | edodram_oe_n                      | SDRAM RAS Negated SDRAM mode: Provides SDRAM RAS control signal to all SDRAM banks. EDODRAM mode: Provides an output enable signal for reads for particular OE types of EDODRAM.                                                                                                                                                                                                                                                                                                                                                                                                        |

| sdram_cas_n                           | 0 | Not applicable                    | SDRAM CAS Negated This active-low signal provides an SDRAM CAS control signal to all SDRAM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| sdram_we_n                            | 0 | edodram_we_n                      | SDRAM WE Negated SDRAM mode: Provides SDRAM WE control signal to all SDRAM banks. EDODRAM mode: Used as edodram_we_n pin to provide a write enable signal for EDODRAM. Write enable is valid at all times and high during refresh.                                                                                                                                                                                                                                                                                                                                                      |

| sdram_clk                             | I | cpu_masterclk                     | SDRAM Clock This signal provides the basic system clock and must be the same clock that is provided to the RC32364 and also, if used, to SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| sdram_cke                             | 0 | Not applicable                    | SDRAM Clock Enable In the SDRAM mode this signal provides the clock enable to all SDRAM banks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| sdram_cs_n[3:0]                       | 0 | edodram_ras_n[3:0]                | SDRAM Chip Select Negated Bus In SDRAM mode, these active-low signals provide chip select to each SDRAM bank. In EDODRAM mode they are used as the edodram_ras_n[3:0] pins and provide a RAS signal for each EDODRAM bank.                                                                                                                                                                                                                                                                                                                                                              |

| sdram_bemask_n[3:0]                   | 0 | edodram_cas_n[3:0]                | SDRAM Byte Enable Mask Negated Bus The SDRAM mode provides byte enables for each byte lane of all DRAM banks. To provide a CAS signal for each byte lane, the EDODRAM mode is used as edodram_cas_n[3:0].                                                                                                                                                                                                                                                                                                                                                                               |

| sdram_245_oe_n                        | 0 | edodram_245_oe_n,<br>edodram_oe_n | SDRAM FCT245 Output Enable Negated In SDRAM mode, this active-low signal controls output enable to optional FCT245 transceiver bank by asserting during both reads and writes to any DRAM bank. In EDODRAM mode this signal controls output enable to optional FCT245 transceiver bank by asserting during both reads and writes to any DRAM bank. Also controls output enable to each EDO DRAM chip. Alternatively, because the EDODRAM controller always uses Early Writes and CAS controlled non-interleaved Reads, the OE_n pin on each EDO DRAM chip can simply be tied to ground. |

Table 2 RC32134 Pin Descriptions (Page 6 of 8)

| Pin Name                                                                                                           | Туре | Alternate Signal(s)                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| sdram_245_dt_r_n O cpu_dt_r_n                                                                                      |      | cpu_dt_r_n                                                                                                                                                          | SDRAM FCT245 Direction Transmit/Receive This active-low signal controls the DT/R pin of an optional FCT245 transceiver bank and is asserted during DMA read operations. This signal is tri-stated during CPU accesses (when the CPU owns the bus) and drives during DMA generated accesses.            |  |  |  |  |

| DMA Interface                                                                                                      | 1    |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| dma_ready_n[1:0]                                                                                                   | I/O  | dma_done_n[1:0]<br>pio[1:0]                                                                                                                                         | DMA Ready Negated Bus Input pin for general purpose DMA channels[1:0] that can initiate the next datum in the current DMA descriptor frame. dma_ready_n[1:0] pins are not synchronized internally by the RC32134 and thus must meet the specified setup and hold time with respect to the input clock. |  |  |  |  |

| dma_done_n[1:0] I/O dma_ready_n[1:0] DMA Done Input pin for general purpose DMA channels[1:0] that can tell frame. |      | Input pin for general purpose DMA channels[1:0] that can terminate the current DMA descriptor                                                                       |                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Interrupt Controller                                                                                               | 1    |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| interrupt_n                                                                                                        | I/O  | cpu_int_n                                                                                                                                                           | Interrupt Negated Uses cpu_int_n. This active-low signal is an interrupt indication to the CPU from RC32134's Interrupt Controller.                                                                                                                                                                    |  |  |  |  |

| PIO Interface                                                                                                      |      |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| pio[11:0]                                                                                                          | 1/0  | pci_eeprom_mdo pci_eeprom_sk sdram_addr_12 pci_eeprom_mdi uart _rx[0], uart_tx[0] uart_rx[1], uart_tx[1] timer_tc_n[0], timer_tc_n[1] dma_ready_n[0] dma_ready_n[1] | Programmable Input/Output General purpose pins that can each be configured as a general purpose input or general purpose output. The pci_eeprom_mdo, pci_eeprom_sk, and sdram_addr12 default to outputs. The rest default to inputs.                                                                   |  |  |  |  |

| Timer/Counter                                                                                                      |      |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| timer_tc_n[1:0]                                                                                                    | 0    | timer_gate_n[1:0], pio[3:2]                                                                                                                                         | Timer Terminal Count Overflow Negated Output indicating that the timer has reached its count compare value and has overflowed back to 0.                                                                                                                                                               |  |  |  |  |

| timer_gate_n[1:0]                                                                                                  | I    | timer_tc_n[1:0], pio[3:2]                                                                                                                                           | Timer Gate Negated Input indicating that the timer may count one tick on the next clock edge.                                                                                                                                                                                                          |  |  |  |  |

| UART Interface                                                                                                     | •    |                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| uart_rx[1:0]                                                                                                       | I/O  | pio[7]<br>pio[5]                                                                                                                                                    | UART Receive Data Bus UART mode: Each UART channel receives data on their respective input pin.                                                                                                                                                                                                        |  |  |  |  |

| uart_tx[1:0]                                                                                                       | I/O  | pio[6]<br>pio[4]                                                                                                                                                    | UART Transmit Data Bus UART mode: Each UART channel sends data on their respective output pin. Note that these pins default to inputs at reset time and must be programmed via the PIO interface before being used as UART outputs.                                                                    |  |  |  |  |

Table 2 RC32134 Pin Descriptions (Page 7 of 8)

| Pin Name             | Туре     | Alternate Signal(s) |                                                                                                                                                                                        |                                                                                      |            | Description                                                                                               |                  |  |

|----------------------|----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------|------------------|--|

| Reset                | <u> </u> | 1                   |                                                                                                                                                                                        |                                                                                      |            |                                                                                                           |                  |  |

| reset_boot_mode[1:0] | I/O      | mem_addr[22:21]     | Reset Initiali<br>Used as Res                                                                                                                                                          |                                                                                      |            | or input pins that are latched by coldreset_n de-ass                                                      | serting.         |  |

|                      |          |                     |                                                                                                                                                                                        | Value                                                                                |            | Description                                                                                               |                  |  |

|                      |          |                     |                                                                                                                                                                                        | 11 <b>Non-boot mode</b> . Idle at reset. This RC32134 does supply boot code control. |            |                                                                                                           |                  |  |

|                      |          |                     | 10 Reserved.                                                                                                                                                                           |                                                                                      | ed.        |                                                                                                           |                  |  |