#

## 2:1 DIFFERENTIAL-TO-LVDS MULTIPLEXER

## ICS85401

## Description

The ICS85401 is a high performance 2:1 Differential-to-LVDS Multiplexer and a member of the HiPerClockS™family of High Performance Clock Solutions from ICS. The ICS85401 can also perform differential translation because the differ-ential

inputs accept LVPECL, CML as well as LVDS levels. The ICS85401 is packaged in a small 3mm x 3mm 16 VFQFN package, making it ideal for use on space constrained boards.

### **Features**

- 2:1 LVDS MUX

- One LVDS output pair

- Two differential clock inputs can accept: LVPECL, LVDS, CML

- Maximum input/output frequency: 2.5GHz

- Translates LVCMOS/LVTTL input signals to LVDS levels by using a resistor bias network on nCLK0, nCLK1

- Propagation delay: 460ps (maximum)

- Part-to-part skew: 100ps (maximum)

- Full 3.3V supply mode

- -40°C to 85°C ambient operating temperature

- Available in both standard (RoHS 5) and lead-free (RoHS 6) packages

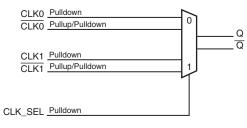

## **Block Diagram**

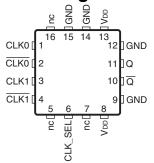

## **Pin Assignment**

#### ICS85401

16-Lead VFQFN 3mm x 3mm x 0.95mm package body K Package Top View

| Number        | Name            | Т      | уре                 | Description                                                                                                                           |

|---------------|-----------------|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1             | CLK0            | Input  | Pulldown            | Non-inverting differential clock input.                                                                                               |

| 2             | CLK0            | Input  | Pullup/<br>Pulldown | Inverting differential clock input. VDD/2 default when left floating.                                                                 |

| 3             | CLK1            | Input  | Pulldown            | Non-inverting differential clock input.                                                                                               |

| 4             | CLK1            | Input  | Pullup/<br>Pulldown | Inverting differential clock input. VDD/2 default when left floating.                                                                 |

| 5, 7, 16      | nc              | Unused |                     | No connect.                                                                                                                           |

| 6             | CLK_SEL         | Input  | Pulldown            | Clock select input. When HIGH, selects CLK1, CLK1 inputs.<br>When LOW, selects CLK0, CLK0 inputs.<br>LVCMOS / LVTTL interface levels. |

| 8, 13         | V <sub>DD</sub> | Power  |                     | Power supply pins.                                                                                                                    |

| 9, 12, 14, 15 | GND             | Power  |                     | Power supply ground.                                                                                                                  |

| 10, 11        | <u>Q</u> , Q    | Output |                     | Differential output pair. LVDS interface levels.                                                                                      |

NOTE: Pullup and Pulldown refer to intenal input resistors. See Table 2, Pin Characteristics, for typical values.

## **Table 2. Pin Characteristics**

| Symbol                | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance       |                 |         | 1       |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |                 |         | 37      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                 |         | 37      |         | kΩ    |

## **Function Tables**

**Table 3. Control Input Function Table**

| Input   | CLK_OUT    |

|---------|------------|

| CLK_SEL | CLK        |

| 0       | CLK0, CLK0 |

| 1       | CLK1, CLK1 |

## Absolute Maximum Ratings

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics or AC Characterisitcs* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                                          | Rating                          |

|---------------------------------------------------------------|---------------------------------|

| Supply Voltage, V <sub>DD</sub>                               | 4.6V                            |

| Inputs, V <sub>I</sub>                                        | -0.5V to V <sub>DD</sub> + 0.5V |

| Outputs, I <sub>O</sub><br>Continous Current<br>Surge Current | 10mA<br>15mA                    |

| Package Thermal Impedance, $\theta_{JA}$                      | 51.5°C/W (0 lfpm)               |

| Storage Temperature, T <sub>STG</sub>                         | -65°C to 150°C                  |

## **DC Electrical Characteristics**

#### Table 4A. Power Supply DC Characteristics, $V_{DD}$ = 3.3V $\pm$ 5%, $T_{A}$ = -40°C to $85^{\circ}C$

| Symbol          | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|-------------------------|-----------------|---------|---------|---------|-------|

| V <sub>DD</sub> | Positive Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| I <sub>DD</sub> | Power Supply Current    |                 |         |         | 40      | mA    |

#### Table 4B. LVCMOS/LVTTL DC Characteristics, $V_{DD}$ = 3.3V $\pm$ 5%, $T_{A}$ = -40°C to 85°C

| Symbol          | Parameter          |         | Test Conditions                                | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------|---------|------------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage |         |                                                | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage  |         |                                                | -0.3    |         | 0.8                   | V     |

| I <sub>IH</sub> | Input High Current | CLK_SEL | $V_{DD} = V_{IN} = 3.465V$                     |         |         | 150                   | μA    |

| I <sub>IL</sub> | Input Low Current  | CLK_SEL | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -150    |         |                       | μΑ    |

#### Table 4C. Differential DC Characteristics, $V_{DD} = 3.3V \pm 5\%$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol             | Parameter            |                    | Test Conditions                                   | Minimum | Typical | Maximum         | Units |

|--------------------|----------------------|--------------------|---------------------------------------------------|---------|---------|-----------------|-------|

|                    | Input High Current   | CLK0, CLK1         | $V_{DD} = V_{IN} = 3.465V$                        |         |         | 150             | μA    |

| ЧΗ                 | Input High Current   | CLKO, CLK          | $V_{DD} = V_{IN} = 3.465V$                        |         |         | 150             | μA    |

| l <sub>IL</sub> In | Input Low Current    | CLK0, CLK1         | V <sub>DD</sub> = 3.465V,<br>V <sub>IN</sub> = 0V | -150    |         |                 | μΑ    |

|                    | •                    | CLKO, CLK          | V <sub>DD</sub> = 3.465V,<br>V <sub>IN</sub> = 0V | -150    |         |                 | μA    |

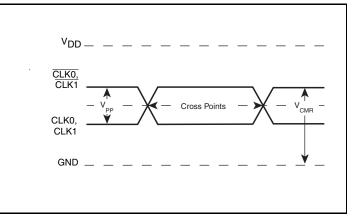

| V <sub>PP</sub>    | Peak-to-Peak Voltage |                    |                                                   | 0.15    | 0.8     | 1.2             | V     |

| V <sub>CMR</sub>   | Common Mode Input    | /oltage; NOTE 1, 2 |                                                   | 1.2     |         | V <sub>DD</sub> | V     |

NOTE 1: Common mode input voltage is defined as V<sub>IH</sub>.

NOTE 2: For single-ended applications, the maximum input voltage for CLKx,  $\overline{\text{CLKx}}$  is V<sub>DD</sub> + 0.3V.

| Symbol          | Parameter                        | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|----------------------------------|-----------------|---------|---------|---------|-------|

| V <sub>OD</sub> | Differential Output Voltage      |                 | 200     | 350     | 500     | mV    |

| $\Delta V_{OD}$ | V <sub>OD</sub> Magnitude Change |                 |         |         | 50      | mV    |

| V <sub>OS</sub> | Offset Voltage                   |                 | 1.05    | 1.15    | 1.25    | V     |

| $\Delta V_{OS}$ | V <sub>OS</sub> Magnitude Change |                 |         |         | 50      | mV    |

#### Table 4D. LVDS DC Characteristics, $V_{DD}$ = 3.3V $\pm$ 5%, $T_{A}$ = -40°C to 85°C

## **AC Electrical Characteristics**

Table 5. AC Characteristics,  $V_{DD}$  = 3.3V  $\pm$  5%,  $T_{A}$  = -40°C to 85°C

| Parameter                       | Symbol                       | Test Conditions | Minimum | Typical | Maximum | Units |

|---------------------------------|------------------------------|-----------------|---------|---------|---------|-------|

| f <sub>MAX</sub>                | Output Frequency             |                 |         |         | >2.5    | GHz   |

| t <sub>PD</sub>                 | Propagation Delay; NOTE 1    |                 | 260     | 360     | 460     | ps    |

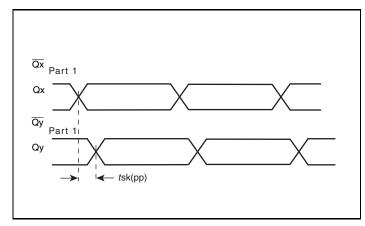

| <i>t</i> sk(pp)                 | Part-to-Part Skew; NOTE 2, 3 |                 |         |         | 100     | ps    |

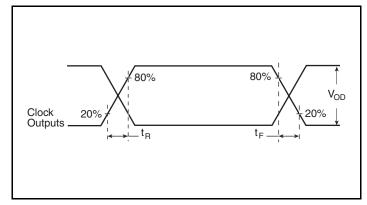

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time        | 20% to 80%      | 125     | 160     | 200     | ps    |

| odc                             | Output Duty Cycle            |                 | 49      |         | 51      | %     |

| MUX_ISOLATION                   | MUX Isolation                |                 |         | -55     |         |       |

All parameters measured at £ 1GHz unless otherwise noted.

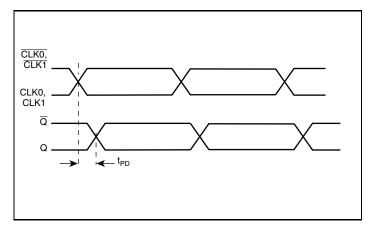

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65. Typical Phase Noise at 156.25MHz

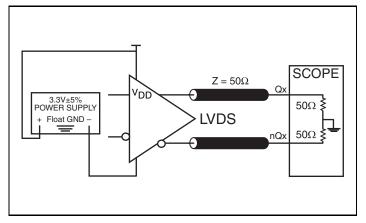

## **Parameter Measurement Information**

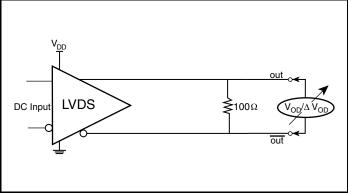

3.3V LVDS Output Load AC Test Circuit

Part-to-Part Skew

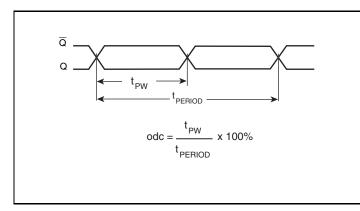

**Output Duty Cycle/Pulse Width/Period**

**Propagation Delay**

**Output Rise/Fall Time**

## Parameter Measurement Information, continued

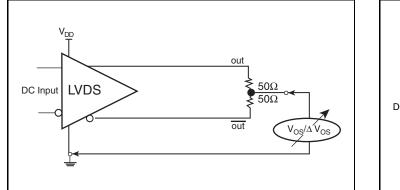

**Offset Voltage Setup**

## **Application Information**

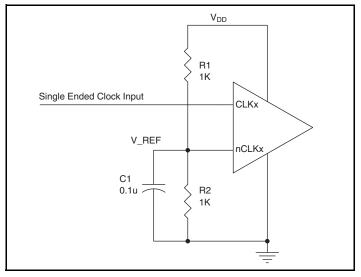

#### Wiring the Differential Input to Accept Single Ended Levels

*Figure 1* shows how the differential input can be wired to accept single ended levels. The reference voltage V\_REF =  $V_{DD}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio of R1 and R2 might need to be adjusted to position the V\_REF in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{DD}$  = 3.3V, V\_REF should be 1.25V and R2/R1 = 0.609.

Figure 1. Single-Ended Signal Driving Differential Input

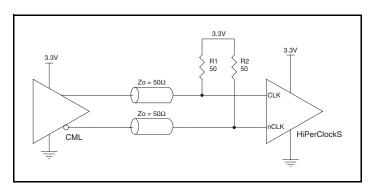

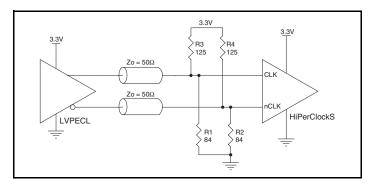

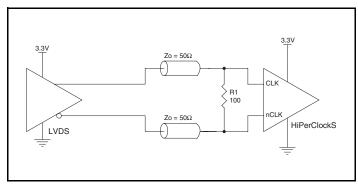

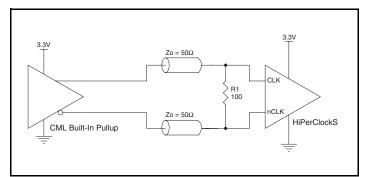

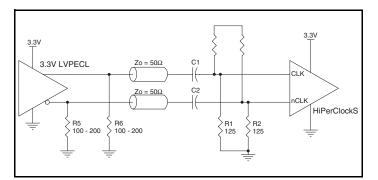

#### **Differential Clock Input Interface**

The CLKx /CLKx accepts LVPECL, LVDS, CML and other differential signals. The signal must meet the V<sub>PP</sub> and V<sub>CMR</sub> input requirements. *Figures 2A to 2E* show interface examples for the HiPerClockS CLKx/CLKx input driven by the most common driver

Figure 2A. HiPerClockS CLK/CLK Input Driven by an IDT Open Collector CML Driver

Figure 2C. HiPerClockS CLK/CLK Input Driven by a 3.3V LVPECL Driver

Figure 2E. HiPerClockS CLK/CLK Input Driven by a 3.3V LVDS Drive

types. The input interfaces suggested here are examples only. If the driver is from another vendor, use their termination recommendation. Please consult with the vendor of the driver component to confirm the driver termination requirements.

Figure 2B. HiPerClockS CLK/CLK Input Driven by a Built-In Pullup CML Driver

Figure 2D. HiPerClockS CLK/CLK Input Driven by a 3.3V LVPECL Driver with AC Couple

#### **Recommendations for Unused Input Pins**

#### Inputs:

#### CLK/CLK Inputs:

For applications not requiring the use of the differential input, both CLK and  $\overline{\text{CLK}}$  can be left floating. Though not required, but for additional protection, a 1kW resistor can be tied from CLK to ground.

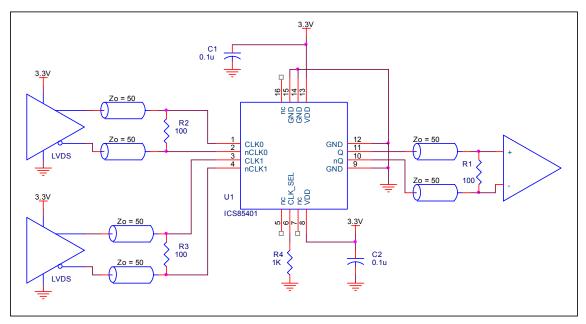

## **Application Schematic Example**

*Figure 3* shows an example of ICS85401 application schematic. This device can accept different types of input signal. In this

example, the input is driven by a LVDS driver. The decoupling capacitor should be located as close as possible to the power pin.

Figure 3. ICS85401 Application Schematic Example

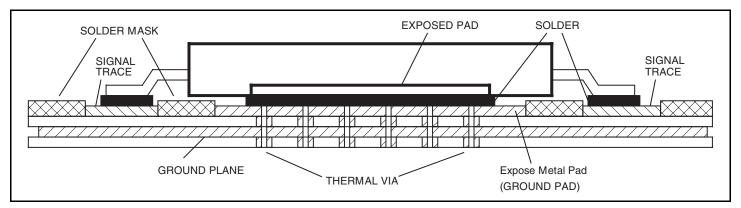

#### **Thermal Release Path**

The expose metal pad provides heat transfer from the device to the P.C. board. The expose metal pad is ground pad connected to ground plane through thermal via. The exposed pad on the device to the exposed metal pad on the PCB is contacted through solder

as shown in *Figure 4*. For further information, please refer to the Application Note on Surface Mount Assembly of Amkor's Thermally /Electrically Enhance Leadframe Base Package, Amkor Technology.

Figure 4. P.C. Board for Exposed Pad Thermal Release Path Example

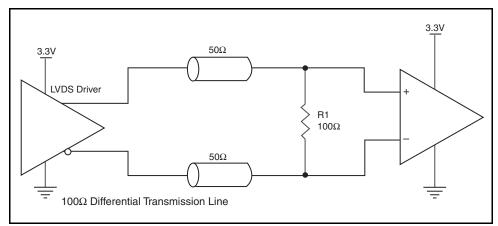

#### **3.3V LVDS Driver Termination**

A general LVDS interface is shown in *Figure 5* In a  $100\Omega$  differential transmission line environment, LVDS drivers require a matched load termination of  $100\Omega$  across near the receiver input. For a

multiple LVDS outputs buffer, if only partial outputs are used, it is recommended to terminate the unused outputs.

Figure 5. Tyical LVDS Driver Termination

## **Power Considerations**

This section provides information on power dissipation and junction temperature for the ICS85401. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the ICS85401 is the sum of the core power plus the analog power plus the power dissipated in the load(s). The following is the power dissipation for  $V_{DD} = 3.3V + 5\% = 3.465V$ , which gives worst case results.

• Power\_MAX = V<sub>DD MAX</sub> \* I<sub>DD MAX</sub> = 3.465V \* 40mA = **138.6mW**

#### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the device. The maximum recommended junction temperature for HiPerClockS devices is 125°C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + T<sub>A</sub>

Tj = Junction Temperature

$\theta_{JA}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

$T_{A}$  = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{JA}$  must be used. Assuming no air flow and a multi-layer board, the appropriate value is 51.5°C/W per Table 6 below.

Therefore, Tj for an ambient temperature of 85°C with all outputs switching is:

$85^{\circ}C + 0.139W * 51.5^{\circ}C/W = 92.2^{\circ}C$ . This is well below the limit of  $125^{\circ}C$ .

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow and the type of board (single layer or multi-layer).

#### Table 6. Thermal Resitance $\theta_{\text{JA}}$ for 16 Lead VFQFN, Forced Convection

| θ <sub>JA</sub> by Velocity                 |          |  |  |  |

|---------------------------------------------|----------|--|--|--|

| Linear Feet per Minute                      | 0        |  |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 51.5°C/W |  |  |  |

#### **Reliability Information**

#### Table 7. $\theta_{\text{JA}}$ vs. Air Flow Table for a 16 Lead VFQFN

| θ <sub>JA</sub> by Velocity                 |          |  |  |  |

|---------------------------------------------|----------|--|--|--|

| Linear Feet per Minute                      | 0        |  |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 51.5°C/W |  |  |  |

#### **Transistor Count**

The transistor count for ICS85401 is: 132

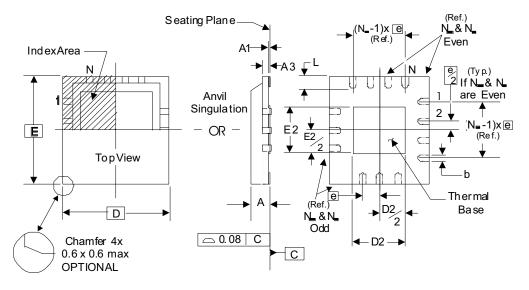

## Package Outline and Package Dimension

#### Package Outline - K Suffix for 16 Lead VFQFN

#### **Table 8. Package Dimensions**

| JEDEC Variation: VEED-2/-4<br>All Dimensions in Millimeters |            |         |  |  |  |

|-------------------------------------------------------------|------------|---------|--|--|--|

| Symbol                                                      | Minimum    | Maximum |  |  |  |

| N                                                           | 16         |         |  |  |  |

| Α                                                           | 0.80       | 1.00    |  |  |  |

| A1                                                          | 0          | 0.05    |  |  |  |

| A3                                                          | 0.25 Ref.  |         |  |  |  |

| b                                                           | 0.18       | 0.30    |  |  |  |

| N <sub>D</sub> & N <sub>E</sub>                             | 4          |         |  |  |  |

| D & E                                                       | 3.00 Basic |         |  |  |  |

| D2 & E2                                                     | 1.00       | 1.80    |  |  |  |

| е                                                           | 0.50 Basic |         |  |  |  |

| L                                                           | 0.30       | 0.50    |  |  |  |

Reference Document: JEDEC Publication 95, MO-220

## **Ordering Information**

#### **Table 9. Ordering Information**

| Part/Order Number | Marking | Package                   | Shipping Packaging | Temperature   |

|-------------------|---------|---------------------------|--------------------|---------------|

| 85401AK           | 401A    | 16 Lead VFQFN             | Tube               | -40°C to 85°C |

| 85401AKT          | 401A    | 16 Lead VFQFN             | 2500 Tape & Reel   | -40°C to 85°C |

| 85401AKLF         | 01AL    | "Lead-Free" 16 Lead VFQFN | Tube               | -40°C to 85°C |

| 85401AKLFT        | 01AL    | "Lead-Free" 16 Lead VFQFN | 2500 Tape & Reel   | -40°C to 85°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial and industrial applications. Any other applications, such as those requiring high reliability or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

## **Revision History Sheet**

| Rev | Table | Page          | Description of Change                                                                                                                                                                                   | Date     |

|-----|-------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| А   |       | 8             | Add Schematic Layout.                                                                                                                                                                                   | 8/23/04  |

| А   | Т8    | 10            | Corrected count in Ordering Information Table.                                                                                                                                                          | 11/17/04 |

| А   |       | 1             | Pin Assignment - corrected label on pin 2.                                                                                                                                                              | 2/22/05  |

| А   | Т8    | 1<br>11       | Features section - added Lead-Free bullet.<br>Ordering Information Table - corrected Shipping Packaging from Tray to<br>Tube, and added Lead-Free part number and note.                                 | 3/14/06  |

| A   | Т9    | 7<br>10<br>13 | Corrected <i>Differential Clock Input Interface.</i><br>Added <i>Power Considerations</i> Section.<br>Ordering Information Table - added Lead-Free marking.<br>Updated format throughout the datasheet. | 3/6/07   |

## Innovate with IDT and accelerate your future networks. Contact:

## www.IDT.com

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited 321 Kingston Road Leatherhead, Surrey KT22 7TU England +44 (0) 1372 363 339 Fax: +44 (0) 1372 378851

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA