# FemtoClock® NG Jitter Attenuator and Clock Synthesizer

# 8V19N408

## DATA SHEET

## **General Description**

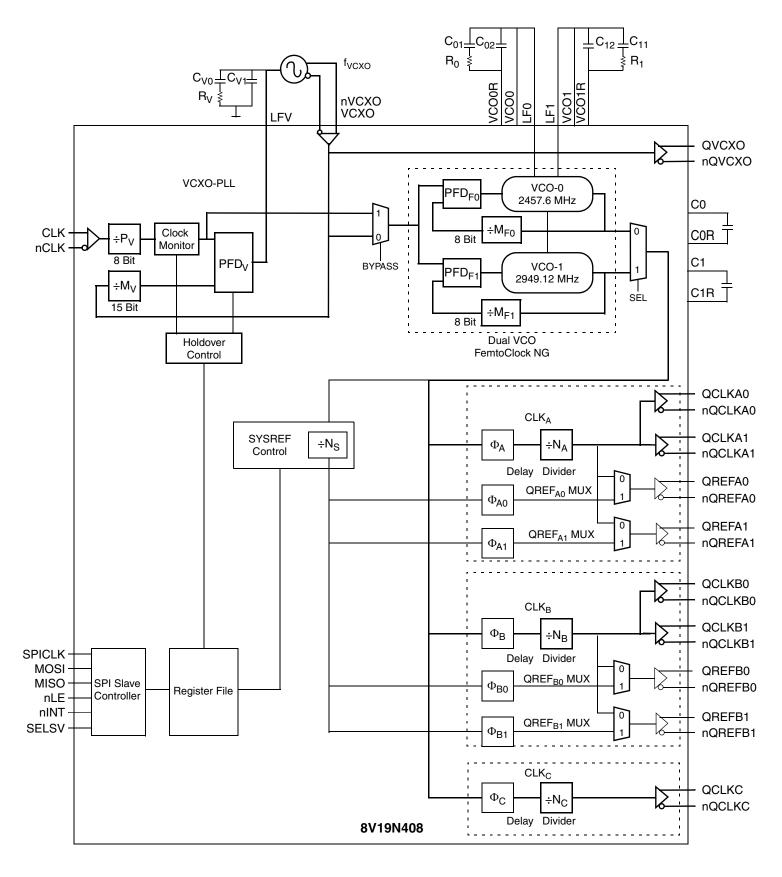

8V19N408 is a fully integrated FemtoClock<sup>®</sup> NG Jitter Attenuator and Clock Synthesizer. The device is a high-performance clock solution for conditioning and frequency/phase management of wireless base station radio equipment boards and is optimized to deliver excellent phase noise performance. The device supports JESD204B subclass 0 and 1 clock implementations. The device is very flexible in programming of the output frequency and phase. A two-stage PLL architecture supports both jitter attenuation and frequency multiplication. The first stage PLL is the jitter attenuator and uses an external VCXO for best possible phase noise characteristics. The second stage PLL lock on the VCXO-PLL output signal and synthesizes the target frequency. For flexibility, the second-stage PLL can use one of two VCOs at 2400MHz - 2500MHz (VCO-0) and 2920MHz - 3000MHz (VCO-1).

The device supports the clock generation of high-frequency clocks from the selected VCO and low-frequency system reference signals (SYSREF). The system reference signals are internally synchronized to the clock signals. Delay functions exist for achieving alignment and controlled phase delay between system reference and clock signals and to align/delay individual output signals. The input is monitored for activity. Short-term hold-over is provided to handle clock input failure scenarios. Auto-lock, individually programmable output frequency dividers and phase adjustment capabilities are added for flexibility. The device is configured through a 4-wire SP serial interface and reports lock and signal loss status in internal registers and optionally via lock detect (nINT) output. The device is packaged in a lead-free (RoHS 6) 72-lead VFQFN package. The extended temperature range supports wireless infrastructure, telecommunication and networking end equipment requirements. The device is a member of the high-performance clock family from IDT.

## Features

- Core timing unit for JESD204B wireless infrastructure clocks

- Fourth generation FemtoClock<sup>®</sup> NG technology

- First stage PLL uses an external VCXO for jitter attenuation

- Second PLL stage facilitates a dual integrated VCO for flexible frequency synthesis

- Integrated VCO frequencies: 2400MHz 2500MHz (VCO-0) and 2920MHz - 3000MHz (VCO-1)

- Five differential configurable LVPECL, LVDS clock outputs with a variable output amplitude

- Four differential LVDS system reference (SYSREF) signal outputs

- Synchronization between clock and system reference signals

- Wide input frequency range supported by 8-bit pre- and 15-bit VCOX-PLL feedback divider

- Output clock frequencies: 2457.6MHz ÷N (VCO-0) and 2949.12MHz ÷N (VCO-1) in wireless infrastructure applications

- Three independent output clock frequency dividers N (range of ÷1 to ÷96)

- Clock output frequency range (VC0-0): (2400MHz 2500MHz) ÷N

- Clock output frequency range (VC0-1): (2920MHz 3000MHz) ÷N

- Phase delay capabilities for alignment/delay for clock and SYSREF signals

- Individual output phase adjustment (Clock): one-period of the selected VCO frequency in 64 steps

- Individual output phase adjustment (SYSREF): approximately half-period of the selected VCO frequency in 8 steps

- Internal, SPI controlled SYSREF pulse generation

- SYSREF frequencies: f<sub>VCO</sub> ÷ N<sub>S</sub> (10 dividers)

- N<sub>S</sub> divider range: ÷64 to ÷2048

- SYSREF (wireless infrastructure): 1.2MHz 46.08MHz

- Clock input compatible with LVPECL, LVDS, LVCMOS signals

- Dedicated power-down features for reducing power consumption

- Input clock monitoring

- · Holdover for temporary loss of input signal scenarios

- Support of output power-down and output disable

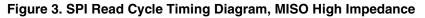

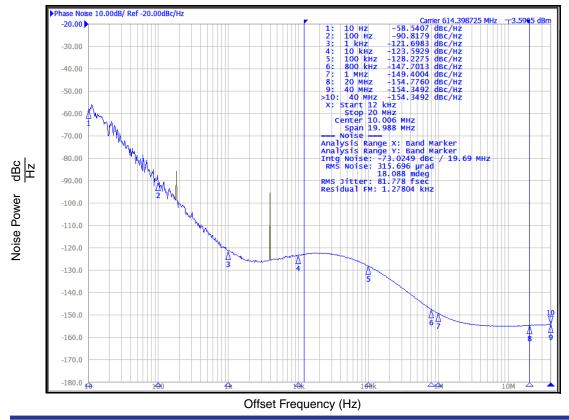

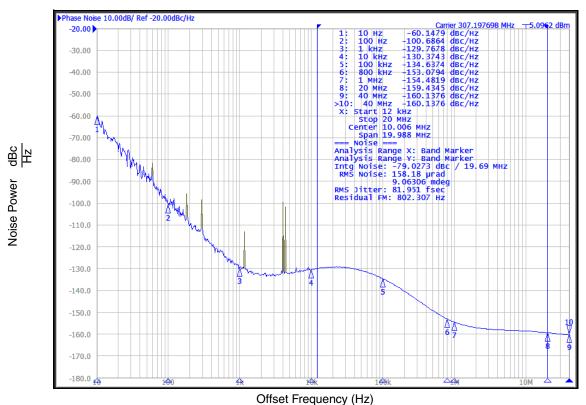

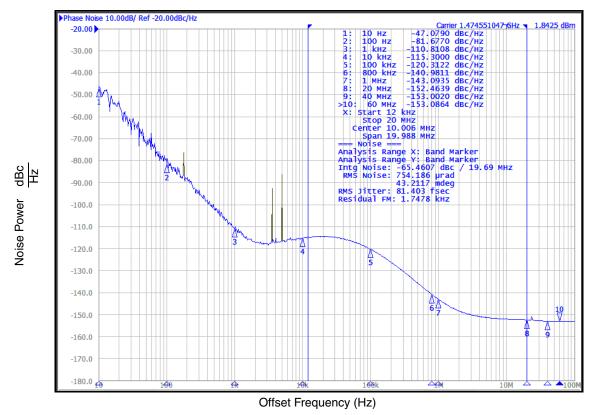

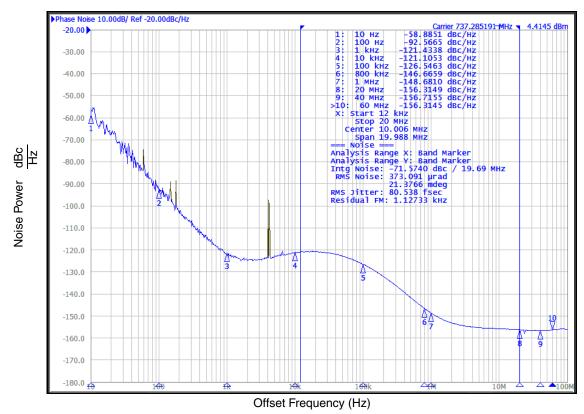

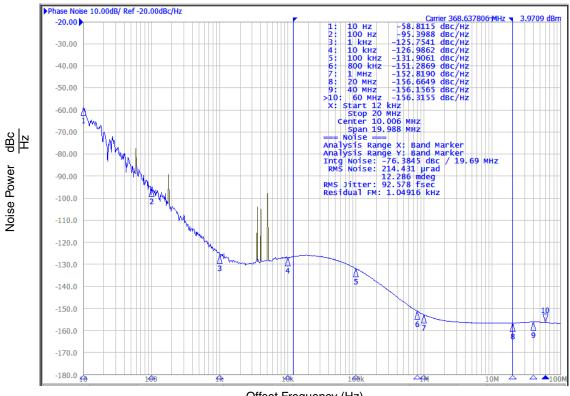

- Typical clock output phase noise at 1228.8MHz:

- 1kHz offset:

-116.9dBc/Hz

10kHz offset:

-118.1dBc/Hz

100kHz offset:

-122.7dBc/Hz

1MHz offset:

-144.7dBc/Hz

- 10MHz offset: -153.5dBc/Hz

- RMS phase noise (12kHz 20MHz): <100fs (target)</li>

- Status conditions with programmable functionality for loss-of-lock and loss-of-reference indication

- Lock detect (nINT) output for status change indication

- LVCMOS/LVTTL compatible SPI serial interface

- 3.3V core and output supply mode

- Control pins support 3.3V I/O logic levels: SPI interface levels support selectable 3.3V/1.8V logic levels

- -40°C to +85°C ambient operating temperature

- Lead-free (RoHS 6) 72-lead VFQFN packaging

## **Block Diagram**

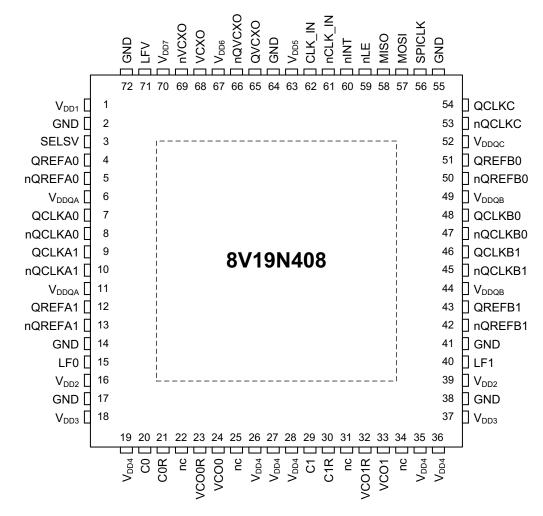

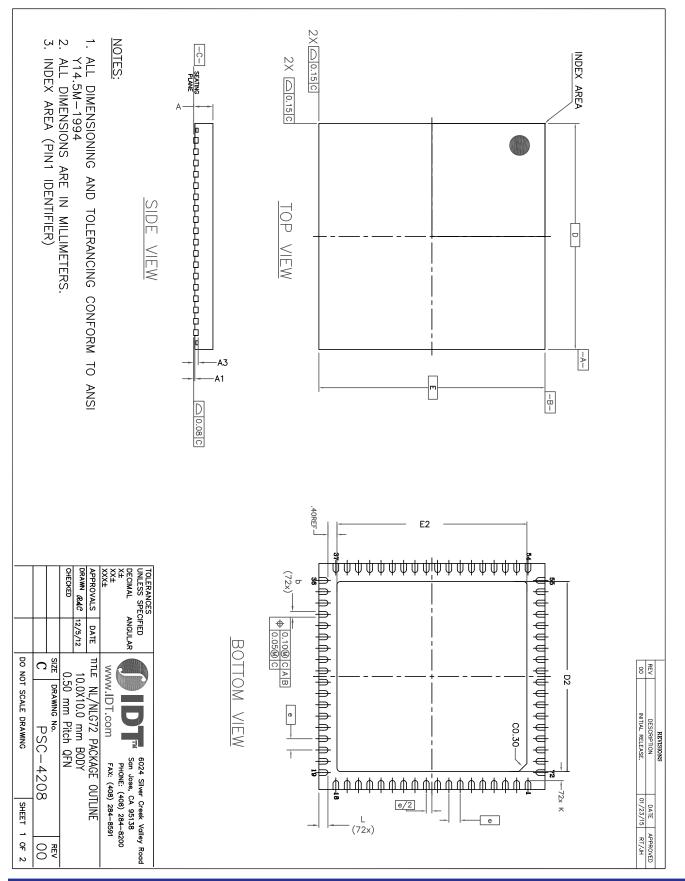

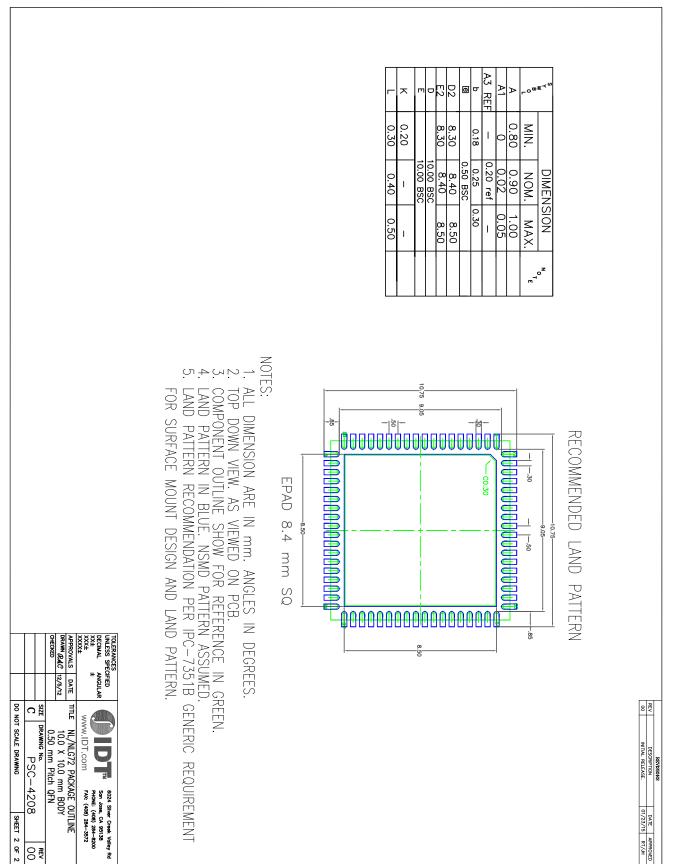

## **Pin Assignment**

72-pin, 10mm x 10mm VFQFN Package

## **Pin Description Table**

## Table 1. Pin Descriptions <sup>1</sup>

| Number | Name              | Туре   |        | Description                                                                                                                              |  |

|--------|-------------------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | V <sub>DD1</sub>  | Power  |        | Positive supply (3.3V) for the VCXO-PLL front end (charge pump and $P_V$ divider).                                                       |  |

| 2      | GND               | Ground |        | Power supply ground. Ground current return path for pin V <sub>DD1</sub> . Connect to board GND (0V).                                    |  |

| 3      | SELSV             | Input  | Pullup | SPI voltage select. 3.3V LVCMOS/LVTTL interface levels                                                                                   |  |

| 4      | QREFA0            | Output |        | Differential SYSREF/clock output A0. LVDS style for SYSREF operation, Configurable LVPECL, LVDS style and amplitude for clock operation. |  |

| 5      | nQREFA0           | Output |        |                                                                                                                                          |  |

| 6      | V <sub>DDQA</sub> | Power  |        | Output supply (3.3V) for the QCLKAn and QREFAn outputs.                                                                                  |  |

| 7      | QCLKA0            | Output |        | <ul> <li>Differential clock output A0. Configurable LVPECL, LVDS style and amplitude.</li> </ul>                                         |  |

| 8      | nQCLKA0           | Output |        |                                                                                                                                          |  |

## Table 1. Pin Descriptions (Continued)<sup>1</sup>

| Number | Name              | Тур    | Description                                                                                                                             |  |

|--------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| 9      | QCLKA1            | Output | Differential alask output A1. Configurable LV/DECL_LV/DE at the and amplitude                                                           |  |

| 10     | nQCLKA1           | Output | Differential clock output A1. Configurable LVPECL, LVDS style and amplitude.                                                            |  |

| 11     | V <sub>DDQA</sub> | Power  | Output supply (3.3V) for the QCLKAn and QREFAn outputs.                                                                                 |  |

| 12     | QREFA1            | Output | Differential SYSREF/clock output A1. LVDS style for SYSREF operation, Configurable                                                      |  |

| 13     | nQREFA1           | Output | LVPECL, LVDS style and amplitude for clock operation.                                                                                   |  |

| 14     | GND               | Power  | Power supply ground. Ground return path for the V <sub>DD2</sub> pins. Connect to board GND (0V).                                       |  |

| 15     | LF0               | Output | Loop filter/charge pump output for the FemtoClock NG PLL, VCO-0. Connect LF0 and VCO0 (pin 24) to the external loop filter components.  |  |

| 16     | V <sub>DD2</sub>  | Power  | Positive supply (3.3V) for the LF0 and LF1 outputs.                                                                                     |  |

| 17     | GND               | Power  | Power supply ground. Ground return path for the $V_{DD3}$ pins. Connect to board GND (0V).                                              |  |

| 18     | V <sub>DD3</sub>  | Power  | Positive supply (3.3V) for the internal PLLs.                                                                                           |  |

| 19     | V <sub>DD4</sub>  | Power  | Positive supply (3.3V) for the internal oscillators VCO-1 and VCO-2.                                                                    |  |

| 20     | C0                | Analog | Regulator 0 bypass capacitor. Use a $4.7\mu$ F capacitor between the C0 and C0R pins.                                                   |  |

| 21     | C0R               | Analog |                                                                                                                                         |  |

| 22     | nc                | Unused | No internal connection. Do not use.                                                                                                     |  |

| 23     | VCO0R             | Analog | Ground return path pin for the VCO-0 loop filter.                                                                                       |  |

| 24     | VCO0              | Analog | Loop filter control voltage input to VCO0.                                                                                              |  |

| 25     | nc                | Unused | No internal connection. Do not use.                                                                                                     |  |

| 26     | V <sub>DD4</sub>  | Power  | Positive supply (3.3V) for the internal VCO-1 and VCO-2.                                                                                |  |

| 27     | V <sub>DD4</sub>  | Power  | Positive supply (3.3V) for the internal VCO-1 and VCO-2.                                                                                |  |

| 28     | V <sub>DD4</sub>  | Power  | Positive supply (3.3V) for the internal VCO-1 and VCO-2.                                                                                |  |

| 29     | C1                | Analog | Regulator 1 bypass capacitor. Use a $4.7\mu$ F capacitor between the C1 and C1R pins.                                                   |  |

| 30     | C1R               | Analog | megulator i bypass capacitor. Ose a 4.7 µr capacitor between the CT and CTH pins.                                                       |  |

| 31     | nc                | Unused | No internal connection. Do not use.                                                                                                     |  |

| 32     | VCO1R             | Analog | Ground return path pin for the VCO-1 loop filter.                                                                                       |  |

| 33     | VCO1              | Analog | Loop filter control voltage input to VCO-1                                                                                              |  |

| 34     | nc                | Unused | No internal connection. Do not use.                                                                                                     |  |

| 35     | V <sub>DD4</sub>  | Power  | Positive supply (3.3V) for the internal oscillators VCO-1 and VCO-2.                                                                    |  |

| 36     | V <sub>DD4</sub>  | Power  | Positive supply (3.3V) for the internal oscillators VCO-1 and VCO-2.                                                                    |  |

| 37     | V <sub>DD3</sub>  | Power  | Positive supply (3.3V) for the internal PLLs.                                                                                           |  |

| 38     | GND               | Power  | Power supply ground. Ground return path for the V <sub>DD3</sub> pins. Connect to board GND (0V).                                       |  |

| 39     | V <sub>DD2</sub>  | Power  | Positive supply (3.3V) for the LF0 and LF1 outputs.                                                                                     |  |

| 40     | LF1               | Output | Loop filter/charge pump output for the FemtoClock NG PLL, VCO-1. Connect LF1 and VCO-1 (pin 33) to the external loop filter components. |  |

| 41     | GND               | Power  | Power supply ground. Ground return path for the $V_{DD2}$ pins. Connect to board GND (0V).                                              |  |

| 42     | nQREFB1           | Output | Differential SYSREF/clock output B1. LVDS style for SYSREF operation, Configurable                                                      |  |

| 43     | QREFB1            | Output | LVPECL, LVDS style and amplitude for clock operation.                                                                                   |  |

| 44     | V <sub>DDQB</sub> | Power  | Output supply (3.3V) for the QREFBn and QCLKBn outputs.                                                                                 |  |

## Table 1. Pin Descriptions (Continued)<sup>1</sup>

| Number | Name              | Т      | уре                  | Description                                                                                                                                                                  |  |

|--------|-------------------|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 45     | nQCLKB1           | Output |                      | <ul> <li>Differential clock output B1. Configurable LVPECL, LVDS style and amplitude.</li> </ul>                                                                             |  |

| 46     | QCLKB1            | Output |                      |                                                                                                                                                                              |  |

| 47     | nQCLKB0           | Output |                      |                                                                                                                                                                              |  |

| 48     | QCLKB0            | Output |                      | Differential clock output B0. Configurable LVPECL, LVDS style and amplitude.                                                                                                 |  |

| 49     | V <sub>DDQB</sub> | Power  |                      | Output supply (3.3V) for the QREFBn and QCLKBn outputs.                                                                                                                      |  |

| 50     | nQREFB0           | Output |                      | Differential SYSREF/clock output B0. LVDS style for SYSREF operation, Configurable                                                                                           |  |

| 51     | QREFB0            | Output |                      | LVPECL, LVDS style and amplitude for clock operation.                                                                                                                        |  |

| 52     | V <sub>DDQC</sub> | Power  |                      | Output supply (3.3V) for the QCLKC output.                                                                                                                                   |  |

| 53     | nQCLKC            | Output |                      |                                                                                                                                                                              |  |

| 54     | QCLKC             | Output |                      | Differential clock output C. Configurable LVPECL, LVDS style and amplitude.                                                                                                  |  |

| 55     | GND               | Power  |                      | Power supply ground. Ground return path for the V <sub>DD5</sub> pins. Connect to board GND (0V).                                                                            |  |

| 56     | SPICLK            | Input  | Pulldown             | Serial Control Port SPI Clock input. 3.3V/1.8V selectable LVCMOS/LVTTL interface levels.                                                                                     |  |

| 57     | MOSI              | Input  | Pulldown             | Serial Control Port SPI Data input. 3.3V/1.8V selectable LVCMOS/LVTTL interface levels.                                                                                      |  |

| 58     | MISO              | Output |                      | Serial Control Port SPI Data output. 3.3V/1.8V selectable LVCMOS/LVTTL interface levels.                                                                                     |  |

| 59     | nLE               | Input  | Pulldown             | Serial Control Port SPI Load Enable input.3.3V/1.8V selectable LVCMOS/LVTTL interface levels.                                                                                |  |

| 60     | nINT              | Output |                      | Status Output pin for signaling fault conditions. 3.3V/1.8V selectable LVCMOS/LVTTL interface levels.                                                                        |  |

| 61     | nCLK_IN           | Input  | Pullup /<br>Pulldown | Device clock inverting and non-inverting differential clock input. Inverting input is biased to                                                                              |  |

| 62     | CLK_IN            | Input  | Pulldown             | 1.2V by default when left floating. Compatible with LVPECL, LVDS and LVCMOS signals.                                                                                         |  |

| 63     | V <sub>DD5</sub>  | Power  |                      | Positive supply (3.3V) for the SPI interface and the CLK, nCLK input.                                                                                                        |  |

| 64     | GND               | Power  |                      | Power supply ground. Ground return path for the V <sub>DD6</sub> pins. Connect to board GND (0V).                                                                            |  |

| 65     | QVCXO             | Output |                      |                                                                                                                                                                              |  |

| 66     | nQVCXO            | Output |                      | Differential VCXO-PLL clock output. Configurable LVPECL, LVDS style and amplitude.                                                                                           |  |

| 67     | V <sub>DD6</sub>  | Power  |                      | Positive supply (3.3V) for the QVCXO output and VCXO-PLL.                                                                                                                    |  |

| 68     | VCXO              | Input  | Pulldown             | VOVO non investiga and investiga differential plack insut lawating input is bigged to 1.0V by                                                                                |  |

| 69     | nVCXO             | Input  | Pullup /<br>Pulldown | VCXO non-inverting and inverting differential clock input. Inverting input is biased to 1.2V by default when left floating. Compatible with LVPECL, LVDS and LVCMOS signals. |  |

| 70     | V <sub>DD7</sub>  | Power  |                      | Positive supply (3.3V) for the VCXO-PLL charge pump output.                                                                                                                  |  |

| 71     | LFV               | Output |                      | VCXO-PLL charge pump output. Connect to the loop filter for the external VCXO.                                                                                               |  |

| 72     | GND               | Power  |                      | Power supply ground. Ground return path for the V <sub>DD6</sub> pins. Connect to board GND (0V).                                                                            |  |

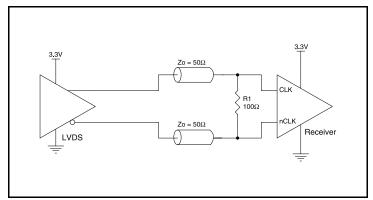

|        | Exposed pad       | Power  |                      | Power supply ground. Ground return path for all differential outputs. Connect to board GND (0V) and to a thermally low resistive path on the board.                          |  |

NOTE 1. Pulldown and Pullup refer to internal input resistors. See Table 4B, Input/Output Characteristics, for typical values.

# **Principles of Operation**

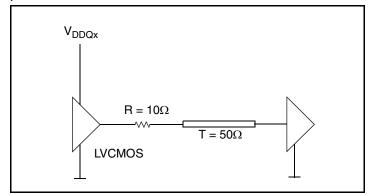

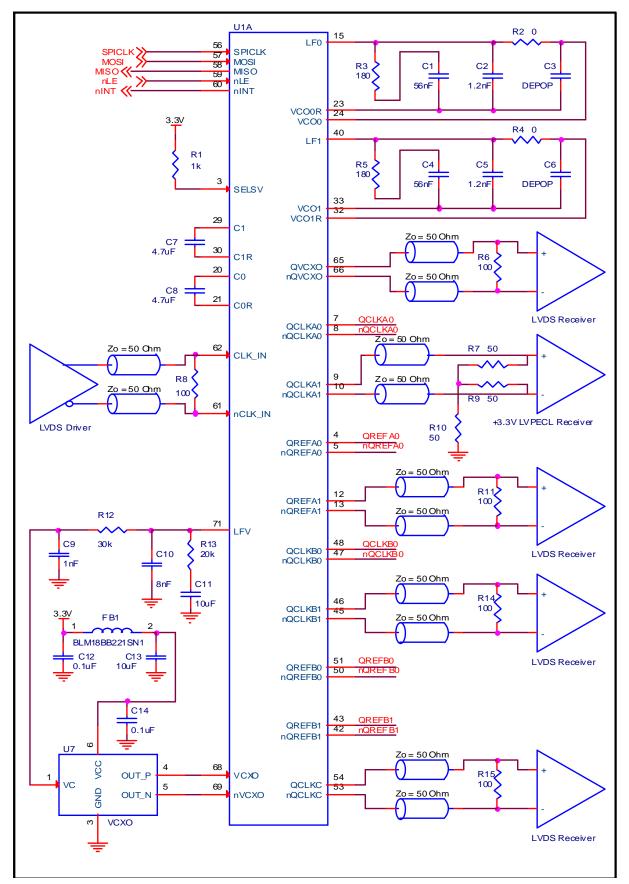

The 8V19N408 is a dual stage PLL clock synthesizer. The first stage is the VCXO-PLL that uses an external VCXO device as a high-quality oscillator and provides jitter attenuation to the input clock signal. The second stage is a FemtoClock NG synthesizer PLL with a dual VCO for flexible output frequency generation. By configuring the 8-bit integer pre-scaler P<sub>V</sub> and the 15-bit integer feedback divider M<sub>V</sub>, the VCXO-PLL can accommodate a wide range of input and VCXO frequencies.The input (P<sub>V</sub>) and VCXO-PLL feedback (M<sub>V</sub>) dividers must be set to match the frequency of the phase detector (PFD<sub>F</sub>). The VCO of the second stage PLL is designed to support center frequencies within the specified VCO range. Each VCO has its own PLL feedback divider (M<sub>F0</sub> or M<sub>F1</sub>) which must be set to match the VCXO-PLL frequency (first loop) to its center frequency range. Table 2A shows the supported input, feedback and output dividers.

The output signal of the second stage FemtoClock NG PLL is then distributed to the individual clock dividers, delay stages and outputs. The device has five clock outputs (QCLK), organized in the three output banks A, B and C. Each output bank has an individual integer clock divider N for clock frequency generation. See Table 2E for a list of supported output frequencies.

The jitter-attenuated clock signal from the VCXO-PLL is routed to the QVCXO output. The phase noise of this output corresponds to the quality of the used external VCXO.

The devices supports the generation of up to four non-periodic or periodic synchronization signals (SYSREF). The SYSREF signals are generated internally from the VCO clock source, therefore the SYSREF outputs (QREF) are synchronous to the QCLK outputs. The SYSREF signals have a pulse repetition rate of  $f_{VCO} \div N_S$  (the  $N_S$  divider can be configured to one of 10 frequency dividers. See Table 2A).

Each QCLK output bank signal can be individually phase-delayed to achieve a specific phase alignment relative to each other and relative to any QREF (SYSREF) clock output. The four QREF outputs can be individually re-configured as device clocks for additional flexibility.

In an alternatively operation mode, the VCXO input stage can by bypassed for applications with multiple 8V19N408 devices locking to a common source clock. In such an application, the first device acts as a jitter attenuator and the second device acts as a low phase noise frequency synthesizer. The first device provides the input signal to the second 8V19N408 at e.g. 122.88MHz. The second 8V19N408 is used in VCXO-bypass mode and its second stage PLL locks to the jitter-attenuated clock input signal of the first device. The device is configured through an SPI interface. Configurations are established by setting or resetting internal bits, which are organized in eight 32-bit words. The SPI interface also supports read-back of configuration settings.

#### Table 2A. PLL Divider Settings

| PLL Divider                                                           | Pango                                     | Operation                                                      |

|-----------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------|

| PLL Divider                                                           | Range                                     | Operation                                                      |

| Prescaler $P_V$                                                       | ÷1 to ÷255<br>(8 bit)                     | Input Clock Frequency:                                         |

| VCXO-PLL<br>Feedback Divider<br>M <sub>V</sub>                        | ÷4 to ÷32767<br>(15 bit)                  | $f_{CLK} = f_{VCXO} \cdot \frac{P_V}{M_V}$                     |

| FemtoClock NG<br>Feedback Divider<br>M <sub>F0,</sub> M <sub>F1</sub> | ÷8 to ÷255<br>(8 bit)                     | VCXO Frequency:<br>$f_{VCXO} = \frac{f_{VCO}}{M_{F0(1)}}$      |

| Output Divider N<br>(N <sub>A</sub> to N <sub>C</sub> )               | ÷1 to ÷96<br>(18 discrete<br>dividers)    | Output Frequency<br>$f_{OUT} = \frac{f_{VCO}}{N_{A, B, C}}$    |

| SYSREF Divider<br>N <sub>S</sub>                                      | ÷64 to ÷2048<br>(10 discrete<br>dividers) | SYSREF<br>Frequency/Rate<br>$f_{SYSREF} = \frac{f_{VCO}}{N_S}$ |

|                                | FemtoClock NG PLL Divider Settings |

|--------------------------------|------------------------------------|

| (f <sub>VCO</sub> = 2457.6MHz) | -                                  |

| VCXO Frequency (MHz) | M <sub>F0</sub> Divider Settings |

|----------------------|----------------------------------|

| 153.6                | ÷16                              |

| 122.88               | ÷20                              |

| 76.8                 | ÷32                              |

| 61.44                | ÷40                              |

| 38.4                 | ÷64                              |

| 30.72                | ÷80                              |

NOTE 1. Example list of VCXO frequencies for VCO frequency of 2457.6MHz. The M<sub>F0</sub> divider has a range from M<sub>F0</sub> = 8 to M<sub>F0</sub> = 255. f<sub>VCXO</sub> = 2457.6  $\div$  M<sub>F0</sub>. See Table 3C for register configuration.

#### Table 2C. VCXO-PLL Bypass Settings<sup>1</sup>

| BYPASS | Operation                                                                                                                                                                                        |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0      | VCXO-PLL operation.                                                                                                                                                                              |  |

| 1      | VCXO-PLL bypassed. The reference clock for<br>the 2nd PLL is the input clock. Clock<br>monitoring is disabled. No jitter attenuation.<br>No external VCXO component and loop filter<br>required. |  |

NOTE 1. See Table 3I for register configuration.

## **Input Reference**

The 8V19N408 is designed for high-reliability applications and supports input frequency monitoring. If no activity has been detected on any clock input within a fixed time period, then the reference is considered to be invalid and an internal status flag is set. This is a loss of signal event (LOS) and sets the STAT0 status bit. See also Table 2Q for an overview of supported status functions. The VCXO-PLL provides a temporary hold-over in LOS situations.The device enters a hold-over state in any of the following cases:

- the clock signal is invalid (LOS)

- the HOLD bit is set to logic 1 (hold-over) (See Table 2D)

#### Table 2D. Holdover<sup>1</sup>

| HOLD | Operation                                                                                    |

|------|----------------------------------------------------------------------------------------------|

| 0    | Normal operation                                                                             |

| 1    | VCXO-PLL is set to holdover. The control voltage of the external VCXO is set to $V_{DD}/2$ . |

NOTE 1. See Table 3I for register configuration.

## VCXO-PLL

The charge pump current of the PLL is configurable in small steps by writing the desired charge pump current amount into a SPI register. 64 steps of  $20\mu$ A are available, the range pump current range is  $0\mu$ A to 1.26mA. See CPV[5:0], Table 3I for available settings.

## **Clock Outputs**

#### **Output Divider**

From the VCO frequency the three independent clock output dividers  $N_A$ ,  $N_B$  and  $N_C$  scale the frequency down to the desired clock output frequencies. (see Table 2E). The output dividers  $N_A$ ,  $N_B$  and  $N_C$  can be set via internal registers. The configuration and re-configuration of any of the output dividers requires the SPI write sequence described in Section, "Clock Output Divider Reset Sequence, (Sequence S1)" on page 12.

| Output Divider N <sub>A</sub> , N <sub>B</sub> , N <sub>C</sub> | Output Clock Frequency |

|-----------------------------------------------------------------|------------------------|

| ÷1                                                              | VCO Frequency ÷1       |

| ÷2                                                              | VCO Frequency ÷2       |

| ÷3                                                              | VCO Frequency ÷3       |

| ÷4                                                              | VCO Frequency ÷4       |

| ÷5                                                              | VCO Frequency ÷5       |

| ÷6                                                              | VCO Frequency ÷6       |

| ÷8                                                              | VCO Frequency ÷8       |

| ÷10                                                             | VCO Frequency ÷10      |

| ÷12                                                             | VCO Frequency ÷12      |

| ÷16                                                             | VCO Frequency ÷16      |

| ÷20                                                             | VCO Frequency ÷20      |

| ÷24                                                             | VCO Frequency ÷24      |

| ÷32                                                             | VCO Frequency ÷32      |

| ÷40                                                             | VCO Frequency ÷40      |

| ÷48                                                             | VCO Frequency ÷48      |

| ÷64                                                             | VCO Frequency ÷64      |

| ÷80                                                             | VCO Frequency ÷80      |

| ÷96                                                             | VCO Frequency ÷96      |

Table 2E. N<sub>A, B, C</sub> Frequency Divider Settings<sup>1</sup>

NOTE 1. Individual setting for each output bank A, B and C. See Table 3E for register configuration.

## Table 2F. N<sub>A, B, C</sub> Example Frequency Divider Settings

| Output Divider                                   | Output Clock Frequency in MHz for a VCO<br>Frequency of: |                      |                         |  |

|--------------------------------------------------|----------------------------------------------------------|----------------------|-------------------------|--|

| N <sub>A</sub> , N <sub>B</sub> , N <sub>C</sub> | 2457.6MHz <sup>1</sup>                                   | 2500MHz <sup>1</sup> | 2949.12MHz <sup>2</sup> |  |

| ÷1                                               | 2457.600                                                 | 2500.000             | 2949.120                |  |

| ÷2                                               | 1228.800                                                 | 1250.000             | 1474.560                |  |

| ÷3                                               |                                                          |                      | 983.04                  |  |

| ÷4                                               | 614.400                                                  | 625.000              | 737.280                 |  |

| ÷5                                               | 491.520                                                  | 500.000              | 589.824                 |  |

| ÷6                                               |                                                          |                      | 491.52                  |  |

| ÷8                                               | 307.200                                                  | 312.500              | 368.640                 |  |

| ÷10                                              | 245.760                                                  | 250.000              | 294.912                 |  |

| ÷12                                              |                                                          |                      | 245.76                  |  |

| ÷16                                              | 153.600                                                  | 156.250              | 184.320                 |  |

| ÷20                                              | 122.880                                                  | 125.000              | 147.456                 |  |

| ÷24                                              |                                                          |                      | 722.88                  |  |

| ÷32                                              | 76.800                                                   | 78.125               | 92.160                  |  |

| ÷40                                              | 61.440                                                   | 62.500               |                         |  |

| ÷48                                              | 51.2                                                     |                      | 61.44                   |  |

| ÷64                                              | 38.4                                                     |                      |                         |  |

| ÷80                                              | 30.720                                                   | 31.250               |                         |  |

| ÷96                                              | 25.600                                                   |                      | 30.720                  |  |

NOTE 1. VCO-0

NOTE 2. VCO-1

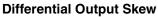

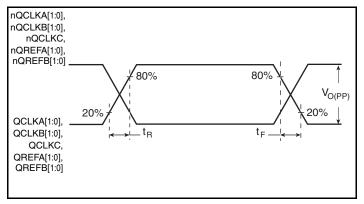

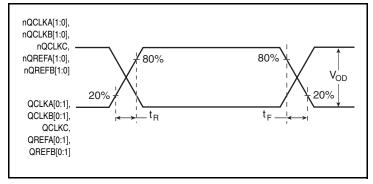

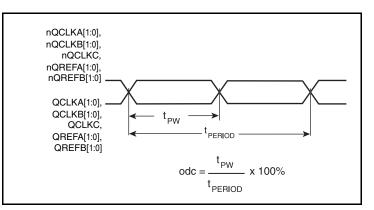

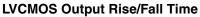

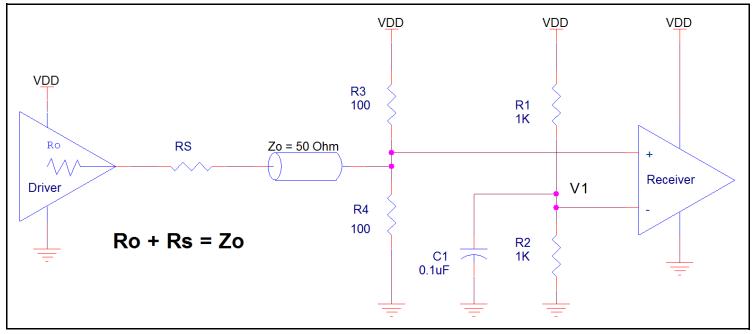

#### **Output Format**

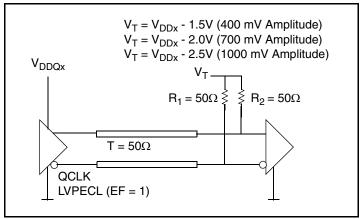

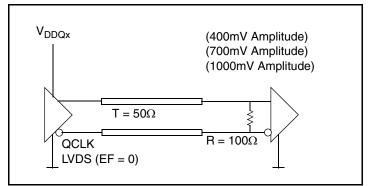

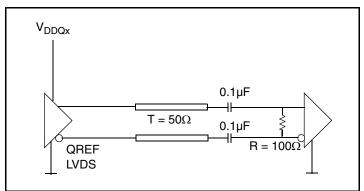

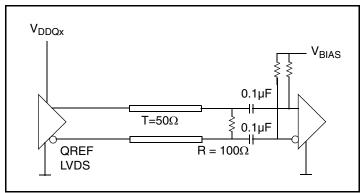

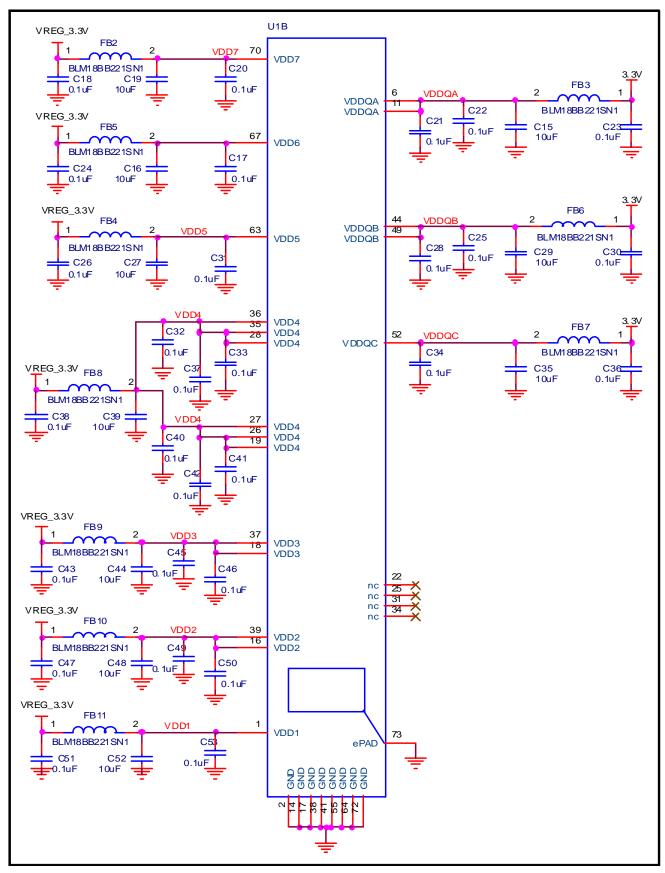

All differential device clock outputs (QCLK) can be individually configured in format (LVPECL, LVDS), output amplitude, state (enable, disable) and power state (power on, power off). Outputs in LVPECL format are terminated to a termination voltage  $V_T$  according to the configured output amplitude. Outputs in LVDS format are terminated  $100\Omega$  across the terminals. The output format of the 8V19N408 was designed for flexibility in amplitude control. The output offset voltage changes with amplitude. For strict LVDS compliance, it is recommended to AC-couple the LVDS outputs and re-bias to  $V_{BIAS} = 1.25V$ . The lowest output amplitude settings correspond with the least amount of power consumed. Unused clock outputs may not be terminated externally to save current consumption. The QCLK outputs LVPECL, LVDS format configuration is shown in Table 2G. For LVPECL format, set EF = 1 and terminate the LVPECL output pair  $50\Omega$  to the specified recommended termination voltage shown in Table 2G. For LVDS format, set EF = 0 and terminate the output pair 100 $\Omega$  across the QCLK, nQCLK terminals. Independent on the state of the EF bit, the A[1:0] bits control the output amplitude of QCLK outputs.

## Table 2G. QCLK Output Control<sup>1</sup>

| EF | <b>A</b> 1      | <b>A</b> 0 | Output Operation                 | Output Termination                   |  |  |

|----|-----------------|------------|----------------------------------|--------------------------------------|--|--|

|    | LVPECL (EF = 1) |            |                                  |                                      |  |  |

| 1  | 0               | 0          | Power off                        | Do not terminate                     |  |  |

| 1  | 0               | 1          | 400mV                            | 50 $\Omega$ to V_{DDx} - 1.5V        |  |  |

| 1  | 1               | 0          | 700mV                            | 50 $\Omega$ to V <sub>DDx</sub> - 2V |  |  |

| 1  | 1               | 1          | 1000mV, f <sub>OUT</sub> >500MHz | 50 $\Omega$ to V_{DDx} - 2.5V        |  |  |

|    | LVDS (EF = 0)   |            |                                  |                                      |  |  |

| 0  | 0               | 0          | Power off                        | 100Ω across                          |  |  |

| 0  | 0               | 1          | 400mV                            | 100Ω across                          |  |  |

| 0  | 1               | 0          | 700mV                            | 100Ω across                          |  |  |

| 0  | 1               | 1          | 1000mV, f <sub>OUT</sub> >500MHz | $100\Omega$ across                   |  |  |

NOTE 1. Individual setting for each output QCLKA[1:0], QCLKB[1:0] and QCLKC.

Each QCLK output can be individually disabled to the logic low state by clearing the corresponding OUTEN bit. See Table 2H for details.

#### Table 2H. QCLK Output Enable<sup>1</sup>

| OUTEN | Output Operation                    |  |

|-------|-------------------------------------|--|

| 0     | QCLK is disabled in logic low state |  |

| 1     | QCLK is enabled                     |  |

NOTE 1. Individual setting for each output QCLKA[1:0], QCLKB[1:0] and QCLKC.

**Clock channel power**: Setting the corresponding nPOWER bit will power-down the N divider and delay stage of an clock output channel to save operating currents in situations of an output channel not used for frequency generation.

#### Table 2I. Clock Channel Power Operation<sup>1</sup>

| nPOWER | Clock Channel                                 |  |  |  |  |  |  |

|--------|-----------------------------------------------|--|--|--|--|--|--|

| 0      | Divider N and delay stage $\Phi$ powered up   |  |  |  |  |  |  |

| 1      | Divider N and delay stage $\Phi$ powered down |  |  |  |  |  |  |

|        |                                               |  |  |  |  |  |  |

NOTE 1. Individual setting for each clock channel A, B and C (dividers N<sub>A</sub>, N<sub>B</sub>, N<sub>C</sub> and clock delay stages  $\Phi_A$ ,  $\Phi_B$ ,  $\Phi_C$ ). See Table 3E for register configuration.

## SYSREF Outputs (QREF)

Each QREF output can be individually configured as SYSREF output or as clock output by setting the corresponding MUX bit. For JESD204B-operation, configure QREF outputs as SYSREF outputs. See Table 2J for details

#### Table 2J. QREF Output Configuration<sup>1</sup>

| QREF MUX | Operation                                                                                                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Clock Mode <ul> <li>Frequency divided by N</li> </ul>                                                                                                                                                                                      |

| 0        | Output amplitude: use any setting in<br>Table 2K                                                                                                                                                                                           |

|          | <ul> <li>Set nPOWER = 1 to power down the corresponding (unused) SYSREF delay stage Φ<sub>A0-B1</sub></li> <li>Set OUTEN = 1 (output enable)</li> </ul>                                                                                    |

| 1        | <ul> <li>SYSREF Mode (JESD204B)</li> <li>Set nPOWER = 0 to power up the corresponding SYSREF delay stage Φ<sub>A0-B1</sub></li> <li>Set the QREF output amplitude to 400mV (A[1:0] = 01)</li> <li>Set OUTEN = 1 (output enable)</li> </ul> |

NOTE 1. Individual setting for each output QREF output QREFA[1:0], QREFB[1:0].

**Clock mode (MUX = 0):** QREF outputs operate as additional clock outputs, increasing the available clock signal fanout. In this mode, the output amplitude can be configured to one of three different values. In clock mode, the output frequency of is controlled by the N divider of the corresponding device clock output. For instance, the divider N<sub>A</sub> controls the output frequency of both QCLKA0, A1 and QREFA0, A1. The QREF output delay setting is controlled by the delay circuit  $\Phi$  of the associated clock output QCLK. See Table 2K for details.

#### Table 2K. QREF Output Control (MUX = 0)

| OUTEN | A[1] | A[0] | Output Operation                               |  |  |  |

|-------|------|------|------------------------------------------------|--|--|--|

| х     | 0    | 0    | QREF output buffer powered-<br>down            |  |  |  |

| 0     | 0    | 1    |                                                |  |  |  |

| 0     | 1    | 0    | QREF disabled in logic low state               |  |  |  |

| 0     | 1    | 1    |                                                |  |  |  |

| 1     | 0    | 1    | V <sub>O, PP</sub> = 400mV                     |  |  |  |

| 1     | 1    | 0    | V <sub>O, PP</sub> = 700mV                     |  |  |  |

| 1     | 1    | 1    | $V_{O, PP}$ = 1000mV, f <sub>OUT</sub> >500MHz |  |  |  |

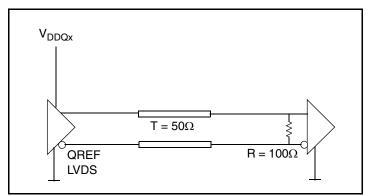

JESD204B (SYSREF) Operation (MUX = 1): The QREF outputs support the generation of SYSREF pulses in JESD204B applications. The delay stages can be used to establish repeatable phase relationships of QCLK outputs to each other and to the SYREF signals QREF: the QCLK delay stages support 64 steps of delay and the QREF outputs support additional 8 steps of fine-delay.

See Table 2P and Section, "SYSREF Generation" on page 11. Each individual QREF output can also be disabled into logic low state by clearing the OUTEN bit. For SYSREF operation, the QREF outputs should be configured as shown in Table 2L:

### Table 2L. QREF Output Control<sup>1</sup> (SYSREF, MUX = 1)

| <b>A</b> 1 | <b>A</b> 0 | Output Operation           | Output Termination  |

|------------|------------|----------------------------|---------------------|

| 0          | 0          | Power off                  | $100\Omega$ across  |

| 0          | 1          | V <sub>O, PP</sub> = 400mV | 100 $\Omega$ across |

NOTE 1. Individual setting for each output QREF output QREFA[1:0], QREFB[1:0].

**SYSREF power down features**: Setting the corresponding nPOWER bit will power-down the  $\Phi$  delay circuit. A QREF output buffer can be powered-down by setting A[1:0] = 00. The QREF outputs automatically power-down when SRO = 0 (counted pulse mode) and no SYSREF pulses are generated. QREF outputs will power up automatically for SYSREF pulse generation, controlled by the SYSREF generation sequence (see Section, "QREF Phase Delay and SYSREF Synchronization Sequence, (Sequence S2)" on page 12). Applications not using a QREF output should power the delay circuit down (nPOWER = 1) and also power off the output buffer (set MUX = 0, A[1:0] = 00). Powered-down output buffers save operating current, even with presence of external termination. See Table 2M and Table 2K for details.

## Synchronization and Phase Alignment

#### **QCLK Outputs**

The 8V19N408 has output dividers which generate the supported clock frequencies at outputs QCLK synchronously. After the SPI controlled synchronization of output dividers, all output clocks QCLK will be in alignment with each other. Outputs which select different output dividers are aligned on the incident rising edge.

#### **QCLK Delay Circuits**

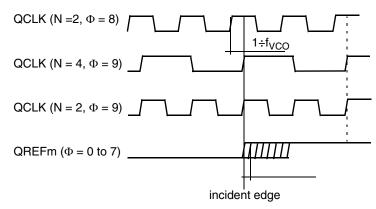

The clock outputs QCLK have an individual delay element ( $\Phi$ ) to advance/delay its clock output phase of an clock output bank if an offset is desired on a particular output. The delay circuit operates by inserting a delay into the clock signal coming out of the individual QCLK bank outputs by a discrete number of one clock period of the FemtoClock NG VCO. The user may select a number of steps to insert via the appropriate register. Each of the two output banks supports 64 steps of phase delay (the delay unit is a function of the internal VCO frequency. See Table 2O). For fine delay, the SYSREF outputs have individual phase delay circuits, each delay circuit supports eight steps. See Table 2P.

The delay capabilities of the clock and SYSREF outputs can be used to establish a specific, repeatable phase relationship between any QCLK and QREF outputs. QREF outputs that are configured with the same delay value are aligned to each other.

## Table 2M. $\Phi_A, \Phi_B, \Phi_C$ QCLK Phase Delay<sup>1</sup>

|            | Phase Delay ( $\Phi$ ) in ns | Phase Delay ( $\Phi$ ) in ns for a VCO Frequency of: |                      |                             |  |  |  |  |

|------------|------------------------------|------------------------------------------------------|----------------------|-----------------------------|--|--|--|--|

| Delay Unit | $\frac{1}{f_{VCO}}$          | 2457.6MHz <sup>2</sup>                               | 2500MHz <sup>2</sup> | 2949.12MHz <sup>3</sup>     |  |  |  |  |

| 0          | 0                            | 0                                                    | 0                    | 0                           |  |  |  |  |

| 1          | 1 · 1/f <sub>VCO</sub>       | 0.406                                                | 0.400                | 0.339                       |  |  |  |  |

| 2          | 2 · 1/f <sub>VCO</sub>       | 0.8138                                               | 0.800                | 0.678                       |  |  |  |  |

|            |                              |                                                      |                      |                             |  |  |  |  |

| Φ          | $\Phi \cdot 1/f_{VCO}$       | $\mathbf{\Phi} \cdot 0.406$                          | $\Phi \cdot 0.400$   | $\mathbf{\Phi} \cdot 0.339$ |  |  |  |  |

|            |                              |                                                      |                      |                             |  |  |  |  |

| 63         | 63 · 1/f <sub>VCO</sub>      | 25.634                                               | 25.200               | 21.362                      |  |  |  |  |

NOTE 1. Individual setting for each clock output Bank A, B and C. NOTE 2. VCO-0

NOTE 3. VCO-1

Table 2N.  $\Phi_{A0}$ ,  $\Phi_{A1}$ ,  $\Phi_{B0}$ ,  $\Phi_{B1}$  QREF Phase Delay<sup>1, 2</sup>

|      |        |                                         | Phase Delay | $(\Phi)$ in ns for a VCO Frequen | cy (f <sub>VCO</sub> ) of: |  |

|------|--------|-----------------------------------------|-------------|----------------------------------|----------------------------|--|

| Dela | y Unit | Delay                                   | 2457.6MHz   | 2500MHz                          | 2949.12MHz                 |  |

| 0    | 000    | 0                                       | 0.000       | 0.000                            | 0.000                      |  |

| 1    | 001    | t <sub>Delay</sub>                      | 0.165       | 0.165                            | 0.165                      |  |

| 2    | 010    | 1/f <sub>VCO</sub>                      | 0.407       | 0.400                            | 0.339                      |  |

| 3    | 011    | t <sub>Delay</sub> + 1/f <sub>VCO</sub> | 0.572       | 0.565                            | 0.504                      |  |

| 4    | 100    | 2/f <sub>VCO</sub>                      | 0.814       | 0.800                            | 0.678                      |  |

| 5    | 101    | t <sub>Delay</sub> + 2/f <sub>VCO</sub> | 0.979       | 0.965                            | 0.843                      |  |

| 6    | 110    | 3/f <sub>VCO</sub>                      | 1.221       | 1.200                            | 1.017                      |  |

| 7    | 111    | t <sub>Delay</sub> + 3/f <sub>VCO</sub> | 1.386       | 1.365                            | 1.182                      |  |

NOTE 1.  $t_{Delay}$  is implemented by inserting a buffer delay of 165ps (±20% tolerance).

NOTE 2. Individual setting for each SYSREF delay stages. See Table 3G for register configurations.

#### **QREF to QCLK Phase Alignment**

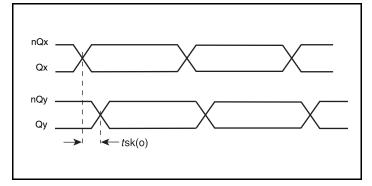

The QREF outputs have a deterministic phase relation to the QCLK outputs. The delay circuits in both QCLK and QREF paths add phase offset to configure the phase relationship of each QCLK and QREF pair. There are 64 delay steps for each QCLK output bank and additional 8 delay steps on each QREF output. The QCLK delay unit is equal to one VCO period, the QREF delay unit is equal to approximately one half VCO period (fine delay). Each QCLK output bank and each QREF output can be individually advanced, aligned or delayed with respect to an incident QCLK rising edge. See Figure 1: For phase alignment between the incident edge of QCLK outputs and QREF, set the phase delay to  $\Phi = 9$  (QCLK) and  $\Phi = 0$  (QREF). As a pre-condition for alignment of SYSREF pulses to the incident clock edge, set the SYSREF synchronizer divider to the least common multiple value of clock dividers N<sub>A</sub> and N<sub>B</sub> (see Table 3K).

Figure 1. QREF to QCLK Phase Relationship

### **SYSREF** Generation

The QREF outputs generate SYSREF signal pulses that support JESD204B synchronization functions. Following SYSREF pulse generation modes are available and configurable by SPI:

- Counted pulse mode: 1 to 255 pulses are generated by the device. SYSREF activity stops automatically after the transmission of the selected number of pulses and the QREF output powers down.

- Continuous mode. The SYSREF signal is a clock signal.

#### Table 20. SYSREF Generation<sup>1, 2</sup>

The generation of SYSREF pulses is configured by SPI commands and is available after the initial setup of output clock divider and QREF phase delay stages.

An essential part of the SYSREF generation is the sequence of SPI commands to apply to synchronize the SYSREF pulses to the clock divider and delay state machines.

|     |   | Ν                    | IS   |                |                              | SYSREF                     | SYSREF Operation (f <sub>SYSREF</sub> ) for f <sub>VCO</sub> (MHz) |       |  |  |  |

|-----|---|----------------------|------|----------------|------------------------------|----------------------------|--------------------------------------------------------------------|-------|--|--|--|

| SRO | 3 | 2 1 0 N <sub>S</sub> |      | N <sub>S</sub> | f <sub>VCO</sub> = 2457.6MHz | 2500                       | 2949.12                                                            |       |  |  |  |

|     |   |                      | 1    |                | L                            | Counted Pulse Mode         |                                                                    |       |  |  |  |

|     |   |                      | (Use | the SRP        | C register to c              | onfigure the number of ger | nerated SYSREF pulses)                                             |       |  |  |  |

|     | 0 | 0                    | 0    | 0              | ÷64                          | 38.4                       | 39.0625                                                            | 46.08 |  |  |  |

|     | 0 | 0                    | 0    | 1              | ÷96                          | 25.6                       | 26.04166                                                           | 30.72 |  |  |  |

|     | 0 | 0                    | 1    | 0              | ÷128                         | 19.2                       | 19.53125                                                           | 23.04 |  |  |  |

|     | 0 | 0                    | 1    | 1              | ÷192                         | 12.8                       | 13.02083                                                           | 15.36 |  |  |  |

| 0   | 0 | 1                    | 0    | 0              | ÷256                         | 9.6                        | 9.76562                                                            | 11.52 |  |  |  |

| 0   | 0 | 1                    | 0    | 1              | ÷384                         | 6.4                        | 6.51041                                                            | 7.68  |  |  |  |

|     | 0 | 1                    | 1    | 0              | ÷512                         | 4.8                        | 4.88281                                                            | 5.76  |  |  |  |

|     | 0 | 1                    | 1    | 1              | ÷768                         | 3.2                        | 3.25520                                                            | 3.84  |  |  |  |

|     | 1 | 0                    | 0    | 0              | ÷1024                        | 2.4                        | 2.44140                                                            | 2.88  |  |  |  |

|     | 1 | 0                    | 0    | 1              | ÷2048                        | 1.2                        | 1.22070                                                            | 1.44  |  |  |  |

|     |   | 1                    | 1    |                | L                            | Continues Pulse Mo         | ode                                                                |       |  |  |  |

|     | 0 | 0                    | 0    | 0              | ÷64                          | 38.4                       | 39.0625                                                            | 46.08 |  |  |  |

|     | 0 | 0                    | 0    | 1              | ÷96                          | 25.6                       | 26.04166                                                           | 30.72 |  |  |  |

|     | 0 | 0                    | 1    | 0              | ÷128                         | 19.2                       | 19.53125                                                           | 23.04 |  |  |  |

|     | 0 | 0                    | 1    | 1              | ÷192                         | 12.8                       | 13.02083                                                           | 15.36 |  |  |  |

|     | 0 | 1                    | 0    | 0              | ÷256                         | 9.6                        | 9.76562                                                            | 11.52 |  |  |  |

| 1   | 0 | 1                    | 0    | 1              | ÷384                         | 6.4                        | 6.51041                                                            | 7.68  |  |  |  |

|     | 0 | 1                    | 1    | 0              | ÷512                         | 4.8                        | 4.88281                                                            | 5.76  |  |  |  |

|     | 0 | 1                    | 1    | 1              | ÷768                         | 3.2                        | 3.25520                                                            | 3.84  |  |  |  |

|     | 1 | 0                    | 0    | 0              | ÷1024                        | 2.4                        | 2.44140                                                            | 2.88  |  |  |  |

|     | 1 | 0                    | 0    | 1              | ÷2048                        | 1.2                        | 1.22070                                                            | 1.44  |  |  |  |

NOTE 1. SRO and SRPC are global settings. See Table 2P for the setting sequence to apply.

NOTE 2. SYSREF setting should only be used with 400mV and 700mV amplitude setting.

# QCLK Phase Delay and SYSREF Synchronization Sequence (S2)

Precondition: Delay circuits are set to powered-up (nPOWER = 0). Set MUX = 1 to assign the SYSREF function to the QREF outputs, N<sub>S</sub> to the SYSREF pulse rate and configure the SYSREF synchronizer divider value to the least common multiple value of N<sub>A</sub> and N<sub>B</sub>.

- Write SR\_REQ0 = 1 (register 5). QREF outputs will power up.

- Write SR\_REQ1 = 1 (register 25): N<sub>S</sub> dividers are reset and synchronize.

- Write SR\_RESET = 1 (register 29): Continuous clocks or a number of specified pulses will be generated at QREF outputs.

See Table 2P for detailed description of the sequences.

#### Table 2P. SYSREF Generation Sequence

| SRO | SYSREF<br>Pulse Mode | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Counted              | <ul> <li>Pre-condition: <ul> <li>OUTEN = 1, MUX = 1, nPOWER = 0,<br/>A[1:0] = 01</li> <li>SPRC[7:0] contains the number of pulses<br/>to generate (1255)</li> <li>NS[3:0] contains the SYSREF divider</li> <li>SYNC[3:0] is set to the least common<br/>multiple value of N<sub>A</sub> and N<sub>B</sub>.</li> </ul> </li> <li>Start operation: apply sequence S2 <ul> <li>QREF output will power-up for SYSREF<br/>pulse generation.</li> <li>The programmed number of SYSREF<br/>pulses is generated</li> <li>QREF output will power down<br/>automatically</li> <li>The three SR_REQ0, 1 and SR_RESET<br/>bits clear automatically</li> </ul> </li> <li>Repeated use: apply sequence (S2) at any<br/>time</li> </ul> |

| 1   | Continues            | <ul> <li>Pre-condition:</li> <li>A[1:0] = 01</li> <li>MUX = 1, nPOWER = 0</li> <li>OUTEN = 1</li> <li>NS[3:0] contains the SYSREF divider</li> <li>SYNC[3:0] is set to the least common multiple value of N<sub>A</sub> and N<sub>B</sub>.</li> <li>Start operation: apply sequence S2</li> <li>Stop operation: Set SRO = 0</li> <li>Restart function: Set SRO = 1 and apply sequence S2</li> </ul>                                                                                                                                                                                                                                                                                                                      |

## Device Start-up, Reset and Synchronization

After the 8V19N408 first powers-up, an internal reset signal is auto-generated. The registers are initialized with the default values listed in the table for each register.

During startup, it is not required to apply an input clock to the CLK input: the VCXO-PLL will "free-run" with the frequency of the external VCXO. The control voltage of the external VCXO (LFV pin) will be held at  $V_{DD}/2$  to support fast PLL lock and the VCXO-PLL will begin operation with their charge pumps in the middle of their operating range.

As a second step, the user should write the desired PLL dividers. Configure other operation settings such the output divider, SYSREF divider and output phase delay settings into the registers and apply software-controlled divider reset and QREF phase delay stage synchronization sequences. This is done by two separate SPI-controlled reset procedures which should be applied in the order below. First, apply the output divider reset sequence:

#### **Clock Output Divider Reset Sequence, (Sequence S1)**

- step 1: write logic 1 to the NR\_REQ0 register bit

- step 2: write logic 1 to the NR\_REQ1 register bit

- step 3: write logic 1 to the NR\_RESET bit

This completes the reset of the output divider stages. Each subsequent change of any N output divider value requires to re-apply above divider reset sequence.

Then, configure the delay stages and when completed, apply the second sequence to synchronize the QREF output delay stages:

# QREF Phase Delay and SYSREF Synchronization Sequence, (Sequence S2)

- step 1: write logic 1 to the SR\_REQ0 register bit

- step 2: write logic 1 to the SR\_REQ1 register bit

- step 3: write logic 1 to the SR\_RESET bit

This completes the synchronization of the delay stages. The clock divider reset sequence and the QREF phase delay & SYSREF synchronization sequence must be done in two separate SPI write cycles (do not combine both sequences in a single SPI write).

If sequences S1 and S2 are programmed in any order other than that which is recommended, this could result in an unknown state of the SYSREF generation. In order to reactivate the SYSREF Synchronization Sequence, power down QREF outputs by programming nPOWER bits to "1". The device is now ready for a new SYSREF Synchronization Sequence.

Any change of the output divider values or delay stage configuration require to re-apply initialization/ synchronization through the respective SPI sequence individually.

When synchronizing the output delay stages through the synchronization sequence, care must be taken prevent writing a logic 1 to the NR\_REQ0, NR\_REQ1, NR\_RESET register bits in the same base register write cycle (write a logic 0 to these bits, which will not affect them).

The QREF phase delay and SYSREF synchronization sequence is also used to trigger the synchronized generation of SYSREF pulses. The last steps, it is recommended to clear all interrupts in preparation to start monitoring the devices status bits.

## **Status Conditions & Interrupts**

The 8V19N408 has an interrupt output to signal changes in status conditions. Settings for status conditions may be accessed in the Status and Interrupt Enable registers. The 8V19N408 has several conditions that can indicate faults and status changes in the operation of the device. These are shown in Table 2Q and can be monitored directly in the status registers. A changed bit on any or all of these can be programmed to generate an interrupt signal (nINT) via settings in the Interrupt Enable registers.

#### Table 2Q. Status Bit Functions

|          |                 | Status if Bit is: |                  |  |  |

|----------|-----------------|-------------------|------------------|--|--|

| Bit Name | Function        | 1                 | 0                |  |  |

| STAT[2]  | VCO calibration | Completed         | Not<br>completed |  |  |

| STAT[1]  | VCXO-PLL        | Locked            | Unlocked         |  |  |

| STAT[0]  | CLK state       | Active            | LOS              |  |  |

For the reference monitor circuit, if there has been no activity on the reference input for three consecutive clock edges (of the feedback 1st-stage VCXO signal) then the appropriate status bit will transition to a 0. It will not return to 1 until activity has resumed for three clock edges.

The lock detect circuit operate by monitoring the loop filter voltage on the first PLL (VCXO-PLL). If the monitored voltage exceeds a range, this indicates an out-of-lock condition.

It is normal when attempting to achieve lock for there to be multiple times when an out-of-lock condition as described above would occur before a full, stable lock is achieved. To prevent a bouncing status, the lock detect bit will not become asserted until the lock is stable. Once a stable lock has been achieved, this de-bounce circuit is deactivated so the lock-detect bit will de-assert immediately if a subsequent out-of-lock condition occurs.

The Interrupt and Interrupt Enable registers are used to control the behavior of the nINT output based on changes in the status indicators. If any of the status indicators STAT[1:0] change, that will set the corresponding INT[1:0] bit of the Interrupt registers. If any of the INT[1:0] bits are set and their corresponding interrupt enable bit INTEN[1:0] is asserted, it will generate an interrupt (low level on nINT).

Interrupts are cleared by writing a 1 to the appropriate INT[1:0] bit(s) in the Interrupt register after the underlying fault condition has been resolved. When all valid interrupt sources have been cleared in this manner, this will release the nINT output until the next unmasked fault.

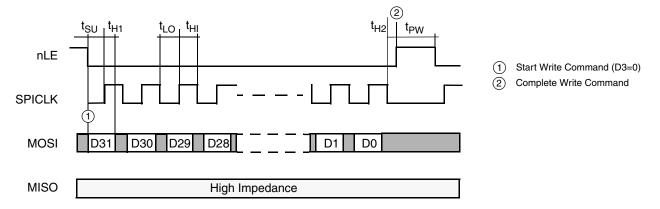

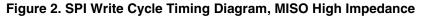

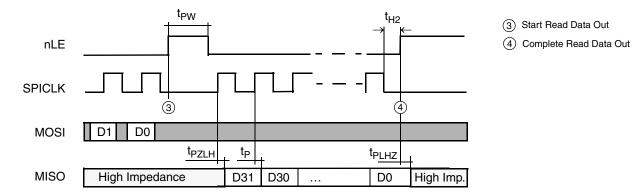

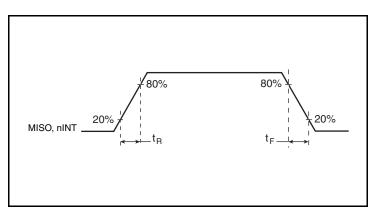

## SPI Mode Operation with MISO Output in High Impedance

SPI mode slave operation requires that some function external to the 8V19N408 has performed any necessary serial bus arbitration and/or address decoding at the level of the board or system. By default, the MISO data output is in high-impedance state. The 8V19N408 begins a cycle by detecting an asserted (low) state on the nLE input at a rising edge of SPICLK. This is also coincident with the first bit of data being shifted into the device. In SPI mode, the first bit is the Most Significant Bit (MSB) of the data word being written. Data must be written in 32-bit words, with nLE remaining asserted and one data bit being shifted in to the 8V19N408 on every rising edge of SPICLK. If nLE is deasserted (high) at any time except following the 32<sup>nd</sup> falling edge of SPICLK, then this is treated as an error and the shift register contents are discarded. No data is written to any internal registers. If nLE is deasserted (high) as expected after the 32<sup>nd</sup> falling edge of SPICLK, then this will result in the shift register contents being acted on according to the instructions (address + R/W) in it. During write operation, the MISO output remains in high-impedance state. The word format of the 32-bit quantity in the shift register is shown in Table 2S. The register fields in the 8V19N408 have been organized so that

the 4 LSBs in each 32-bit register row are not used for data transfer. Three of these bits will represent the base address for the eight 32-bit base registers and the 4th bit indicates whether a read or write operation is requested. If a read operation is requested, 32-bits of read data will be provided in the immediately subsequent access. The nLE must be deasserted (high) and then reasserted (low). On the first SPICLK rising edge, once nLE is re-asserted to low state, the MISO output will turn to active state and one data bit will be placed on the MISO output at each rising edge of SPICLK as long as nLE remains asserted (low). If nLE is deasserted (high) before 32-bits of read data have been shifted out, the read cycle will be considered to be completed. If nLE remains asserted (low) longer than 32-bit times, then the data during those extra clock periods will be undefined. The MSB of the data will be presented first. When nLE is de-asserted (high), the MISO output will go into high impedance state and the SPI bus is available for transactions with other devices.

## Table 2R. SPI Read / Write Cycle Timing Parameters

| Symbol            | Parameter                                                              | Test Condition               | Minimum | Maximum | Unit |

|-------------------|------------------------------------------------------------------------|------------------------------|---------|---------|------|

| f <sub>CLK</sub>  | SPICLK frequency                                                       |                              | -       | 20      | MHz  |

| t <sub>SU</sub>   | nLE, MOSI setup time to SPICLK                                         |                              | 15      | -       | ns   |

| t <sub>H1</sub>   | SPICLK to nLE, MOSI hold time                                          |                              | 10      | -       | ns   |

| t <sub>H2</sub>   | SPICLK falling edge to nLE rising edge, hold time                      |                              | 10      | -       | ns   |

| t <sub>LO</sub>   | SPICLK low period                                                      |                              | 25      | -       | ns   |

| t <sub>HI</sub>   | SPICLK high period                                                     |                              | 25      | -       | ns   |

| t <sub>PW</sub>   | nLE deasserted pulse width                                             |                              | 50      | -       | ns   |

| t <sub>PZLH</sub> | Propagation Delay, MISO Output High<br>Impedance to Active High or Low | External pullup = $5k\Omega$ |         | 16      | ns   |

| t <sub>PLHZ</sub> | Propagation Delay, MISO Output Active<br>High or Low to High Impedance | External pullup = $5k\Omega$ |         | 2       | ns   |

| t <sub>P</sub>    | Propagation Delay, SPICLK to MISO                                      | External pullup = $5k\Omega$ |         | 20      | ns   |

## Table 2S. SPI Interface I/O Voltage Select

| SELSV       | SPI Interface I/O Voltage (SPICLK, MOSI, MISO, nLE, nINT) |

|-------------|-----------------------------------------------------------|

| 0           | 1.8V                                                      |

| 1 (default) | 3.3V                                                      |

# **Register Descriptions**

The Serial Control port of the 8V19N408 supports SPI mode operation. Below indicates how registers may be accessed.

## Table 3A. Register Map

| Base Address | Register |                                                             |                      | Default   |                       |                       |                      |                  |                       |                       |                  |                     |

|--------------|----------|-------------------------------------------------------------|----------------------|-----------|-----------------------|-----------------------|----------------------|------------------|-----------------------|-----------------------|------------------|---------------------|

| Bas          |          | Register Name                                               | See                  | Setting   | D7                    | D6                    | D5                   | D4               | D3                    | D2                    | D1               | D0                  |

|              | 0        | QCLKC Control                                               | Table 3E             | 0000 XXXX | QC<br>DLY[5]          | QC<br>DLY[4]          | QC<br>DLY[3]         | QC<br>DLY[2]     | R/Wn                  | 0                     | 0                | 0                   |

| 0            | 1        | M <sub>V</sub> Feedback<br>Divider Control                  | Table 3C             | 1111 1111 | MV[7]                 | MV[6]                 | MV[5]                | MV[4]            | MV[3]                 | MV[2]                 | MV[1]            | MV[0]               |

|              | 2        | M <sub>F0</sub> Feedback<br>Divider                         | Table 3C             | 0001 0000 | MF0[7]                | MF0[6]                | MF0[5]               | MF0[4]           | MF0[3]                | MF0[2]                | MF0[1]           | MF0[0]              |

|              | 3        | SYSREF Control                                              | _                    | 1000 0001 | Reserved              | Reserved              | Reserved             | Reserved         | Reserved              | Reserved              | Reserved         | SRO                 |

|              | 4        | QCLKC Control<br>QCLKB Control                              | Table 3E             | 0000 XXXX | QC<br>DLY[1]          | QC<br>Dly[0]          | QB<br>DLY[1]         | QB<br>DLY[0]     | R/Wn                  | 0                     | 0                | 1                   |

| 1            | 5        | Reset Control<br>M <sub>V</sub> Feedback<br>Divider Control | Table 3S<br>Table 3C | X000 0000 | SR_REQ0               | MV[14]                | MV[13]               | MV[12]           | MV[11]                | MV[10]                | MV[9]            | MV[8]               |

|              | 6        | QREFA1, A0<br>Control                                       | Table 3G             | 1000 1000 | QREFA1<br><b>A[1]</b> | QREFA1<br><b>A[0]</b> | QREFA1<br>EF         | QREFA1<br>MUX    | QREFA0<br>A[1]        | QREFA0<br><b>A[0]</b> | QREFA0<br>EF     | QREFA0<br>MUX       |

|              | 7        | Reset Control<br>SYSREF Control                             | Table 3S<br>Table 3K | X000 1000 | NR_REQ0               | Reserved              | SYNC<br>nPOWER       | Reserved         | SYNC<br><b>N[3]</b>   | SYNC<br><b>N[2]</b>   | SYNC<br>N[1]     | SYNC<br><b>N[0]</b> |

|              | 8        | QCLKB Control                                               | Table 3E             | 0000 XXXX | QB<br>DLY[5]          | QB<br>DLY[4]          | QB<br>DLY[3]         | QB<br>DLY[2]     | R/Wn                  | 0                     | 1                | 0                   |

|              | 9        | P <sub>V</sub> Pre-Divider                                  | Table 3C             | 1111 1111 | PV[7]                 | PV[6]                 | PV[5]                | PV[4]            | PV[3]                 | PV[2]                 | PV[1]            | PV[0]               |

| 2            | 10       | Status Control                                              | Table 3O             | XXXX X0XX | Reserved              | STAT2                 | STAT1                | STAT0            | Reserved              | Reserved              | INT1             | INT0                |

|              | 11       | SYSREF Control<br>QREF B1, B0<br>Control                    | Table 3K<br>Table 3G | 0100 1111 | NS[3]                 | NS[2]                 | NS[1]                | NS[0]            | QREFB1<br>OE          | QREFB0<br>OE          | QREFA1<br>OE     | QREFA0<br>OE        |

|              | 12       | QCLKA Control                                               | Table 3E             | 0000 XXXX | QA<br>DLY[5]          | QA<br>DLY[4]          | QA<br>DLY[3]         | QA<br>DLY[2]     | R/Wn                  | 0                     | 1                | 1                   |

| 3            | 13       | VCXO-PLL Control                                            | Table 3I             | 0010 0000 | POLV                  | HOLD                  | CPV[5]               | CPV[4]           | CPV[3]                | CPV[2]                | CPV[1]           | CPV[0]              |

| 3            | 14       | M <sub>F1</sub> Feedback<br>Divider                         | Table 3C             | 0001 0000 | MF1[7]                | MF1[6]                | MF1[5]               | MF1[4]           | MF1[3]                | MF1[2]                | MF1[1]           | MF1[0]              |

|              | 15       | Reserved                                                    |                      | 1000 0000 | Reserved              | Reserved              | Reserved             | Reserved         | Reserved              | Reserved              | Reserved         | Reserved            |

|              | 16       | QCLKA Control<br>VCXO-PLL Control                           | Table 3E<br>Table 3I | 0000 XXXX | QA<br>DLY[1]          | QA<br>DLY[0]          | Reserved             | BYPASS           | R/Wn                  | 1                     | 0                | 0                   |

| 4            | 17       | QREFA1 Control<br>QREFA0 Control                            | Table 3G             | 0001 0001 | QREFA1<br>DLY[2]      | QREFA1<br>DLY[1]      | QREFA1<br>DLY[0]     | QREFA1<br>nPOWER | QREFA0<br>DLY[2]      | QREFA0<br>DLY[1]      | QREFA0<br>DLY[0] | QREFA0<br>nPOWER    |