# Quad Freq LVDS+CMOS Oscillator 148.5 / 74.25 / 148.35 / 74.175MHz with 27MHz CMOS

4EA1485A0Z4

# **ADVANCE DATASHEET**

#### **Features**

4 LVDS Frequencies: 148.5, 74.25, 148.35 & 74.175MHz

1 CMOS output: 27MHz

Frequency Stability: ± 50ppm

Supply Voltage: 2.5V and 3.3V

Standard Packages: 7.0 x 5.0 mm

■ RMS phase jitter: <1 ps typical (12k to 20MHz)

Operating Temperature: - 40 to 85 °C

# 7.0 x 5.0 mm package

#### **General Description**

The 4EA1485A0Z4 is a quad frequency oscillator incorporating IDT's pMEMS technology to generate up to four LVDS clock frequencies. An additional synchronous CMOS output is also provided for general purpose clocking. One 4EA1485A0Z4 can replace up to 5 separate crystal oscillators, reducing inventory and bill-of-material cost. The pinout and footprint is backward compatible to industry standard 7050 size oscillators, ensuring second source compatibility to traditional 6 pin SMD oscillators.

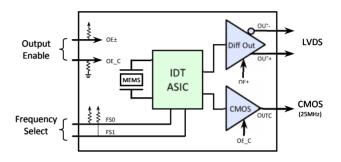

# **Functional Block Diagram**

#### **Pin Description**

| Pin  | Name       | Description        | OUTC OE_C |

|------|------------|--------------------|-----------|

| 1    | OE±        | LVDS Output Enable | OE± 1 VDD |

| 6, 7 | OUT+, OUT- | LVDS Output        |           |

| 2    | N/C        | No connect         | N/C OUT-  |

| 3,8  | GND, VDD   | Supply Voltage     | ]         |

| 4, 5 | FS0, FS1   | Frequency Select   | GND OUT+  |

| 9    | OE_C       | CMOS Output Enable |           |

| 10   | OUTC       | CMOS Output        | FSO FS1   |

#### **Frequency Table**

| Input*  | Output (MHz) |        |  |  |

|---------|--------------|--------|--|--|

| FS[1,0] | LVDS         | CMOS   |  |  |

| 1,1     | 148.50       | 27.0   |  |  |

| 1,0     | 74.25        | 27.0   |  |  |

| 0,1     | 148.35       | 26.973 |  |  |

| 0,0     | 74.175       | 20.973 |  |  |

<sup>\*</sup> FS0, FS1 includes weak pull-up resistor

#### Enable/Disable

| OE±* | LVDS |  |  |

|------|------|--|--|

| HI   | ON   |  |  |

| LOW  | OFF  |  |  |

\*Includes weak pull-up resistor

| OE_C* | CMOS |

|-------|------|

| HI    | ON   |

| LOW   | OFF  |

<sup>\*</sup>Includes weak pull-down resistor

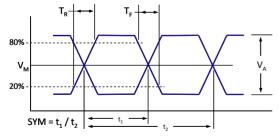

#### **Output Waveform (LVDS)**

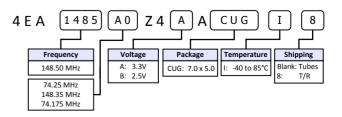

#### **Part Ordering Information**

| Package Size     | Voltage | Ordering Code     |  |

|------------------|---------|-------------------|--|

| 7.0 x 5.0 mm     | 3.3V    | 4EA1485A0Z4AACUGI |  |

| 7.0 X 5.0 IIIIII | 2.5V    | 4EA1485A0Z4BACUGI |  |

<sup>\*</sup> Factory minimum order quantity: 500pcs (T/R)

### **Output Waveform (CMOS)**

#### **Specification**

|                                   | 2.5 V                |      |                | 3.3 V                |      | Units       | Conditions |                                                                                           |

|-----------------------------------|----------------------|------|----------------|----------------------|------|-------------|------------|-------------------------------------------------------------------------------------------|

| Parameter                         | Specifications       |      | Specifications |                      |      |             |            |                                                                                           |

|                                   | Min                  | Тур  | Max            | Min                  | Тур  | Max         |            |                                                                                           |

| Supply Voltage (V <sub>DD</sub> ) | 2.375                | 2.50 | 2.625          | 2.97                 | 3.30 | 3.63        | V          |                                                                                           |

| Frequency Stability               | - 50                 |      | + 50           | - 50                 |      | + 50        | ppm        | Includes supply voltage and temperature variation (-40 to 85°C), reflow drift, and aging. |

| Supply Current                    |                      | 130  |                |                      | 140  |             | mA         | No load                                                                                   |

| Enable/Disable Time               |                      |      | 1              |                      |      | 1           | us         | Guaranteed by design                                                                      |

| Input HIGH/LOW level              | $0.\ 7V_{DD}$        |      | $0.3V_{DD}$    | $0.7V_{\text{DD}}$   |      | $0.3V_{DD}$ | V          | At OE± & OE_C pins                                                                        |

| Start-up Time                     |                      | 10   |                |                      | 10   |             | ms         | Output valid time after power up, 25°C                                                    |

| Aging                             |                      | ± 5  |                |                      | ± 5  |             | ppm        | 25°C, 10 years                                                                            |

|                                   |                      |      |                |                      |      | LVD         | Outp       | ut                                                                                        |

| Output LOW level                  |                      | 1.05 |                |                      | 1.05 |             | V          |                                                                                           |

| Output HIGH level                 |                      | 1.40 |                |                      | 1.40 |             | V          |                                                                                           |

| Amplitude (V <sub>A</sub> )       |                      | 0.35 |                |                      | 0.35 |             | V          | Single Ended output swing (Pk-Pk)                                                         |

| Mid Level (V <sub>M</sub> )       |                      | 1.22 |                |                      | 1.22 |             | V          |                                                                                           |

| Rise Time (T <sub>R</sub> )       |                      | 370  | 420            |                      | 410  | 520         | ps         | Maximum; 20/80% of $V_A$ ; Output load (CL) = 2pF; Guaranteed by Char.                    |

| Fall Time (T <sub>F</sub> )       |                      | 370  | 420            |                      | 410  | 520         | ps         | Maximum; $20/80\%$ of $V_A$ ; Output load (CL) = 2pF; Guaranteed by Char.                 |

| Symmetry (SYM)                    | 48                   | 50   | 52             | 48                   | 50   | 52          | %          | Worst case; measured at 50% of waveform                                                   |

| Phase Jitter                      |                      | 1.0  |                |                      | 0.9  |             | ps         | 12k to 20MHz, RMS; Measured Differentially                                                |

| Period Jitter                     |                      | 4.1  |                |                      | 4.2  |             | ps         | RMS                                                                                       |

| Cycle-to-Cycle Jitter             |                      | 32   |                |                      | 32   |             | ps         | 1,000 cycles, Peak                                                                        |

| CMOS Output (27 MHz / 26.973 MHz) |                      |      |                |                      |      |             |            |                                                                                           |

| Rise/Fall Time $(T_{R/} T_F)$     |                      | 500  |                |                      | 500  |             | ps         | Maximum; 20/80% of V <sub>A</sub> ; Output load (CL) = 15pF                               |

| Symmetry (SYM)                    | 48                   |      | 52             | 48                   |      | 52          | %          | Worst case; measured at 50% of waveform                                                   |

| Output HIGH/LOW level             | V <sub>DD</sub> -0.3 |      | 0.3            | V <sub>DD</sub> -0.3 |      | 0.3         | V          | I <sub>OL</sub> =8mA; I <sub>OH</sub> =-8mA                                               |

| Period Jitter (rms)               |                      | 25   |                |                      | 20   |             | ps         | Measured over 10k cycles                                                                  |

| Cycle to Cycle Jitter             |                      | 120  |                |                      | 100  |             | ps         | 1,000 cycles, Peak                                                                        |

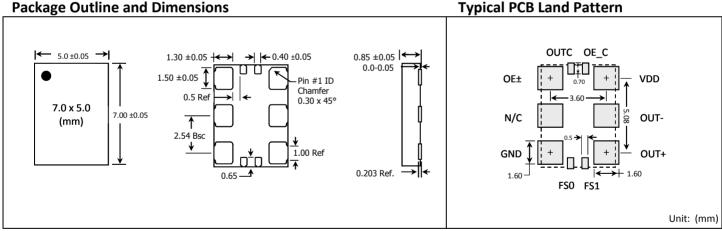

**Package Outline and Dimensions**

800-345-7015 (inside USA) +1 408-284-8200 (outside USA)

**Technical Support**

MEMS\_Support@idt.com www.idt.com/go/MEMS

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including DISCLAMENT INITEGRATE DEVICE a Technology, inc. (LIT) and its Subsidiaries reserve the Inglit to Indidity the products and products are not at IDT sold at IDT sold as a subject to change without notice. Performance performance is subject to change without notice specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties. IDT's products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners. Copyright 2010, 2011, 2012, 2013. All rights reserved