3 Channel High-Side and Low-Side Linear Solenoid Driver IC

TLE82453SA

# Data Sheet

Rev 1.0, 2013-03-21

# Automotive Power

#### **Table of Contents**

# **Table of Contents**

| 1                                                                                               | Overview                                                                                                                                                                                                                                                                                                                                                     | . 4                                                      |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2                                                                                               | Block Diagram                                                                                                                                                                                                                                                                                                                                                | . 5                                                      |

| <b>3</b><br>3.1<br>3.2                                                                          | Pin Configuration         Pin Assignment         Pin Definitions and Functions                                                                                                                                                                                                                                                                               | . 6                                                      |

| <b>4</b><br>4.1<br>4.2<br>4.3                                                                   | General Product Characteristics         Absolute Maximum Ratings         Functional Range         Thermal Resistance                                                                                                                                                                                                                                         | . 9<br>11                                                |

| <b>5</b><br>5.1<br>5.2                                                                          | Input / Output<br>I/O Description<br>Electrical Characteristics I/O                                                                                                                                                                                                                                                                                          | 13                                                       |

| <b>6</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12 | Power Supply         Overview         Battery Supply (VBAT)         Load Supplies (LSUP2, LSUP1, LSUP0)         Analog Supplies (VDDA and VDDAREF)         Digital Supply (VDDD)         I/O Supply (VIO)         Power On Reset         Charge Pump         Sleep Mode         Power Supply Modes         Initialization         Electrical Characteristics | 16<br>16<br>16<br>16<br>16<br>16<br>17<br>17<br>17       |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4                                                            | Power Stages         Overview         Channel Disabled         Channel Enabled         Electrical Characteristics Power Stages                                                                                                                                                                                                                               | 22<br>22<br>22                                           |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.10                        | Current Control<br>Overview<br>Average current setpoint<br>Dither waveform<br>Sense Resistor<br>Current Controller<br>PWM Frequency Controller<br>Autozero<br>Measurement Functions<br>Calibration Mode<br>Electrical Characteristics                                                                                                                        | 24<br>24<br>25<br>26<br>27<br>28<br>28<br>28<br>28<br>29 |

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.4                                                            | Protection Functions         Overview         Over Current Protection         Over Temperature Protection         Over Voltage Shutdown                                                                                                                                                                                                                      | 30<br>30<br>30                                           |

| 9.5                                                                                                                   | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                             |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

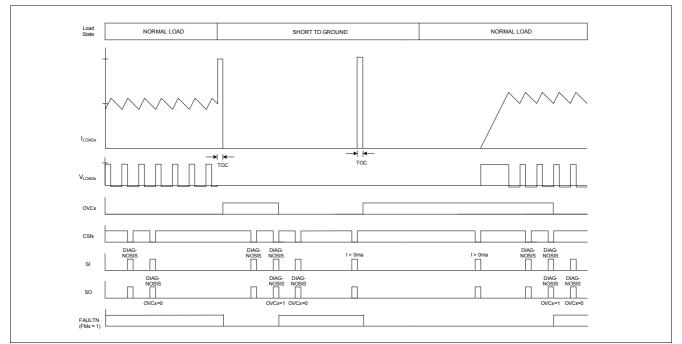

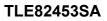

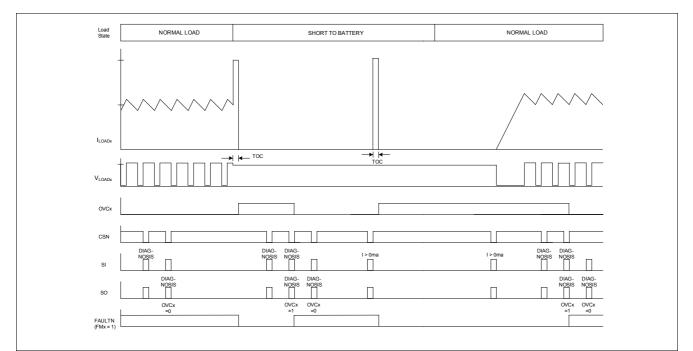

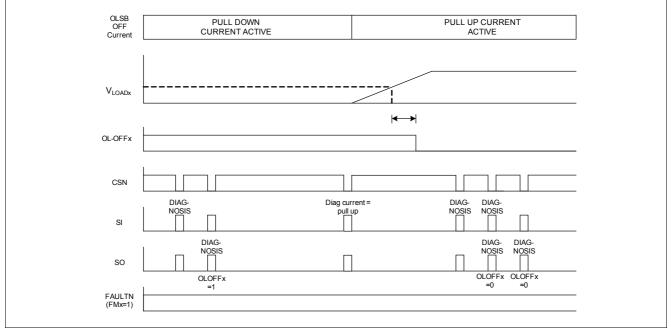

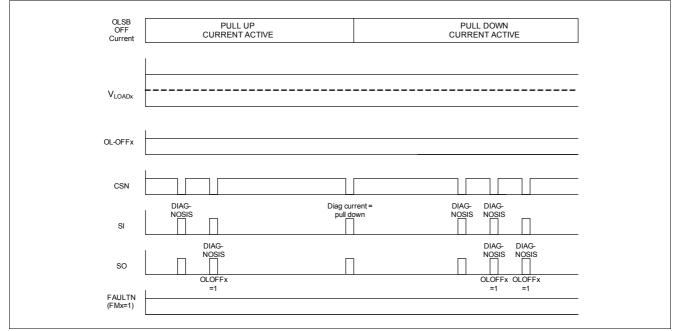

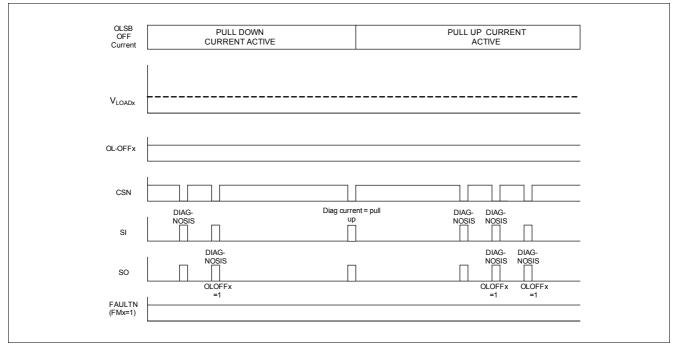

| <b>10</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.9                                     | Diagnosis Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33<br>34<br>34<br>35<br>39<br>40<br>40                         |

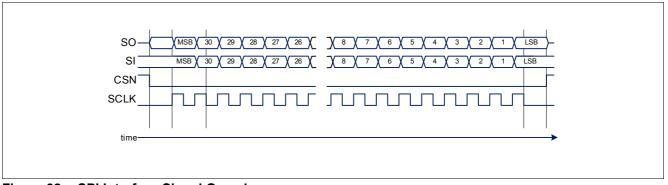

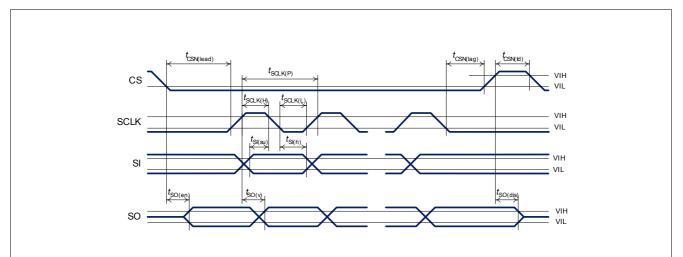

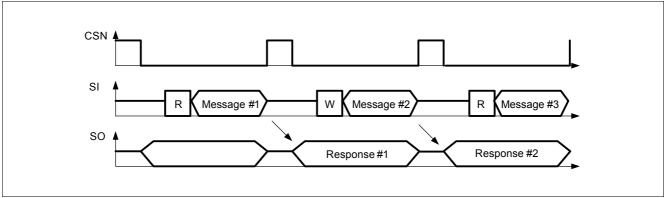

| <b>11</b><br>11.1<br>11.2<br>11.3                                                                                     | Serial Peripheral Interface (SPI)       4         Description of Interface       4         Timing Diagrams       4         Electrical Characteristics SPI Interface       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42<br>42                                                       |

| <b>12</b><br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>12.9<br>12.10<br>12.11<br>12.12<br>12.13 | SPI Registers4Description of Protocol4ICVID REGISTER4CONFIGURATION REGISTER4DIAGNOSIS REGISTER4CLK-DIVIDER REGISTER4CALIBRATION REGISTER4SETPOINT REGISTER4DITHER REGISTER4DITHER REGISTER4DITHER REGISTER4INTEGRATOR LIMIT REGISTER4PWM PERIOD REGISTER4INTEGRATOR THRESHOLD &OPEN ON REGISTER4AUTOZERO REGISTER4FEEDBACK REGISTER4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44<br>45<br>46<br>47<br>48<br>49<br>51<br>52<br>53<br>54<br>55 |

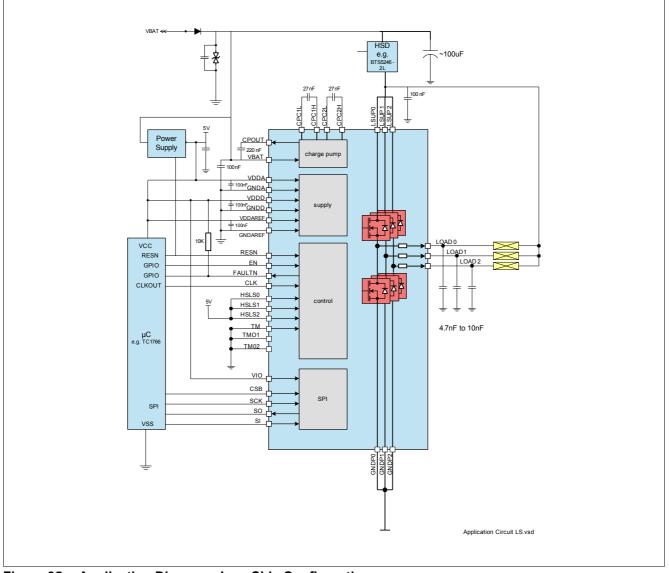

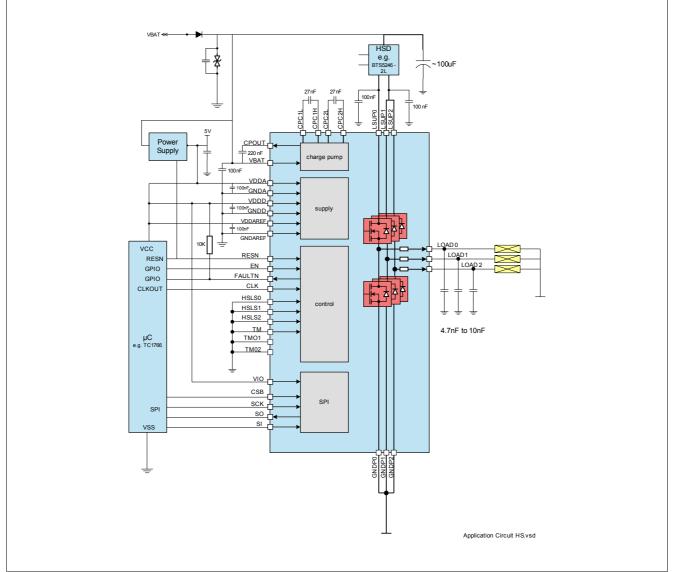

| <b>13</b><br>13.1                                                                                                     | Application Information         Second S |                                                                |

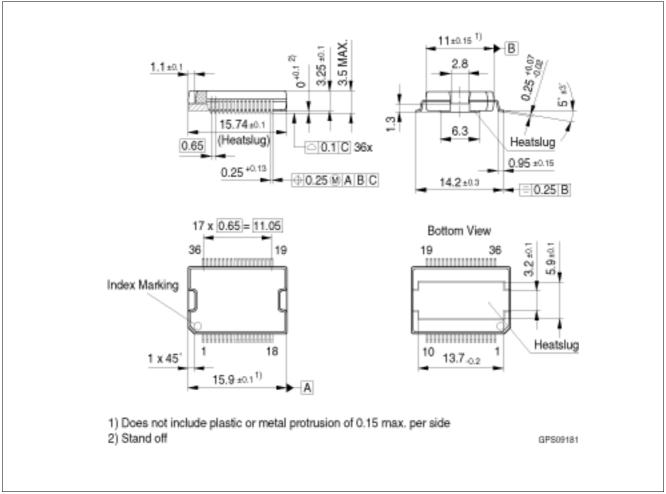

| 14                                                                                                                    | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                |

| 15                                                                                                                    | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60                                                             |

#### 3 Channel High-Side and Low-Side Linear Solenoid Driver IC Dragon IC

#### TLE82453SA

1 Overview

#### Features

- Three independent low side / high side configurable channels

- Integrated half-bridge power stages

- R<sub>ON</sub>(max) = 250 mΩ @ Tj = 150 °C

- Integrated sense resistor with internal TCR compensation

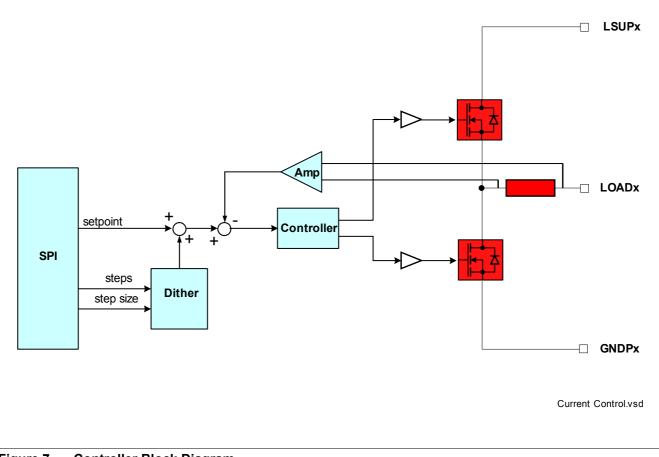

- Load current measurement range = 0 mA to 1500 mA (typical)

- Current setpoint resolution = 0.73 mA

- Current control accuracy

- +/- 5mA for load currents less than 500 mA

- +/- 1% for load currents greater than 500 mA

- Excellent immunity to large load supply voltage changes

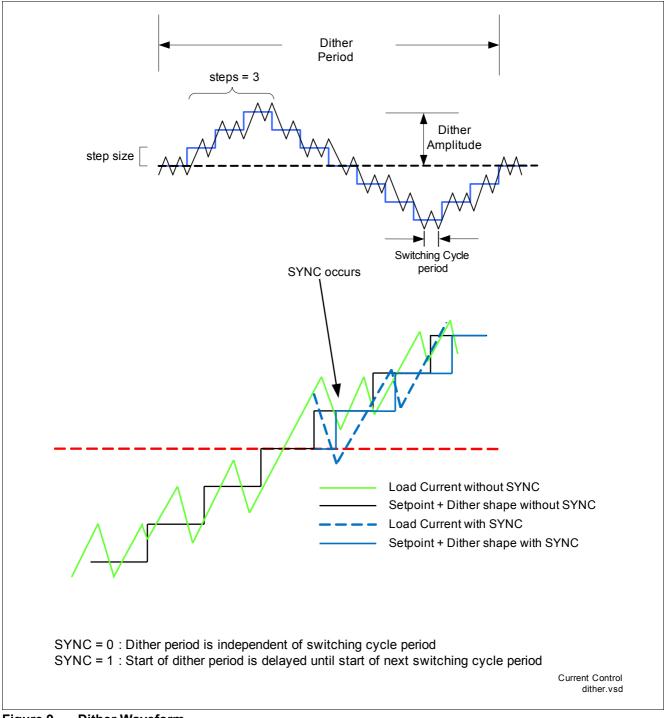

- Integrated dither generator with programmable amplitude & frequency

- SPI interface for output control, diagnosis, and configuration

- Independent thermal shutdown for each channel

- Open load, switch bypass, and overcurrent protection and diagnosis for each channel

- · Programmable slew rate control for reduced EMI

- Green Product (RoHS compliant)

- AEC Qualified

#### Description

The TLE 82453 is a flexible, monolithic solenoid driver IC designed for the control of linear solenoids in automatic transmission, electronic stability control, and active suspension applications. The three channels can be used as either lowside or highside drivers in any combination. The device includes the drive transistor, recirculation transistor, and current sensing resistor; minimizing the number of required external components.

This device is capable of regulating the average current flow in a load up to 1500 mA, depending on the dither settings and the load characteristics, with 0.73 mA resolution. A triangular dither waveform generator, when enabled, superimposes a triangular waveform with programmable amplitude and frequency on the programmed current setpoint.

A 32 bit SPI interface is used to control the three channels and to monitor the status of the diagnostic functions.

An active low reset input, RESN, is used to disable all of the channels and reset the internal registers to the default values. An active high enable pin, EN, is used to enable or disable the operation of the output channels. When the EN pin is low, the channels are disabled, and the SPI interface is fully functional. A fault output pin is provided to generate a signal that can be used as an external interrupt to the microcontroller whenever a fault is detected.

| Туре       | Package   | Marking    |

|------------|-----------|------------|

| TLE82453SA | PG-DSO-36 | TLE82453SA |

PG-DSO-36

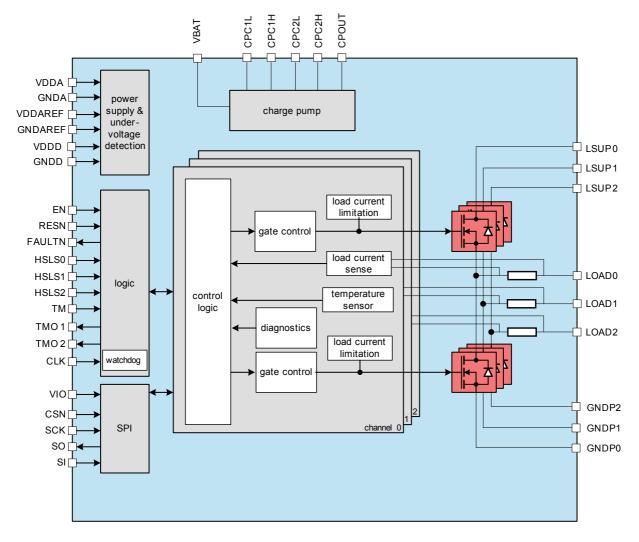

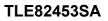

**Block Diagram**

# 2 Block Diagram

Block\_Diagram.vsd

#### Figure 1 Block Diagram

**Pin Configuration**

# 3 Pin Configuration

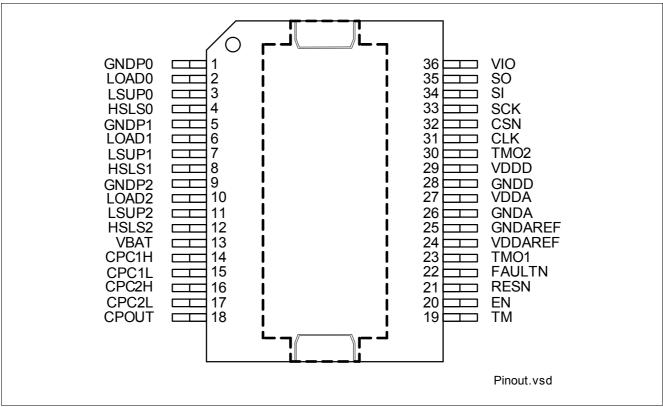

#### 3.1 Pin Assignment

#### Figure 2 Pin Configuration

# 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                                                               |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GNDP0  | <b>Ground;</b> Ground connection for channel 0 power stage. Chip damaged if connection lost                                            |

| 2   | LOAD0  | Output<br>Connect a ceramic capacitor <= 10 nF to GND for ESD protection.                                                              |

| 3   | LSUP0  | <b>Supply Voltage;</b> Supplies channel 0. Connect to Switched Battery Voltage with reverse protection diode and filter against EMC    |

| 4   | HSLS0  | <b>Control Input;</b> Digital input. Connect to ground for high-side configuration. Connect to +5V or VBAT for low-side configuration. |

| 5   | GNDP1  | <b>Ground;</b> Ground connection for channel 1 power stage. Chip damaged if connection lost.                                           |

| 6   | LOAD1  | Output<br>Connect a ceramic capacitor of <= 10 nF to GND for ESD protection.                                                           |

# infineon

# **TLE82453SA**

#### **Pin Configuration**

| Pin | Symbol  | Function                                                                                                                                                                                                                      |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LSUP1   | <b>Supply Voltage;</b> Supplies channel 1. Connect to Switched Battery Voltage with Reverse protection diode and filter against EMC                                                                                           |

| 8   | HSLS1   | <b>Control Input;</b> Digital input. Connect to ground for high-side configuration. Connect to +5V or VBAT for low-side configuration.                                                                                        |

| 9   | GNDP2   | <b>Ground;</b> Ground connection for channel 2 power stage. Chip damaged if connection lost.                                                                                                                                  |

| 10  | LOAD2   | <b>Output;</b><br>Connect a ceramic capacitor of <= 10 nF to GND for ESD protection.                                                                                                                                          |

| 11  | LSUP2   | <b>Supply;</b><br>Supplies channel 2. Connect to Switched Battery Voltage with reverse protection diode and filter against EMC                                                                                                |

| 12  | HSLS2   | <b>Control Input;</b> Digital input. Connect to ground for high-side configuration. Connect to +5V or VBAT for low-side configuration.                                                                                        |

| 13  | VBAT    | <b>Supply Voltage</b> ; Connected to Battery Voltage with reverse protection diode and filter against EMC                                                                                                                     |

| 14  | CPC1H   | <b>Charge Pump;</b> For internal charge pump; connect a ceramic capacitor from this pin to CPC1L                                                                                                                              |

| 15  | CPC1L   | <b>Charge Pump;</b> For internal charge pump; connect a ceramic capacitor from this pin to CPC1H                                                                                                                              |

| 16  | CPC2H   | <b>Charge Pump;</b> For internal charge pump; connect a ceramic capacitor from this pin to CPC2L                                                                                                                              |

| 17  | CPC2L   | <b>Charge Pump;</b> For internal charge pump; connect a ceramic capacitor from this pin to CPC2L                                                                                                                              |

| 18  | CPOUT   | <b>Charge Pump Output</b><br>For internal charge pump; connect a ceramic storage capacitor from this pin to<br>VBAT. This pin should not be connected to other external components or used as a<br>supply for other circuits. |

| 19  | ТМ      | Test Pin; connect to GND                                                                                                                                                                                                      |

| 20  | EN      | Control Input; Digital input - 3.3V or 5.0V logic levels. Active high enable input.                                                                                                                                           |

| 21  | RESN    | Control Input; Digital input - 3.3V or 5.0V logic levels. Active low reset input.                                                                                                                                             |

| 22  | FAULTN  | Status Output; Open Drain output. In case not used, keep open.                                                                                                                                                                |

| 23  | TMO1    | Test Pin; connect to GND                                                                                                                                                                                                      |

| 24  | VDDAREF | Supply Voltage; Supplies analog circuits. Connect to 5.0V supply voltage                                                                                                                                                      |

| 25  | GNDAREF | Ground; Ground connection for analog circuits                                                                                                                                                                                 |

| 26  | GNDA    | Ground; Ground connection for analog circuits                                                                                                                                                                                 |

| 27  | VDDA    | Supply Voltage; Supplies analog circuits. Connect to 5.0V supply voltage                                                                                                                                                      |

| 28  | GNDD    | Ground; Ground connection for digital circuits                                                                                                                                                                                |

| 29  | VDDD    | Supply Voltage; Supplies digital circuits. Connect to 5.0V supply voltage                                                                                                                                                     |

| 30  | TMO2    | Test Pin; connect to GND                                                                                                                                                                                                      |

| 31  | CLK     | Clock Input; Main system clock.                                                                                                                                                                                               |

| 32  | CSN     | SPI Chip Select Input; Digital input - 3.3V or 5.0V logic levels.                                                                                                                                                             |

| 33  | SCK     | SPI Clock Input; Digital input - 3.3V or 5.0V logic levels.                                                                                                                                                                   |

#### **Pin Configuration**

| Pin            | Symbol | Function                                                                 |

|----------------|--------|--------------------------------------------------------------------------|

| 34             | SI     | SPI Input; Digital input - 3.3V or 5.0V logic levels.                    |

| 35             | SO     | SPI Output; Push Pull output compatible to 3.3 V and 5.0 V logic levels. |

| 36             | VIO    | IO Supply;<br>Connected to 3.3 V or 5.0 V supply                         |

| Cooling<br>Tab | g GND  | Cooling Tab; internally connected to GND.                                |

# 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

# Table 1 Absolute Maximum Ratings <sup>1)</sup>

$T_j = -40 \cdot C$  to +150 ·C; all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| Parameter                                         | Symbol                                                                    |              | Value | S                                       | Unit | Note /                                                  | Number       |  |

|---------------------------------------------------|---------------------------------------------------------------------------|--------------|-------|-----------------------------------------|------|---------------------------------------------------------|--------------|--|

|                                                   |                                                                           | Min.         | Тур.  | Max.                                    |      | Test Condition                                          |              |  |

| Voltages                                          | •<br>•                                                                    |              |       |                                         |      |                                                         |              |  |

| Supply Voltage                                    | $V_{BAT}$                                                                 | -0.3         | -     | 45                                      | V    | _                                                       | P_4.1.1      |  |

| Load Supply Voltage                               | V <sub>LSUP</sub>                                                         | -0.3         | -     | 45                                      | V    | -                                                       | P_4.1.2      |  |

| Digital, Analog, and IO Supply<br>Voltage         | $\begin{array}{c} V_{DDD}, V_{DDA}, \\ V_{DDAREF}, \\ V_{IO} \end{array}$ | -0.3         | -     | 5.5                                     | V    | with respect to<br>GNDD, GNDA,<br>GNDAREF, and<br>GNDPx | P_4.1.3      |  |

| Input Voltage; SCK, CSN, SI,<br>RESN, EN, TM, CLK | V <sub>INLV</sub>                                                         | -0.3         | -     | V <sub>DDD</sub> +<br>0.3 <sup>2)</sup> | V    |                                                         | P_4.1.4      |  |

| Input Voltage; HSLS0, HSLS1, and HSLS2            | V <sub>HSLSX</sub>                                                        | -0.3         | -     | V <sub>BAT</sub> +<br>0.3 <sup>3)</sup> | V    |                                                         | P_4.1.5      |  |

| Open Drain Output; FAULTN                         | V <sub>FAULTN</sub>                                                       | -0.3         |       | V <sub>IO</sub> +<br>0.3 <sup>2)</sup>  | V    |                                                         | P_4.1.9      |  |

| Push Pull Output; SO                              | V <sub>SO</sub>                                                           | -0.3         |       | V <sub>IO</sub> +<br>0.3 <sup>2)</sup>  | V    |                                                         | P_4.1.1<br>0 |  |

| Voltage; LOADx                                    | V <sub>LOAD</sub>                                                         | -2           | -     | V <sub>LSUPx</sub><br>+ 5 <sup>4)</sup> | V    | <i>I</i> <sub>l</sub>   < 1.6 A                         | P_4.1.1<br>1 |  |

| Voltage; CPOUT                                    | V <sub>CPOUT</sub>                                                        | VBAT-<br>0.3 | -     | 50                                      | V    |                                                         | P_4.1.1<br>2 |  |

| Maximum Voltage; CPC1L, CPC2L                     | V <sub>CPCxL</sub>                                                        | -0.3         | -     | 50                                      | V    |                                                         | P_4.1.1<br>3 |  |

| Maximum Voltage; CPC1H,<br>CPC2H                  | V <sub>CPCxH</sub>                                                        | -0.3         | -     | 50                                      | V    |                                                         | P_4.1.1<br>4 |  |

| Maximum Voltage; GNDPx                            | V <sub>GNDP</sub>                                                         | -0.3         |       | 1.0                                     | V    | with respect to GNDD                                    | P_4.1.1<br>5 |  |

| Maximum Voltage; GNDA,<br>GNDAREF                 | V <sub>GND</sub>                                                          | -0.3         |       | 0.3                                     | V    | with respect to GNDD                                    | P_4.1.1<br>6 |  |

| Currents                                          |                                                                           |              |       | <b>i</b>                                |      |                                                         |              |  |

| Output Current                                    | I <sub>LOAD</sub>                                                         | -1.6         |       | 1.6                                     | A    | DC <sup>5)</sup>                                        | P_4.1.1<br>7 |  |

| Output Current, FAULTN Pin                        | I <sub>FAULTN</sub>                                                       | 0            | -     | 20                                      | mA   | DC                                                      | P_4.1.1<br>8 |  |

| Output Current, SO Pin                            | I <sub>SO</sub>                                                           | -20          | -     | 20                                      | mA   | DC                                                      | P_4.1.1<br>9 |  |

#### Table 1 Absolute Maximum Ratings (cont'd)<sup>1)</sup>

$T_j$  = -40 ·C to +150 ·C; all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| Parameter                                          | Symbol                     |           | Value | s    | Unit     | Note /                                                                                 | Number       |

|----------------------------------------------------|----------------------------|-----------|-------|------|----------|----------------------------------------------------------------------------------------|--------------|

|                                                    |                            | Min. Typ. |       | Max. |          | Test Condition                                                                         |              |

| Input Current; SCK, CSN, SI,<br>RESN, EN, TM, CLK  | I <sub>IN</sub>            | -5        | -     | 5    | mA       | maximum<br>allowable<br>forward and<br>reverse current<br>through the ESD<br>structure | P_4.1.2<br>0 |

| Temperatures                                       | -                          |           |       |      | <u> </u> | -                                                                                      | •            |

| Junction Temperature                               | Tj                         | -40       | -     | 150  | °C       | continuous operation                                                                   | P_4.1.2<br>1 |

| Storage Temperature                                | T <sub>stg</sub>           | -55       | -     | 150  | °C       | -                                                                                      | P_4.1.2<br>2 |

| ESD Susceptibility                                 |                            |           |       |      |          |                                                                                        | 1            |

| ESD Resistivity to GND                             | V <sub>ESD</sub>           | -2        | -     | 2    | kV       | HBM <sup>6)</sup>                                                                      | P_4.1.2<br>3 |

| ESD Resistivity all pins <sup>7)</sup>             | V <sub>ESD</sub>           | -2        | -     | 2    | kV       | HBM <sup>6)</sup>                                                                      | P_4.1.2<br>4 |

| ESD Resistivity to GND                             | V <sub>ESD</sub>           | -500      | -     | 500  | V        | CDM <sup>8)</sup>                                                                      | P_4.1.2<br>5 |

| ESD Resistivity Pin 1, 18, 19, 36<br>(corner pins) | V <sub>ESD1,18,19,36</sub> | -750      | -     | 750  | V        | CDM <sup>8)</sup>                                                                      | P_4.1.2<br>6 |

1) Not subject to production test, specified by design.

2) Voltage must not exceed 5.5V

3) Voltage must not exceed 45.0V

4) VLOADx - VGNDPx and VLSUPx-VLOADx must not exceed 45.0V

5) Compliant to short circuit requirements according to AEC-Q100-012

6) ESD susceptibility, HBM according to EIA/JESD 22-A114B

- 7) Pin VBAT vs Pin CPC1H : +/- 1.5kV

- 8) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

#### Notes

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

# 4.2 Functional Range

#### Table 2Functional Range

| Parameter                                      | Symbol                              |      | Value | S                           | Unit | Note /                                                         | Number   |

|------------------------------------------------|-------------------------------------|------|-------|-----------------------------|------|----------------------------------------------------------------|----------|

|                                                |                                     | Min. | Тур.  | Max.                        |      | <b>Test Condition</b>                                          |          |

| Supply Voltage Range for Nominal Operation     | V <sub>BATnom</sub>                 | 8    | -     | 17                          | V    | -                                                              | P_4.2.1  |

| Extended Supply Voltage<br>Range for Operation | $V_{\rm BAT(ext)}, V_{\rm LSUP}$    | 5.5  | -     | 8                           | V    | Parameter<br>deviations<br>possible                            | P_4.2.2  |

| Extended Supply Voltage<br>Range for Operation | $V_{\rm BAT(ext)}, \\ V_{\rm LSUP}$ | 17   | -     | 40                          | V    | Parameter<br>deviations<br>possible                            | P_4.2.3  |

| VBAT Supply Voltage transients slew rate       | $dV_{BAT}/dt$                       | -1   | -     | 1                           | V/µs | -                                                              | P_4.2.4  |

| Load Supply Voltage                            | V <sub>LSUP</sub>                   | 8    | -     | V <sub>BAT</sub> +0.3       | V    | -                                                              | P_4.2.5  |

| Load Supply Voltage transients slew rate       | dV <sub>LSUP</sub> /<br>dt          | -1   | -     | 1                           | V/µs | -                                                              | P_4.2.6  |

| Digital Supply Voltage                         | $V_{\rm VDDD}$                      | 4.75 |       | 5.25                        | V    |                                                                | P_4.2.7  |

| Analog Supply Voltage                          | $V_{\rm VDDA,}$                     | 4.75 |       | 5.25                        | V    |                                                                | P_4.2.8  |

| Ground Offset Voltage;<br>GNDA, GNDAREF        | V <sub>GND</sub>                    | -0.1 |       | 0.1                         | V    | with respect to GNDD                                           | P_4.2.9  |

| IO Supply Voltage                              | V <sub>IO</sub>                     | 3.0  |       | 5.25                        | V    |                                                                | P_4.2.10 |

| Voltage (static); LOADx                        | V <sub>LOADx</sub>                  | -0.3 | -     | V <sub>LSUPx</sub> +<br>0.3 | V    |                                                                | P_4.2.11 |

| Voltage (dynamic); LOADx                       | $V_{LOADx}$                         | -2   | -     | V <sub>LSUPx</sub> + 5      | V    | <i>I</i> <sub>I</sub>   < 1.6 A                                | P_4.2.12 |

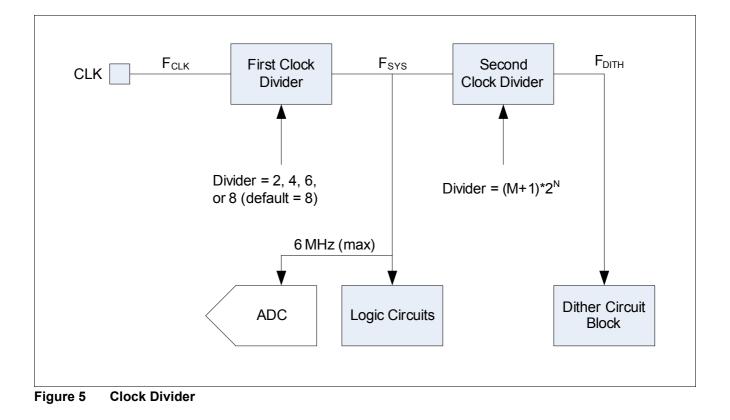

| System Clock Frequency                         | F <sub>SYS</sub>                    | 4    |       | 6                           | MHz  | F <sub>SYS</sub> = F <sub>CLK</sub> /<br>F <sub>SYS</sub> _div | P_4.2.13 |

| CLK pin Frequency                              | F <sub>CLK</sub>                    | 8    |       | 40                          | MHz  |                                                                | P_4.2.14 |

| SPI Clock Frequency                            | F <sub>SCK</sub>                    |      |       | 8                           | MHz  |                                                                | P_4.2.15 |

| LOADx PWM Frequency                            | FLOAD                               | 100  |       | 4000                        | Hz   | dependent on<br>solenoid<br>characteristics                    | P_4.2.16 |

| Junction Temperature                           | T <sub>i</sub>                      | -40  | -     | 150                         | °C   | -                                                              | P_4.2.17 |

1) VLSUPx - GNDD must not exceed 45.0V.

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### 4.3 Thermal Resistance

#### Table 3Thermal Resistance

| Parameter                      | Symbol            | Values |      |      | Unit | Note /         | Number  |

|--------------------------------|-------------------|--------|------|------|------|----------------|---------|

|                                |                   | Min.   | Тур. | Max. |      | Test Condition |         |

| Junction to Case <sup>1)</sup> | R <sub>thJC</sub> | -      | -    | 2    | K/W  | -              | P_4.3.1 |

| Junction to Ambient            | R <sub>thJA</sub> | -      | 15   | -    | K/W  | 2)             | P_4.3.2 |

1) Not subject to production test, specified by design.

Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70 mm Cu, 2 × 35 mm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

# 5 Power Supply

#### 5.1 Overview

The TLE82453 has multiple supply pins. The internal circuits are powered by three +5.0 V supply pins; VDDD, VDDA, and VDDAREF; and by one battery pin, VBAT. A separate supply pin, VIO, can be connected to either a 3.3V or 5V supply depending on the logic levels of the interfaced microcontroller I/O signals. The device includes a charge pump circuit which generates a supply voltage greater than VBAT.

# 5.2 Battery Supply (VBAT)

This pin is the supply for the internal charge pump and must be connected to the reverse polarity protected battery voltage supply. For correct operation the voltage on this pin must not be lower than the voltage on any of the LSUPx pins. This pin is also used by the overvoltage detection circuit.

# 5.3 Load Supplies (LSUP2, LSUP1, LSUP0)

These pins are the supply pins for the three output stages. If the voltage on one of these pins is lower than the LSUP under voltage threshold, the respective power stage is disabled and the respective UVx fault bit is set in the DIAGNOSIS register. The LSUP pins of unused channels must be connected to VBAT.

# 5.4 Analog Supplies (VDDA and VDDAREF)

The VDDA pin is the supply for the internal analog circuits such as the amplifiers and analog-to-digital converters. The VDDAREF pin is the supply for the internal bandgap references. An externally regulated 5.0 VDC +/- 5% supply must be connected to these pins. A ceramic capacitor with a value of 100nF must be connected between each of these pins and ground near the IC.

These pins are monitored by a pair of internal comparators. The internal logic circuits are held in a reset state if the voltage on either of these pins is less than the threshold VDDA\_UV and VDDAREF\_UV.

# 5.5 Digital Supply (VDDD)

This pin is the supply for all of the internal logic circuitry. An externally regulated 5.0 VDC +/- 5% supply must be connected to this pin. A ceramic capacitor with a value of 100nF must be connected between this pin and ground near the IC.

This pin is monitored by an internal comparator. The internal logic circuits are held in a reset state if the voltage on this pin is less than the threshold VDDD\_UV.

# 5.6 I/O Supply (VIO)

This pin is used to supply the pins that interface with the external microcontroller. This pin must be connected to a supply with the same voltage, 3.3V or 5.0V, that is used to supply the peripherals of the microcontroller.

#### 5.7 Power On Reset

An internal power on reset circuit holds the device in a reset state if any of the supplies VDDD, VDDA, or VDDAREF is below the respective undervoltage detection threshold. The device is also held in reset if the clock signal on the CLK pin is missing or the clock frequency is too low when the CLK pin watchdog is enabled. The power on reset is released a fixed power on reset time ( $t_{POR}$ ) after all of these supplies are above their respective threshold voltage. The SPI interface can be accessed after the power on reset time.

The fault bit "RST" in the DIAGNOSIS register is set whenever the device exits the reset state. This bit is cleared automatically whenever the DIAGNOSIS register is accessed. The microcontroller can use this bit to determine if an internal or external reset has occurred.

# 5.8 Charge Pump

In order to provide low Rdson of the high-side mosfet transistors, a charge pump is used to drive the internal gate voltage above VBAT. The device uses a common charge pump for all channels. The charge pump uses the battery voltage supply connected to the VBAT pin. The charge pump output voltage at the CPOUT pin is regulated to typically 11V above the voltage at the VBAT pin.

The charge pump circuit requires three external capacitors. A reservoir capacitor with a recommended value of 220nF must be connected between the CPOUT pin and the VBAT pin. Two pump capacitors with recommended values of 27nF must be connected between the CPC1L and CPC1H pins and also between the CPC2L and CPC2H pins. A built in supervisor circuit checks if the charge pump output voltage is sufficient to control the high-side mosfet transistors. If the VCPOUT voltage is less than the charge pump undervoltage threshold, the output transistors are disabled and the CPUV fault flag is set in the DIAGNOSIS register. A separate CPW (Charge Pump Warning) fault bit in the DIAGNOSIS register is set if the VCPOUT voltage is below the CP warning threshold voltage. The device will continue to operate normally when the VCPOUT voltage is between the CPW threshold and the CPUV threshold, however the current control accuracy may be outside of the specification limits.

# 5.9 Sleep Mode

If any one of the VDDD, VDDA, and VDDAREF voltage supplies is below the respective undervoltage threshold, the device enters sleep mode. The current drawn into the VBAT pin is reduced during this mode of operation. Sleep mode is automatically exited when all of the VDDD, VDDA, and VDDAREF supply pins are above the respective undervoltage threshold.

# 5.10 Power Supply Modes

The following table describes the operation of the device with all possible power supply modes of VBAT, VCPOUT, VDDD, VDDA, VDDAREF, and VIO. The "X" symbol means that the state of this supply does not effect the result (can be either supplied or not supplied) in the specific case.

| VDDD                      | < VDDx_UV | х         | х         | > VDDx_UV | > VDDx_UV          | > VDDx_UV               | > VDDx_UV                                    | > VDDx_UV                      | > VDDx_UV          | > VDDx_UV          | > VDDx_UV              | > VDDx_UV          |

|---------------------------|-----------|-----------|-----------|-----------|--------------------|-------------------------|----------------------------------------------|--------------------------------|--------------------|--------------------|------------------------|--------------------|

| VDDA                      | х         | < VDDx_UV | х         | > VDDx_UV | > VDDx_UV          | > VDDx_UV               | > VDDx_UV                                    | > VDDx_UV                      | > VDDx_UV          | > VDDx_UV          | > VDDx_UV              | > VDDx_UV          |

| VDDAREF                   | х         | х         | < VDDx_UV | > VDDx_UV | > VDDx_UV          | > VDDx_UV               | > VDDx_UV                                    | > VDDx_UV                      | > VDDx_UV          | > VDDx_UV          | > VDDx_UV              | > VDDx_UV          |

| RESN                      | х         | х         | х         | LOW       | HIGH               | HIGH                    | HIGH                                         | HIGH                           | HIGH               | HIGH               | HIGH                   | HIGH               |

| CLK                       | х         | х         | х         | х         | TCLK ><br>TCLK_MSS | TCLK ><br>TCLK_MSS      | TCLK <<br>TCLK_MSS                           | TCLK <<br>TCLK_MSS             | TCLK <<br>TCLK_MSS | TCLK <<br>TCLK_MSS | TCLK <<br>TCLK_MSS     | TCLK <<br>TCLK_MSS |

| VIO                       | х         | x         | x         | х         | > 3.0V             | > 3.0V                  | 0V                                           | > 3.0V                         | > 3.0V             | > 3.0V             | > 3.0V                 | > 3.0V             |

| WDEN                      | х         | х         | х         | х         | LOW                | HIGH                    | HIGH                                         | HIGH                           | HIGH               | HIGH               | HIGH                   | HIGH               |

| EN                        | х         | х         | х         | х         | х                  | х                       | HIGH                                         | LOW                            | HIGH               | HIGH               | HIGH                   | HIGH               |

| VCPOUT -<br>VBAT          | х         | х         | х         | х         | х                  | x                       | > CPUV                                       | х                              | < CPUV             | > CPUV             | > CPUV                 | > CPUV             |

| VBAT                      | х         | х         | х         | х         | х                  | x                       | < VBATOV                                     | х                              | х                  | > VBATOV           | < VBATOV               | < VBATOV           |

| VLSUPx                    | х         | х         | х         | х         | х                  | х                       | > VLSUPUV                                    | х                              | х                  | х                  | < VLSUPUV              | > VLSUPUV          |

| Sleep Mode                | YES       | YES       | YES       | NO        | NO                 | NO                      | NO                                           | NO                             | NO                 | NO                 | NO                     | NO                 |

| Watchdog<br>Fault         | NO        | NO        | NO        | NO        | NO                 | YES                     | NO                                           | NO                             | NO                 | NO                 | NO                     | NO                 |

| Channel<br>Operational    | NO        | NO        | NO        | NO        | NO                 | NO                      | YES                                          | NO                             | NO                 | NO                 | NO<br>(Channel X only) | YES                |

| SPI<br>Functional         | NO        | NO        | NO        | NO        | YES                | NO<br>Response is ICVID | INPUT – YES<br>Response is 0000 <sub>H</sub> | YES                            | YES                | YES                | YES                    | YES                |

| Diagnostics<br>Functional | NO        | NO        | NO        | NO        | NO                 | NO                      | YES                                          | NO Load faults<br>are detected | YES                | YES                | YES                    | YES                |

| FAULTN                    | LOW       | LOW       | LOW       | LOW       | LOW                | LOW                     | Undefined                                    | LOW (1)                        | LOW                | LOW                | LOW (4)                | HIGH               |

| RST bit                   | HIGH (2)  | HIGH (2)  | HIGH (2)  | HIGH (2)  | HIGH (3)           | HIGH (3)                | unchanged                                    | unchanged                      | unchanged          | unchanged          | unchanged              | unchanged          |

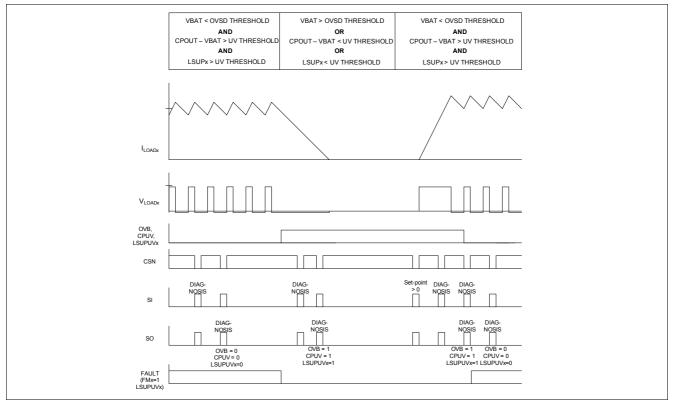

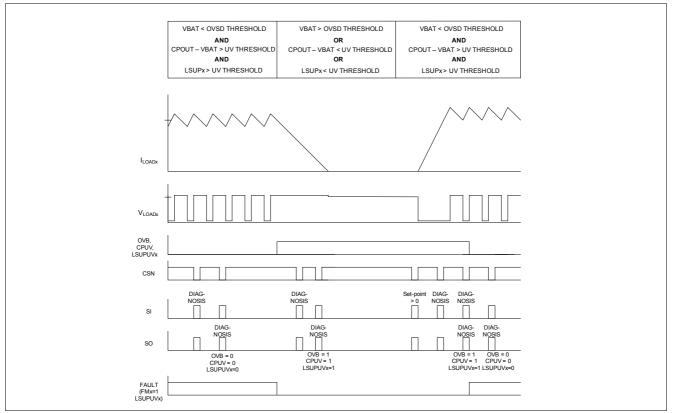

#### Figure 3 Power Supply Mode Diagram

- 1. The FAULTN pin is LOW if the FME fault mask bit is set to 1

- 2. The RST bit in the DIAGNOSIS register will be set after the device exits the reset state

- 3. A missing CLK signal will result in a reset only if the CLK Watchdog has been enabled.

- 4. The FAULTN pin is LOW if the FMx fault mask bit is set to 1

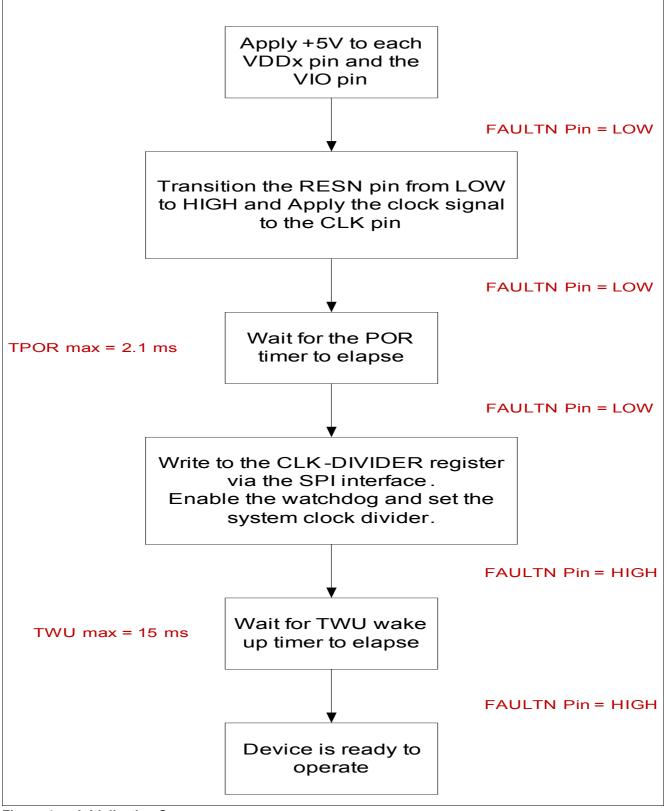

#### 5.11 Initialization

The following figure illustrates the initialization sequence for the device after power-up.

#### **Power Supply**

Figure 4 Initialization Sequence

# 5.12 Electrical Characteristics

#### Table 4 Electrical Characteristics: Power Supply

$V_{\text{BAT}}$  = 8 V to 17 V,  $V_{\text{DDx}}$  = 4.75 V to 5.25 V,  $T_{\text{j}}$  = -40 ·C to +150 ·C, CPC1 and CP2 = 27nF CPCOUT = 220nF, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| Parameter                                           | Symbol                 |                     | Value | Values                                |     | Note /                                                                                                                                                             | Number    |

|-----------------------------------------------------|------------------------|---------------------|-------|---------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                     |                        | Min.                | Тур.  | Max.                                  |     | <b>Test Condition</b>                                                                                                                                              |           |

| VBAT Current Consumption normal mode                | I <sub>VBAT</sub>      | -                   |       | 10                                    | mA  | all channels active                                                                                                                                                | P_6.12.1  |

| VBAT Current Consumption<br>sleep mode              | $I_{\rm VBAT\_SLP}$    | -                   |       | 8                                     | μA  |                                                                                                                                                                    | P_6.12.2  |

| VDDD Current Consumption                            | $I_{\rm VDDD}$         | -                   |       | 20                                    | mA  |                                                                                                                                                                    | P_6.12.3  |

| VDDA Current Consumption                            | I <sub>VDDA</sub>      | -                   |       | 13                                    | mA  |                                                                                                                                                                    | P_6.12.4  |

| VDDAREF Current<br>Consumption                      | I <sub>VDDAREF</sub>   | -                   |       | 4                                     | mA  |                                                                                                                                                                    | P_6.12.5  |

| VIO Current Consumption                             | I <sub>VIO</sub>       | -                   |       | 1                                     | mA  | CSN=VIO=5.25V                                                                                                                                                      | P_6.12.6  |

| Undervoltage reset (internally generated) - VDDA    | V <sub>DDA_UV</sub>    | 3.8                 |       | 4.3                                   | V   | VDDA decreasing                                                                                                                                                    | P_6.12.7  |

| Undervoltage reset (internally generated) - VDDAREF | V <sub>DDAREF_UV</sub> | 3.8                 |       | 4.3                                   | V   | VDDAREF<br>decreasing                                                                                                                                              | P_6.12.8  |

| Undervoltage reset (internally generated) - VDDD    | V <sub>DDD_UV</sub>    | 3.8                 |       | 4.3                                   | V   | VDDD<br>decreasing                                                                                                                                                 | P_6.12.9  |

| Undervoltage hysteresis                             | V <sub>UV_HYS</sub>    |                     | 150   |                                       | mV  |                                                                                                                                                                    | P_6.12.10 |

| LSUP undervoltage threshold                         |                        | 4.5                 |       | 5.5                                   | V   |                                                                                                                                                                    | P_6.12.11 |

| Missing CLK clock detection time                    | T <sub>CLK_MSS</sub>   |                     |       | 10                                    | μs  |                                                                                                                                                                    | P_6.12.12 |

| Power On Reset time                                 | T <sub>POR</sub>       |                     |       | 2.1                                   | ms  | Logic circuits are<br>functional after<br>POR timer                                                                                                                | P_6.12.13 |

| Power-on wake up time                               | T <sub>wu</sub>        |                     |       | 15                                    | ms  | Timer starts when<br>all supplies are<br>above the UV<br>thresholds and<br>RESN pin is high<br>$F_{CLK} = 8$ MHz.<br>Output stages<br>functional after<br>$T_{WU}$ | P_6.12.14 |

| Charge Pump                                         | 1                      |                     |       | I                                     |     | 1 -                                                                                                                                                                | 1         |

| Charge pump voltage                                 | V <sub>CP_OUT</sub>    | V <sub>BAT</sub> +8 |       | V <sub>BAT</sub><br>+13 <sup>1)</sup> | V   |                                                                                                                                                                    | P_6.12.15 |

| Charge pump <mark>clock</mark><br>frequency         | F <sub>CP</sub>        |                     | 65    |                                       | KHz | $F_{SYS}$ = 6 MHz <sup>2)</sup>                                                                                                                                    | P_6.12.16 |

| Charge pump warning threshold voltage               | V <sub>CPOUT_W</sub>   | V <sub>BAT</sub> +7 |       | V <sub>BAT</sub> +<br>8.5             | V   |                                                                                                                                                                    | P_6.12.17 |

#### Table 4 Electrical Characteristics: Power Supply

$V_{\text{BAT}}$  = 8 V to 17 V,  $V_{\text{DDx}}$  = 4.75 V to 5.25 V,  $T_{\text{j}}$  = -40 ·C to +150 ·C, CPC1 and CP2 = 27nF CPCOUT = 220nF, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| Parameter                                  | Symbol                |                          | Values | S                        | Unit | Note /         | Number    |

|--------------------------------------------|-----------------------|--------------------------|--------|--------------------------|------|----------------|-----------|

|                                            |                       | Min.                     | Тур.   | Max.                     |      | Test Condition |           |

| Charge pump undervoltage threshold voltage | V <sub>CPOUT_UV</sub> | V <sub>BAT</sub><br>+4.5 |        | V <sub>BAT</sub><br>+5.5 | V    |                | P_6.12.18 |

| Charge pump overvoltage clamp              | V <sub>CPOUT_OV</sub> |                          | 48.5   |                          | V    |                | P_6.12.19 |

1) Will not exceed VCPOUT\_OV

2) Parameter not subject to production test, specified by design

Attention: Voltage Ratings for Charge Pump caps: CPC1/CPC2: Vmin=VBATmax + 10V, CCPOUT: Vmin=VBATmax + 16V

# 6 Input / Output

# 6.1 I/O Description

The CLK pin must be connected to a precise clock signal. This clock is used by the internal analog to digital converters and by the internal logic. A small internal pull down current will keep the voltage on this pin near ground when the pin is open. The device includes a programmable divider to generate the internal system clock from the CLK pin signal. This divider ratio is programmed in the CLK-DIVIDER register by the SPI interface. The output stages cannot be enabled until this field has been written.

An internal watchdog circuit will hold the device in an internal reset state if the delay between rising edges on the CLK pin is greater than the threshold time,  $T_{CLK\_MSS}$ . The watchdog is initially disabled when the device exits the reset state. The watchdog is enabled by setting the WDEN bit in the CLK-DIVIDER register.

Until the watchdog is enabled, the output stages are disabled. Once the watchdog function is enabled, a missing CLK signal will set the Watchdog Status Bit in the IC VERSION register, set the FAULTN pin to a logic low state, disable the output stages, and cause the device to enter an internal reset state. In this mode of operation, the SPI response from the device will always be the response to a IC VERSION register read command. To exit this mode of operation, the device must be reset externally by the RESN pin.

The EN pin is used to enable / disable the output stages. If the EN pin is low, all of the channels are disabled and (when the fault mask bit FME = 1) the FAULTN pin is pulled low. The SPI interface remains functional, however. When the EN pin is low, the EN bits in the SET-POINT registers are cleared. The EN pin can be connected to a general purpose output pin of the microcontroller or to an output of a safing circuit.

The RESN pin is the reset input for the device. If the RESN pin is low, the device is held in an internal reset state, the FAULTN pin is held low, and the SPI interface is disabled. An internal pull down current source will hold the RESN pin low in case the pin is open.

The FAULTN pin is an open drain output. This pin is pulled low when a fault is detected by the diagnosis circuit or when the device is in an internal reset state. An external resistor should be connected between this pin and the VIO supply.

The SI, SO, CSN, and SCLK pins comprise the SPI interface. See Sections 11 and 12 for details.

#### Input / Output

Input / Output

# 6.2 Electrical Characteristics I/O

#### Table 5 Electrical Characteristics:

$V_{\text{BAT}}$  = 8 V to 17 V,  $V_{\text{DDx}}$  = 4.75 V to 5.25 V,  $T_{\text{j}}$  = -40 ·C to +150 ·C, all voltages with respect to ground (GNDD), positive current flowing into pin

(unless otherwise specified)

| Parameter                                     | Symbol              |                          | Value    | s               | Unit | Note /                                                     | Number  |

|-----------------------------------------------|---------------------|--------------------------|----------|-----------------|------|------------------------------------------------------------|---------|

|                                               |                     | Min.                     | Тур.     | Max.            |      | Test Condition                                             |         |

| Control Inputs EN, RESN, O                    | CSN, SI, SCH        | K, CLK                   |          | 1               |      |                                                            |         |

| Input threshold - low                         | $V_{\rm IN\_L}$     | 0.8                      |          |                 | V    | $V_{\rm IN}$ increasing                                    | P_5.2.1 |

| Input threshold - high                        | V <sub>IN_H</sub>   |                          |          | 2.0             | V    | $V_{\rm IN}$ decreasing                                    | P_5.2.2 |

| Input hysteresis                              | V <sub>IN_HYS</sub> |                          | 50       |                 | mV   |                                                            | P_5.2.3 |

| Pull up current - CSN                         | I <sub>PU</sub>     | -50                      |          | -10             | μA   |                                                            | P_5.2.4 |

| Pull down current - EN, SI,<br>SCK, CLK, RESN | I <sub>PD</sub>     | 10                       |          | 50              | μA   |                                                            | P_5.2.5 |

| Output SO                                     |                     | <b>I</b>                 | <b>I</b> | <b>I</b>        |      |                                                            | L       |

| Output low-level voltage                      | $V_{\rm SO_L}$      | 0                        |          | 0.5             | V    | I <sub>SO</sub> = 0.5mA                                    | P_5.2.6 |

| Output high-level voltage                     | V <sub>SO_H</sub>   | V <sub>IO</sub> -<br>0.5 |          | V <sub>IO</sub> | V    | I <sub>SO</sub> = -0.5mA,<br>3.0V < V <sub>IO</sub> < 5.5V | P_5.2.7 |

| Output tri-state leakage current              | I <sub>SO_OFF</sub> | -10                      |          | 10              | μA   | V <sub>CSN</sub> =V <sub>IO</sub>                          | P_5.2.8 |

| Output FAULTN                                 |                     |                          |          |                 |      |                                                            |         |

| Output low-level voltage                      | $V_{FLT\_L}$        | 0                        |          | 0.4             | V    | I <sub>FLT</sub> = 2mA                                     | P_5.2.9 |

# 7 Power Stages

#### 7.1 Overview

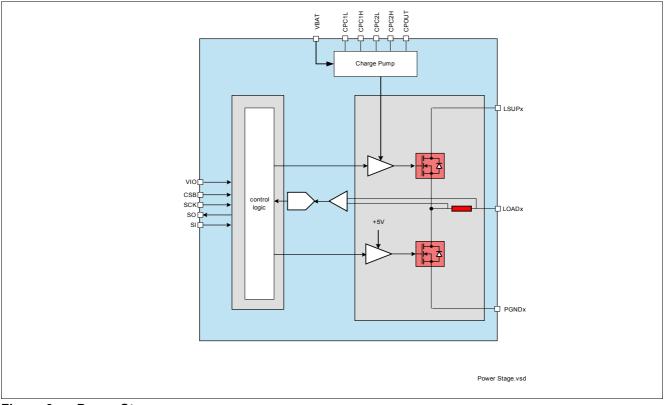

There are three output channels implemented in this device. The output power stages of each channel consists of a half bridge made up of two n-channel DMOS transistors and a current sensing resistor. An internal charge pump generates the voltage required to switch the n-channel DMOS high-side switches. The switches are protected from external failures by built in over current and over temperature detection circuits.

The half bridge arrangement allows the use of active freewheeling, which reduces the power dissipation of the device. The arrangement also allows each channel to be individually programmed for lowside or highside drive. The output current slew rate of the power stages can be programmed to one of three values by programming the CONFIGURATION register by SPI.

# 7.2 Channel Disabled

When the channel is disabled, both transistors of the half bridge are turned off. The output stage is in a high output impedance state in this condition.

# 7.3 Channel Enabled

When a channel is configured for lowside operation, the lowside DMOS switch is the "drive" switch and the highside DMOS switch is the "recirculation" switch. Likewise, when a channel is configured for highside operation, the highside DMOS switch is the "drive" switch and the lowside switch is the "recirculation" switch. In normal operation, the "drive" switch is turned on and off with the duty cycle needed to regulate the solenoid current at the target value. During the time that the "drive" switch is turned off, the device is in active freewheeling mode. The "recirculation" switch is turned on in this mode to reduce the voltage drop across the device during recirculation.

#### **Power Stages**

The transistors are controlled in a way that prevents shoot through current during switching, that is the control logic prevents the simultaneous activation of both the "drive" switch and the "recirculation" switch.

#### 7.4 Configuration of Channels

The pins HSLS0, HSLS1, and HSLS2 are used to configure each channel for highside or lowside operation. The pin must be connected to ground for highside operation and to VBAT or + 5V for lowside operation. The configuration of each channel can be verified by reading the CONFIGURATION register via SPI.

**Power Stages**

# 7.5 Electrical Characteristics Power Stages

#### Table 6 Electrical Characteristics: Power Stages

$V_{\text{BAT}}$  = 8 V to 17 V,  $V_{\text{DDx}}$  = 4.75 V to 5.25 V,  $T_j$  = -40 ·C to +150 ·C, all voltages with respect to ground (GNDD), positive current flowing into pin (unless otherwise specified)

| Parameter                              | Symbol                                     |      | Values            | 5    | Unit | Note /                                                                                                           | Number   |

|----------------------------------------|--------------------------------------------|------|-------------------|------|------|------------------------------------------------------------------------------------------------------------------|----------|

|                                        |                                            | Min. | Тур.              | Max. |      | Test Condition                                                                                                   |          |

| LSUPx leakage current                  | I <sub>LSUP_LKG</sub>                      | -    |                   | 150  | μA   | set-point = 0mA<br>$8V < V_{LSUP} < V_{BAT}$<br>+ 0.3V                                                           | P_7.6.1  |

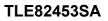

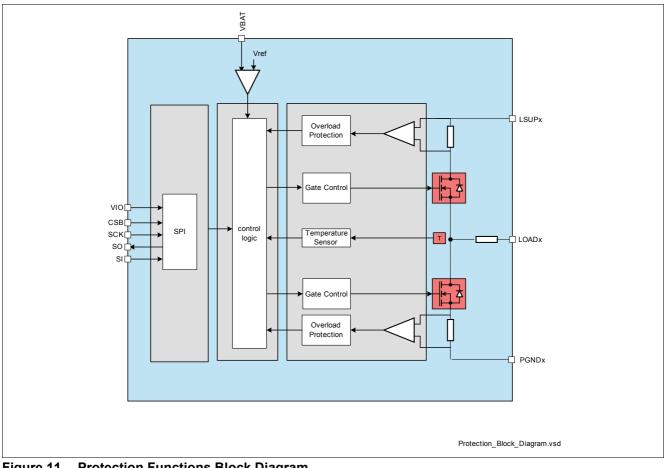

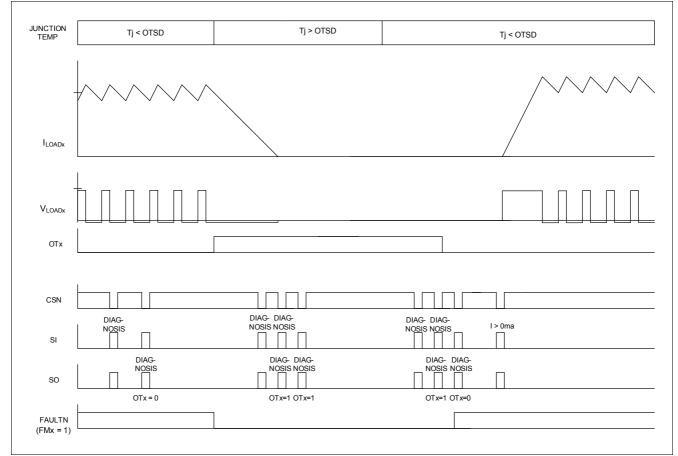

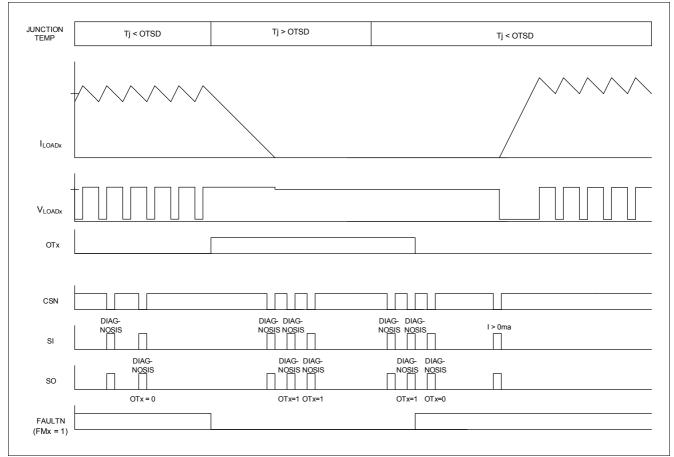

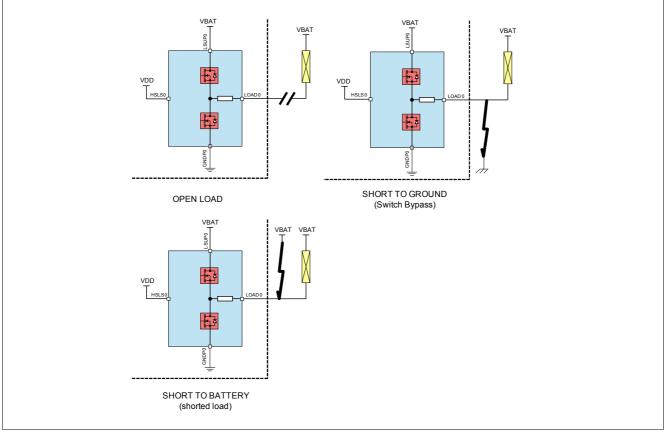

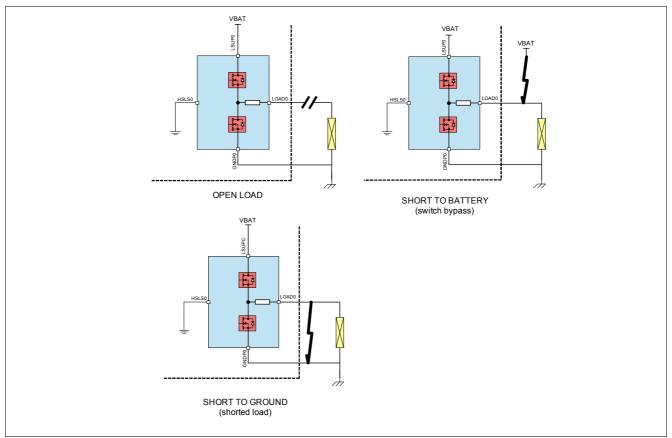

| LSUPx leakage current in<br>sleep mode | $I_{\text{LSUP}_{\text{LG}}_{\text{SLP}}}$ | -    |                   | 50   | μA   | Sleep mode All<br>VDDx=0V                                                                                        | P_7.6.2  |