# TLE7809G

Integrated double low-side switch, high-side/LED driver, hall supply, wake-up inputs and LIN communication with embedded MCU (16kB Flash)

**Automotive Power**

#### **Table of Contents**

# **Table of Contents**

|                                                            | Table of Contents                                                                                                                                                                                  | 2                                    |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1                                                          | Overview                                                                                                                                                                                           | 3                                    |

| 2                                                          | Block Diagram                                                                                                                                                                                      | 5                                    |

| 3                                                          | Pin Definitions and Functions                                                                                                                                                                      | 6                                    |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br>4.5.3 | Operating Modes SBC Standby Mode SBC Active Mode SBC Active Mode "LIN Sleep" LIN Receive-Only Mode ("LIN RxD-Only") Power Saving Modes SBC Sleep Mode SBC Stop Mode SBC Stop Mode with Cyclic Wake | . 10<br>. 10<br>. 11<br>. 12<br>. 12 |

| 5                                                          | LIN Transceiver                                                                                                                                                                                    | . 15                                 |

| 6<br>6.1<br>6.1.1<br>6.2<br>6.2.1                          | ADC Measurement Interface  Voltage Measurement                                                                                                                                                     | . 16<br>. 16<br>. 17                 |

| 7                                                          | Low Dropout Voltage Regulator                                                                                                                                                                      | . 18                                 |

| 8                                                          | SPI (Serial Peripheral Interface)                                                                                                                                                                  | . 19                                 |

| 9                                                          | Reset Behavior and Window Watchdog                                                                                                                                                                 | . 25                                 |

| 10                                                         | Monitoring / Wake-Up Inputs MON1 5 and Wake-Up Event Signalling                                                                                                                                    | . 26                                 |

| 11                                                         | Low Side Switches                                                                                                                                                                                  | . 28                                 |

| 12                                                         | Supply Output for Hall Sensor Supply                                                                                                                                                               | . 29                                 |

| 13                                                         | High-Side Switch as LED Driver (HS-LED)                                                                                                                                                            | . 30                                 |

| 14                                                         | General Purpose I/Os (GPIO)                                                                                                                                                                        | . 31                                 |

| 15                                                         | Error Interconnect (ERR)                                                                                                                                                                           | . 32                                 |

| 16<br>16.1<br>16.2<br>16.3<br>16.4                         | General Product Characteristics Absolute Maximum Ratings Functional Range Thermal Resistance Electrical Characteristics                                                                            | . 34<br>. 34                         |

| 17                                                         | Timing Diagrams                                                                                                                                                                                    | . 44                                 |

| 18<br>18.1<br>18.2<br>18.3<br>18.4                         | Application Information Application Diagram Hints for Unused Pins Flash Program Mode via LIN-Fast-Mode Thermal Resistance                                                                          | . 48<br>. 48<br>. 49                 |

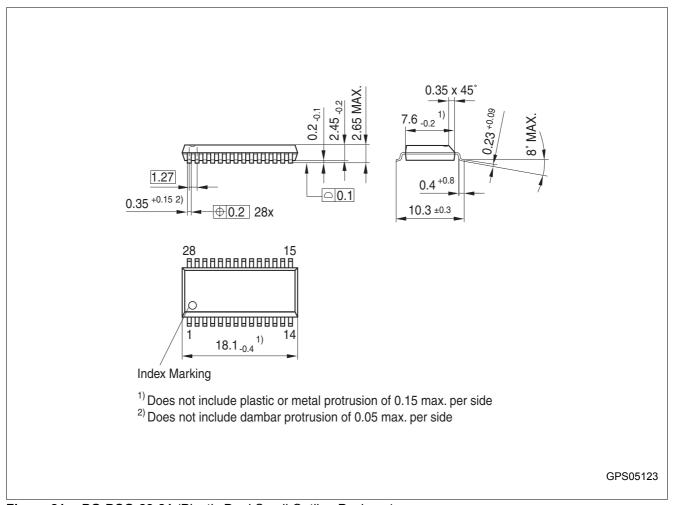

| 19                                                         | Package Outlines                                                                                                                                                                                   | . 50                                 |

| 20                                                         | Revision History                                                                                                                                                                                   | . 51                                 |

2

Integrated double low-side switch, high-side/LED driver, hall supply, wake-up inputs and LIN communication with embedded MCU (16kB Flash)

**TLE7809G**

#### 1 Overview

#### Relay Driver - System Basis Chip

- Low-Dropout Voltage Regulator (LDO)

- LIN Transceiver

- Standard 16-bit SPI-Interface

- 2 x Low-Side Switches, e.g. as Relay Driver

- 2 × Supply e.g. for Hall Sensor Supply / LED Driver

- 5 × High-Voltage Wake-Up Inputs

- Programmable. Window Watchdog & Power Saving Modes

- Power-On and Undervoltage Reset Generator

- · Overtemperature Protection

- Short Circuit Protection

# 8-bit Microcontroller

- Compatible to 8051 μC Core

- Two clocks per machine cycle

- 8kByte Boot ROM for test and Flash routines

- · LIN Bootloader (Boot ROM)

- 256 Byte RAM / 512 Byte XRAM

- · 16kByte Flash Memory for Program Code & Data

- On-Chip Oscillator

- Power Saving Modes (slow-down & idle mode)

- Programmable Watchdog Timer

- 10-bit A/D Converter, e.g. for Temperature &  $V_{\rm bat}$ -Measurement

- Three 16-bit Timers & Capture/Compare Unit

- · General Purpose I/Os, e.g. with PWM Functionality

- On-Chip Debug Support (JTAG)

- UART and Synchronous Serial Channel (SSC respective SPI)

#### **General Characteristics**

- Package PG-DSO-28-21

- Temperature Range  $T_{\rm J}$ : -40 °C up to 125 °C (for industrial applications)

- Green Package (RoHS compliant)

| © Infineon PC-DSO-28 |

|----------------------|

|----------------------|

PG-DSO-28-21

| Туре     | Package      | Marking  |

|----------|--------------|----------|

| TLE7809G | PG-DSO-28-21 | TLE7809G |

Overview

#### **Description**

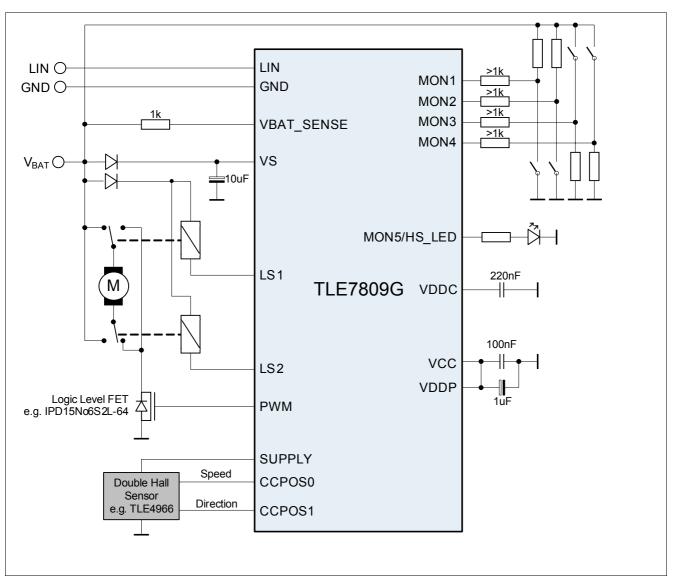

This single-packaged solution incorporates an 8-bit state-of-the-art microcontroller compatible to the standard 8051 core with On-Chip Debug Support (OCDS), and a System-Basis-Chip (SBC). The SBC is equipped with LIN transceiver, low-dropout voltage regulator (LDO) as well as two low-side switches (relay driver) and a high-side driver e.g. for driving LEDs. An additional supply, e.g. to supply hall sensors (TLE 4966) is also available.

For Micro Controller Unit (MCU) supervision and additional protection of the circuit a programmable window watchdog circuit with a reset feature, supply voltage supervision and integrated temperature sensor is implemented on the SBC.

Microcontroller and LIN module offer low power modes in order to support terminal 30 connected automotive applications. A wake-up from the low power mode is possible via a LIN bus message or wake-up inputs.

This integrated circuit is realized as Multi-Chip-Module (MCM) in a PG-DSO-28-21 package, and is designed to withstand the severe conditions of industrial applications.

Note: A detailed description of the 8-bit microcontroller XC866 can be found in a dedicated User's Manual and Data Sheet.

Data Sheet 4 Rev. 3.01, 2008-04-15

**Block Diagram**

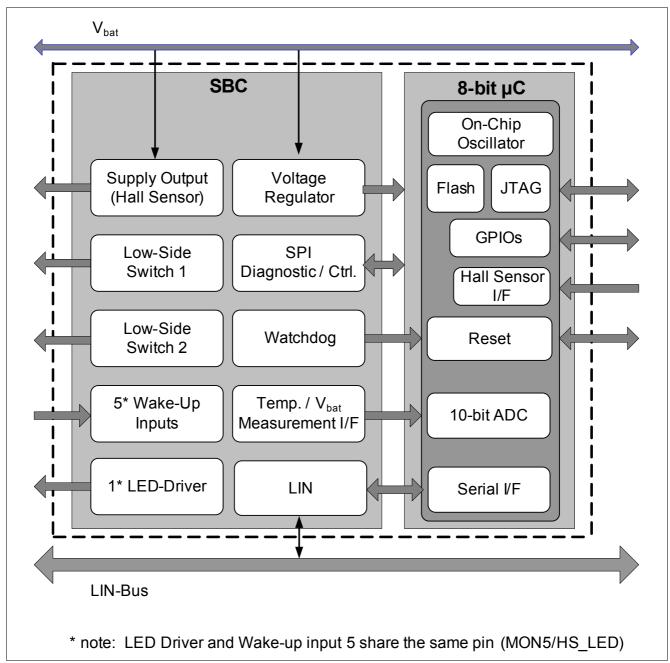

# 2 Block Diagram

Figure 1 Functional Block Diagram (Module Overview)

## **Pin Definitions and Functions**

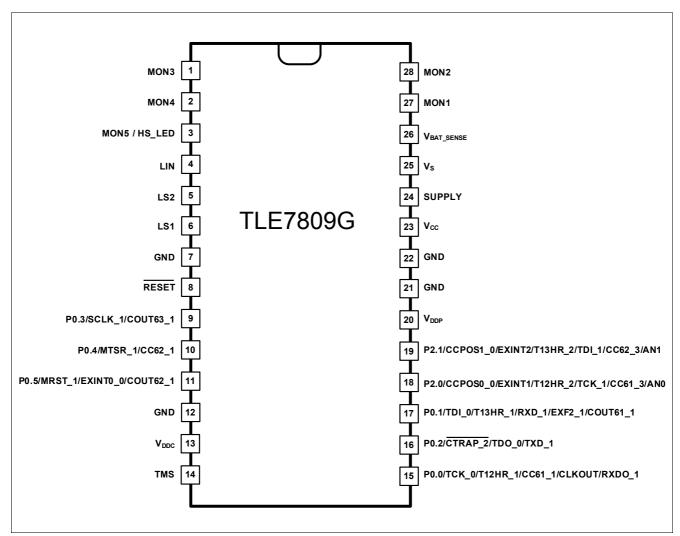

# 3 Pin Definitions and Functions

Figure 2 Pin Configuration

| Pin No. | Symbol           | Function                                                                            |

|---------|------------------|-------------------------------------------------------------------------------------|

| 27      | MON1,            | Monitoring / Wake-Up Inputs; bi-level sensitive inputs used to monitor signals for  |

| 28      | MON2,            | example coming from an external switch panel                                        |

| 1       | MON3,            |                                                                                     |

| 2       | MON4,            |                                                                                     |

| 3       | MON5/HS_LED      | MON5 is combined with an LED Driver output                                          |

| 25      | $V_{S}$          | Power Supply Input; recommendation to block to GND directly at the IC with          |

|         |                  | ceramic capacitor (ferrite bead for better EMC behavior)                            |

| 26      | $V_{BAT\_SENSE}$ | Battery Voltage Sense Input; for connection to terminal 30 with external serial     |

|         |                  | resistor                                                                            |

| 23      | $V_{\rm CC}$     | Voltage Regulator Output; for internal supply (5 V); to stabilize block to GND with |

|         |                  | an external capacitor; for external loads up to the specified value (see Table 13   |

|         |                  | "Operating Range" on Page 34)                                                       |

| 8       | RESET            | Reset; output of SBC; "low active"; input for μController                           |

## **Pin Definitions and Functions**

| Pin No. | Symbol          | Function                                                                                                                                                                                                                                                                                                                                       |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | LIN             | <b>LIN Bus;</b> Bus Line for the LIN interface, according to ISO 9141 and LIN specification 1.3 and 2.0                                                                                                                                                                                                                                        |

| 24      | SUPPLY          | Supply Output; e.g. for Hall Sensor; controlled via SPI                                                                                                                                                                                                                                                                                        |

| 5       | LS2             | Low Side Switch 2 Output; controlled via SPI                                                                                                                                                                                                                                                                                                   |

| 6       | LS1             | Low Side Switch 1 Output; controlled via SPI                                                                                                                                                                                                                                                                                                   |

| 9       | P0.3            | General Purpose I/O with PWM Functionality (alternate function: SCK, see XC866 data sheet)                                                                                                                                                                                                                                                     |

| 10      | P0.4            | General Purpose I/O with Capture and PWM Functionality (alternate function: MTSR, see XC866 data sheet)                                                                                                                                                                                                                                        |

| 11      | P0.5            | General Purpose I/O with PWM Functionality (alternate function: MRST and EXINT0 ,see XC866 data sheet)                                                                                                                                                                                                                                         |

| 13      | $V_{DDC}$       | Voltage Regulator Output for μController Core (2.5 V); for connection of block capacitor to GND; not to be used for external loads                                                                                                                                                                                                             |

| 14      | TMS             | Test Mode Select (JTAG)                                                                                                                                                                                                                                                                                                                        |

| 15      | P0.0<br>[TCK_0] | General Purpose I/O; see XC866 data sheet (alternate function: JTAG Clock Input)                                                                                                                                                                                                                                                               |

| 16      | P0.2<br>[TDO_0] | General Purpose I/O; see XC866 data sheet (alternate function: JTAG Serial Data Output; RxD1)                                                                                                                                                                                                                                                  |

| 17      | P0.1<br>[TDI_0] | General Purpose I/O; see XC866 data sheet (alternate function: JTAG Serial Data Input; TxD1)                                                                                                                                                                                                                                                   |

| 18      | P2.0            | General Purpose Input (digital/analog) with Capture Functionality; e.g. for Hall Sensor (alternate function: EXINT1)                                                                                                                                                                                                                           |

| 19      | P2.1            | General Purpose Input (digital/analog) with Capture Functionality; e.g. for Hall Sensor (alternate function: EXINT2)                                                                                                                                                                                                                           |

| 20      | $V_{DDP}$       | Voltage Supply Input for $\mu$ Controller I/Os (5 V); to be connected with $V_{\rm CC}$ pin                                                                                                                                                                                                                                                    |

| _       | RxD             | LIN Transceiver Data Output; according to the ISO 9141 and LIN specification 1.3 and 2.0; LOW in dominant state; connected to µC General Purpose Input P1.0                                                                                                                                                                                    |

| _       | TxD             | LIN Transceiver Data Input; according to ISO 9141 and LIN specification 1.3 and 2.0; TxD has an internal pull-up; connected to μC General Purpose Input P1.1                                                                                                                                                                                   |

| _       | DI              | SPI Data Input; receives serial data from the control device; serial data transmitted to DI is a 16-bit control word with the Least Significant Bit (LSB) transferred first: the input has a pull-down and requires CMOS logic level inputs; DI will accept data on the falling edge of CLK-signal; connected to μC General Purpose Input P1.3 |

| _       | DO              | SPI Data Output; this tri-state output transfers diagnosis data to the control device; the output will remain in the high-impedance state unless the device is selected by a low on Chip-Select-Not (CSN); connected to μC General Purpose Input P1.4 (EXTINT0_1)                                                                              |

| _       | CLK             | SPI Clock Input; clock input for shift register; CLK has an internal pull-down and requires CMOS logic level inputs; connected to μC General Purpose Input P1.2                                                                                                                                                                                |

| _       | CSN             | SPI Chip Select Not Input; CSN is an active low input; serial communication is enabled by pulling the CSN terminal low; CSN input should only be transitioned when CLK is low; CSN has an internal pull-up and requires CMOS logic level inputs; connected to μC General Purpose Input P1.5                                                    |

| _       | $V_{AREF}$      | Voltage Reference for ADC                                                                                                                                                                                                                                                                                                                      |

#### **Pin Definitions and Functions**

| Pin No. | Symbol  | Function                                                                                                                       |  |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------|--|

| _       | $V_{A}$ | ADC Measurement Output (analog); for chip temperature and battery voltage measurement                                          |  |

| _       | ERR     | Error Pin; bi-directional signal; ERR has an internal pull-up; low-active; connected to μC General Purpose Input P3.6 (RSTOUT) |  |

| 7       | GND     | Ground; including GND for LSx and LIN                                                                                          |  |

| 12      |         | <b>Ground</b> ; corresponding GND to $V_{\mathrm{DDC}}$                                                                        |  |

| 21      |         | <b>Ground</b> ; $V_{\rm AGND}$ (ADC) & corresponding GND to $V_{\rm DDP}$                                                      |  |

| 22      |         | <b>Ground;</b> $V_{AGND}$ (ADC); also GND for LDO and Measurement Interface                                                    |  |

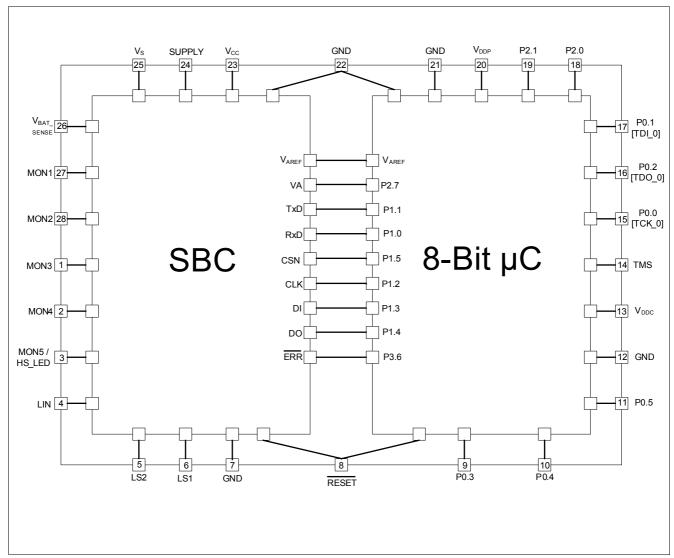

Figure 3 Pinout and Module Interconnects

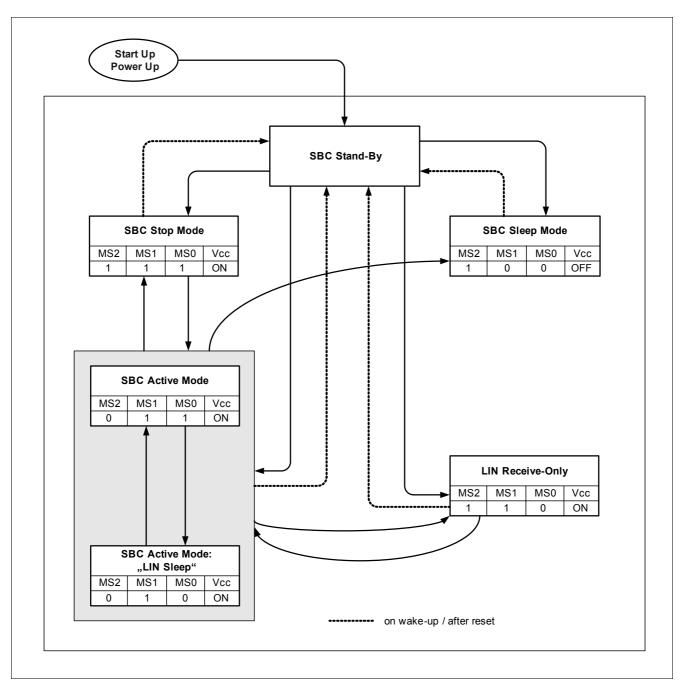

# 4 Operating Modes

The TLE7809G incorporates several SBC operating modes, that are listed in Table 1.

Table 1 SBC Operating Modes

| Functional Block                                    | SBC Standby<br>Mode    | SBC Active Mode | SBC Stop Mode            | SBC Sleep Mode         |

|-----------------------------------------------------|------------------------|-----------------|--------------------------|------------------------|

| $\overline{V_{\rm CC}}$ , 5 V, LDO                  | ON                     | ON              | ON                       | OFF                    |

| Window Watchdog                                     | ON                     | ON              | OFF / ON <sup>1)2)</sup> | OFF / ON <sup>2)</sup> |

| Monitoring / wake-up pins                           | ON / OFF <sup>3)</sup> | SPI-controlled  | ON / OFF <sup>3)</sup>   | ON / OFF <sup>3)</sup> |

| LS1,LS2 -switch                                     | OFF                    | SPI-controlled  | OFF                      | OFF                    |

| Supply Output                                       | ON / OFF <sup>3)</sup> | SPI-controlled  | ON / OFF <sup>3)</sup>   | OFF                    |

| HS-LED                                              | OFF                    | SPI-controlled  | OFF                      | OFF                    |

| 16-bit SPI                                          | ON                     | ON              | ON                       | OFF                    |

| LIN wake-up via bus                                 | ON                     | OFF             | ON                       | ON                     |

| message                                             |                        |                 |                          |                        |

| LIN Transmit                                        | OFF                    | ON              | OFF                      | OFF                    |

| LIN Receive                                         | OFF                    | ON              | OFF                      | OFF                    |

| RxD                                                 | Active low wake-up     | L/H             | Active low wake-up       | Active low wake-up     |

|                                                     | interrupt              |                 | interrupt                | interrupt              |

| Measurement I/F                                     | OFF                    | SPI-controlled  | OFF                      | OFF                    |

| $\overline{V_{AREF}}$                               | OFF                    | ON (2.5V)       | OFF                      | OFF                    |

| Voltage Monitoring at $V_{\rm S}$ and $V_{\rm BAT}$ | OFF                    | ON              | OFF                      | OFF                    |

<sup>1)</sup> WD "off" when voltage-regulator output current below "watchdog disable current threshold"

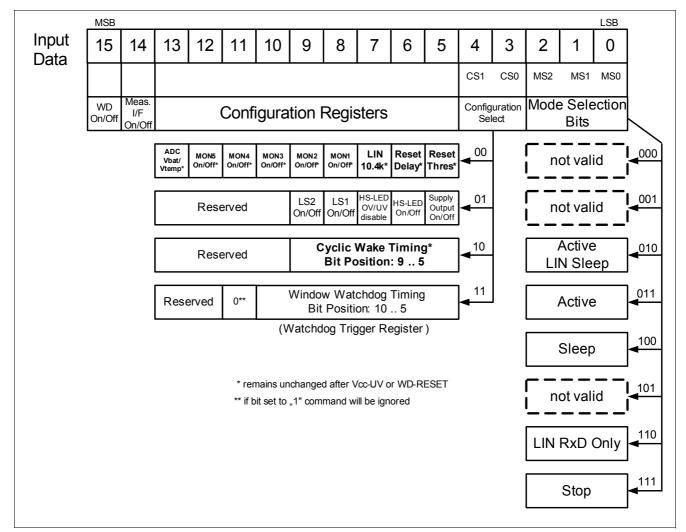

The System-Basis-Chip (SBC) offers several operation modes that are controlled via three mode select bits MS0, MS1 and MS2 within the SPI: SBC Active, Sleep and Stop mode, as well as LIN Receive-Only mode.

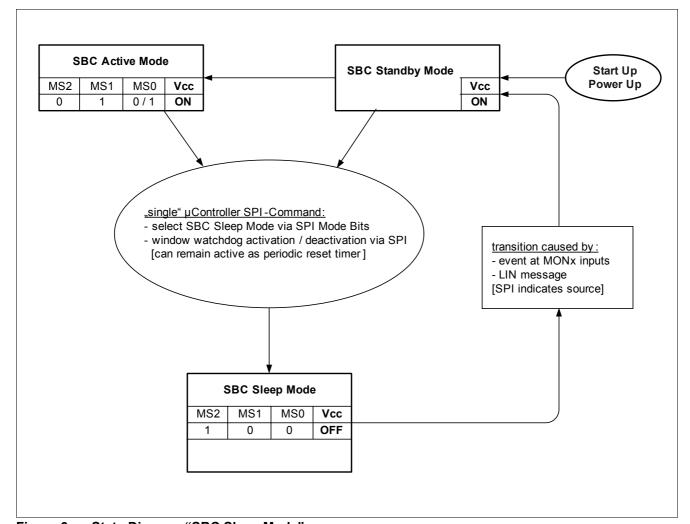

An overview of the operating modes and the operating mode transitions is indicated in Figure 4 below.

Note: It is possible to directly change from Stand-By to Stop or Sleep mode, however this might result in a higher current consumption (~200µA). The higher current consumption will occur in case of a power up and in case of a LIN wake-up from Stop and Sleep mode. To avoid this conditions its recommended to prior set Active mode before changing to Stop or Sleep mode.

<sup>2)</sup> WD default "off" in SBC Stop / Sleep Mode; WD can be active in order to generate period wake-ups of SBC

<sup>3) &</sup>quot;ON / OFF" state is inherited from previous operating mode ("OFF" after POR and RESET)

Figure 4 State Diagram "SBC Operation Modes"

#### 4.1 SBC Standby Mode

After powering-up the SBC or wake-up from power-saving, it automatically starts-up in **SBC Standby Mode**, waiting for the microcontroller to finish its startup and initialization sequences. However, this mode cannot be selected via SPI command. From this transition mode the SBC can be switched via SPI command into the desired operating mode. All modes are selected via SPI bits or certain operation conditions, e.g. external wake-up events.

#### 4.2 SBC Active Mode

The SBC Active Mode is used to transmit and receive LIN messages and provides the sub-mode "LIN Sleep".

## 4.3 SBC Active Mode "LIN Sleep"

In **SBC Active Mode** "**LIN Sleep**" the SBC's current consumption is reduced by disabling the LIN transceiver. This also means that the internal pull-up resistor of the LIN transceiver is turned off in SBC Active Mode "LIN Sleep". During this mode the LIN transceiver remains its wake-up capability in order to react on a remote frame or wake-up pulse (specified in LIN Specification V2.0) from the master node or other slave nodes. In case of a wake-up event via LIN message the (internal) RxD is pulled "low" and the "bus wake-up bit" within the SPI status word is set. However, the LIN transceiver needs to be activated by switching to "SBC Active Mode".

## 4.4 LIN Receive-Only Mode ("LIN RxD-Only")

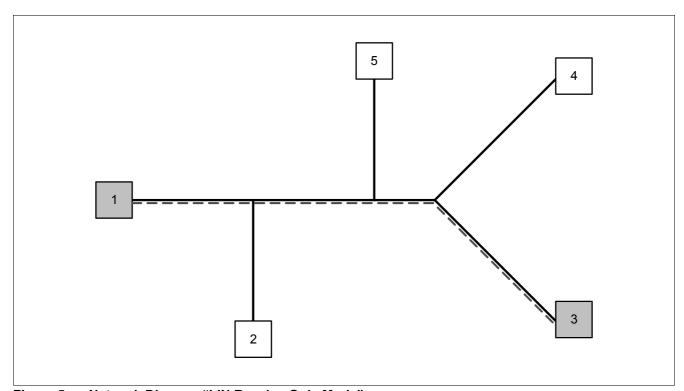

The LIN Receive-Only Mode ("LIN RxD-Only") is designed for a special test procedure to check the bus connections. Figure 5 shows a network consisting of 5 nodes. Node 1 is the LIN master node, the others are LIN slave nodes. If the connection between node 1 and node 3 shall be tested, the nodes 2, 4 and 5 are switched into LIN Receive-Only Mode. Node 1 and node 3 are in Active Mode. If node 1 sends a message ("remote frame"), node 3 is the only node which is physically able to reply to the remote frame. The other nodes have their outputs drivers disabled.

The main difference between the **SBC Active Mode** and the **LIN Receive-Only Mode** is that the LIN transmit stage is automatically turned-off in LIN Receive-Only-Mode. However, the LIN receiver is still active in both modes.

Figure 5 Network Diagram "LIN Receive-Only Mode"

# 4.5 Power Saving Modes

#### 4.5.1 SBC Sleep Mode

During **SBC Sleep Mode** (see **Figure 6**), the lowest power consumption is achieved, by having its main voltage regulator switched-off. As the microcontroller cannot be supplied, the integrated window watchdog can be disabled in Sleep Mode via a dedicated SPI control bit. However, it can be turned-on for periodically waking-up the system, e.g. ECU, by generating a reset and automatically switching to SBC Standby Mode.

This mode is entered via SPI command, and turns-off the integrated LIN bus transceiver, main voltage regulator as well as all switches. Upon a voltage level change at the monitoring / wake-up pins or by LIN message the SBC Sleep Mode will be terminated and the SBC Standby Mode will automatically be entered (turning-on the LDO).

Note: Upon a wake-up via LIN message the (internal) RxD signal stays "low" until mode switch.

Note: If the Window Watchdog was not enabled in Sleep Mode the Window Watchdog starts after wake-up with a "long open window" in SBC Standby Mode.

Note: In Sleep Mode with activated watchdog (see **Table 2 "SPI Input Data Bits" on Page 20**) the oscillator remains turned on.

Figure 6 State Diagram "SBC Sleep Mode"

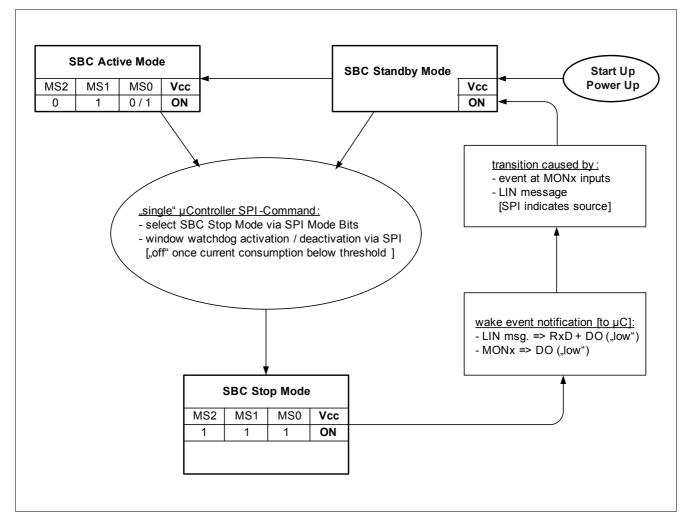

### 4.5.2 SBC Stop Mode

The **SBC Stop Mode** has the advantage of reducing the current consumption to a minimum, while supplying the microcontroller with its quiescent current during its power saving mode ("Stop"). This mode is entered via SPI command, and turns-off the integrated bus transceivers and respective termination, but the voltage regulator for the microcontroller supply remains active. A microcontroller in a power saving mode has the advantage over a turned-off microcontroller to have a reduced reaction time upon a wake-up event.

A voltage level change at the monitoring/wake-up pins will, in contrast to the behavior in Sleep Mode, generate a signal that indicates the wake-up event at the microcontroller in Power-Down Mode. This is realized via an interconnect from the SPI of the SBC [DO] to the microcontroller [P1.4]. In case the wake-up event was a LIN message, the respective RxD pin of the SBC **and** the SPI Data Out [DO] will be pulled "low". RxD is pulled "low" until mode switch, while DO stays "low" for **two** internal SBC cycles. (The microcontroller itself has to take care of switching SBC modes after a wake-up event notification (see **Figure 7**).)

Note: The window watchdog is automatically disabled once the LDO output current goes below a specified "watchdog current threshold", unless the SPI setting "WD On/Off" prevents this (see Figure 10, Watchdog disable current threshold, Table 14 and "Window Watchdog Reset Period Settings" on Page 22).

Note: If the Window Watchdog was not enabled in Stop Mode the Window Watchdog starts after wake-up with a "long open window" in SBC Standby Mode.

Figure 7 State Diagram "SBC Stop Mode"

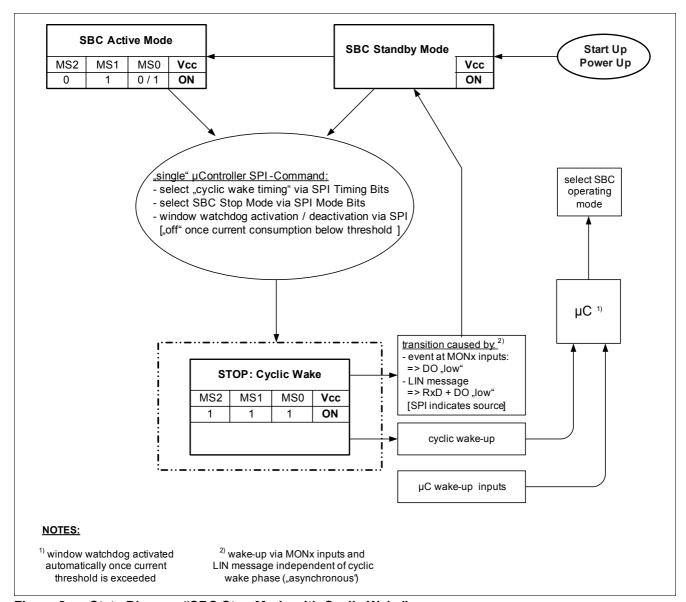

## 4.5.3 SBC Stop Mode with Cyclic Wake

The SBC Stop Mode has the advantage of reducing the current consumption to a minimum, while supplying the microcontroller with its quiescent current during its power saving mode ("Stop"). This mode is entered via SPI command, and turns-off the integrated LIN bus transceiver, but the voltage regulator remains active.

The SBC periodically generates a wake-up "low" pulse at DO ("interconnect signal") that is connected to an interrupt input [P1.4] of the microcontroller. This period can be defined via the "cyclic wake period" bit field within the SPI register. This pulse at DO has a length of **two** internal SBC cycles.

In case of a detected wake-up event via LIN message or any of the MONx pins, DO stays "low" until the first valid SPI command.

Note: The window watchdog is automatically disabled once the LDO output current goes below a specified "watchdog current threshold", unless the SPI setting "WD On/Off" prevents this (see Figure 10).

Note: A wake-up event via LIN message or via MONx inputs can happen independently of the cyclic wake phase.

Note: The Window Watchdog starts with a "long open window" after a mode switch, e.g. to SBC Active Mode.

Figure 8 State Diagram "SBC Stop Mode with Cyclic Wake"

**LIN Transceiver**

### 5 LIN Transceiver

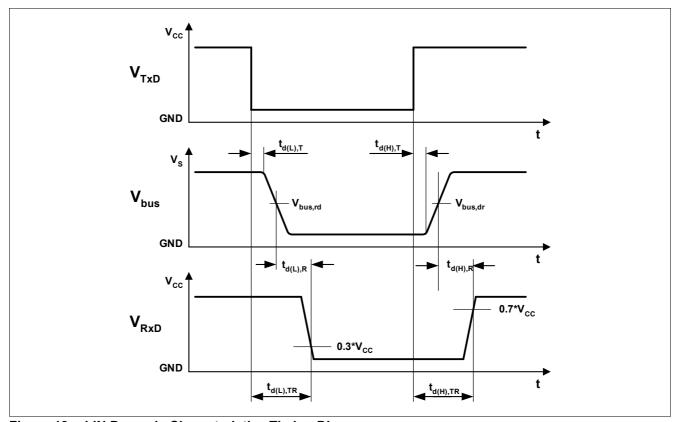

The TLE7809G offers a LIN transceiver, which is compatible to ISO9141 and certified according to LIN Specification 1.3 and 2.0 "Physical Layer". The transceiver has a pull-up resistor of 30 k $\Omega$  implemented and is protected against short to battery and short to GND.

The LIN transceiver has an implemented wake-up capability during operation in power saving modes. In Stop Mode a wake-up event is indicated via (internal) RxD and DO signals, that are pulled "low". Out of Sleep Mode a wake-up event causes an automatic transition into Standby Mode and the (internal) RxD and DO signals are pulled "low". If the TxD input is pulled low for longer than the TxD dominant timeout the TxD input is ignored and the LIN bus goes back to recessive state. This fail-safe feature in case of a permanent low TxD signal recovers if the TxD pin is high for TxD dominant timeout recovery time.

For LIN automotive applications in the United States a dedicated mode by the name "Low Slope Mode" can be used. This mode reduces the maximum data transmission rate of 20 kBaud to 10.4 kBaud by switching to a different slew rate. By using this mode the EM noise emission can be reduced.

Data Sheet 15 Rev. 3.01, 2008-04-15

**ADC Measurement Interface**

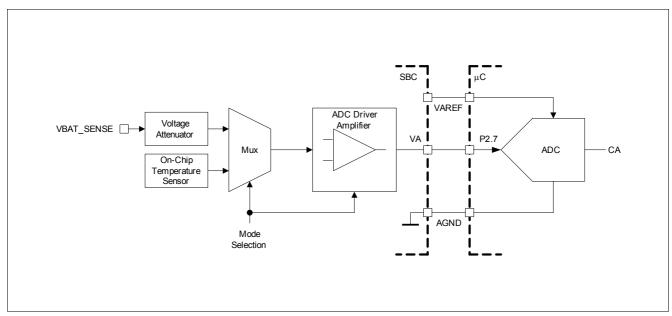

#### 6 ADC Measurement Interface

The SBC measurement interface comprises a battery measurement unit (high voltage input  $V_{\rm bat\_sense}$ ) and an on-chip temperature sensor. A multiplexer is used to select the desired input channel that is connected to the ADC of the  $\mu$ C. This multiplexer is controlled via the SPI interface. Also, the reference voltage  $V_{\rm AREF}$  is provided by the SBC. The  $V_{\rm bat\_sense}$  input must be protected against voltage transients, like ISO pulses by a resistor in series to terminal 30.

Figure 9 Simplified Block Diagram of ADC Measurement Interface

#### 6.1 Voltage Measurement

The input voltage is filtered and scaled down to the input voltage range of the ADC converter. The voltage measurement output code of the ADC can be calculated using the following equation, where  $V_{\rm SENS}$  is the voltage at the pin  $V_{\rm BAT\ SENSE}$  and N the resolution of the ADC:

$$C_{\text{VSENS}} = \text{round} \left[ \frac{V_{\text{SENS}}}{V_{\text{AREF}}} \frac{1}{8} (2^{N} - 1) \right], 0V \le V_{\text{SENS}} \le V_{\text{bat-fs}}$$

(1)

The input voltage corresponding to the ADC output code  $C_{\rm VSENS}$  can be calculated with the following equation:

$$V_{\text{SENS}} = \frac{8 \times V_{\text{AREF}}}{2^{N} - 1} \times C$$

vsens

#### 6.1.1 Voltage Measurement Calibration Concept

Best measurement accuracy can be obtained by applying the calibration function:

$$C_{\text{VSENSCAL}} = \text{round}[c_1(C_{\text{VSENS}} - c_0)] \tag{3}$$

$C_{\rm VSENS}$  represents the ADC output code for the analog input voltage at the pin  $V_{\rm BAT\_SENSE}$ . The correction coefficients  $c_1$  and  $c_0$  correct for slope variations and offset errors of the measurement transfer function.

During the production test these calibration figures are calculated and stored in the flash memory of the microcontroller.

#### **ADC Measurement Interface**

Further details on the implementation of the calibration function and location of the calibration figures in Flash memory can be found in a dedicated application note. The voltage measurement target parameters can be found in "ADC Battery Voltage Measurement Interface, VBAT\_SENSE" on Page 43.

#### **6.2** Temperature Measurement

In the temperature measurement mode the typical internal analog output voltage of the on-chip temperature sensor can be described with the first order approximation:

$$V_{A} \approx \mathbf{m}_{0} - \mathbf{m}_{1} \times T_{i} \tag{4}$$

Where:

- $T_i$  is the junction temperature in Kelvin

- m<sub>o</sub>and m<sub>1</sub> are typical linear fitting parameters (see Table "ADC Temperature Measurement Interface" on Page 43)

The output code of the ADC is given by the following equation, where  $V_{\mathsf{AREF}}$  and N denote the ADC reference voltage and the resolution of the ADC:

$$C_{\mathsf{A}} = \mathsf{round} \left[ V_{\mathsf{A}}(T_{\mathsf{j}}) \times \frac{(2^{\mathsf{N}} - 1)}{V_{\mathsf{AREF}}} \right], \ V_{\mathsf{A}} \le V_{\mathsf{AREF}}$$

(5)

The junction temperature  $T_1$  corresponding to the output code  $C_A$  is given by:

$$T_{\rm j} = \frac{1}{\rm m_1} \left[ \rm m_0 - \frac{C_A(T_{\rm j}) \times V_{AREF}}{2^{\rm N} - 1} \right]$$

[unit: K]

273.15 °C need to be subtracted to convert  $T_i$  [K] into Centigrade Scale [°C].

The temperature measurement target parameters can be found in "ADC Temperature Measurement Interface" on Page 43.

#### 6.2.1 Temperature Measurement Calibration Concept

Best measurement accuracy can be obtained by applying the calibration function:

$$T_{\text{CAL}} = 586 + f_0 \cdot 2^{-1} - [2^{-2} + f_1 \cdot 2^{-10}] C_{\text{A}}(T_{\text{j}})$$

(7)

The calibration coefficients  $f_{0/1}$  are computed during the production test and stored in the flash memory of the microcontroller.

The selection between battery voltage and temperature measurement is done via SPI bit (see "SPI (Serial Peripheral Interface)" on Page 19).

Further details on the implementation of the calibration function and location of the calibration figures can be found in a dedicated application note.

Low Dropout Voltage Regulator

# 7 Low Dropout Voltage Regulator

The Low Drop-Out Voltage Regulator (LDO) has mainly been integrated in the TLE7809G in order to supply the integrated microcontroller and several modules of the SBC.

Note: The LDO is **not** intended to be used as supply for external loads. However, it might be used as supply for small external loads (see **Table 13 "Operating Range" on Page 34**).

In the event of a short circuit condition at the  $V_{\rm cc}$  pin, a shutdown/reset of the TLE7809G may occur due to overcurrent condition. This maximum output current for external loads is specified in the electrical characteristics.

The voltage regulator output is protected against overload and overtemperature.

An external reverse current protection is required at the pin  $V_{\rm S}$  to prevent the output capacitor at  $V_{\rm CC}$  from being discharged by negative transients or low  $V_{\rm S}$  voltage.

Data Sheet 18 Rev. 3.01, 2008-04-15

# 8 SPI (Serial Peripheral Interface)

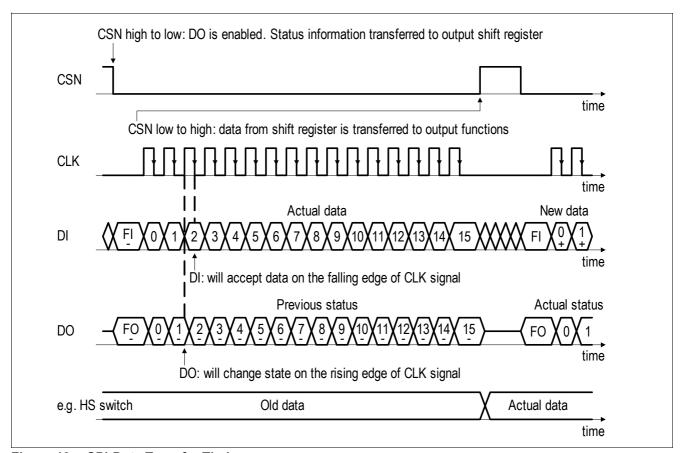

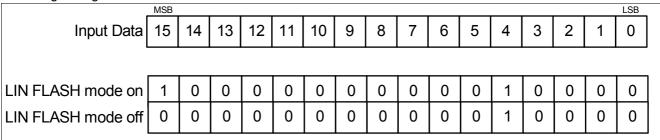

Control and status information between SBC and  $\mu$ C is exchanged via a digital interface, that is called "serial peripheral interface" (SPI) on the SBC side, and "synchronous serial channel" (SSC) on the  $\mu$ C side. The 16-bit wide Programming or Input Word of the SBC (see **Table 2** to **Table 8**) is read in via the data input DI (with "LSB first"), which is synchronized with the clock input CLK supplied by the  $\mu$ C. The Diagnosis or Output Word appears synchronously at the data output DO (see **Table 9**).

The transmission cycle begins when the chip is selected by the Chip Select Not input CSN ("low" active). After the CSN input returns from L to H, the word that has been read in becomes the new control word. The DO output switches to tri-state status at this point, thereby releasing the DO bus for other usage.

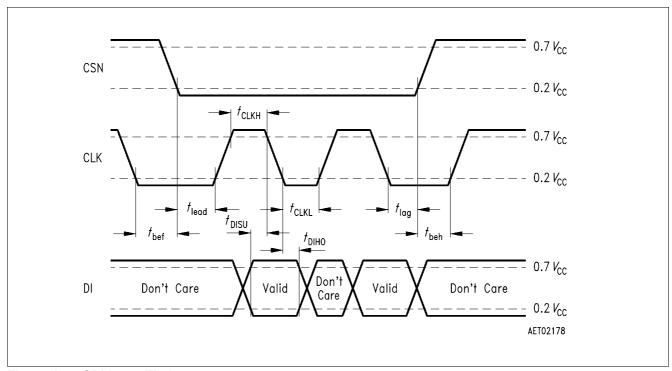

The state of DI is shifted into the input register with every falling edge on CLK. The state of DO is shifted out of the output register after every rising edge on CLK. The number of received input clocks is supervised by a modulo-16 operation and the Input/Control Word is discarded in case of a mismatch.

This error is flagged by a "high" at the data output pin DO (interconnect to  $\mu$ C: P1.4) of the following SPI output word before the first rising edge of the clock is received. Additionally the logic level of DO will be "OR-ed" with the logic level of DI (P1.3).

Note: After wake-up from low-power modes the device needs to be set to Active Mode first before switches like LS1, LS2, Supply Output and LED Driver can be turned on with the second SPI command.

Figure 10 16-Bit SPI Input Data / Control Word

#### Table 2 SPI Input Data Bits

| BIT  | Input Data                                                                                                                                                                                                                                                                                |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0    | Mode Selection Bit 0 (MS0)                                                                                                                                                                                                                                                                |  |

| 1    | Mode Selection Bit 1 (MS1)                                                                                                                                                                                                                                                                |  |

| 2    | Mode Selection Bit 2 (MS2)                                                                                                                                                                                                                                                                |  |

| 3    | Configuration Selection Bit 0 (CS0)                                                                                                                                                                                                                                                       |  |

| 4    | Configuration Selection Bit 1 (CS1)                                                                                                                                                                                                                                                       |  |

| 5 13 | Configuration Register (meaning based on "Configuration Selection Bits")                                                                                                                                                                                                                  |  |

| 14   | Measurement Interface "on" / "off" (setting only valid in active mode, in power saving modes the Measurement interface is turned off)                                                                                                                                                     |  |

| 15   | Window Watchdog Stop/Sleep mode configuration "on" / "off" (the configuration is only valid for Stop/Sleep mode, in Active mode the Window Watchdog is always on); if "on" is set before Stop Mode is entered, watchdog remains active regardless of "watchdog disable current threshold" |  |

# Table 3 Mode Selection Bits

| MS2 | MS1 | MS0 | Mode Selection: SBC Mode          |

|-----|-----|-----|-----------------------------------|

| 0   | 0   | 0   | "reserved" / not used             |

| 0   | 0   | 1   | "reserved" / not used             |

| 0   | 1   | 0   | SBC Active Mode: "LIN Sleep"      |

| 0   | 1   | 1   | SBC Active Mode (LIN "on")        |

| 1   | 0   | 0   | SBC Sleep (LIN & VReg "off")      |

| 1   | 0   | 1   | "reserved" / not used             |

| 1   | 1   | 0   | LIN Transceiver: LIN Receive-Only |

| 1   | 1   | 1   | SBC Stop Mode (LIN "off")         |

# Table 4 Configuration Selection Bits

| CS1 | CS0 | Configuration Selection         |

|-----|-----|---------------------------------|

| 0   | 0   | General Configuration           |

| 0   | 1   | Integrated Switch Configuration |

| 1   | 0   | Cyclic Wake Configuration       |

| 1   | 1   | Window Watchdog Configuration   |

Table 5 General & Integrated Switch Configuration

| Pos. | General Configuration <sup>1)</sup>             | Integrated Switch Configuration <sup>2)</sup>                         |

|------|-------------------------------------------------|-----------------------------------------------------------------------|

| 5    | Reset Threshold: "default" or "SPI option"      | Supply Output "on" / "off"                                            |

|      | (see Table 14: Reset Generator; Pin RESET)      |                                                                       |

| 6    | Reset Delay: "default" or "SPI option"          | HS-LED "on" / "off"                                                   |

|      | (see Table 14: Reset Generator; Pin RESET)      |                                                                       |

| 7    | LIN "Low Slope Mode" (10.4 kBaud)               | HS-LED OV/UV disable                                                  |

|      |                                                 | "0": HS-LED will be turned off in case of V <sub>bat</sub> OV/UV      |

|      |                                                 | "1": HS-LED will <u>not</u> be turned off in case of $V_{\text{bat}}$ |

|      |                                                 | OV/UV                                                                 |

| 8    | MON1 Input Activation                           | LS1 "on" / "off"                                                      |

| 9    | MON2 Input Activation                           | LS2 "on" / "off"                                                      |

| 10   | MON3 Input Activation                           | "reserved" / not used                                                 |

| 11   | MON4 Input Activation                           | "reserved" / not used                                                 |

| 12   | MON5 Input Activation                           | "reserved" / not used                                                 |

| 13   | ADC Measurement: $V_{\rm bat}$ / $V_{\rm temp}$ | "reserved" / not used                                                 |

|      | $("0" = V_{\text{bat}}; "1" = V_{\text{temp}})$ |                                                                       |

<sup>1) &</sup>quot;1" = ON / enable, "0" = OFF / disable

Table 6 Cyclic Wake & Window Watchdog Period Settings<sup>1)2)</sup>

| Pos. | Cyclic Sense / Wake Config. | Window Watchdog Config.    |

|------|-----------------------------|----------------------------|

| 5    | Cyclic Period Bit 0 (T0)    | Watchdog Period Bit 0 (T0) |

| 6    | Cyclic Period Bit 1 (T1)    | Watchdog Period Bit 1 (T1) |

| 7    | Cyclic Period Bit 2 (T2)    | Watchdog Period Bit 2 (T2) |

| 8    | Cyclic Period Bit 3 (T3)    | Watchdog Period Bit 3 (T3) |

| 9    | Cyclic Period Bit 4 (T4)    | Watchdog Period Bit 4 (T4) |

| 10   | "reserved" / not used       | Watchdog Period Bit 5 (T5) |

| 11   | "reserved" / not used       | "0" (mandatory)            |

| 12   | "reserved" / not used       | "reserved" / not used      |

| 13   | "reserved" / not used       | "reserved" / not used      |

<sup>1) &</sup>quot;1" = ON, "0" = OFF

Data Sheet 21 Rev. 3.01, 2008-04-15

<sup>2) &</sup>quot;1" = ON, "0" = OFF

<sup>2)</sup> Cyclic wake and window watchdog period settings see Table 7 "Cyclic Wake Period Settings (Stop Mode only)" on Page 22

| Table 7 | Cyclic Wake | Period Settings | (Stop Mode only) |  |

|---------|-------------|-----------------|------------------|--|

|---------|-------------|-----------------|------------------|--|

| T4 | Т3 | T2 | T1 | ТО | Cyclic Wake Period |  |

|----|----|----|----|----|--------------------|--|

| 0  | 0  | 0  | 0  | 0  | Cyclic Wake "off"  |  |

| 0  | 0  | 0  | 0  | 1  | 16 ms              |  |

| 0  | 0  | 0  | 1  | 0  | 32 ms              |  |

| 0  | 0  | 0  | 1  | 1  | 48 ms              |  |

| 0  | 0  | 1  | 0  | 0  | 64 ms              |  |

| 0  | 0  | 1  | 0  | 1  | 80 ms              |  |

| 0  | 0  | 1  | 1  | 0  | 96 ms              |  |

|    |    |    |    |    | ms                 |  |

| 1  | 1  | 1  | 1  | 1  | 496 ms             |  |

Table 8 Window Watchdog Reset Period Settings

| T5 | T4 | Т3 | T2 | T1 | ТО | Window Watchdog<br>Reset Period |  |

|----|----|----|----|----|----|---------------------------------|--|

| 0  | 0  | 0  | 0  | 0  | 0  | "not a valid selection"         |  |

| 0  | 0  | 0  | 0  | 0  | 1  | 16 ms                           |  |

| 0  | 0  | 0  | 0  | 1  | 0  | 32 ms                           |  |

| 0  | 0  | 0  | 0  | 1  | 1  | 48 ms                           |  |

| 0  | 0  | 0  | 1  | 0  | 0  | 64 ms                           |  |

| 0  | 0  | 0  | 1  | 0  | 1  | 80 ms                           |  |

| 0  | 0  | 0  | 1  | 1  | 0  | 96 ms                           |  |

|    |    |    |    |    |    | ms                              |  |

| 1  | 1  | 1  | 1  | 1  | 1  | 1008 ms                         |  |

## Table 9 SPI Output Data

| Pos. | Output Data <sup>1)</sup>                                         | Output Data after Wake-up <sup>2)</sup> |

|------|-------------------------------------------------------------------|-----------------------------------------|

| 0    | $V_{\rm CC}$ Temperature Prewarning                               | $V_{\rm CC}$ Temperature Prewarning     |

| 1    | HS-LED fail (OC / OT)                                             | HS-LED fail (OC / OT)                   |

| 2    | $V_{INT}	ext{-}Fail$ ("active low")                               | $V_{INT}$ -Fail ("active low")          |

| 3    | LS1/2 (OC / OT)                                                   | LS1/2 (OC / OT)                         |

| 4    | Window Watchdog Reset                                             | Window Watchdog Reset                   |

| 5    | MON1 Logic Input Level                                            | Wake-Up via MON1                        |

| 6    | MON2 Logic Input Level                                            | Wake-Up via MON2                        |

| 7    | MON3 Logic Input Level                                            | Wake-Up via MON3                        |

| 8    | MON4 Logic Input Level                                            | Wake-Up via MON4                        |

| 9    | MON5 Logic Input Level                                            | Wake-Up via MON5                        |

| 10   | "reserved" / not used                                             | "reserved" / not used                   |

| 11   | LIN Failure                                                       | Bus Wake-Up via LIN Msg.                |

| 12   | $V_{\rm bat}$ Range 1 (UV) <sup>3)</sup> [only "SBC Active Mode"] | End of Cyclic Wake Period               |

| 13   | $V_{\mathrm{bat}}$ Range 2 (OV) [only "SBC Active Mode"]          | "low" <sup>4)</sup>                     |

Table 9 SPI Output Data (cont'd)

| Pos. | Output Data <sup>1)</sup>                             | Output Data after Wake-up <sup>2)</sup> |  |  |  |

|------|-------------------------------------------------------|-----------------------------------------|--|--|--|

| 14   | Supply Output (OC / OT)                               | Supply Output (OC / OT)                 |  |  |  |

| 15   | $V_{\rm S}$ UV <sup>5)</sup> [only "SBC Active Mode"] | "low"                                   |  |  |  |

- 1) "1" = ON / enable, "0" = OFF / disable, OC = overcurrent, UV = undervoltage, OT = overtemperature (temp. shut-down)

- 2) "1" = ON, "0" = OFF, OC = overcurrent, UV = undervoltage, OT = overtemperature (temp. shut-down)

- 3) Becomes valid after start-up time for voltage monitoring

- 4) Voltage monitoring not active in SBC Standby Mode

- 5) This bit needs to be read twice to indicate an undervoltage condition (only for  $V_{\rm S}$  ramping down bit15 set to "1")

Table 10 Diagnostic, Protection and Safety Functions

| Module                                              | Function                                                     | Effect                                                                                                                          | Concept                                                                     |  |

|-----------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| Window Watchdog                                     | WD <sup>1)</sup> Failure                                     | Reset; see Table 11 "Reset<br>Behavior SBC" on Page 25                                                                          | SPI status latched until next read-out                                      |  |

| LDO (VReg)                                          | ${\sf OC^{2)}}$ at $V_{\sf CC}$                              | current limitation                                                                                                              | _                                                                           |  |

| , 5                                                 | voltage regulator UV condition $(V_{\rm S} \ {\rm related})$ | Reset, see Table 11 "Reset<br>Behavior SBC" on Page 25                                                                          | Condition occurs at $V_{\rm S}$ below operating range                       |  |

|                                                     | V <sub>CC</sub> -UV                                          | Reset, see Table 11 "Reset<br>Behavior SBC" on Page 25                                                                          | -                                                                           |  |

|                                                     | WD current threshold (Stop Mode)                             | WD only disabled if $V_{\rm CC}$ -current < threshold and WD not enabled via SPI                                                | WD enabled if $V_{\rm CC}\text{-current}$ > threshold                       |  |

|                                                     | OT <sup>3)</sup>                                             | $V_{\rm CC}$ -shutdown, Reset as soon as $V_{\rm CC}$ falls below reset threshold, see Table 11 "Reset Behavior SBC" on Page 25 | automatically enabled with thermal hysteresis                               |  |

|                                                     | OT prewarning                                                | SPI status output                                                                                                               | SPI status latched until next read-out                                      |  |

| internal supply [SBC] $(V_{\rm S} \ {\rm related})$ | $V_{INT}	ext{-}UV$                                           | (internal) Reset; register settings<br>cleared; SPI status output; see<br>Table 11 "Reset Behavior SBC"<br>on Page 25           | _                                                                           |  |

| LS-Switches                                         | OC, OT                                                       | LSx-shutdown; SPI status output; signalization via ERR pin                                                                      | re-activation via SPI<br>command; SPI status<br>latched until next read-out |  |

|                                                     | microcontroller error signalization (ERR)                    | LSx-shutdown; see "Error<br>Interconnect (ERR)" on Page 32                                                                      | re-activation via SPI command                                               |  |

| Supply Output                                       | OC, OT                                                       | Supply-shutdown; SPI status output                                                                                              | re-activation via SPI<br>command; SPI status<br>latched until next read-out |  |

Table 10

Diagnostic, Protection and Safety Functions (cont'd)

| Module                                                                    | Function                                                                     | Effect                                                                        | Concept                                                                     |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| HS-LED                                                                    | OC, OT                                                                       | HS-LED-shutdown; SPI status output                                            | re-activation via SPI<br>command; SPI status<br>latched until next read-out |

|                                                                           | $V_{BAT}	ext{-}UV$                                                           | HS-LED-shutdown (optional), SPI status output                                 | re-activation via SPI<br>command; SPI status<br>latched until next read-out |

|                                                                           | $V_{\mathrm{BAT}}	ext{-}\mathrm{OV}$ HS-LED-shutdown (optional status output |                                                                               | re-activation via SPI<br>command; SPI status<br>latched until next read-out |

| $\overline{V_{\mathrm{BAT}}}$ -Monitor (at $V_{\mathrm{BAT\_SENSE}}$ pin) | $V_{BAT}	ext{-}UV$                                                           | HS-LED-shutdown (optional), SPI status output                                 | SPI status latched until next read-out                                      |

|                                                                           | $V_{BAT}	ext{-}OV$                                                           | HS-LED-shutdown (optional), SPI status output                                 | SPI status latched until next read-out                                      |

| $\overline{V_{\mathrm{S}}}$ -Monitor                                      | $V_{ m S}$ -UV                                                               | SPI status output                                                             | SPI status latched until next read-out                                      |

| LIN                                                                       | LIN-Failure (OT, UV, TxD time-out)                                           | SPI status output                                                             | -                                                                           |

|                                                                           | Wake-up                                                                      | signalization via interconnect to μC (RxD and DO "low") and SPI status output | _                                                                           |

| MONx-Inputs                                                               | Wake-up                                                                      | signalization via interconnect to μC (DO "low") and SPI status output         | -                                                                           |

| SPI                                                                       | Failure Indicator                                                            | signalled at interconnect (DO "high" OR-ed with DI) once CSN is active        | _                                                                           |

<sup>1)</sup> WD (Window) Watchdog

<sup>2)</sup> OC overcurrent detection

<sup>3)</sup> OT overtemperature detection

#### **Reset Behavior and Window Watchdog**

# 9 Reset Behavior and Window Watchdog

The SBC provides three different resets:

- $V_{\mathsf{INT}} ext{-}\mathsf{UV}$ : reset of SBC upon undervoltage detection at **internal** supply voltage

- $V_{cc}$ -UV: reset of SBC upon undervoltage detection at supply voltage ( $V_{cc}$ )

- Watchdog: reset of SBC caused by integrated window watchdog

Should the internal supply voltage become lower than the internal threshold the  $V_{\mathsf{INT}}$ -Fail SPI bit will be reset in order to indicate the undervoltage condition ( $V_{\mathsf{INT}}$ -UV). All other SPI settings are also reset by this condition. The  $V_{\mathsf{INT}}$ -Fail feature can also be used to give an indication that the system supply was disconnected and therefore a pre-setting routine of the microcontroller has to be started.

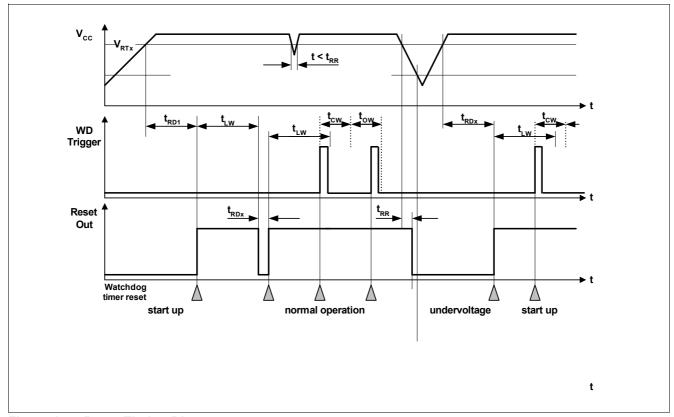

When the  $V_{\rm CC}$  voltage falls below the reset threshold voltage  $V_{\rm RTx}$  for a time duration longer than the filter time  $t_{\rm RR}$  the reset output is switched LOW and will be released after a programmable delay time (default setting for Power-On-Reset) when  $V_{\rm CC} > V_{\rm RTx}$ . This is necessary for a defined start of the microcontroller when the application is switched on after Power-On-Reset. As soon as an undervoltage condition of the output voltage ( $V_{\rm CC} < V_{\rm RTx}$ ) appears, the reset output is switched LOW again ( $V_{\rm CC}$ -UV). The reset delay time can be shortened via SPI bit. Please refer to Figure 17.

Table 11 Reset Behavior SBC

| Affected by Reset      | $V_{INT}	ext{-}UV$         | $V_{ m cc}$ -UV ${ m or}$ Watchdog-Reset                        |

|------------------------|----------------------------|-----------------------------------------------------------------|

| Reset Pin              | "low"                      | "low"                                                           |

| Watchdog Timer         | long open window           | long open window                                                |

| Operating Mode         | SBC Standby                | SBC Standby                                                     |

| LS-Switches            | "off"                      | "off"                                                           |

| Supply Output          | "off"                      | "off"                                                           |

| HS-LED                 | "off"                      | "off"                                                           |

| Configuration Settings | Reset ("all bits cleared") | see Figure 10 "16-Bit SPI Input Data / Control Word" on Page 19 |

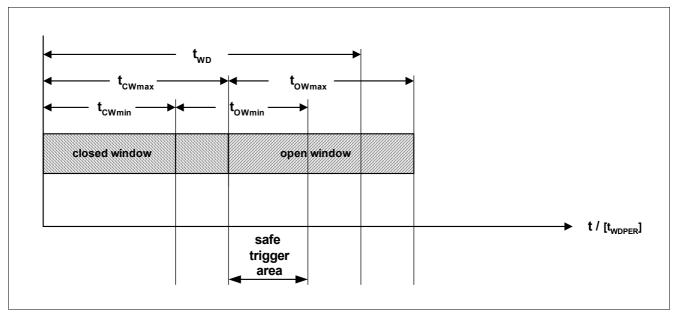

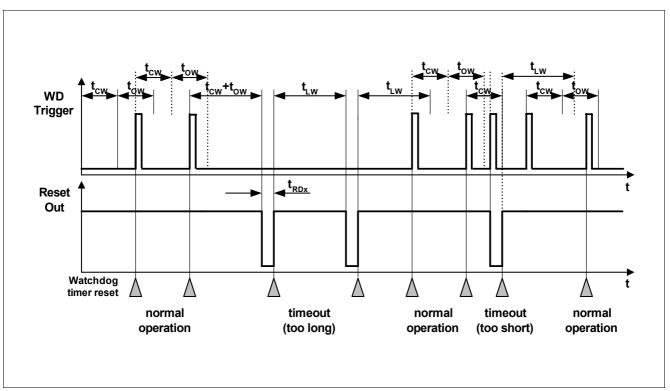

After the above described delayed reset (LOW to HIGH transition at RESET pin) the **window watchdog** circuit is started by opening a long open window in SBC Standby Mode. The long open window allows the microcontroller to run its initialization sequences and then to trigger the watchdog via the SPI. Within the long open window period a watchdog trigger is detected as a write access to the "window watchdog period bit field" within the SPI control word. The trigger is accepted when the CSN input becomes HIGH after the transmission of the SPI word.

A correct watchdog trigger results in starting the window watchdog by opening a closed window with a width of 50% of the selected window watchdog period. This period, selected via the SPI window watchdog timing bit field, is programmable in a wide range. The closed window is followed by an open window with a width of 50% of the selected period. The microcontroller has to service the watchdog by periodically writing to the window watchdog timing bit field. This write access has to meet the open window. A correct watchdog service immediately results in starting the next closed window.

Should the trigger signal not meet the open window a watchdog reset is generated by setting the reset output low. Then the watchdog again starts by opening a long open window. In addition, a "window watchdog reset flag" is set within the SPI to monitor a watchdog reset. For fail safe reasons the TLE7809G is automatically switched to SBC Standby mode if a watchdog trigger failure occurs. This minimizes the power consumption in case of a permanent faulty microcontroller. This "window watchdog reset flag" will be cleared by any access to the SPI.

When entering a low power mode the watchdog can be requested to be enabled via an SPI bit. In SBC Stop Mode the watchdog is only turned off once the current consumption at  $V_{\rm CC}$  falls below the "watchdog current threshold".

Monitoring / Wake-Up Inputs MON1 ... 5 and Wake-Up Event Signalling

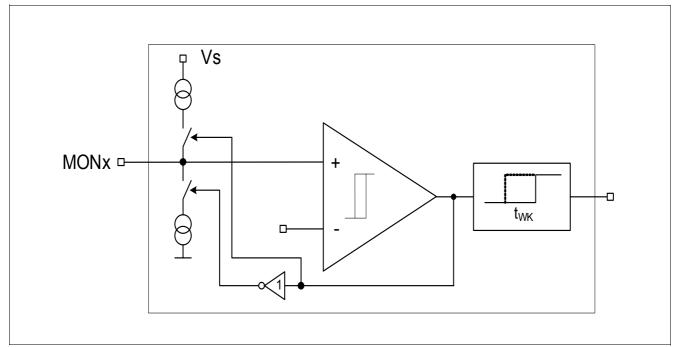

# 10 Monitoring / Wake-Up Inputs MON1 ... 5 and Wake-Up Event Signalling

In addition to a wake-up from SBC Stop / Sleep Mode via the LIN bus line it is also possible to wake-up the TLE7809G from low power mode via the monitoring/wake-up inputs. These inputs are sensitive to a transition of the voltage level, either from high to low or vice versa. Monitoring is available in Active Mode and indicates the voltage level of the inputs via SPI status bits.

A positive or negative voltage edge at MONx in SBC Sleep or Stop Mode results in signalling a wake-up event (via SBC [DO] to  $\mu$ C [P1.4] interconnect). After a wake-up via MONx the first transmission of the SPI diagnosis word in SBC Standby mode indicates the wake-up source. Further SPI status word transmissions show the logic level at the monitoring input pins.

Note: Immediately before switching the TLE7809G into a SBC power saving mode the activated MONx are initialized with the actual logic level detected at the MONx. In case a MONx is deactivated it can neither be used as wake-up source nor can it be used to detect logic levels.

However, there should be a minimum delay of three times "CSN high time" (see **Table "SPI Data Input Timing1)**" on Page 42) between activation of MONx and entering a power saving mode.

The monitoring input module consists of an input circuit with pull-up and pull-down current sources to define a certain voltage level with open inputs and a filter function to avoid wake-up events caused by unwanted voltage transients at the module inputs.

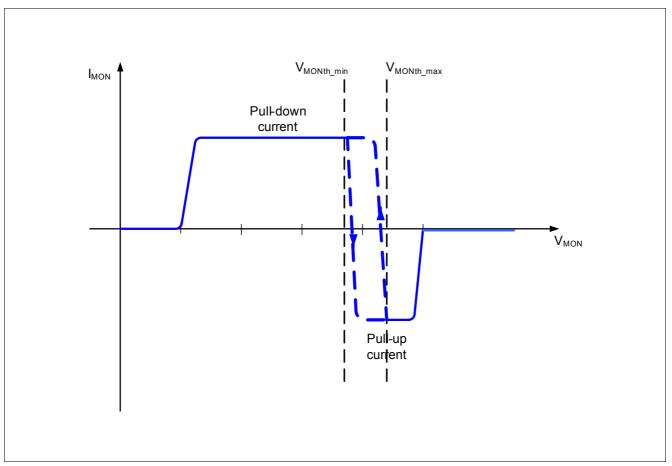

At a voltage level at the monitoring pins of  $V_{\text{MON\_th}} < V_{\text{MONx}} < 5.5 \text{ V}$  the pull-up current source becomes active, while at 1 V <  $V_{\text{MONx}} < V_{\text{MON\_th}}$  the pull-down sink is activated (see **Figure 11**) guaranteeing stable levels at the monitoring/wake-up inputs. Below and above these voltage ranges the current is minimized to a leakage current (see "Monitoring Inputs MONx" on Page 37).

Figure 11 Monitoring Input Block Diagram

## Monitoring / Wake-Up Inputs MON1 ... 5 and Wake-Up Event Signalling

Figure 12 Monitoring Input Characteristics

**Low Side Switches**

#### 11 Low Side Switches

The low side switches LS1 and LS2 have been designed to drive relays, e.g. in window lift applications. The continuous output current is dimensioned for 300mA (each) maximum. In SBC Active and LIN Receive-Only mode the low side outputs can be switched on and off, respectively via an SPI input bit. Protection against overcurrent, overtemperature and overvoltage conditions is integrated in the low-side drivers.

In case of a load current that is exceeding the overcurrent threshold both drivers are switched-off after a filter time. A thermal protection circuit is included as well, and is switching-off the drivers in case the overtemperature threshold is reached. In both cases the SPI diagnostic information is updated accordingly and the ERR interconnect is pulled "low" for **one internal cycle** (see "SBC Oscillator" on Page 36). The drivers have to be re-activated via SPI command. An overvoltage protection has been implemented by active clamping for inductive loads preventing the occurrence of voltage peaks.

Moreover the switches are automatically disabled when a reset or watchdog reset occurs. However, the switches are not automatically switched off in case of an overvoltage condition, e.g. load dump. If a double-failure occurs at the same time causing an overcurrent (OC) or overtemperature (OT) condition, than the LSx are turned off in order to protect the IC.

Note: In case one LSx is turned off due to an OC / OT condition the second LSx is turned off automatically (bidirectional ERR interconnect pulled "low").

The LSx can also be switched off by the microcontroller by pulling the bi-directional ERR interconnect "low" for at least one internal cycle (see "SBC Oscillator" on Page 36).

Data Sheet 28 Rev. 3.01, 2008-04-15

**Supply Output for Hall Sensor Supply**

# 12 Supply Output for Hall Sensor Supply

The SUPPLY Output is intended to be used as Hall Sensor supply. In SBC Active and LIN Receive-Only mode this output can be switched on and off, respectively via an SPI input bit.

Note: The SUPPLY Output needs to be turned-off prior to entering **SBC Stop Mode** via SPI command as it will inherit the "on or off state" from the previous operation mode. In case of entering SBC Sleep Mode it is turned-off automatically.

This output provides an output voltage limitation and is protected against overcurrent and overtemperature. The protection mechanisms for the low-sides switches also apply for this high-side switch. In case of an overcurrent shutdown the supply output can be re-activated via SPI command. In order to prevent an unintended shut-down due to an overcurrent situation when a capacitive load is connected, a specified blanking time after switching-on has been implemented and is applied directly after activation of this output.

Data Sheet 29 Rev. 3.01, 2008-04-15

High-Side Switch as LED Driver (HS-LED)

# 13 High-Side Switch as LED Driver (HS-LED)

The high side output HS\_LED is intended for driving LEDs or small lamps. This function and the wake-up function via MON5 input are realized on the same pin (MON5/HS\_LED). In SBC Active and LIN Receive-Only mode the high side output can be switched on and off, respectively via an SPI input bit (automatically "off" in SBC Stop Mode).

The high-side driver is protected against overcurrent and overtemperature. The HS-LED is automatically disabled in case of an undervoltage ( $V_{\rm bat}$ -UV) and overvoltage condition ( $V_{\rm bat}$ -OV) and can only be re-activated via SPI command. This HS-LED OV/UV feature can be disabled via SPI bit (see **Table 5 "General & Integrated Switch Configuration" on Page 21**).

General Purpose I/Os (GPIO)

# 14 General Purpose I/Os (GPIO)

The pins P0.3 / P0.4 / P0.5 and P2.0 / P2.1 provide general purpose functionality, like Hall Sensor inputs, PWM output and capture. GPIOs P0.0, P0.1 and P0.2 are available in user mode only (alternate JTAG functionality). For further information see dedicated XC866 User's Manual and/or Data Sheet.

Data Sheet 31 Rev. 3.01, 2008-04-15

**Error Interconnect (ERR)**

# 15 Error Interconnect (ERR)

The ERR interconnect provides a bi-directional error signalization. The ERR output (active low) immediately signals that a low side switch LSx has been shut down due to overcurrent or overtemperature condition. If the ERR signal is pulled "low" by the microcontroller for at least one internal cycle (see "SBC Oscillator" on Page 36), the low side switches LS1/LS2 are turned off (see Table 10 "Diagnostic, Protection and Safety Functions" on Page 23).

# 16 General Product Characteristics

# 16.1 Absolute Maximum Ratings

#### Table 12 Absolute Maximum Ratings<sup>1)</sup>

$T_{\rm j}$  = -40 °C to +125 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.      | Parameter                                                                            | Symbol                         | Limit               | Values                | Unit | Conditions                                                                                         |  |

|-----------|--------------------------------------------------------------------------------------|--------------------------------|---------------------|-----------------------|------|----------------------------------------------------------------------------------------------------|--|

|           |                                                                                      |                                | Min.                | Max.                  |      |                                                                                                    |  |

| Voltages  | s                                                                                    | •                              | •                   |                       |      |                                                                                                    |  |

| 16.1.1    | Supply voltage                                                                       | $V_{S}$                        | -0.3                | 40                    | V    | _                                                                                                  |  |

| 16.1.2    | Regulator output voltage                                                             | $V_{\sf CC}$                   | -0.3                | 5.5                   | V    | _                                                                                                  |  |

| 16.1.3    | Input voltage at MON1-4                                                              | $V_{MONx}$                     | V <sub>S</sub> - 40 | 40                    | V    | also for pulses according to ISO 7637; external series resistor $R > 1.0 \text{ k}\Omega$ required |  |

| 16.1.4    | Input voltage at MON5/HS_LED (output)                                                | V <sub>MON5</sub>              | V <sub>S</sub> - 40 | V <sub>S</sub> + 0.3  | V    | MON5 input voltage limited due to LED driver functionality. $R > 1.0 \text{ k}\Omega$ required     |  |

| 16.1.5    | Input voltage at $V_{\mathrm{BAT\_SENSE}}$                                           | $V_{BATSENSE}$                 | V <sub>S</sub> - 40 | 40                    | V    | also for pulses according to ISO 7637; external series resistor $R > 1.0 \text{ k}\Omega$ required |  |

| 16.1.6    | Low-Side Switches LSx                                                                | $V_{LSx}$                      | -0.3                | $V_{LSx\_CL}$         | V    | limited by output clamping voltage & clamping energy                                               |  |

| 16.1.7    | SUPPLY Output                                                                        | $V_{Supply}$                   | -0.3                | V <sub>S</sub> + 0.3  | V    | _                                                                                                  |  |

| 16.1.8    | Logic input voltages (TMS, TCK, TDI, CLKIN)                                          | $V_1$                          | -0.3                | V <sub>CC</sub> + 0.3 | V    | 0 V < V <sub>S</sub> < 27 V<br>0 V < V <sub>CC</sub> < 5.5 V                                       |  |

| 16.1.9    | Logic output voltage (TDO, RESET)                                                    | $V_{\mathrm{DRI},\mathrm{RD}}$ | -0.3                | V <sub>CC</sub> + 0.3 | V    | 0 V < V <sub>S</sub> < 27 V<br>0 V < V <sub>CC</sub> < 5.5 V                                       |  |

| 16.1.10   | LIN line bus input voltages                                                          | $V_{bus}$                      | V <sub>S</sub> - 40 | 40                    | V    | _                                                                                                  |  |

| 16.1.11   | Electrostatic discharge voltage "HBM" at pin LIN, MONx, $V_{\rm BAT\_SENSE}$ vs. GND | $V_{ESD}$                      | -4                  | 4                     | kV   | EIA/JESD22-A114-B<br>C = 100 pF,<br>$R$ = 1.5 k $\Omega$                                           |  |

| 16.1.12   | Electrostatic discharge voltage "HBM" at pin $V_{\rm DDC}$ vs. GND                   | $V_{ESD}$                      | -600                | 600                   | V    | EIA/JESD22-A114-B<br>C = 100 pF; $R$ = 1.5 kΩ                                                      |  |

| 16.1.13   | Electrostatic discharge voltage "HBM" at any other pin                               | $V_{ESD}$                      | -2                  | 2                     | kV   | EIA/JESD22-A114-B<br>C = 100 pF; $R$ = 1.5 kΩ                                                      |  |

| 16.1.14   | Electrostatic discharge voltage "CDM" at any pin                                     | $V_{ESD}$                      | -500                | 500                   | V    | Charged device model;<br>according to AEC Q100-011<br>Rev-B                                        |  |

| Tempera   | atures                                                                               | 1                              | 1                   |                       | 1    | •                                                                                                  |  |