### **Smart Quad Low-Side Switch**

#### **Features**

- Shorted circuit protection

- Overtemperature protection

- Overvoltage protection

- Open Load Detection

- Direct parallel control of the inputs

- Inputs high or low active programmable

- · General fault flag

- Very low standby quiescent current

- Compatible with 3V microcontrollers

- Electostatic discharge (ESD) protection

### **Application**

- μC compatible power switch for 12 V applications

- · Switch for automotive and industrial systems

- · Line, relay or lamp driver

## General description

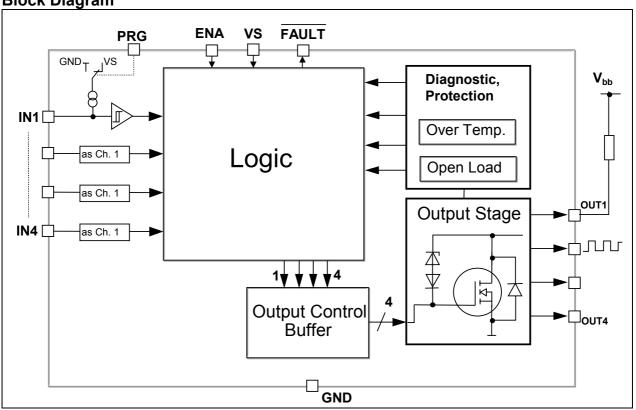

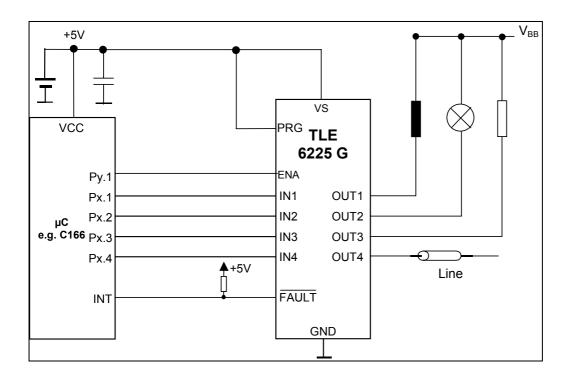

Quad channel Low-Side Switch in Smart Power Technology (SPT) with four separate inputs and four open drain DMOS output stages. The TLE 6225 G is protected by embedded protection functions and designed for automotive and industrial applications, to drive lines, lamps and relays.

### **Block Diagram**

#### **Product Summary**

| Supply voltage       | Vs                     | 4.5 – 32 | V  |

|----------------------|------------------------|----------|----|

| Drain source voltage | $V_{\text{DS(AZ)max}}$ | 60       | V  |

| On resistance        | $R_{ON}$               | 1.7      | Ω  |

| Output current(each) | $I_{D(NOM)}$           | 350      | mΑ |

| (individ.)           |                        | 500      | mΑ |

## **Pin Description**

| Pin | Symbol | Function                            |  |  |

|-----|--------|-------------------------------------|--|--|

| 1   | IN1    | Input Channel 1                     |  |  |

| 2   | IN2    | Input Channel 2                     |  |  |

| 3   | FAULT  | General Fault Flag                  |  |  |

| 4   | GND    | Ground                              |  |  |

| 5   | GND    | Ground                              |  |  |

| 6   | GND    | Ground                              |  |  |

| 7   | GND    | Ground                              |  |  |

| 8   | VS     | Supply Voltage                      |  |  |

| 9   | IN3    | Input Channel 3                     |  |  |

| 10  | IN4    | Input Channel 4                     |  |  |

| 11  | ENA    | Enable for all channels/Standby     |  |  |

| 12  | OUT4   | Power Output channel 4              |  |  |

| 13  | OUT3   | Power Output channel 3              |  |  |

| 14  | GND    | Ground                              |  |  |

| 15  | GND    | Ground                              |  |  |

| 16  | GND    | Ground                              |  |  |

| 17  | GND    | Ground                              |  |  |

| 18  | OUT2   | Power Output channel 2              |  |  |

| 19  | OUT1   | Power Output channel 1              |  |  |

| 20  | PRG    | Program (inputs high or low active) |  |  |

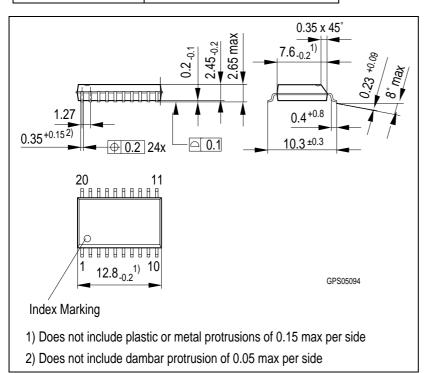

## Pin Configuration (Top view)

| IN1   | 1● | 20 | PRG  |

|-------|----|----|------|

| IN2   | 2  | 19 | OUT1 |

| FAULT | 3  | 18 | OUT2 |

| GND   | 4  | 17 | GND  |

| GND   | 5  | 16 | GND  |

| GND   | 6  | 15 | GND  |

| GND   | 7  | 14 | GND  |

| VS    | 8  | 13 | OUT3 |

| IN3   | 9  | 12 | OUT4 |

| IN4   | 10 | 11 | ENA  |

P-DSO-20-6

# Maximum Ratings for $T_j = -40$ °C to 150°C

| Parameter                                                                                                   | Symbol                                | Values       | Unit |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|------|

| Supply Voltage                                                                                              | V <sub>S</sub>                        | -0.3 +40     | V    |

| Continuous Drain Source Voltage (OUT1OUT4)                                                                  | V <sub>DS</sub>                       | -0.7 +45     | V    |

| Input Voltage, IN1 - IN4                                                                                    | V <sub>IN</sub>                       | - 0.3 + 7    | V    |

| Input Voltage, PRG, ENA                                                                                     | V <sub>IN</sub>                       | - 0.3 + 40   | V    |

| Output Load Dump Protection V <sub>Load Dump</sub> =U <sub>P</sub> +U <sub>S</sub> ; U <sub>P</sub> =13.5 V | V <sub>Load Dump</sub> <sup>2</sup> ) | 75           | V    |

| With Automotive Relay Load $R_L$ = 70 $\Omega$                                                              | ·                                     |              |      |

| $R_1^{(1)} = 2 \Omega$ ; $t_d = 400 \text{ms}$ ; IN = low or high                                           |                                       |              |      |

| FAULT Output Voltage                                                                                        | $V_{Fault}$                           | - 0.3 + 40   | V    |

| Operating Temperature Range                                                                                 | T <sub>j</sub>                        | - 40 + 150   | °C   |

| Storage Temperature Range                                                                                   | $T_{ m stg}$                          | - 55 + 150   |      |

| Output Current per Channel (see electrical characteristics)                                                 | $I_{D(lim)}$                          | self limited | Α    |

| Output Clamping Energy                                                                                      | <b>E</b> AS                           | 10           | mJ   |

| I <sub>D</sub> = 0.2 A                                                                                      |                                       |              |      |

| Power Dissipation (DC) @ $T_A$ = 25 °C (on PCB 6 cm <sup>2</sup> cooling area)                              | P <sub>tot</sub>                      | 2.5          | W    |

| Electrostatic Discharge Voltage (Human Body Model)                                                          | V <sub>ESD</sub>                      | 2000         | V    |

| according to MIL STD 883D, method 3015.7 and EOS/ESD assn. standard S5.1 - 1993                             |                                       |              |      |

| DIN Humidity Category, DIN 40 040                                                                           |                                       | E            |      |

| IEC Climatic Category, DIN IEC 68-1                                                                         |                                       | 40/150/56    |      |

| Thermal Resistance                                                                                          |                                       |              |      |

| junction - pin                                                                                              | $R_{thJP}$                            | 23           | K/W  |

| junction - ambient @ min. footprint                                                                         | $R_{thJA}$                            | 80           |      |

| junction - ambient @ 6 cm <sup>2</sup> cooling area                                                         | $R_{thJA}$                            | 45           |      |

<sup>1)</sup>  $R_l$ =internal resistance of the load dump test pulse generator LD200 2)  $V_{LoadDump}$  is setup without DUT connected to the generator per ISO 7637-1 and DIN 40 839.

# **Electrical Characteristics**

| Parameter and Conditions                                                                             | Symbol                         | <u> </u>           |                    |                    | Unit |

|------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|--------------------|--------------------|------|

| $V_S = 4.5 \text{ to } 32 \text{ V} ; T_j = -40 ^{\circ}\text{C} \text{ to } + 150 ^{\circ}\text{C}$ |                                | min                | typ                | max                |      |

| (unless otherwise specified)                                                                         |                                |                    |                    |                    |      |

| 1. Power Supply                                                                                      |                                |                    | ı                  | 1                  | 1    |

| Supply Voltage                                                                                       | <b>V</b> s                     | 4.5                |                    | 32                 | V    |

| Supply Current (ENA = H, Outputs ON)                                                                 | I <sub>S(ON)</sub>             |                    | 1                  | 2                  | mA   |

| Supply Current in Standby Mode (ENA = L)                                                             | I <sub>S(stby)</sub>           |                    |                    | 10                 | μA   |

| 2. Power Outputs                                                                                     |                                |                    |                    |                    |      |

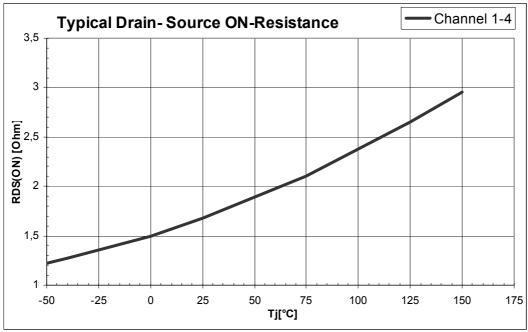

| ON Resistance $V_S \ge 6 \text{ V}$ ; $I_D = 300 \text{ mA}$ $T_J = 25^{\circ}\text{C}$              | R <sub>DS(ON)</sub>            |                    | 1.7                | 2                  | Ω    |

| $T_{J} = 150^{\circ}C$                                                                               |                                |                    | 3                  | 3.6                |      |

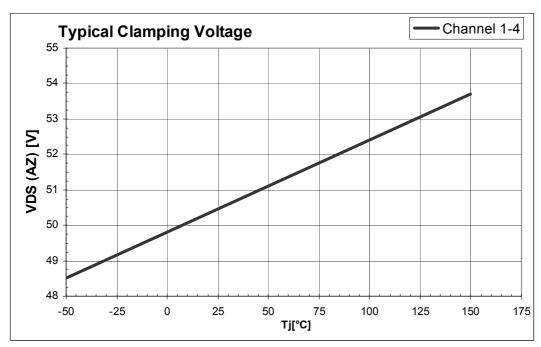

| Output Clamping Voltage Output OFF                                                                   | $V_{\rm DS(AZ)}$               | 45                 | 50                 | 60                 | V    |

| Current Limit                                                                                        | $I_{D(lim)}$                   | 500                | 750                | 1000               | mA   |

| Output Leakage Current $V_{ENA} = L$                                                                 | I <sub>D(lkg)</sub>            |                    |                    | 5                  | μA   |

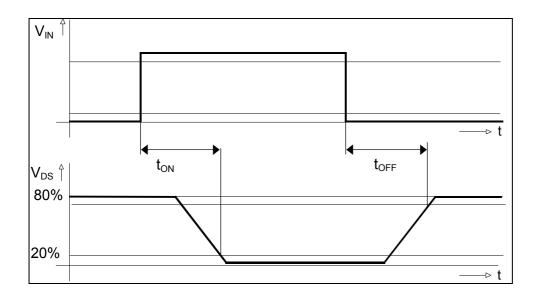

| Turn-On Time $I_D = 200 \text{ mA}$ , resistive load                                                 | ton                            |                    | 5                  | 10                 | μs   |

| Turn-Off Time $I_D = 200 \text{ mA}$ , resistive load                                                | t <sub>OFF</sub>               |                    | 5                  | 10                 | μs   |

| 3. Digital Inputs (IN1 – IN4, ENA, PRG)                                                              |                                |                    |                    |                    |      |

| Input Low Voltage (IN1 – IN4, PRG)                                                                   | $V_{INL}$                      | - 0.3              |                    | 1                  | V    |

| Input Low Voltage (ENA)                                                                              | $V_{INL}$                      | - 0.3              |                    | 0.8                | V    |

| Input High Voltage                                                                                   | $V_{INH}$                      | 2.0                |                    |                    | V    |

| Input Voltage Hysteresis (IN1 – IN4, PRG)                                                            | $V_{INHys}$                    | 50                 | 100                |                    | mV   |

| Input Voltage Hysteresis (ENA)                                                                       | $V_{INHys}$                    | 20                 | 100                |                    | mV   |

| Input Pull Up Current (IN1IN4) @ PRG = L,                                                            | I <sub>IN(14)PU</sub>          | 20                 | 50                 | 100                | μA   |

| $V_{IN} = 0V$                                                                                        |                                |                    |                    |                    |      |

| Input Pull Down Current (IN1IN4) @ PRG = H,                                                          | I <sub>IN(14)PD</sub>          | 20                 | 50                 | 100                | μA   |

| $V_{IN} < V_S$ ; $V_{IN} < 6$                                                                        |                                |                    |                    |                    |      |

| PRG, ENA Pull Down Current $V_{IN} = 5 V$                                                            | I <sub>IN(PRG,ENA)</sub>       | 20                 | 50                 | 100                | μA   |

| PRG, ENA Pull Down Current $V_{IN} = 14 \text{ V}$                                                   | $I_{\text{IN(PRG,ENA)}}$       |                    |                    | 200                | μA   |

| 4. Digital Output (FAULT)                                                                            |                                |                    |                    |                    |      |

| FAULT Output Low Voltage $I_{FAULT} = 1.6 \text{ mA}$                                                | $V_{FAULTL}$                   |                    |                    | 0.4                | V    |

| 5. Diagnostic Functions                                                                              |                                |                    |                    |                    |      |

| Open Load/Short to Ground Detection Voltage                                                          | $V_{\mathrm{DS}(\mathrm{OL})}$ | 0.4*V <sub>S</sub> | 0.5*V <sub>S</sub> | 0.6*V <sub>S</sub> | V    |

| Output Pull Down Current                                                                             | $I_{PD(OL)}$                   | 20                 | 50                 | 200                | μΑ   |

| Fault Delay Time; V <sub>S</sub> = 12V                                                               | t <sub>d(fault)</sub>          | 50                 | 100                | 200                | μs   |

| Overtemperature Shutdown Threshold                                                                   | $T_{th(sd)}$                   | 170                |                    | 200                | °C   |

| Hysteresis                                                                                           | $T_{hys}$                      |                    | 10                 |                    | K    |

## **Functional Description**

The TLE 6225 G is a quad channel low-side switch with four power DMOS stages. The power transistors are protected against short to  $V_{BB}$ , overload, overtemperature and against overvoltage by zenerclamp.

The diagnostic logic recognises a fault condition which is indicated by a fault flag.

## **Circuit Description**

### **Output Stage Control**

Each output is independently controlled by an input pin and a common enable line, which enables/disables all four outputs. The parallel inputs are high or low active depending on the PRG pin. If the parallel input pins are not connected (independent of high or low activity) it is guaranteed that the outputs 1 to 4 are switched OFF. ENA - and PRG - pin itself are internally pulled down when they are not connected.

**ENA** - Enable pin. ENA = High: Active mode. Channels are enabled

ENA = Low (GND): Sleep mode. Channels are switched off. Less than

1 μA current consumption.

**PRG** - Program pin. PRG = High: Parallel inputs Channel 1 to 4 are high active

PRG = Low (GND): Parallel inputs Channel 1 to 4 are low active.

#### **Power Transistors**

Each of the four output stages has its own zenerclamp. This causes a voltage limitation at the power transistors when inductive loads are switched off. The outputs are provided with a current limitation set to a minimum of 500 mA.

Each output is protected by embedded protection functions. In the event of an overload or short to supply, the current is internally limited. If this operation leads to an overtemperature condition, a second protection level (about 170 °C) will turn the effected output into a PWM-mode (selective thermal shutdown with restart) to prevent critical chip temperatures. The temperature hysteresis is typically 10K.

#### **Diagnostic**

The FAULT pin is an open drain output. The logic status depends on the programming pin PRG.

$\overline{FAULT}$  - pin.  $\overline{FAULT}$  = High no fault @ PRG = High

FAULT = Low no fault @ PRG = Low

### **Diagnostic Table**

| Operating Condition          | Enable<br>Input | Program<br>Input | Control<br>Input | Power<br>Output        | Diagnostic<br>Output |

|------------------------------|-----------------|------------------|------------------|------------------------|----------------------|

|                              | ENA             | PRG              | IN               | OUT                    | FAULT                |

| Standby                      | L               | X                | Х                | OFF                    | Н                    |

| Normal function              | H<br>H<br>H     | L<br>L<br>H      | LHLH             | ON<br>OFF<br>OFF<br>ON | L<br>L<br>H          |

| Overtemperature              | нн              | L<br>H           | ПП               | OFF *<br>OFF *         | H<br>L               |

| Open load or short to ground | HHHH            | L<br>L<br>H      | <b>-</b> エ - エ   | ON<br>OFF<br>OFF<br>ON | L<br>H<br>L<br>H     |

X = not relevant

### **Fault Distinction**

Open load/short to ground is recognised in OFF-state. Overtemperature as a result of an overload or short to battery can only arise in ON-state. If there is only one fault at a time, it is possible to distinguish which channel is affected with which fault.

<sup>\*</sup>selective thermal shutdown for each channel at overtemperature

## **Typical electrical Characteristics**

### **Drain-Source on-resistance**

$R_{DS(ON)} = f(T_j)$ ;  $V_s = 5V$

**Figure 6**: Typical ON Resistance versus Junction-Temperature Channel 1-4

## **Output Clamping Voltage**

$V_{DS(AZ)} = f(T_j)$ ;  $V_s = 5V$

**Figure 7**: Typical Clamp Voltage versus Junction-Temperature Channel 1-4

## **Timing Diagrams**

## **Power Outputs**

## **Application Circuit**

## Package and ordering code

#### all dimensions in mm

P - DSO - 20 - 6

Ordering code

TLE 6225 G

Q 67006 A9373

Published by Infineon Technologies AG, Bereichs Kommunikation St.-Martin-Strasse 76, D-81541 München © Infineon Technologies AG 1999 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

9