### 2-Phase Stepper-Motor Driver

**TLE 4727**

#### Bipolar IC

#### Overview

#### **Features**

- 2 × 0.7 amp. outputs

- Integrated driver, control logic and current control (chopper)

- · Fast free-wheeling diodes

- Max. supply voltage 45 V

- · Outputs free of crossover current

- Offset-phase turn-ON of output stages

- All outputs short-circuit proof

- 5 V output for logic supply

- Error-flag for overload, open load, overtemperature

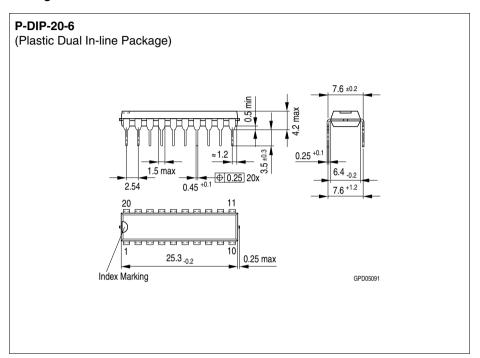

| Туре     | Ordering Code | Package    |

|----------|---------------|------------|

| TLE 4727 | on request    | P-DIP-20-6 |

### Description

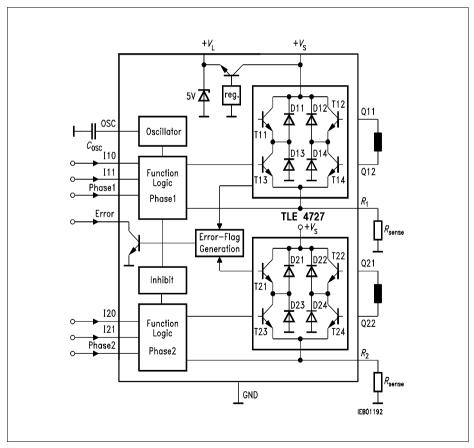

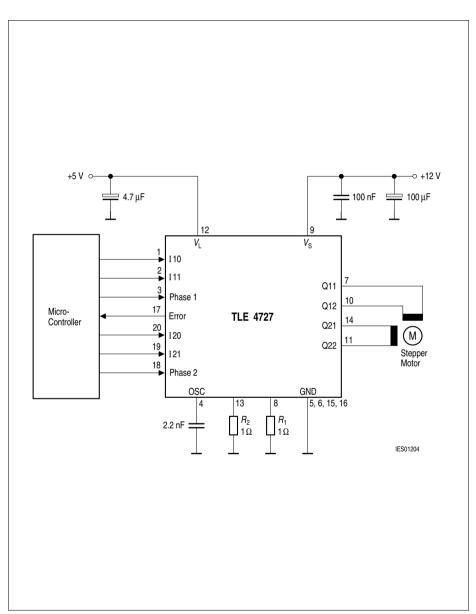

The TLE 4727 is a bipolar, monolithic IC for driving bipolar stepper motors, DC motors and other inductive loads that operate on constant current. The control logic and power output stages for two bipolar windings are integrated on a single chip which permits switched current control of motors with 0.7 A per phase at operating voltages up to 16 V.

The direction and value of current are programmable for each phase via separate control inputs. A common oscillator generates the timing for the current control and turn-on with phase offset of the two output stages. The two output stages in a full-bridge configuration include fast integrated free-wheeling diodes and are free of crossover current. The device can be driven directly by a microprocessor in several modes by programming phase direction and current control of each bridge independently.

A stabilized 5 V output allows the supply of external components up to 5 mA. With the error output the TLE 4727 signals malfunction of the device. Setting the control inputs high resets the error flag and by reactivating the bridges one by one the location of the error can be found.

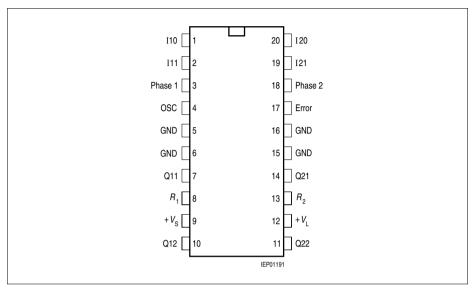

Figure 1 Pin Configuration (top view)

## **Pin Definitions and Functions**

|                       | Function                                                                                                                                     |                                                                                           |                                                                                                                                                        |                                                                                                    |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1, 2, 19, 20          | the particula                                                                                                                                | ar phase                                                                                  |                                                                                                                                                        | gnitude of the <b>current</b> of                                                                   |

|                       | $I_{\text{set}} = 500 \text{ m}$                                                                                                             | A with R                                                                                  | Sense = 1 Ω                                                                                                                                            |                                                                                                    |

|                       | Current Co<br>IX1                                                                                                                            | ontrol<br>IX0                                                                             | Phase Current                                                                                                                                          | Example of Motor Status                                                                            |

|                       | Н                                                                                                                                            | Н                                                                                         | 0                                                                                                                                                      | No current 1)                                                                                      |

|                       | Н                                                                                                                                            | L                                                                                         | $0.14 \times I_{\text{set}}$                                                                                                                           | Hold                                                                                               |

|                       | L                                                                                                                                            | Н                                                                                         | I <sub>set</sub>                                                                                                                                       | Normal mode                                                                                        |

|                       | L                                                                                                                                            | L                                                                                         | $1.4 \times I_{\text{set}}$                                                                                                                            | Accelerate                                                                                         |

|                       | 1) "No current<br>below 3 mA                                                                                                                 |                                                                                           | ridges inhibits the circuit an                                                                                                                         | d current consumption will sink                                                                    |

| 3                     |                                                                                                                                              | the phas                                                                                  | e current flows from C                                                                                                                                 | gh phase winding 1. On<br>111 to Q12, on L-potential                                               |

| 4                     |                                                                                                                                              | works at                                                                                  | typ. 25 kHz if this pin                                                                                                                                | is wired to ground across                                                                          |

|                       | 2.2 nF.                                                                                                                                      |                                                                                           |                                                                                                                                                        | g                                                                                                  |

| 5, 6, 15, 16          |                                                                                                                                              | pins are                                                                                  | e connected at leadfra                                                                                                                                 |                                                                                                    |

| 5, 6, 15, 16<br>7, 10 | Ground; all                                                                                                                                  | outputs                                                                                   | e connected at leadfra                                                                                                                                 | me internally.                                                                                     |

|                       | Ground; all Push-pull o wheeling di                                                                                                          | outputs<br>odes.                                                                          |                                                                                                                                                        | me internally. with integrated free-                                                               |

| 7, 10                 | Ground; all Push-pull of wheeling die Resistor R Supply vol                                                                                  | outputs<br>odes.<br>for sens<br>tage; blo                                                 | Q11, Q12 for phase 1 sing the current in phack to ground, as closelytic capacitor of at least                                                          | me internally. with integrated free-                                                               |

| 7, 10                 | Ground; all  Push-pull of wheeling die Resistor R.  Supply volumith a stable ceramic cap                                                     | outputs odes. I for sens tage; blo e electro oacitor of outputs                           | Q11, Q12 for phase 1 sing the current in phack to ground, as closelytic capacitor of at least                                                          | me internally.  with integrated free- ase 1. e as possible to the IC, ast 47 µF in parallel with a |

| 7, 10<br>8<br>9       | Ground; all  Push-pull of wheeling did  Resistor R  Supply vol with a stable ceramic cap  Push-pull of wheeling did  Logic supp supply up to | outputs odes. I for sens tage; blo e electro pacitor of outputs odes. bly volta o 5 mA; s | Q11, Q12 for phase 1 sing the current in phase cock to ground, as closelytic capacitor of at leaf 100 nF. Q22, Q21 for phase 2 ge; internally generate | me internally.  with integrated free- ase 1. e as possible to the IC, ast 47 µF in parallel with a |

## Pin Definitions and Functions (cont'd)

| Pin No. | Function                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | <b>Error output</b> ; signals with "low" the errors: open load or short circuit to ground of one or more outputs or short circuits of the load or overtemperature. |

| 18      | Input phase 2; controls the current flow through phase winding 2. On H-potential the phase current flows from Q21 to Q22, on L-potential in the reverse direction. |

Figure 2 Block Diagram

Datasheet 4 2005-07-20

## **Absolute Maximum Ratings**

Temperature  $T_i = -40$  to 150 °C

| Parameter                               | Symbol        | Limit Values |      | Unit | Remarks           |

|-----------------------------------------|---------------|--------------|------|------|-------------------|

|                                         |               | min.         | max. |      |                   |

| Supply voltage                          | $V_{S}$       | - 0.3        | 45   | V    | _                 |

| Error outputs                           | $V_{Err}$     | - 0.3        | 45   | V    | _                 |

|                                         | $I_{Err}$     | _            | 3    | mA   | _                 |

| Logic supply voltage                    | $V_{L}$       | - 0.3        | 6.5  | ٧    | _                 |

| Output current of V <sub>L</sub>        | $I_{L}$       | <b>-</b> 5   | 1)   | mA   | 1) Int. limited   |

| Output current                          | $I_{Q}$       | <b>– 1</b>   | 1    | Α    | _                 |

| Ground current                          | $I_{GND}$     | -2           | _    | Α    | _                 |

| Logic inputs                            | $V_{IXX}$     | <b>– 15</b>  | 15   | ٧    | IXX; Phase X      |

| Oscillator voltage                      | $V_{Osc}$     | - 0.3        | 6    | ٧    | _                 |

| $R_1$ , $R_2$ input voltage             | $V_{RX}$      | - 0.3        | 5    | V    | _                 |

| Junction temperature                    | $T_{\rm j}$   | _            | 125  | °C   | _                 |

|                                         | $T_{\rm j}$   | _            | 150  | °C   | Max. 10,000 h     |

| Storage temperature                     | $T_{\rm stg}$ | - 50         | 125  | °C   | _                 |

| Thermal resistance                      |               |              |      |      |                   |

| Junction ambient                        | $R_{thja}$    | _            | 56   | K/W  | _                 |

| Junction ambient (soldered on a         | $R_{thja}$    | _            | 40   | K/W  | _                 |

| 35 μm thick 20 cm <sup>2</sup> PC board |               |              |      |      |                   |

| copper area)                            |               |              |      |      |                   |

| Junction case                           | $R_{th\ jc}$  | _            | 18   | K/W  | Measured on pin 5 |

Note: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Operating Range**

| Parameter                 | Symbol              | Limit Values |         | Unit    | Remarks                                           |

|---------------------------|---------------------|--------------|---------|---------|---------------------------------------------------|

|                           |                     | min.         | max.    |         |                                                   |

| Supply voltage            | $V_{S}$             | 5            | 16      | ٧       | _                                                 |

| Current from logic supply | $I_{L}$             | _            | 5       | mA      | _                                                 |

| Case temperature          | $T_{C}$             | - 40         | 110     | °C      | Measured on pin 5 $P_{\text{diss}} = 2 \text{ W}$ |

| Output current            | $I_{Q}$             | - 800        | 800     | mA      | _                                                 |

| Logic inputs              | $V_{IXX}$           | - 5          | 6       | ٧       | IXX; Phase 1, 2                                   |

| Error output              | $V_{Err} \ I_{Err}$ | _<br>0       | 25<br>1 | V<br>mA |                                                   |

Note: In the operating range, the functions given in the circuit description are fulfilled.

### Characteristics

$V_{\rm S}$  = 6 to 16 V;  $T_{\rm i}$  = -40 to 130 °C

| Parameter               | eter Symbol Limit Values |      | lues | Unit | <b>Test Condition</b> |                             |

|-------------------------|--------------------------|------|------|------|-----------------------|-----------------------------|

| -                       |                          | min. | typ. | max. |                       |                             |

| Current Consumption     |                          |      |      |      |                       |                             |

| from + V <sub>S</sub>   | $I_{S}$                  | 1    | 2    | 3    | mA                    | IXX = H                     |

| from + $V_S$            | $I_{S}$                  | 20   | 30   | 50   | mA                    | IXX = L;                    |

|                         |                          |      |      |      |                       | $I_{Q1, 2} = 0 A$           |

| Oscillator              |                          |      |      |      |                       |                             |

| Output charging current | $I_{\mathrm{Osc}}$       | 90   | 120  | 135  | μА                    | _                           |

| Charging threshold      | $V_{\sf OscL}$           | 8.0  | 1.3  | 1.9  | V                     | _                           |

| Discharging threshold   | $V_{OscH}$               | 1.7  | 2.3  | 2.9  | ٧                     | _                           |

| Frequency               | $f_{\sf Osc}$            | 18   | 24   | 30   | kHz                   | $C_{\rm OSC} = 2.2  \rm nF$ |

## Characteristics (cont'd)

$V_{\rm S}$  = 6 to 16 V;  $T_{\rm i}$  = -40 to 130 °C

| Parameter                                 | Symbol       | Limit Values |      |      | Unit | <b>Test Condition</b> |  |

|-------------------------------------------|--------------|--------------|------|------|------|-----------------------|--|

|                                           |              | min.         | typ. | max. |      |                       |  |

| Phase Current ( $V_S = 9$ to 16 V)        | )            |              |      |      |      |                       |  |

| Mode "no current"                         | $I_{Q}$      | -2           | 0    | 2    | mA   | IX0 = H;              |  |

| Voltage threshold of current              | · ·          |              |      |      |      | IX1 = H               |  |

| comparator at $R_{\text{sense}}$ in mode: |              |              |      |      |      |                       |  |

| Hold                                      | $V_{\sf ch}$ | 40           | 70   | 100  | mV   | IX0 = L; IX1 = H      |  |

| Setpoint                                  | $V_{cs}$     | 450          | 500  | 570  | mV   | IX0 = H; IX1 = L      |  |

| Accelerate                                | $V_{ca}$     | 630          | 700  | 800  | mV   | IX0 = L; IX1 = L      |  |

## Logic Inputs (IX1 ; IX0 ; phase X)

| . J . P            | ,         |             |            |     |    |                             |

|--------------------|-----------|-------------|------------|-----|----|-----------------------------|

| Threshold          | $V_{I}$   | 1.2         | 1.7        | 2.2 | V  | _                           |

| Hysteresis         | $V_{IHv}$ | _           | 50         | _   | mV | _                           |

| Low-input current  | $I_{IL}$  | <b>– 10</b> | <b>– 1</b> | 1   | μΑ | $V_{\rm I} = 1.2 \text{ V}$ |

| Low-input current  | $I_{IL}$  | - 100       | - 20       | - 5 | μΑ | $V_{\rm I} = 0 \text{ V}$   |

| High-input current | $I_{IH}$  | <b>–</b> 1  | 0          | 10  | μΑ | $V_{\rm I} = 5 \ {\rm V}$   |

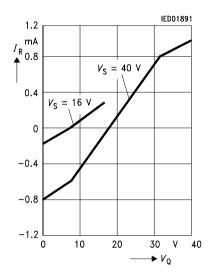

## **Error Output**

| Saturation voltage | $V_{ErrSat}$ | 50 | 200 | 500 | mV | $I_{\rm Err} = 1  {\rm mA}$ |

|--------------------|--------------|----|-----|-----|----|-----------------------------|

| Leakage current    | $I_{ErrL}$   | _  | _   | 10  | μΑ | $V_{Err} = 25 \; V$         |

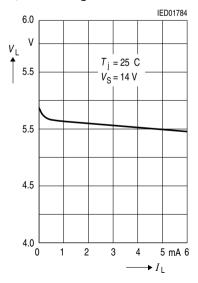

## **Logic Supply Output**

| Output voltage | V  | 4.5 | 5 | 6 | V | <i>T</i> <sub>i</sub> < 150 °C           |

|----------------|----|-----|---|---|---|------------------------------------------|

| Output voltage | VL | 4.5 | 3 |   | V | 1 mA < $I_L$ < 5 mA<br>$V_S$ = 6 to 45 V |

## **Thermal Protection**

| Shutdown | $T_{jsd}$          | 140 | 150 | 160 | °C | $I_{Q1, 2} = 0 \text{ A}$                      |

|----------|--------------------|-----|-----|-----|----|------------------------------------------------|

| Prealarm | $T_{\rm jpa}$      | 120 | 130 | 140 | °C | $V_{Err} = L$                                  |

| Delta    | $\Delta T_{\rm j}$ | 10  | 20  | 30  | K  | $\Delta T_{\rm j} = T_{\rm jsd} - T_{\rm jpa}$ |

### Characteristics (cont'd)

$V_{\rm S} = 6$  to 16 V;  $T_{\rm i} = -40$  to 130 °C

| Parameter | Symbol | Limit Values |      |      | Unit | <b>Test Condition</b> |

|-----------|--------|--------------|------|------|------|-----------------------|

|           |        | min.         | typ. | max. |      |                       |

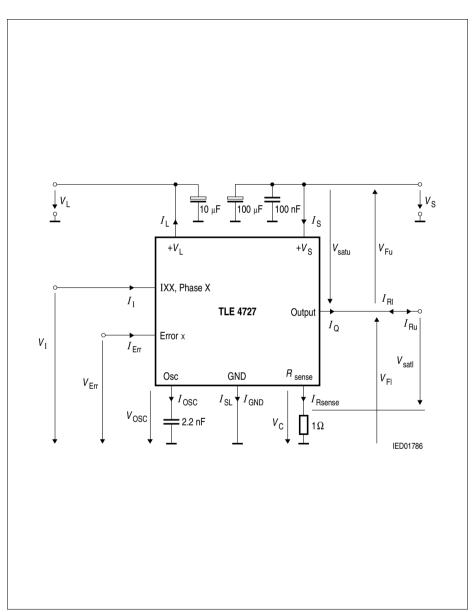

### Power Output Sink Diode Transistor Sink Pair

(D13, T13; D14, T14; D23, T23; D24, T24)

| Saturation voltage | $V_{satl}$ | 0.1 | 0.4  | 0.6  | ٧  | $I_{\rm O} = -0.5  {\rm A}$            |

|--------------------|------------|-----|------|------|----|----------------------------------------|

| Saturation voltage | $V_{satl}$ | 0.2 | 0.5  | 0.8  | ٧  | $I_0 = -0.7 \text{ A}$                 |

| Reverse current    | $I_{RI}$   | 500 | 1000 | 1500 | μΑ | $V_{\rm S} = V_{\rm O} = 40 \text{ V}$ |

| Forward voltage    | $V_{FI}$   | 0.6 | 0.95 | 1.25 | ٧  | $I_{\rm O} = 0.5  {\rm A}$             |

| Forward voltage    | $V_{FI}$   | 0.7 | 1    | 1.3  | V  | $I_{Q} = 0.7 \text{ A}$                |

### Power Output Source Diode Transistor Source Pair

(D11, T11; D12, T12; D21, T21; D22, T22)

| • • • • • • • • • • • • • • • • • • • • |                 | •   |      |      |    |                             |

|-----------------------------------------|-----------------|-----|------|------|----|-----------------------------|

| Saturation voltage; charge              | $V_{satuC}$     | 0.6 | 1.1  | 1.3  | ٧  | $I_{\rm Q} = 0.5  {\rm A}$  |

| Saturation voltage; discharge           | $V_{satuD}$     | 0.1 | 0.4  | 0.7  | V  | $I_{\rm O} = 0.5  {\rm A}$  |

| Saturation voltage; charge              | $V_{\sf satuC}$ | 0.7 | 1.2  | 1.5  | V  | $I_{\rm O} = 0.7  {\rm A}$  |

| Saturation voltage; discharge           | $V_{satuD}$     | 0.2 | 0.5  | 8.0  | V  | $I_{\rm O} = 0.7  {\rm A}$  |

| Reverse current                         | $I_{Ru}$        | 400 | 800  | 1200 | μΑ | $V_{\rm S} = 40 \text{ V},$ |

|                                         |                 |     |      |      |    | $V_{\rm O} = 0 \text{ V}$   |

| Forward voltage                         | $V_{Fu}$        | 0.7 | 1.05 | 1.35 | V  | $I_{\rm O} = -0.5  {\rm A}$ |

| Forward voltage                         | $V_{Fu}$        | 8.0 | 1.1  | 1.4  | V  | $I_{Q} = -0.7 \text{ A}$    |

| Diode leakage current                   | $I_{SL}$        | 0   | 3    | 10   | mΑ | $I_{\rm F} = -0.7  {\rm A}$ |

|                                         |                 |     |      |      |    |                             |

Note: The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25\,^{\circ}\text{C}$  and the given supply voltage.

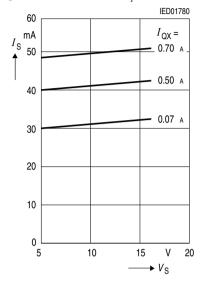

## Quiescent Current $I_{\rm S}$ versus Supply Voltage

$V_{\rm S}$ ; bridges not chopping;  $T_{\rm i}$  = 25 °C

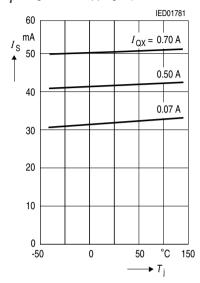

## Quiescent Current $I_{\rm S}$ versus Junction Temp.

$T_i$ ; bridges not chopping;  $V_s = 14 \text{ V}$

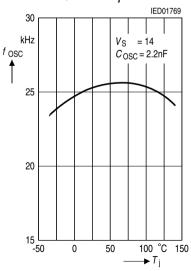

# Oscillator Frequency $f_{\rm OSC}$ versus Junction Temperature $T_{\rm i}$

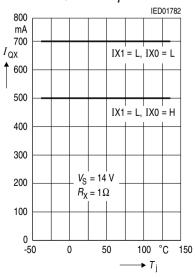

# Output Current $I_{\rm QX}$ versus Junction Temperature $T_{\rm i}$

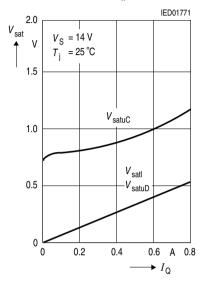

# Output Saturation Voltages $V_{\rm sat}$ versus Output Current $I_{\rm Q}$

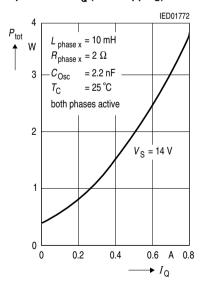

# Typical Power Dissipation $P_{\rm tot}$ versus Output Current $I_{\rm Q}$ (non stepping)

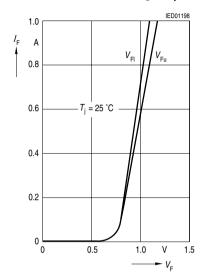

# Forward Current $I_{\rm F}$ of Free-Wheeling Diodes versus Forward Voltages $V_{\rm F}$

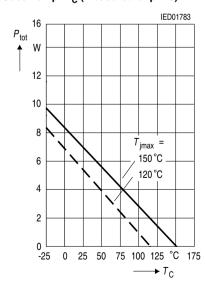

# Permissible Power Dissipation $P_{\rm tot}$ versus Case Temp. $T_{\rm C}$ (measured at pin 5)

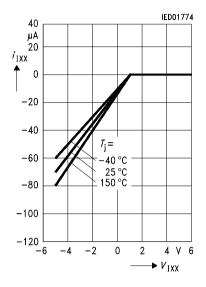

## Input Characteristics of IXX , Phase X

# Logic Supply Output Voltage versus Output Current $I_{\rm L}$

### **Output Leakage Current**

## Logic Supply Output Voltage versus Junction Temperature $T_{\rm i}$

Figure 3 Application Circuit

Figure 4 Test Circuit

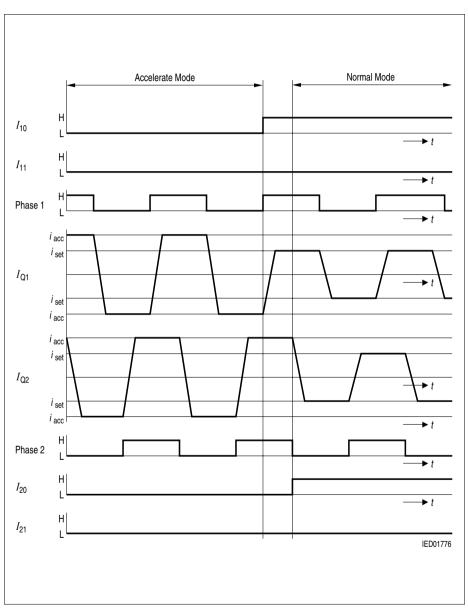

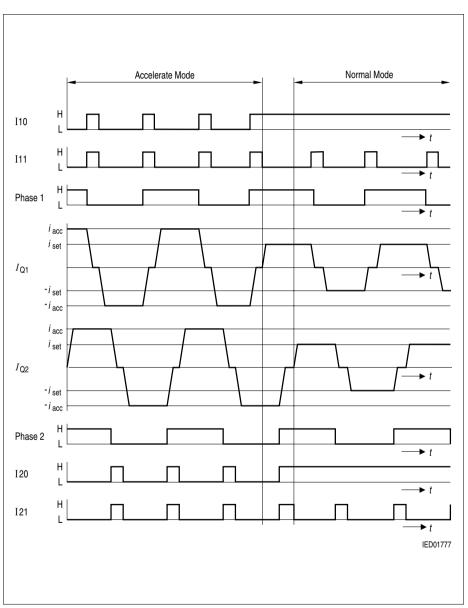

Figure 5 Full-Step Operation

Figure 6 Half-Step Operation

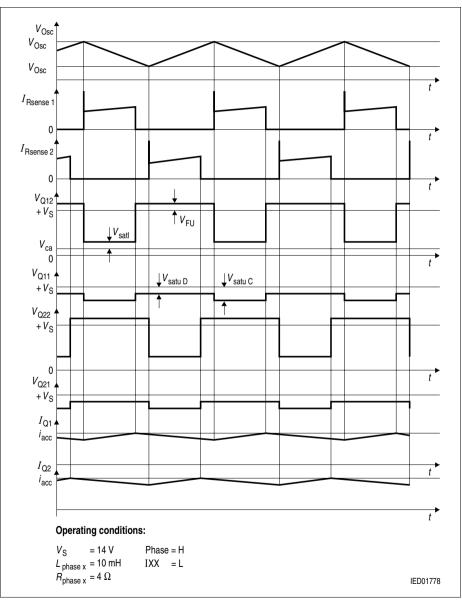

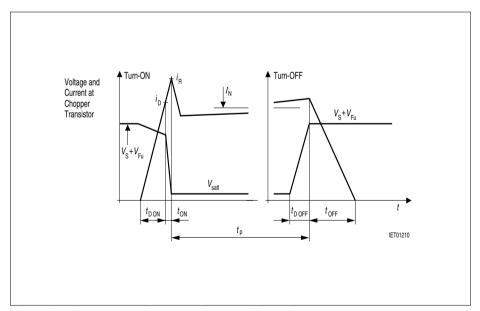

Figure 7 Current Control in Chop-Mode

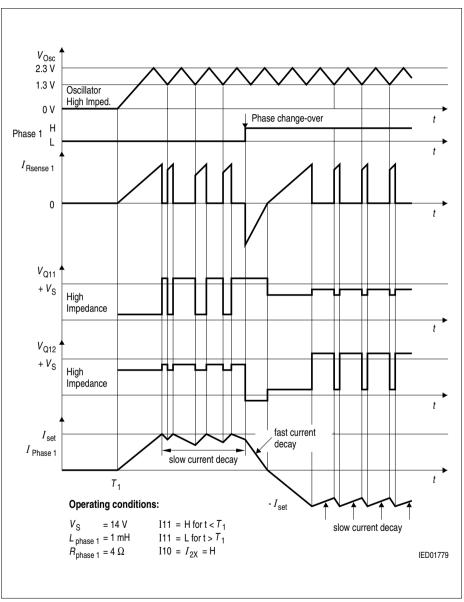

Figure 8 Phase Reversal and Inhibit

#### **Calculation of Power Dissipation**

The total power dissipation  $P_{tot}$  is made up of

$\begin{array}{ll} \textbf{saturation losses } P_{\text{sat}} & \text{(transistor saturation voltage and diode forward voltages),} \\ \textbf{quiescent losses } P_{\text{q}} & \text{(quiescent current times supply voltage) and} \\ \textbf{switching losses } P_{\text{s}} & \text{(turn-ON / turn-OFF operations).} \\ \end{array}$

The following equations give the power dissipation for chopper operation without phase reversal. This is the worst case, because full current flows for the entire time and switching losses occur in addition.

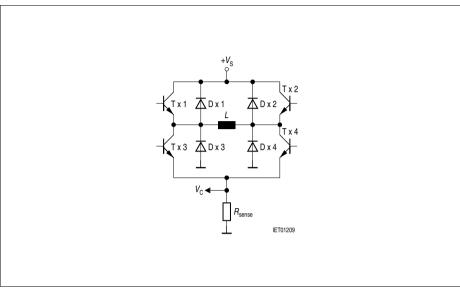

$$\begin{split} P_{\text{tot}} &= 2 \times P_{\text{sat}} + P_{\text{q}} + 2 \times P_{\text{S}} \\ \text{where} \qquad \qquad P_{\text{sat}} &\cong I_{\text{N}} \left\{ V_{\text{satI}} \times d + V_{\text{Fu}} \left( 1 - d \right) + V_{\text{satuC}} \times d + V_{\text{satuD}} \left( 1 - d \right) \right\} \\ P_{\text{q}} &= I_{\text{q}} \times V_{\text{S}} \\ P_{\text{S}} &\cong \frac{V_{\text{S}}}{T} \left\{ \frac{i_{\text{D}} \times t_{\text{DON}}}{2} + \frac{(i_{\text{D}} + i_{\text{R}}) \times t_{\text{ON}}}{4} + \frac{I_{\text{N}}}{2} (t_{\text{DOFF}} + t_{\text{OFF}}) \right\} \end{split}$$

$I_N$  = nominal current (mean value)

$I_{q}$  = quiescent current

*i*<sub>D</sub> = reverse current during turn-ON delay

$i_{\rm R}$  = peak reverse current

$t_{\rm p}$  = conducting time of chopper transistor

$t_{

m ON}$  = turn-ON time  $t_{

m OFF}$  = turn-OFF time  $t_{

m DON}$  = turn-ON delay  $t_{

m DOFF}$  = turn-OFF delay T = cycle duration d = duty cycle  $t_{

m D}$  / T

$V_{\text{satl}}$  = saturation voltage of sink transistor ( $T_{X3}$ ,  $T_{X4}$ )

$V_{\rm satuC}$  = saturation voltage of source transistor (T<sub>X1</sub>, T<sub>X2</sub>) during charge cycle  $V_{\rm satuD}$  = saturation voltage of source transistor (T<sub>X1</sub>, T<sub>X2</sub>) during discharge cycle

$V_{Fu}$  = forward voltage of free-wheeling diode (D<sub>X1</sub>, D<sub>X2</sub>)

$V_{\rm S}$  = supply voltage

Figure 9

Figure 10 Voltage and Current at Chopper Transistor

### **Application Hints**

The TLE 4727 is intended to drive both phases of a stepper motor. Special care has been taken to provide high efficiency, robustness and to minimize external components.

#### **Power Supply**

The TLE 4727 will work with supply voltages ranging from 5 V to 16 V at pin  $V_{\rm S}$ . Surges exceeding 16 V at  $V_{\rm S}$  won't harm the circuit up to 45 V, but whole function is not guaranteed. As soon as the voltage drops below approximately 16 V the TLE 4727 works promptly again.

As the circuit operates with chopper regulation of the current, interference generation problems can arise in some applications. Therefore the power supply should be decoupled by a 0.1  $\mu F$  ceramic capacitor located near the package. Unstabilized supplies may even afford higher capacities.

### **Current Sensing**

The current in the windings of the stepper motor is sensed by the voltage drop across  $R_{\rm sense}$ . Depending on the selected current internal comparators will turn off the sink transistor as soon as the voltage drop reaches certain thresholds (typical 0 V, 0.07 V, 0.50 V and 0.70 V). These thresholds are not affected by variations of  $V_{\rm S}$ . Consequently unstabilized supplies will not affect the performance of the regulation. For precise current level it must be considered, that internal bonding wire (typ. 60 m $\Omega$ ) is a part of  $R_{\rm sense}$ .

Due to chopper control fast current rises (up to  $10A/\mu s$ ) will occur at the sensing resistors. To prevent malfunction of the current sensing mechanism  $R_{\rm sense}$  should be pure ohmic. The resistors should be wired to GND as directly as possible. Capacitive loads such as long cables (with high wire to wire capacity) to the motor should be avoided for the same reason.

## Synchronizing Several Choppers

In some applications synchronous chopping of several stepper motor drivers may be desirable to reduce acoustic interference. This can be done by forcing the oscillator of the TLE 4727 by a pulse generator overdriving the oscillator loading currents (approximately  $\pm$  120  $\mu\text{A}$ ). In these applications low level should be between 0 V and 0.8 V while high level should be between 3 V and 5 V.

### **Optimizing Noise Immunity**

Unused inputs should always be wired to proper voltage levels in order to obtain highest possible noise immunity.

To prevent crossconduction of the output stages the TLE 4727 uses a special break before make timing of the power transistors. This timing circuit can be triggered by short glitches (some hundred nanoseconds) at the Phase inputs causing the output stage to become high resistive during some microseconds. This will lead to a fast current decay during that time. To achieve maximum current accuracy such glitches at the Phase inputs should be avoided by proper control signals.

To lower EMI a ceramic capacitor of max. 3 nF is advisable from each output to GND.

#### Thermal Shut Down

To protect the circuit against thermal destruction, thermal shut down has been implemented.

### **Error Monitoring**

The error output signals with low-potential one of the following errors:

| overtem | perature | implemented as | pre-alarm; appears | approximately | 20 K before |

|---------|----------|----------------|--------------------|---------------|-------------|

|---------|----------|----------------|--------------------|---------------|-------------|

thermal shut down.

short circuit a connection of one output to GND for longer than 30 μs sets an

internal error flipflop. A phase change-over of the affected bridge resets the flipflop. Being a separate flipflop for each bridge, the

error can be located in such way.

**underload** the recirculation of the inductive load is watched. If there is no

recirculation after a phase change-over, the internal error flipflop is set. Additionally an error is signaled after a phase change-over

during hold-mode.

## **Package Outlines**

#### Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

Dimensions in mm