## **Integrated Switch**

(MOSFET Driver and MOSFETs)

#### **Features**

- Replaces with one part only the semiconductors of a DC/DC power stage for a 12 V → 1 ... 3.3 V conversion:

FET driver + High side FET + Low side FET

- Raises the efficiency by reducing static and dynamic losses beyond 85 % due to optimized MOSFETs and Driver

- Reduces overall part count and board space consumption

- Simplifies and shortens the circuit design and the layout

- Eliminates the need for external bootstrap components

- Provides simplest overall output current scalability

- Protects the Driver <u>and</u> the MOSFETs against overtemperature and shoot-through problems Vcc → Gnd

- Achieves the lowest thermal resistance Rthjc and Rthja

- Uses the well-known, easy-to-assemble and robust standard TO-220 and TO-263 (D<sup>2</sup>Pak) package

- Requires no separate supply voltage to operate except 12 V

- Three state input to enable a shut down mode to turn off both MOSFETs

- Compatible with standard 2-, 3-, 4-, 6-phase PWM controller ICs

- Ideal for compact, highly-efficient, multi-phase voltage regulators on motherboards and VRMs

| Туре        | Package      | Marking | Ordering Code |

|-------------|--------------|---------|---------------|

| TDA21201-P7 | TO-220-7-3   | 21201P7 | Q67042-S4100  |

| TDA21201-S7 | TO-220-7-230 | 21201S7 | Q67042-S4101  |

| TDA21201-B7 | TO-263-7-2   | 21201B7 | Q67042-S4099  |

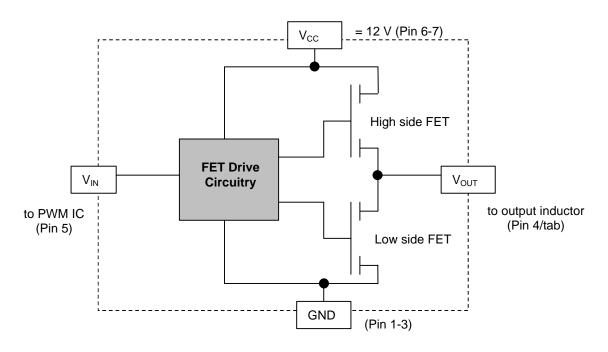

## Pin Configuration and Function

| Pin number | Pin name         | Pin description                                |

|------------|------------------|------------------------------------------------|

| 1,2,3      | GND              | Ground                                         |

| 4/tab      | V <sub>OUT</sub> | Output voltage from common node of the MOSFETs |

| 5          | IN               | Input signal from PWM controller               |

| 6,7        | $V_{CC}$         | Supply voltage to MOSFETs and Driver IC        |

### **General Description**

The Integrated Switch TDA21201 incorporates an intelligent MOSFET driver and two Power MOSFETs in a single package to form a fully integrated and optimized power stage of a DC/DC synchronous buck converter including the bootstrap components for the high-side MOSFET.

The Power MOSFETs are optimized for lowest static and dynamic losses for a 12 V to sub-3.5 V conversion and can handle up to 30 A output current. The TDA21201 is manufactured in Infineon's state-of-the-art multi-chip assembly using a low-Rth 7-Pin

TO-220 package or its associated SMD counterpart TO-263 and Infineon's latest chip technologies.

## **Block Diagram**

### **Absolute Maximum Ratings**

At Tj = 25 °C, unless otherwise specified

| Parameter                                                                   | Symbol Value         |      |       | Unit     |

|-----------------------------------------------------------------------------|----------------------|------|-------|----------|

|                                                                             | _                    | Min. | Max.  |          |

| Peak voltage supplied to 'VCC' pins                                         | V <sub>CC_PEAK</sub> |      | 20*   |          |

| Peak voltage supplied to 'IN' pin, D <sub>IN_Peak</sub> < 10 %              | V <sub>IN</sub>      | -5   | 10    | V        |

| Peak voltage at 'Vout' pin to GND                                           | $V_{OUT\_PK}$        | -5   | 20*   |          |

| Maximum DC output current, V <sub>CC</sub> = 12 V, V <sub>OUT</sub> ≤ 3.3 V | I <sub>OUT_MAX</sub> | -10  | 30    | Α        |

| Junction temperature                                                        | $T_J$                |      | 150   |          |

| Storage temperature                                                         | Ts                   | -55  | 150   |          |

| Lead temperature TO-263;                                                    | $T_L$                |      | 225   | °C       |

| MSL1, IPC/JEDEC J-STD-020A                                                  |                      |      |       |          |

| Lead temperature TO-220 (soldering, 10 seconds)                             | $T_L$                |      | 260   |          |

| ESD rating (Human body model)                                               | ESD                  | 2 k  |       | <b>V</b> |

| IEC climatic category; DIN EN 60068-1                                       |                      | 55/1 | 50/56 | -        |

<sup>\*</sup> The positive peak voltage (= the voltage overshoot during switching transients) at the VCC pins and the OUT pin/tab is limited by the Integrated Switch itself (pls., see the "Over-voltage protection of VCC" paragraph

### **Thermal Characteristic**

| Parameter                                     | Symbol | Values |      | Unit |     |

|-----------------------------------------------|--------|--------|------|------|-----|

|                                               |        | Min.   | Тур. | Max. |     |

| Thermal resistance, junctions-case            |        |        |      | 1.9  | K/W |

| Thermal resistance, junctions-ambient, leaded |        |        |      | 62.5 |     |

| SMD version, device on PCB:      |  |    |  |

|----------------------------------|--|----|--|

| @ min. footprint                 |  | 62 |  |

| @ 6 cm <sup>2</sup> cooling area |  | 40 |  |

## **Electrical Characteristics**

At Tj = 25 °C, unless otherwise specified

| Parameter                               | Symbol               | Conditions                                   | Values |      |      | Unit     |

|-----------------------------------------|----------------------|----------------------------------------------|--------|------|------|----------|

|                                         |                      |                                              | Min.   | Тур. | Max. |          |

| Input Characteristic (                  | = MOSFET             | Driver)                                      |        |      |      |          |

| Shut down window                        | V <sub>IN_SHUT</sub> | t_ <sub>SHUT</sub> > 1.5 μs                  | 1.2    |      | 1.6  | <b>V</b> |

| Shut down hold-off                      | t_shut               | $1.2~V \leq V_{IN} \leq 1.6~V$               | 0.8    | 1.5  | 2.5  | μs       |

| time                                    |                      |                                              |        |      |      |          |

| Supply current during                   | I <sub>CC_SHUT</sub> | $1.2 \text{ V} \le V_{IN} \le 1.6 \text{ V}$ | 10     | 16   | 22   | mA       |

| shut down                               |                      | $V_{CC} = 12 V$                              |        |      |      |          |

| Current into 'IN' pin, during shut down | I <sub>IN_SHUT</sub> | $V_{IN} = 1.4 V$                             | -10    |      | 10   |          |

| Current into 'IN' pin,                  | I <sub>IN_LOW</sub>  | V <sub>IN</sub> = 0.4 V                      | -2     | -10  | -50  | μΑ       |

| Low                                     |                      |                                              |        |      |      |          |

| Current into 'IN' pin,<br>High          | I <sub>IN_HIGH</sub> | V <sub>IN</sub> = 4.5 V                      | 20     | 35   | 80   |          |

| Static Characteristic (= High Side and Low Side MOSFET) |                     |                                              |  |      |    |    |  |

|---------------------------------------------------------|---------------------|----------------------------------------------|--|------|----|----|--|

| D-S Breakdown                                           | $V_{DS\_HS}$        |                                              |  |      |    |    |  |

| Voltage High Side                                       |                     | $1.2 \text{ V} \le V_{IN} \le 1.6 \text{ V}$ |  |      | 30 | V  |  |

| D-S Breakdown                                           | $V_{DS\_LS}$        | $I_D = 0.25 A$                               |  |      |    |    |  |

| Voltage Low Side                                        |                     |                                              |  |      |    |    |  |

| D-S Leakage Current                                     | I <sub>DSS_HS</sub> |                                              |  |      |    |    |  |

| High Side                                               |                     | $1.2 \text{ V} \le V_{IN} \le 1.6 \text{ V}$ |  | 0.1  | 1  | μΑ |  |

| D-S Leakage Current                                     | $I_{DSS\_LS}$       | $V_{CC} = 12 \text{ V}$                      |  |      |    |    |  |

| High Side                                               |                     |                                              |  |      |    |    |  |

| Drain-Source on                                         | $R_{DSon\_HS}$      |                                              |  | 13.3 |    |    |  |

| Resistance High Side                                    |                     | $I_{OUT} = 15 A$                             |  |      |    |    |  |

| Drain-Source on                                         | $R_{DSon\_LS}$      | Tj = 25 °C                                   |  | 4.8  |    |    |  |

| Resistance Low Side                                     |                     |                                              |  |      |    | mΩ |  |

| Drain-Source on                                         | $R_{DSon\_HS}$      |                                              |  | 17.7 |    |    |  |

| Resistance High Side                                    |                     | $I_{OUT} = 15 A$                             |  |      |    |    |  |

| Drain-Source on                                         | $R_{DSon\_LS}$      | Tj = 125 °C                                  |  | 6.4  |    |    |  |

| Resistance Low Side                                     |                     |                                              |  |      |    |    |  |

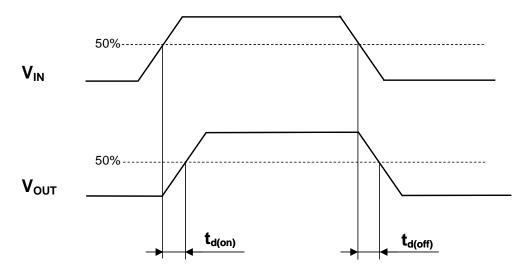

| <b>Dynamic Characteris</b>       | tic (= Integ        | grated Switch)          |     |     |    |

|----------------------------------|---------------------|-------------------------|-----|-----|----|

| IN to OUT delay time             | t <sub>d(ON)</sub>  |                         | 110 | 150 |    |

| $L \rightarrow H$ ; 50 % to 50 % | , ,                 |                         |     |     |    |

| IN to OUT delay time             | t <sub>d(OFF)</sub> | I <sub>OUT</sub> = 15 A | 70  | 100 |    |

| $H \rightarrow L$ ; 50 % to 50 % | , ,                 |                         |     |     | ns |

| OUT rise time; 20 %              | t <sub>r</sub>      | (s. Timing Diagram)     | 10  | 25  |    |

| to 80 %                          |                     |                         |     |     |    |

| OUT fall time; 80 to             | t <sub>f</sub>      |                         | 10  | 30  |    |

| 20 %                             |                     |                         |     |     |    |

### **Operating Conditions**

At Tj = 25 °C, unless otherwise specified

| Parameter               | Symbol            | Conditions | Values |      |      | Unit |

|-------------------------|-------------------|------------|--------|------|------|------|

|                         | -                 |            | Min.   | Тур. | Max. |      |

| Voltage supplied to     | $V_{CC}$          |            | 9      |      | 15   |      |

| 'VCC' pins              |                   |            |        |      |      | V    |

| Voltage 'IN' Low        | $V_{IN_{L}}$      |            | -0.5   |      | 8.0  |      |

| Voltage 'IN' High       | V <sub>IN_H</sub> |            | 2.1    |      | 5.5  |      |

| Input signal transition | f                 |            | 100    |      | 500  | KHz  |

| frequency               |                   |            |        |      |      |      |

| Pulse width Input       | $t_{P\_IN}$       |            | 90     |      |      | ns   |

| Power dissipation       | P <sub>TOT</sub>  |            |        |      | 10   | W    |

| Junction temperature    | $T_J$             |            | -25    |      | 125  | å    |

## **Timing Diagram**

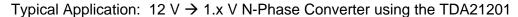

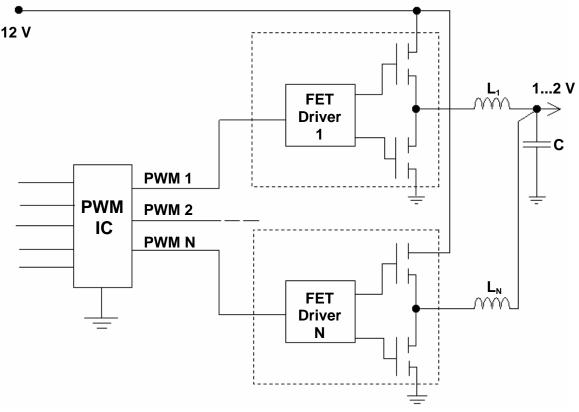

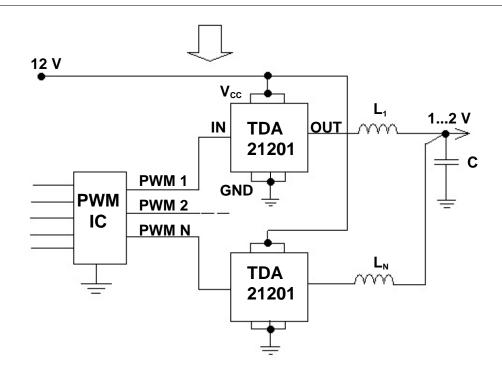

### **Typical application**

A circuit designer will value the Integrated Switch TDA21201 as cost-optimized power stage solution in high-density DC/DC conversion applications using a Vcc = 12 V input where efficiency and board space is an issue, e.g. in multi-phase microprocessor supplies on motherboards, in VRMs and servers. The TDA21201 can also be used to power Logic circuits, Memory banks etc. that require higher voltages, e.g. 2.5 or 3.3 V. The efficiency of the Integrated Switch and the overall efficiency of the converter will even go up at these elevated output

voltages compared to the 1.6 V efficiency given later on in this data sheet.

## Designing a 12 V to sub-3.3 V converter using the TDA21201

#### General info

To design a multi-phase converter with a 12 V input simply use in each phase just one TDA21201 instead of using a MOSFET driver, a high side MOSFET, bootstrap components, and one or more low side MOSFETs. The entire converter is completed by the input filter, the output filter and a multi-phase PWM IC.

Input compatibility to standard PWM controllers / shut-down mode

The Integrated Switch TDA21201 has a high impedance input pin 'IN' to be connected to PWM controller outputs 'PWM1', 'PWM2' etc. It sinks or sources only a fraction of a mA from the controller's output. The TDA21201 is compatible to standard controller and driver signals in terms of the signal level (5 V TTL) and in terms of the 'Low'/'High' relationship ('Low' turns the low side MOSFET on, 'High' turns the High side MOSFET on).

The TDA21201 can be shut down (the high side MOSFET and the low side MOSFET is turned off) by applying an input signal  $V_{\text{IN}} = 1.2 \dots 1.6 \text{ V}$  for more than 1.5 µs typical. This way the TDA21201 reduces the power dissipation by saving the gate charges of both the high side and the low side MOSFET during no load conditions. The shutdown state is terminated when  $V_{\text{IN}}$  moves into the 'Low' or 'High' threshold.

Page 5 Apr-29, 2002

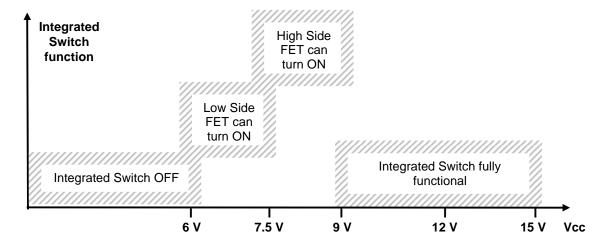

Integrated Switch functionality vs. supply voltage Vcc

The Integrated Switch reaches gradually its full functionality while the supply voltage Vcc increases from 0 to its nominal value +12 V, e.g. during turn-on. The same happens vice versa when the supply voltage decreases from its nominal value +12 V to 0, e.g. during turn-off. The TDA21201 is very insensitive to Vcc tolerances. It behaves properly in a wide Vcc range from 9 to 15 V. There is no distinct  $V_{CC}$  threshold at which the Integrated Switch's functionality or state changes abrupt while  $V_{CC}$  increases or decreases. E.g., there is no tight specified Under Voltage Lockout level. The TDA21201 changes smoothly its state, e.g., as the High Side and Low Side MOSFETs' gate drive voltage increases while  $V_{CC}$  increases from 7.5 V to 9 V the Rds[on] of both the High Side MOSFET and the Low Side MOSFET decreases gradually, rather than being fully Off at VCC slightly below a threshold level or

being fully On at a VCC level slightly greater than the threshold.

## Bootstrapping

Turning on and off the High side MOSFET is done internally by the Driver. The TDA21201 does not require any external bootstrap components such as a capacitor or diode. Just apply GND, Vcc = 12 V, and the PWM signal of the Controller to it and the Integrated Switch will operate.

## Input filter / Output filter / Converter Stability

The Integrated Switch TDA21201 is a new solution to implement the power semiconductor components in a DC/DC converter. It offers many advantages to the user. However, the basic behavior with respect to the voltages, the currents and the timing remains unchanged. Therefore, any of the rules and procedures applied to design DC/DC converters using discrete MOSFETs and Drivers apply in the same way to converters using the Integrated Switch – except the worries regarding dead time control, lowest impedance in the AC loop, elevated driver temperatures etc.

#### Current sense

Any of the commonly used current sense techniques are supported by the Integrated Switch. For Low side sensing measure the voltage drop across the GND pins and the OUT pin (or the tab when using the SMD version) during the Low side switch's On-time (Vin = Low). The High side MOSFET is sensed across the Vcc and the OUT pin (or the tab when using the SMD version) of the Integrated Switch during its On-time (Vin = High). Inductor sensing is implemented outside of the integrated switch the usual way. Resistor sensing using a separate resistor in the Input capacitor  $\rightarrow$  High side MOSFET (Vcc pin) path is possible but not recommended. This current sense approach introduces ample stray inductance in the AC current loop (+terminal of the input capacitor  $\rightarrow$  High side MOSFET  $\rightarrow$  Low side MOSFET  $\rightarrow$  GND  $\rightarrow$  -terminal of the input capacitor). This results in a very noisy Vcc line especially during the switching period and a non-optimized switching behavior of the Integrated Switch. This in turn, increases the switching losses and the device temperature and lowers the efficiency.

#### Output current scalability

The converter output current can be chosen in a wide range by selecting the appropriate number of phases. At a given number of phases the current per phase (= current per TDA21201) and in turn the overall converter output current is set by application requirements, e.g. the switching frequency, and by environmental conditions, e.g. ambient temperature and the thermal resistance of the TDA21201 to ambient. As a reference, one TDA21201 generates roughly 3.2 W @ 15 A RMS and 250 kHz ( $V_{CC}$  = 12 V,  $V_{O}$  = 1.6 V). This amount of loss can be dissipated by the SMD version of the Integrated Switch on a regular motherboard using proper thermal design techniques. Greater phase currents result in higher losses; and higher switching

frequencies will also result in more losses. So, in modifying the thermal environment and a switching frequency the phase current can be matched your requirements; please, consult the efficiency curves in this Data Sheet to choose the most suitable phase current and switching frequency per phase for a particular design. To give a circuit designer more freedom in scaling the phase current, the Integrated Switch is offered in a heat sink capable TO-220 version that allows better thermal coupling to ambient and a higher junction temperature in the Integrated Switch as well - without violating the applicable regulations.

### Over temperature shut-down

The over temperature shut-down function of the Integrated Switch takes effect @ 150 °C junction temperature typically and turns off the High side MOSFET and the Low side MOSFET. Unlike as in discrete converter solutions the MOSFETs and the Driver are thermally very well coupled. Therefore, this function protects the Driver and the MOSFETs. Once the Integrated Switch is cooled down and the temperature shut-down is released the Integrated Switch continues to operate by turning on one of the MOSFETs according to its PWM signal present on the input.

### Under Voltage Lockout / $\Delta$ Vcc detection

The TDA21201 is fully functional at  $Vcc \ge 9$  V. However, the Low side MOSFET can already be turned on at  $Vcc \approx 6$  V or greater when the input is Low. The Integrated Switch is disabled and both MOSFETs are turned off at lower Vcc, e.g. during power-up of the ATX supply.

The TDA21201 has two paralleled Vcc pins. The voltage applied to these pins will be converted to a lower output voltage but it also serves as supply voltage of the integrated gate drive circuit. Therefore, the voltage difference  $\Delta$  Vcc is monitored for safety reasons. When  $\Delta$  Vcc  $\geq$  0.45 V for more than 2  $\mu s$  typically the Integrated Switch is disabled. This way it prevents the part itself but it also protects the load from inadequate behavior, e.g. due to a bad soldering connection of the Vcc pins.

## Layout guidelines

In general, the layout is simplified when using the Integrated Switch. However, it should be kept in mind that the power density in the Integrated Switch is higher than in a discrete solution. Therefore, proper thermal layout is very critical in designs that employ the SMD version.

Another important aspect is a very low impedance path in the Vcc =  $12 \text{ V} \rightarrow \text{TDA21201} \rightarrow \text{GND}$  loop. It is recommended to place the capacitors of the input filter as close to the GND and Vcc pins of the TDA21201 as possible. Additional ceramic capacitors in parallel to the input capacitors help to reduce the effect of stray inductance of the input capacitors and the PCB traces. Reducing parasitic inductance will result in an optimized switching behavior and lower switching losses. The arrangement of the output filter is of second order importance.

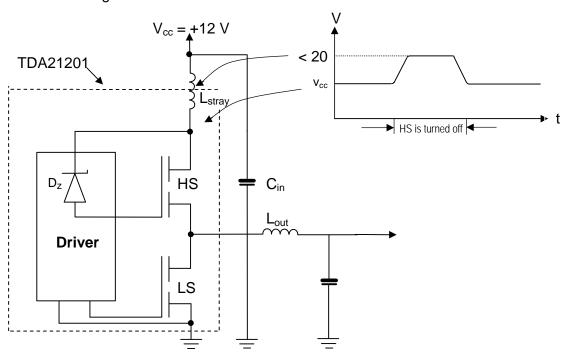

Over voltage protection of Vcc / Avalanche avoidance

The voltage at the Vcc pins of the TDA21201 rises above the nominal DC value of the Vcc supply (= + 12 V) during the turn-off of the High Side MOSFET. The voltage overshoots at the Vcc pins according to:

vcc (t) = instantaneous value of vcc; Vcc = +12 V DC; Lstray = stray inductance of the PCB traces + the input capacitor's ESL + the parasitic inductance of the TDA21201 package itself; di/dt = slew rate of the High Side current during its turn-off.

This equation reveals that Lstray should be made as small as possible (as vcc(t) is limited by the breakdown voltage of the device, Vcc is given by the application, di/dt should be as large as possible to reduce switching losses) using proper layout techniques and low ESL capacitors, e.g. ceramics, between the Vcc and GND pins of the Integrated Switch.

To protect the Integrated Switch from unallowable voltage spikes, the slew rate of the High Side current di/dt is controlled in a way so that the overall voltage (between Vcc pins to GND pins) does not exceed 20 V (measured between the Vcc and GND pins at the PCB, this voltage will slightly exceed the 20 V limit within the package/at the chips). As the MOSFETs have a Breakdown voltage rating Vds = 30 V, it is made sure that they are never driven into avalanche.

The slew rate control is implemented using the principal of the active zener clamp technique: When vcc(t) rises during turn-off then the effective gate-drain voltage of the High Side MOSFET rises, too. If, for what reason ever, the vcc(t) overshoot approaches a value that possibly could damage the integrated

driver or the MOSFETs, the zener diode becomes conducting and reduces the discharge speed of the High Side MOSFET's gate within nanoseconds. This will reduce slightly the turn-off slew rate of the High Side MOSFET's current (= di/dt). As a result the over voltage will be limited.

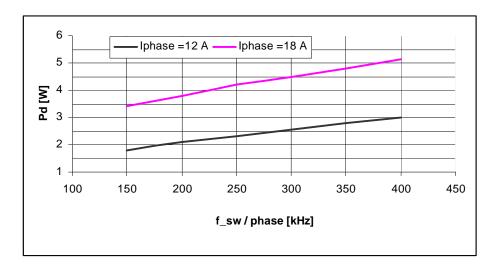

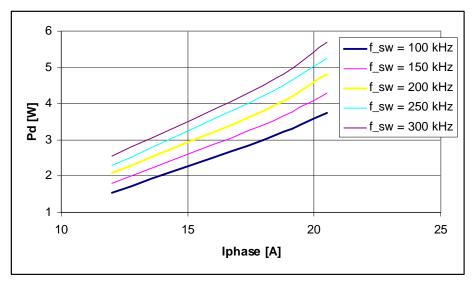

Power loss in the Integrated Switch TDA21201 / Heat sink estimation

The power loss in the Integrated Switch depends mainly on the current and the switching frequency. Other conditions that impact the power loss are increased junction temperature and the layout (e.g. very tight coupling of the input capacitor to the  $V_{CC}$  and GND pins to reduce the PCB trace inductance).

Using the above two diagrams the power loss (= the required power dissipation Pd for thermally stable operation) can be estimated based on a required phase current Iphase (= current in the Integrated Switch) an based on the switching frequency per phase f\_sw (= frequency of the Integrated Switch in each phase).

Having the power dissipation Pd of the Integrated Switch, the required thermal resistance RthCA can be calculated. RthCA is the value of the heat sink attached to the TO-220 version of the Integrated Switch. RthCA is the "effective" thermal resistance (takes airflow etc. into account):

$$RthCA \le \frac{Tj - \max - TA}{Pd} - Rthjc$$

Wherein:

R<sub>th</sub>CA = Thermal resistance from the package's metal backside (= lead frame) to ambient air that is required to operate the Integrated Switch under given load and environmental conditions without exceeding the maximum allowed junction temperature; in [°C/W]

T<sub>j\_max</sub> = Maximum allowed junction temperature of the Integrated Switch; in [°C], use 110 °C for the SMD version of the Integrated Switch, use 125 °C for the TO-220 version of the Integrated Switch

TA = The ambient temperature; in [°C], usually this is the maximum temperature of the surrounding air @ worst case, e.g. 55 °C

Pd = The power loss generated in the Integrated Switch that needs to be dissipated through the heat sink → air (TO-220) or the PCB → air for thermal balance; in [W], use one of the two diagrams Pd vs. Iphase or Pd vs. f\_sw to find the this value for your particular application

$R_{th}jc \hspace{2mm} = \hspace{2mm} Thermal \hspace{2mm} resistance \hspace{2mm} junction \hspace{2mm} to \hspace{2mm} case \hspace{2mm} of \hspace{2mm} the \hspace{2mm} Integrated \hspace{2mm} Switch; \\ \hspace{2mm} in \hspace{2mm} [K/W], \hspace{2mm} use \hspace{2mm} \leq 2 \hspace{2mm} K/W \hspace{2mm} (s. \hspace{2mm} also \hspace{2mm} pg. \hspace{2mm} 3 \hspace{2mm} and \hspace{2mm} 4 \hspace{2mm} "Thermal \\ \hspace{2mm} characteristic \hspace{2mm} of \hspace{2mm} the \hspace{2mm} High \hspace{2mm} side/Low \hspace{2mm} side \hspace{2mm} \hspace{2mm} MOSFET" \hspace{2mm} in \hspace{2mm} this \\ \hspace{2mm} data \hspace{2mm} sheet; \hspace{2mm} the \hspace{2mm} majority \hspace{2mm} of \hspace{2mm} the \hspace{2mm} losses \hspace{2mm} are \hspace{2mm} generated \hspace{2mm} within \\ \hspace{2mm} the \hspace{2mm} MOSFETs, \hspace{2mm} not \hspace{2mm} in \hspace{2mm} the \hspace{2mm} driver)$

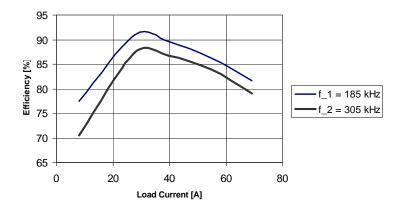

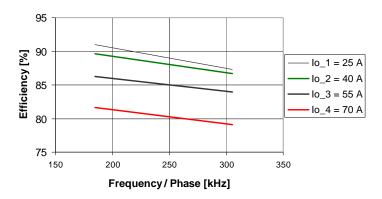

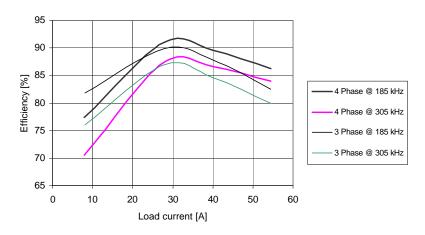

## Efficiency of a DC/DC converter using the Integrated Switch TDA21201

The following measurements were performed on a 4-phase Evaluation Board.

Phase 4 can be disabled so that the converter operates in a 3-phase mode. Boundary Conditions: Vcc = 12 V, Vo = 1.6 V, TDA21201 as SMD

I 4-Phase Converter: Efficiency vs. Load current

## II 4-Phase Converter: Efficiency vs. Switching frequency

III 3- and 4-Phase Converter: Efficiency vs. Load current

It should be noted that the overall converter efficiency and the maximum converter output power will increase as the output voltage increases, e.g.  $V_0 = 2.5$  or 3.3 V.

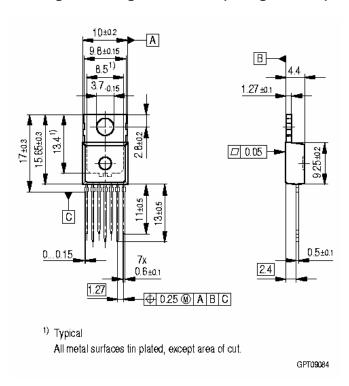

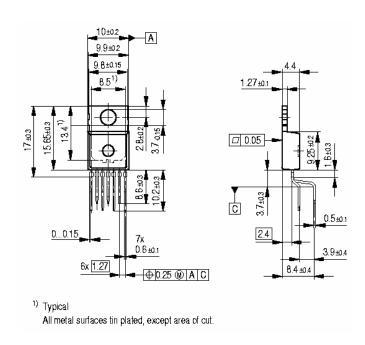

## Package Drawing TO-220-7-3 (straight leads)

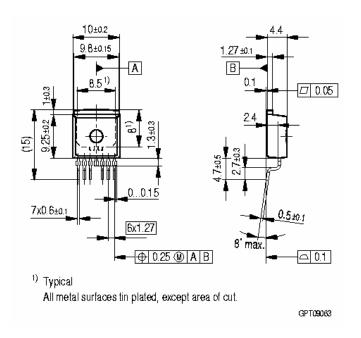

## Package Drawing TO-220-7-230 (staggered leads)

# Package Drawing TO-263-7-2 (SMD)

Published by

Infineon Technologies AG,

Bereichs Kommunikation

St.-Martin-Strasse 53,

D-81541 München

Ó Infineon Technologies AG 1999

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted Characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address lists).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.