Data Sheet, DS 1, Mar. 2003

# INCA-D

Infineon Codec with DASL Transceiver and embedded Microcontroller Featuring Acoustic Echo Cancellation PSB 21473 Version 1.3

Wired Communications

Never stop thinking.

### Data Sheet

| Revision H     | listory: 2003-03-31                                                      | DS 1       |

|----------------|--------------------------------------------------------------------------|------------|

| Previous V     | ersion: 02.01 / Data Sheet DS3                                           |            |

| Page           | Subjects (major changes since last revision)                             |            |

| <b>52/ 173</b> | Reset value of SYSCON modified                                           |            |

| 74             | Table entries deleted                                                    |            |

| 103            | HDLEN bit of register PSW removed                                        |            |

| 174            | Reset value of BUSCON0 corrected                                         |            |

| 181            | Reset value of WDTCON corrected                                          |            |

| 232            | S0CON.RXDI bit moved to position 5                                       |            |

| 407            | Peak Detector has no output                                              |            |

| 420            | Note for PIDDHWCFG added                                                 |            |

| <b>421</b> ff  | Modified formulas marked by vertical change bars                         |            |

| 507            | DSP register descriptions moved                                          |            |

| <b>508</b>     | Description of keyscanner interrupt generation modified                  |            |

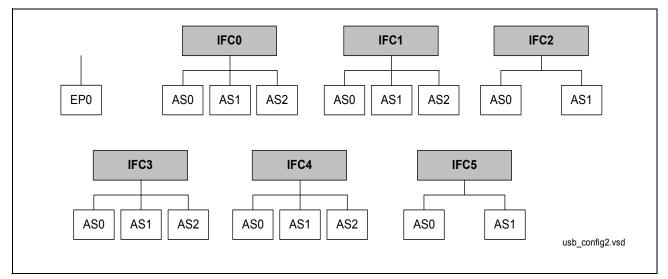

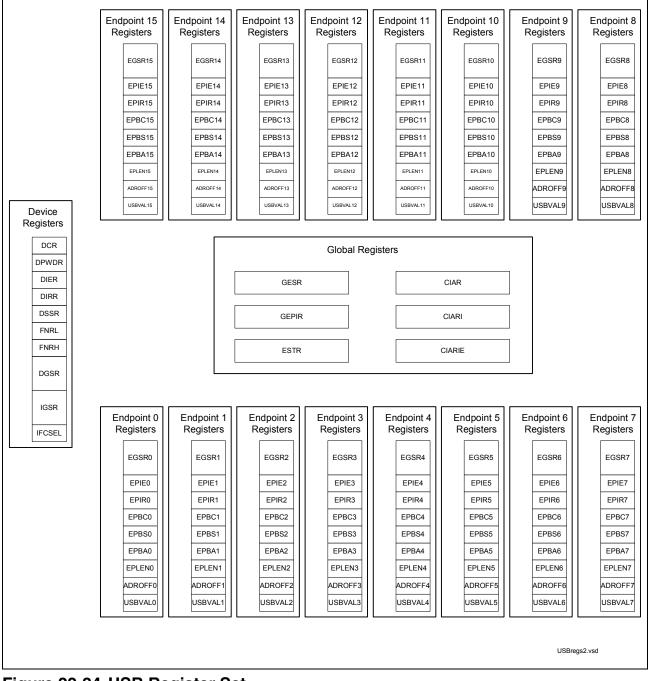

| 515            | 14 interfaces and 6 Alternate settings supported (see vertical cha       | ange bars) |

| 516            | Description regarding physical vs. logical endpoints modified            |            |

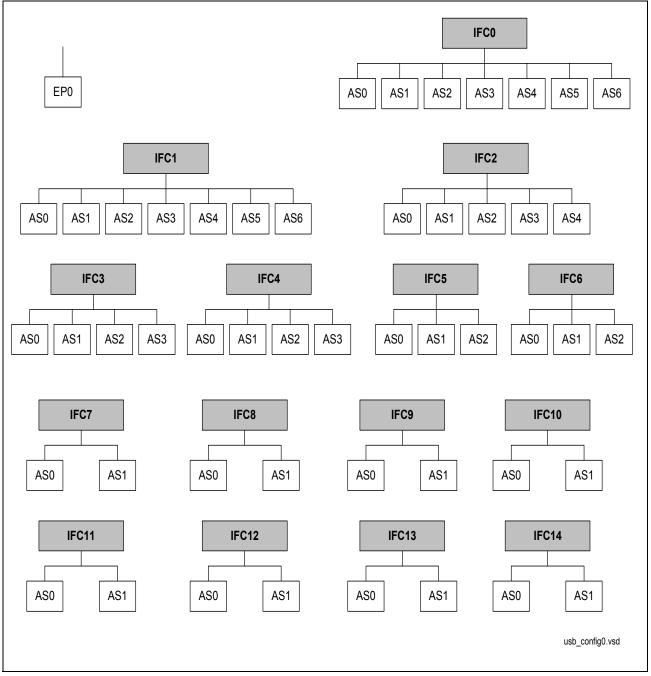

| 516            | Figure for Configuraton 0 added                                          |            |

| 550            | Bit position of AIM and IWIE                                             |            |

| <b>559</b>     | Description of CIAR modified                                             |            |

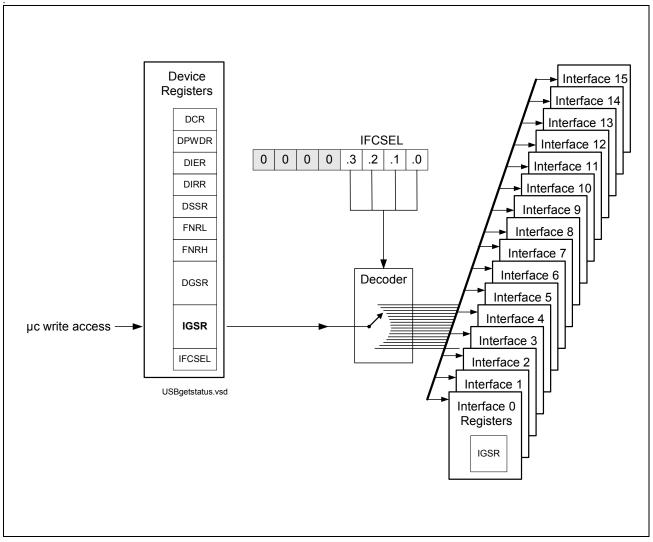

| <b>560</b>     | Reset of bits in GEPIR                                                   |            |

| <b>562</b>     | Two bits in register CIARIE added                                        |            |

| 566            | Device Detach Interrupt not available                                    |            |

| 567            | Description for SUI modified                                             |            |

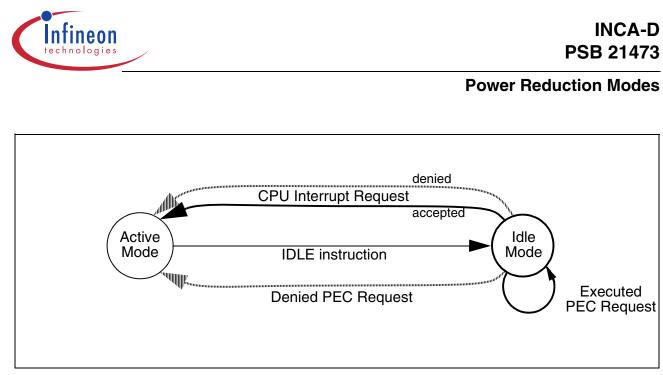

| 583            | Sleep mode description modified                                          |            |

| 608            | Reset values adapted                                                     |            |

| 633            | Absolute Maximum Ratings modified                                        |            |

| 634ff          | DC characteristics modified                                              |            |

| 656            | DC characteristics of transceiver removed (informaton partly move char.) | ved to DC  |

| 659ff          | Values for ADC charateristics modified, transmission characteris         | stics for  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com.

Edition 2003-03-31 Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 11/23/04. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Table of Contents**

#### Page

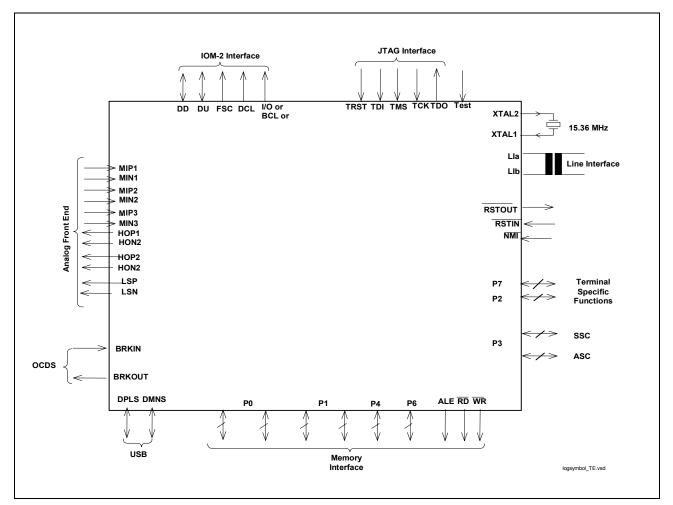

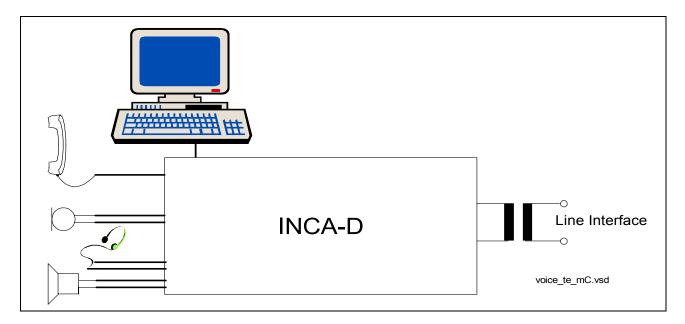

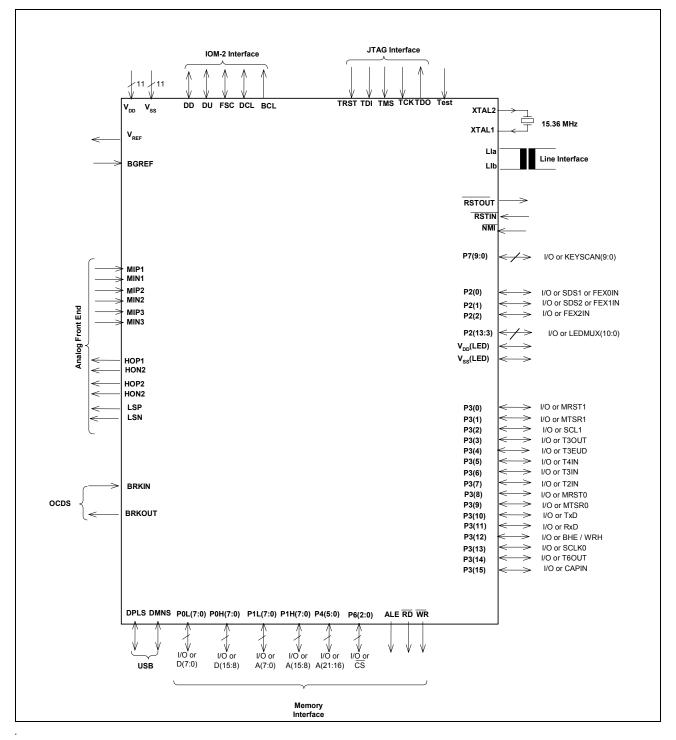

| <b>1</b><br>1.1<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.4<br>1.1.5<br>1.1.6<br>1.1.7<br>1.1.8<br>1.1.9<br>1.1.10<br>1.1.11<br>1.2<br>1.3 | Overview<br>Features<br>16 bit CPU, Internal RAM and Memory Interface<br>General Purpose Timer Unit<br>Asynchronous/Synchronous Serial Interface (ASC)<br>Two Serial Channel Interfaces (SSC)<br>USB Interface<br>16 bit fixed-point DSP<br>Analog Front End<br>Transceiver<br>Terminal Specific Functions (TSF)<br>IOM-2 Handler<br>General Features<br>Logical Symbols<br>Typical Application | 15<br>15<br>16<br>16<br>16<br>16<br>17<br>17<br>17<br>17<br>17 |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

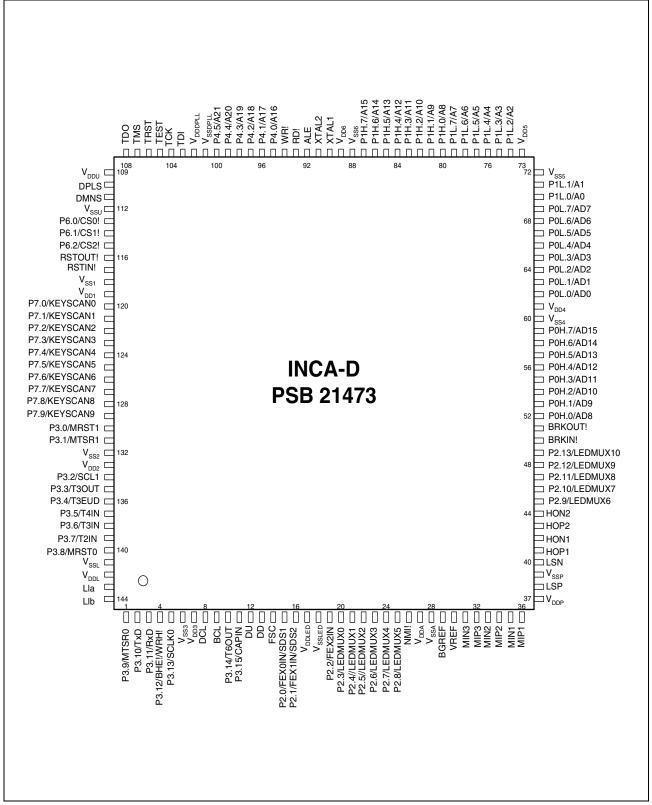

| <b>2</b><br>2.1<br>2.2                                                                                                             | Pin Descriptions         Pin Configuration         Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                | 20<br>20                                                       |

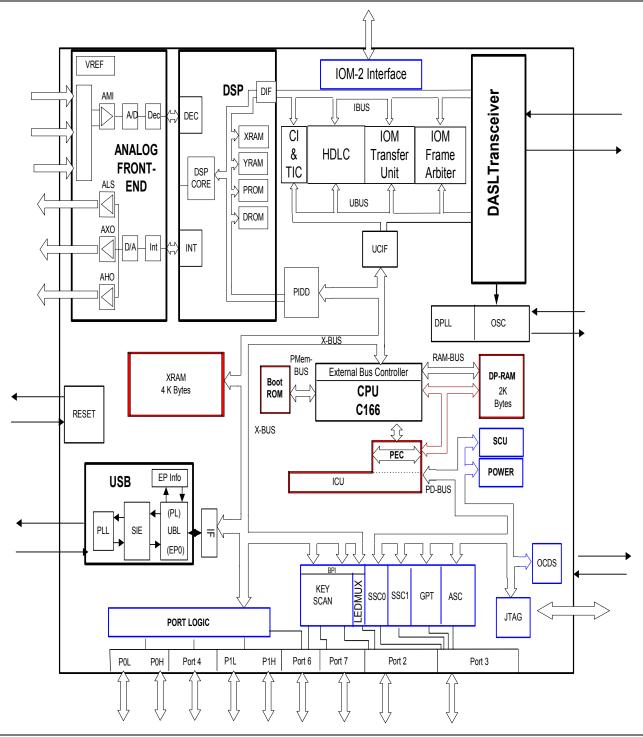

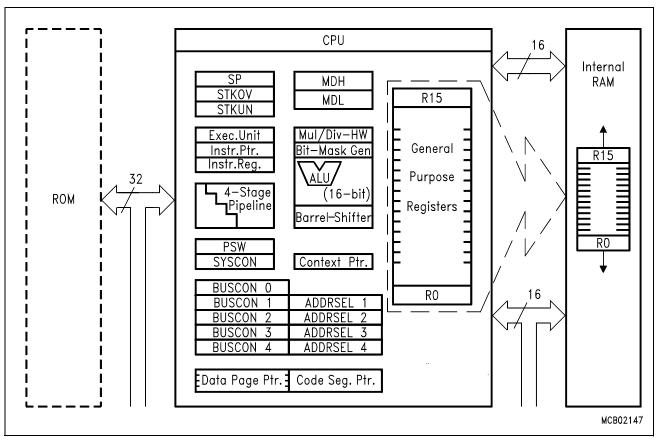

| <b>3</b><br>3.1<br>3.2                                                                                                             | Architectural Overview<br>Functional Block Diagram<br>Bus Systems                                                                                                                                                                                                                                                                                                                               | 31                                                             |

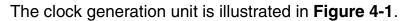

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8                                                                   | Clock Concept<br>Clock Generation<br>Terminal Specific Functions<br>USB<br>DSP<br>Microcontroller and Peripherals<br>AFE<br>IOM-2 clocks<br>Register Description of the Clock Concept Unit                                                                                                                                                                                                      | 34<br>35<br>35<br>35<br>36<br>38<br>38                         |

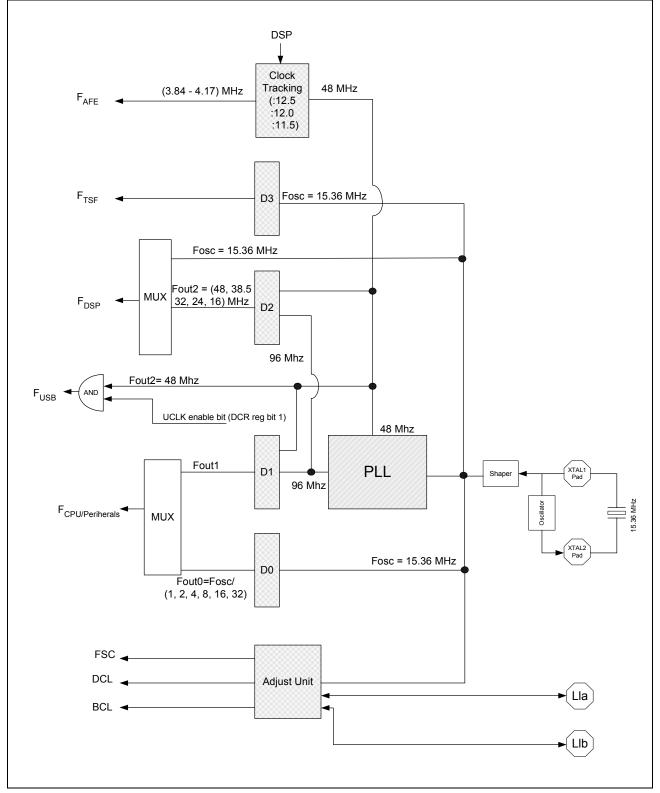

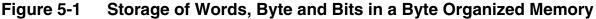

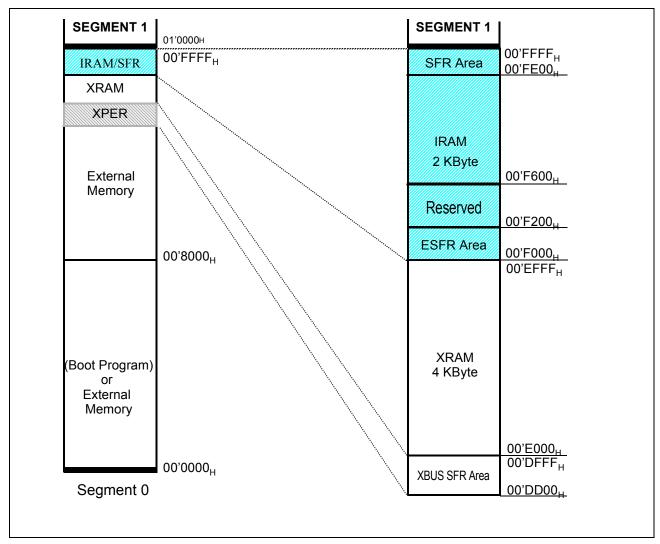

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                            | Memory OrganizationInternal ROM (Bootstrap Loader)On Chip XRAMInternal Dual-Port-RAM and SFR AreaXBUS PeripheralsSystem StackGeneral Purpose RegistersPEC Source and Destination PointersSpecial Function RegistersExternal Memory Space                                                                                                                                                        | 41<br>41<br>42<br>43<br>43<br>43<br>44<br>45                   |

| Table o                                                                                                                                                                                                                                            | f Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.10                                                                                                                                                                                                                                               | Crossing Memory Boundaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47   |

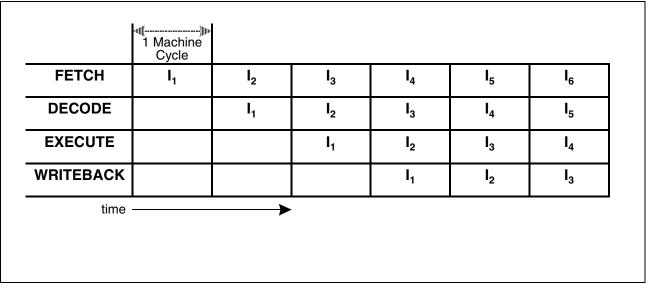

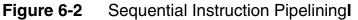

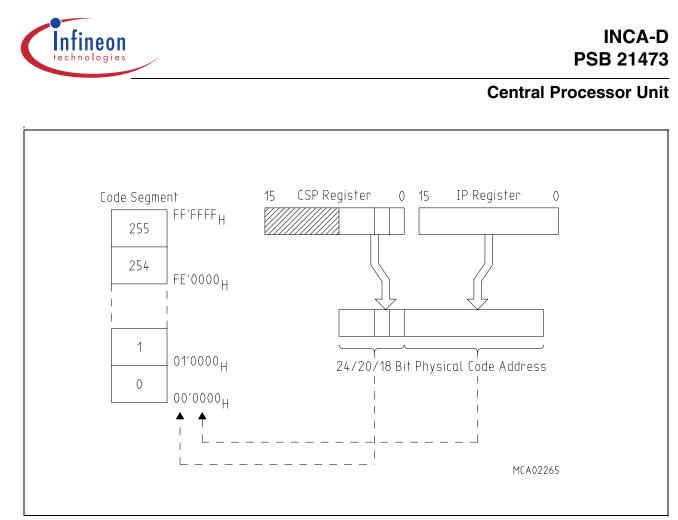

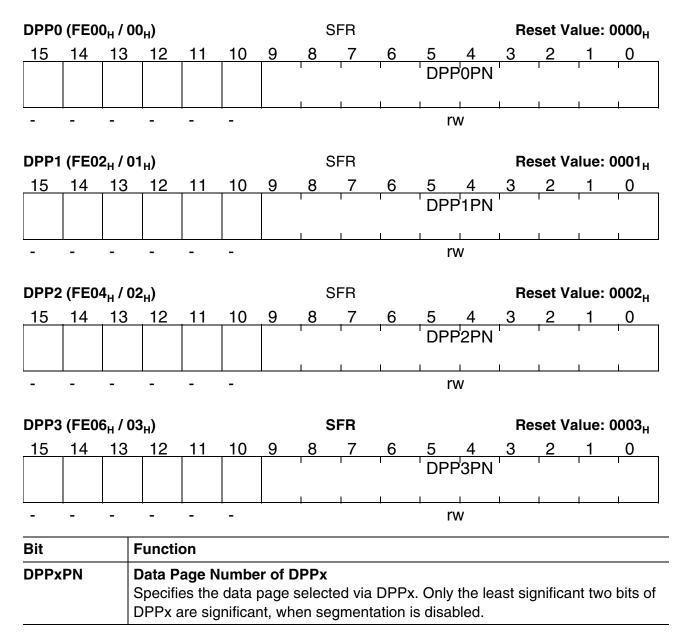

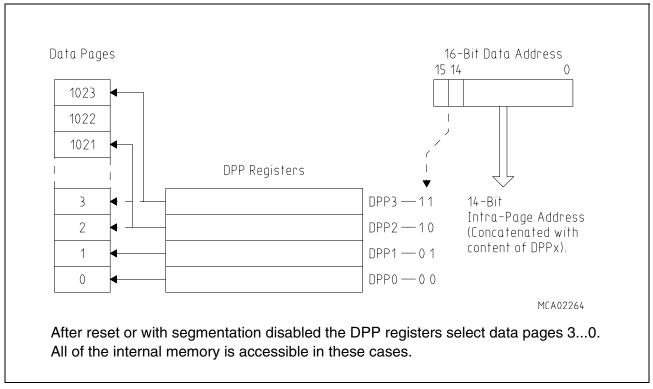

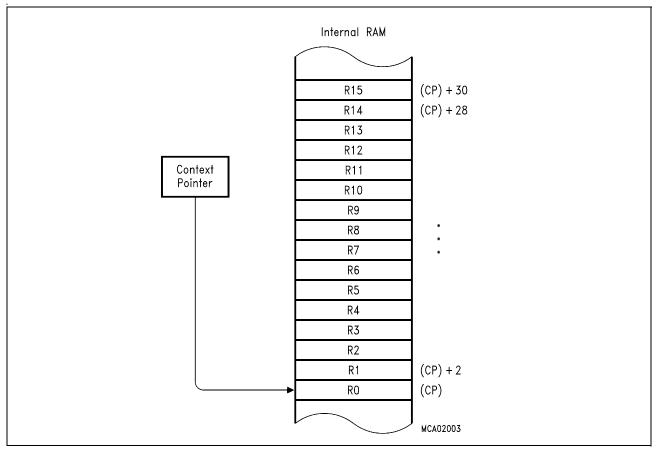

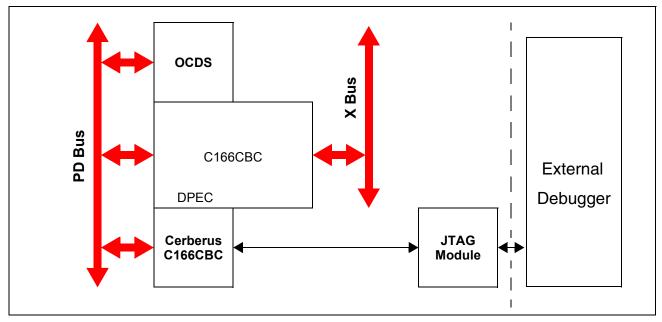

| <b>6</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.4.1<br>6.4.2                                                                                                                                                                                             | Central Processor Unit<br>Instruction Pipelining<br>CPU Special Function Registers<br>PEC - Extension of Functionality<br>XBUS System Architecture<br>Bus Access Control<br>XBUS Peripheral Configuration Block                                                                                                                                                                                                                                                                                                         |      |

| <b>7</b><br>7.1                                                                                                                                                                                                                                    | Integrated OCDS Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

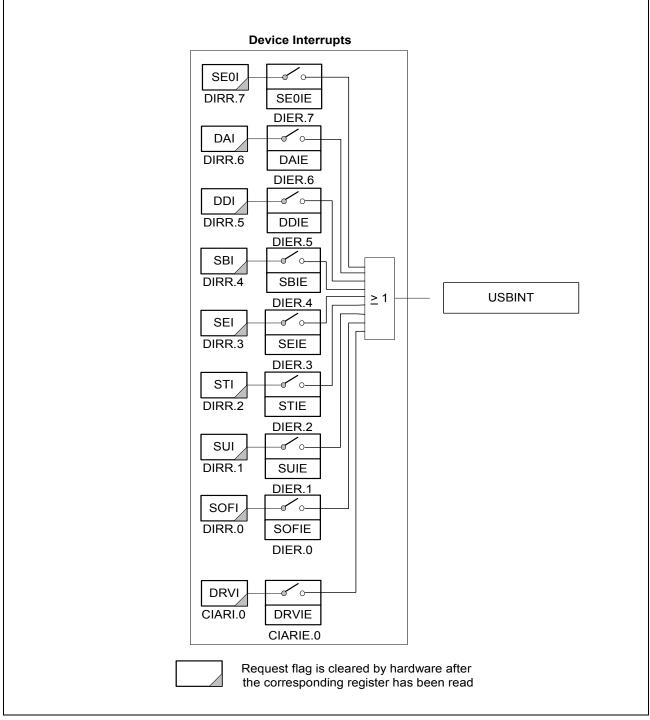

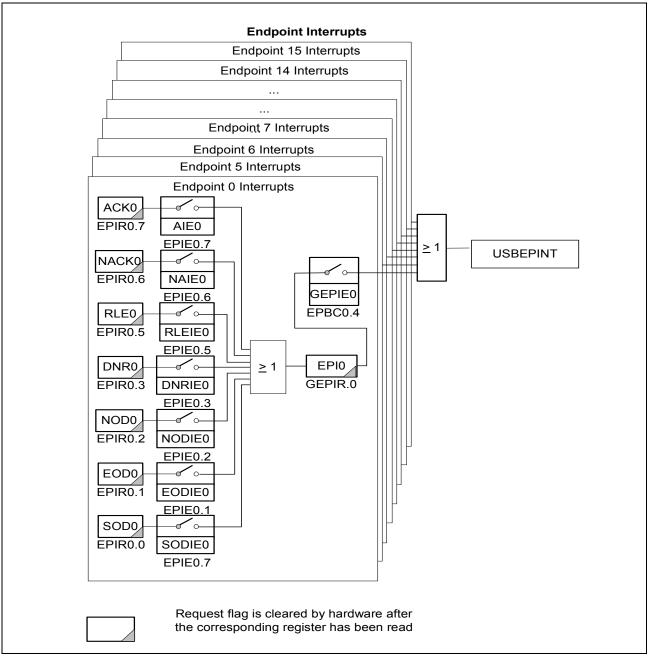

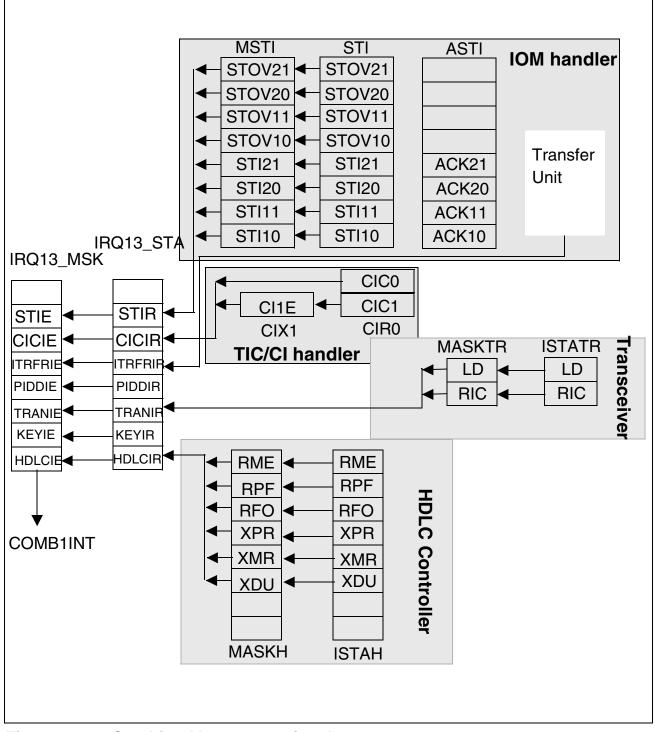

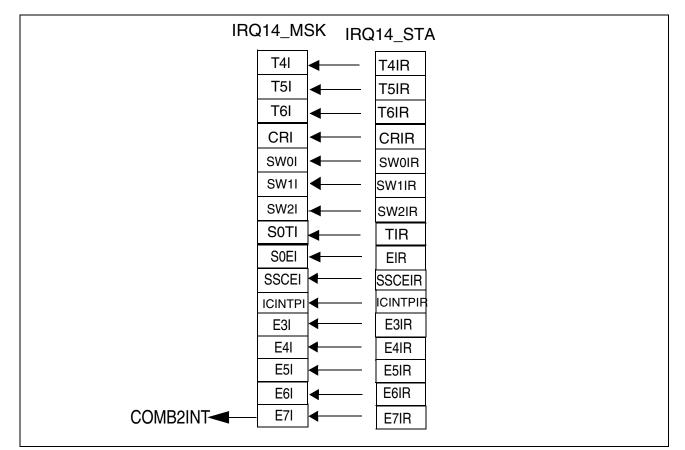

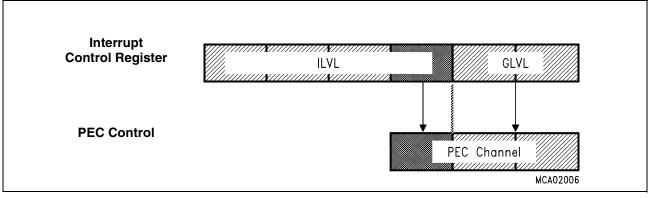

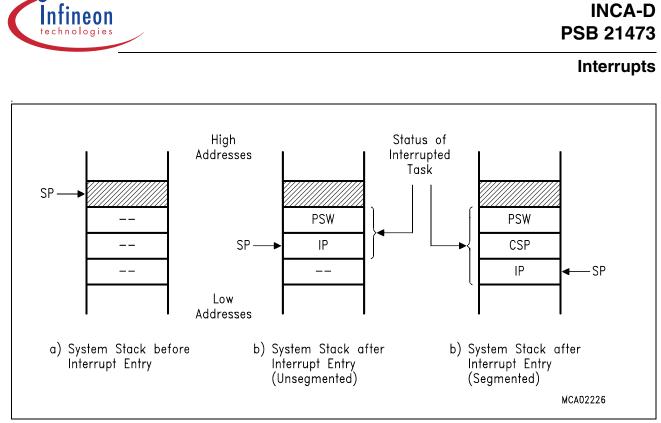

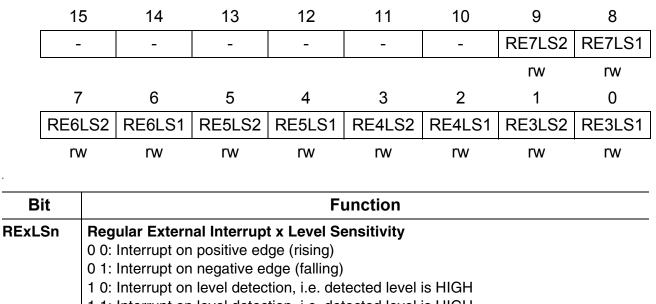

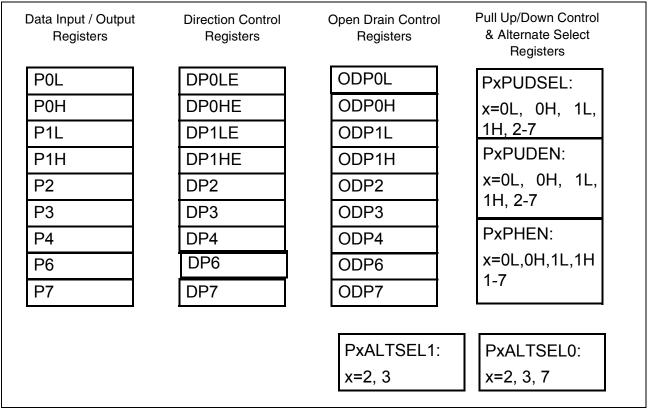

| <ul> <li>8</li> <li>8.1</li> <li>8.2</li> <li>8.2.1</li> <li>8.2.2</li> <li>8.2.3</li> <li>8.2.4</li> <li>8.2.5</li> <li>8.2.6</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> <li>8.6</li> <li>8.7</li> <li>8.8</li> <li>8.9</li> <li>8.10</li> </ul> | InterruptsInterrupt System StructureCombined Interrupt SourcesInterrupt Node 3 (USBINT)Interrupt Node 4 (USBEPINT)Interrupt Node 13 (COMB1INT)Interrupt Node 14 (COMB2INT)Interrupt Node 14 (COMB2INT)Normal Interrupt Processing and PEC ServiceInterrupt System Register DescriptionInterrupt Control RegistersOperation of the PEC ChannelsPrioritization of Interrupt and PEC Service RequestsSaving the Status during Interrupt ServiceInterrupt Response TimesPEC Response TimesExternal InterruptsTrap Functions |      |

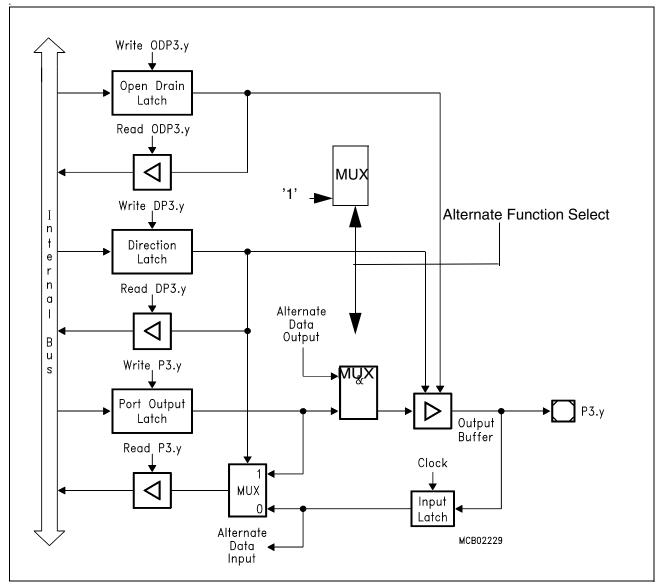

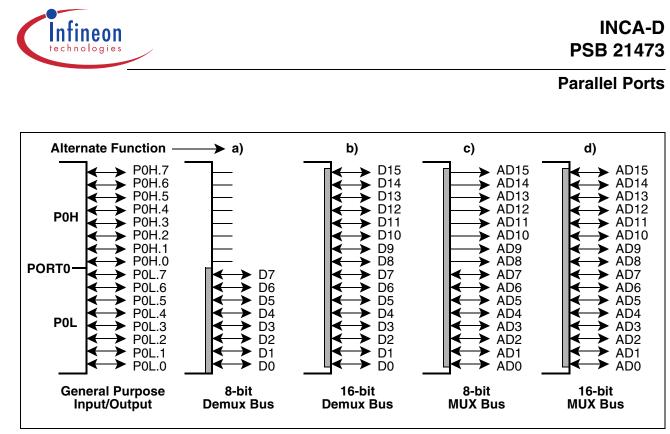

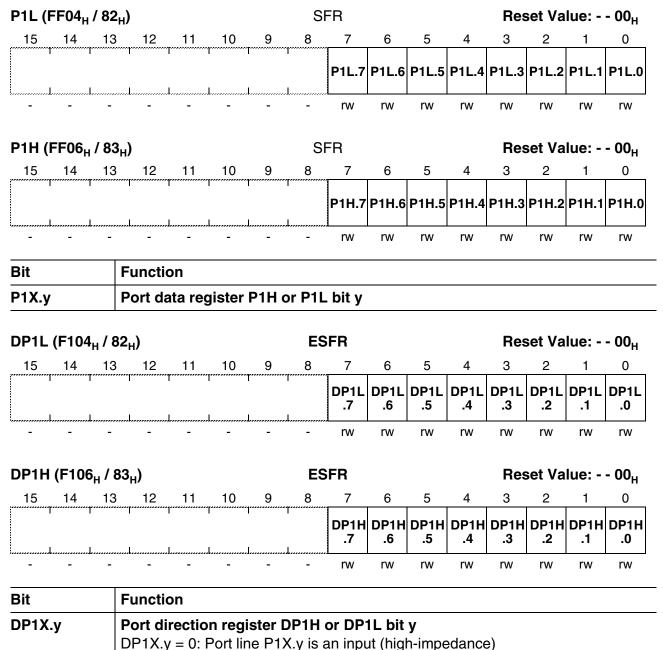

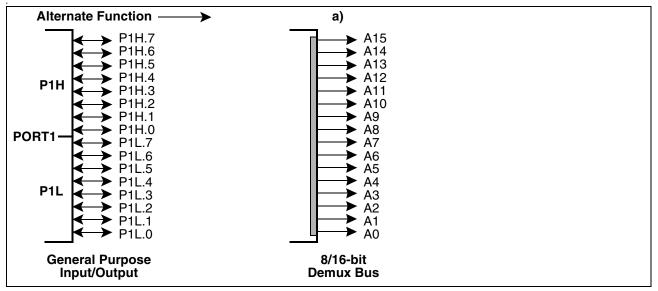

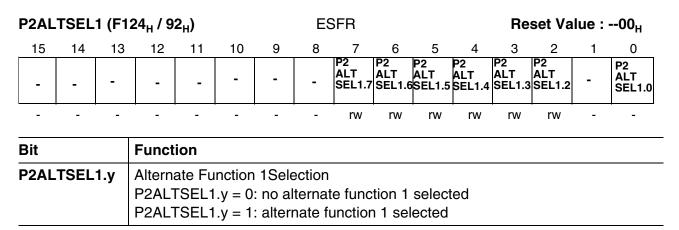

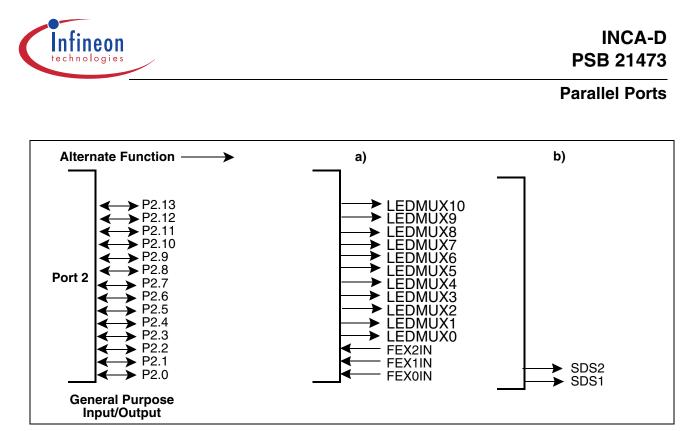

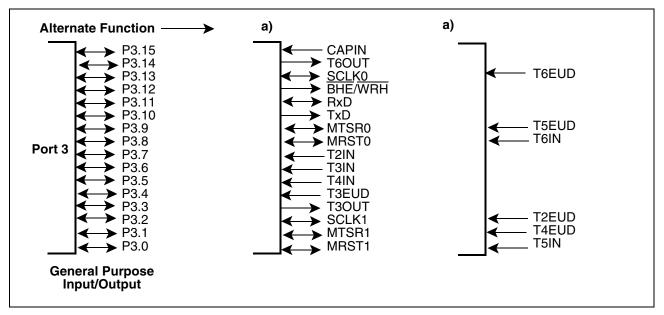

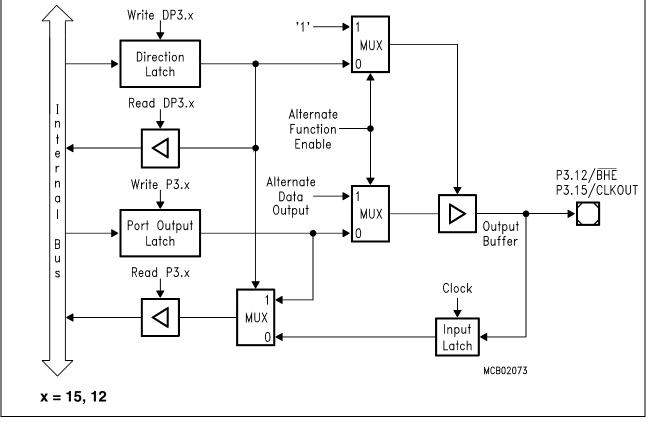

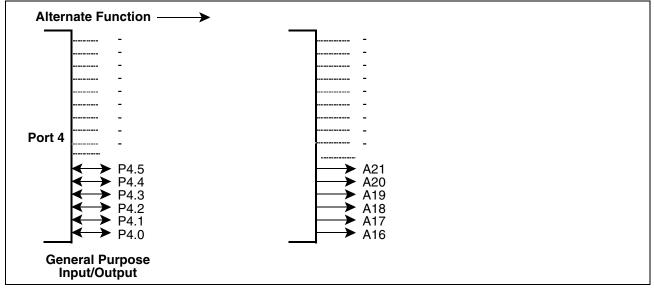

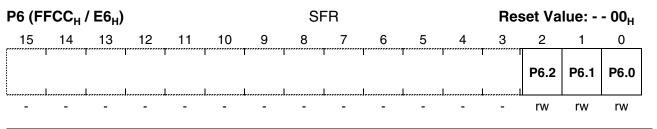

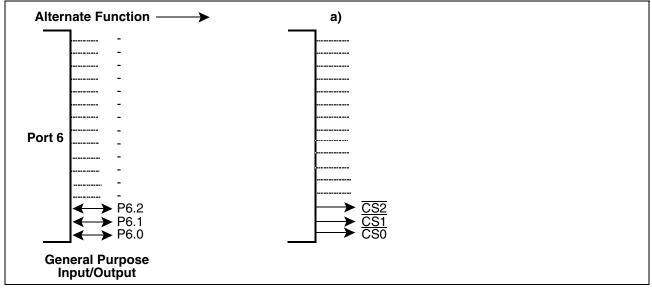

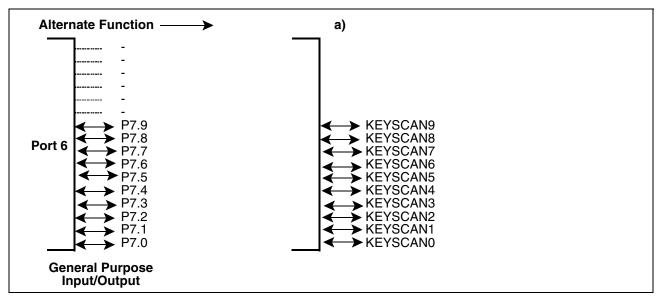

| 9<br>9.1<br>9.2<br>9.2.1<br>9.3<br>9.3.1<br>9.4<br>9.4.1<br>9.5<br>9.5.1<br>9.6<br>9.6.1                                                                                                                                                           | Parallel PortsPORT0Alternate Functions of PORT0PORT1Alternate Functions of PORT1PORT2Alternate Functions of PORT2PORT3Alternate Functions of PORT3PORT4Alternate Functions of PORT4PORT6Alternate Functions of PORT6                                                                                                                                                                                                                                                                                                    |      |

| Table of                                                                                                                                    | Contents                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.7<br>9.7.1                                                                                                                                | PORT7 Alternate Functions of PORT7                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                |

| 10                                                                                                                                          | Dedicated Pins                                                                                                                                                                                                                                                                                                                                                                     | . 156                                                                                                                                                                                          |

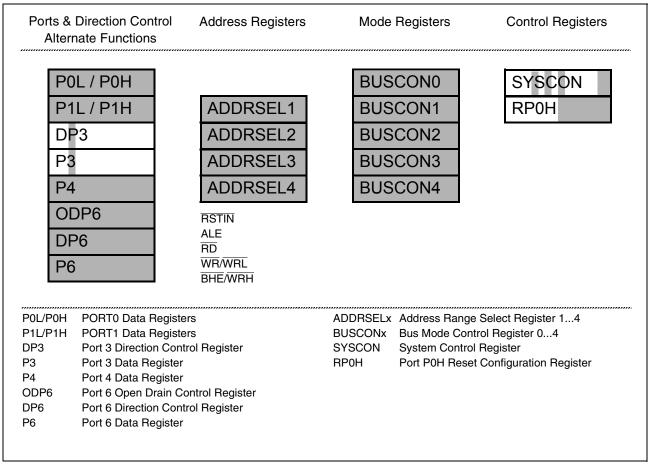

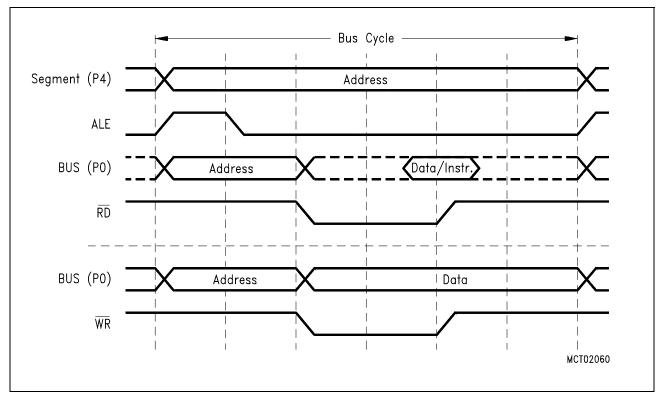

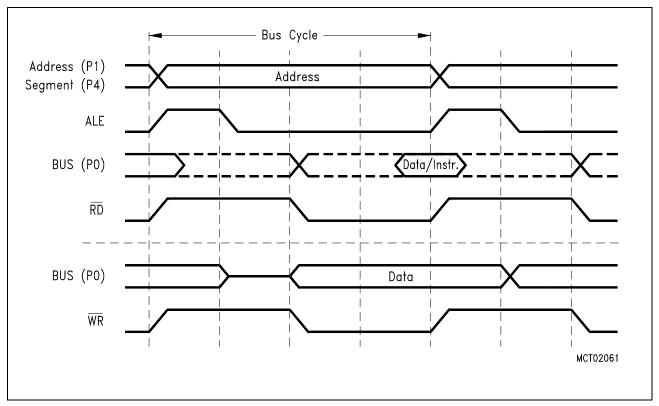

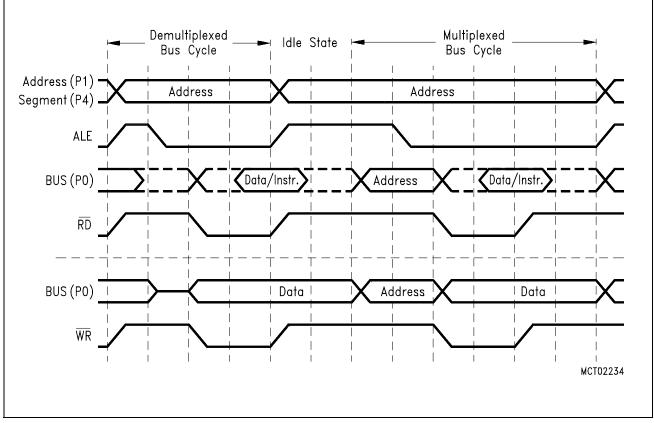

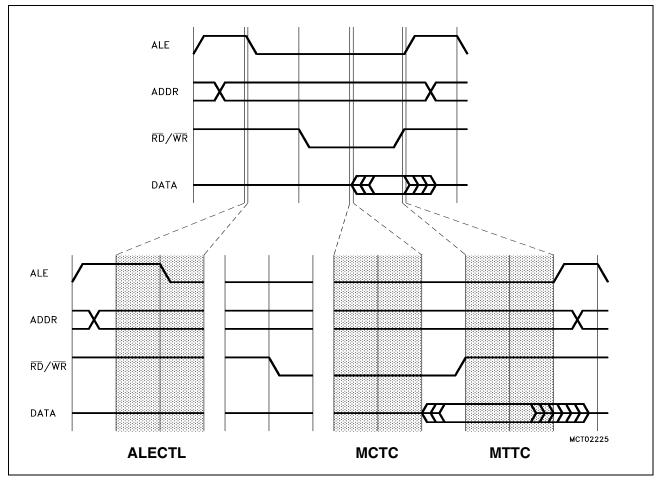

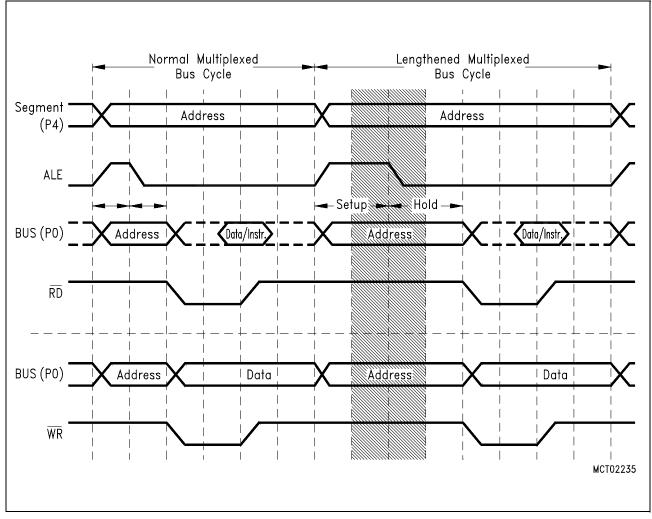

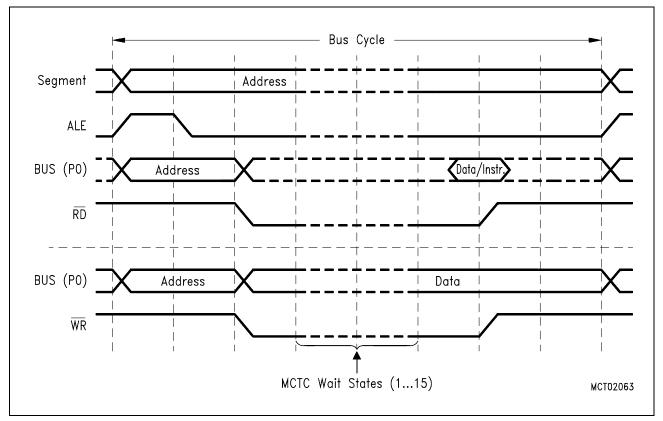

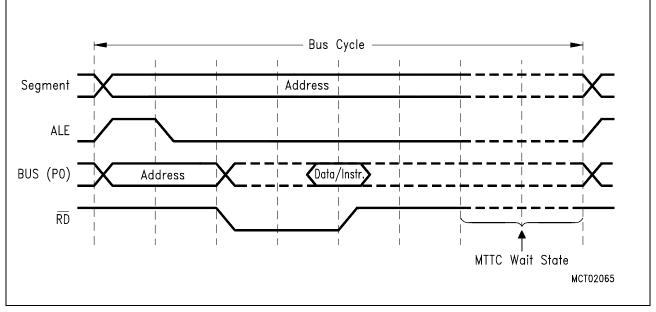

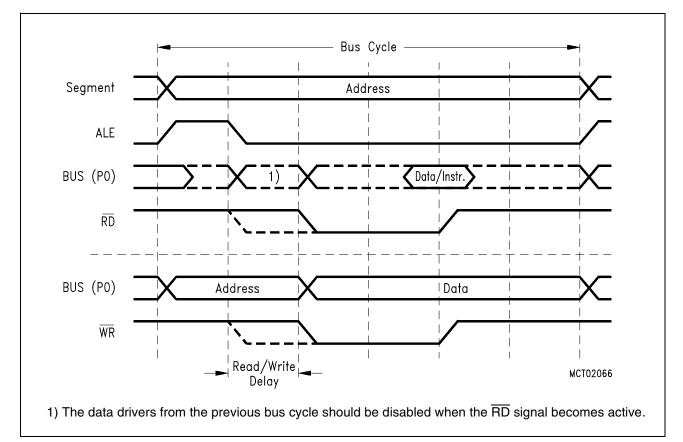

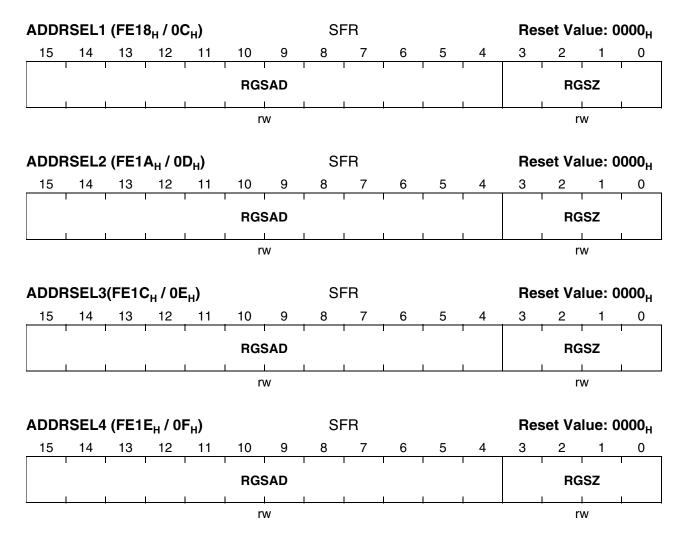

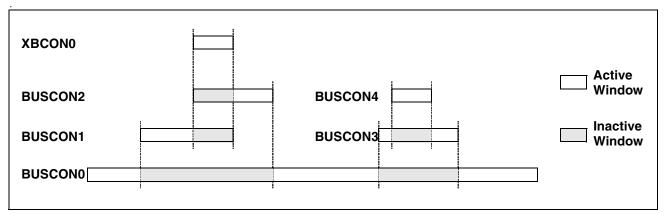

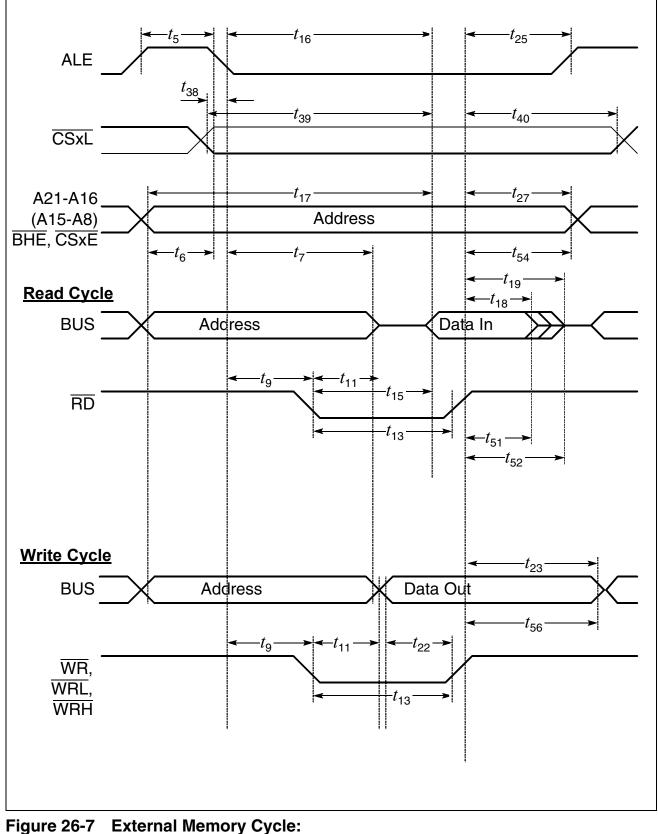

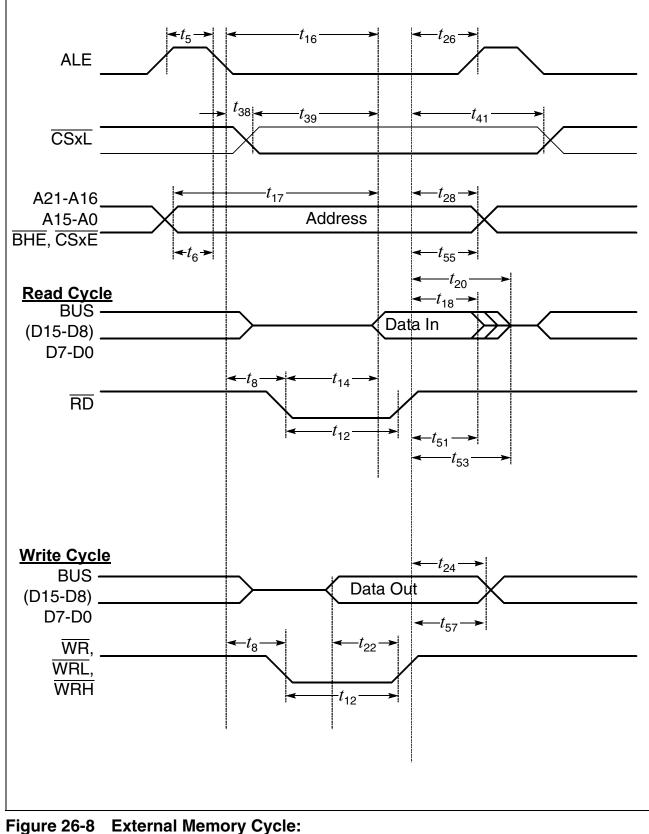

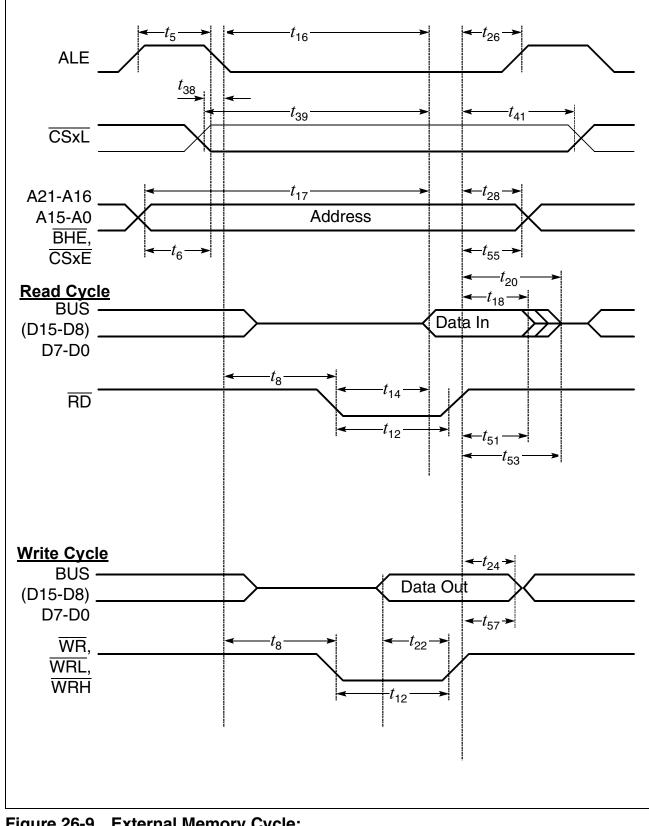

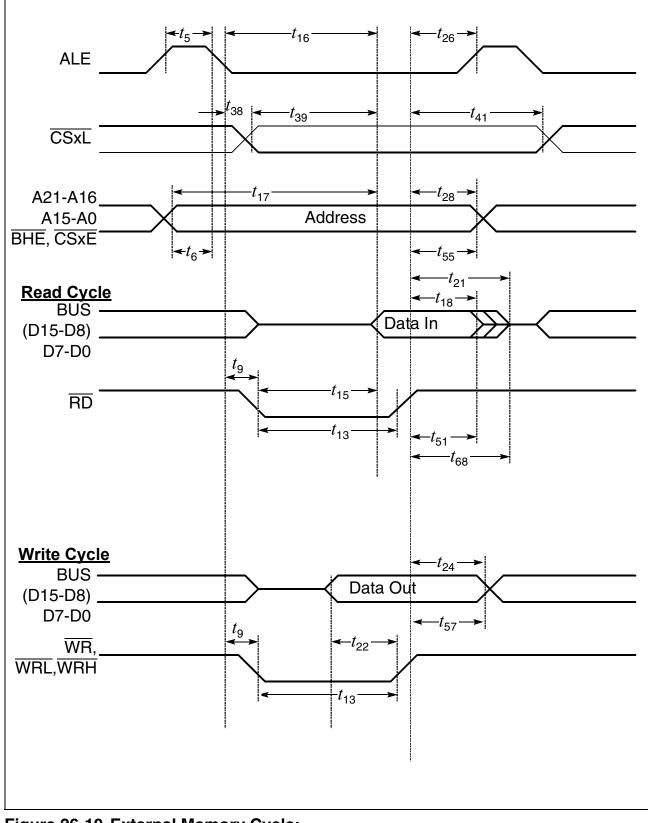

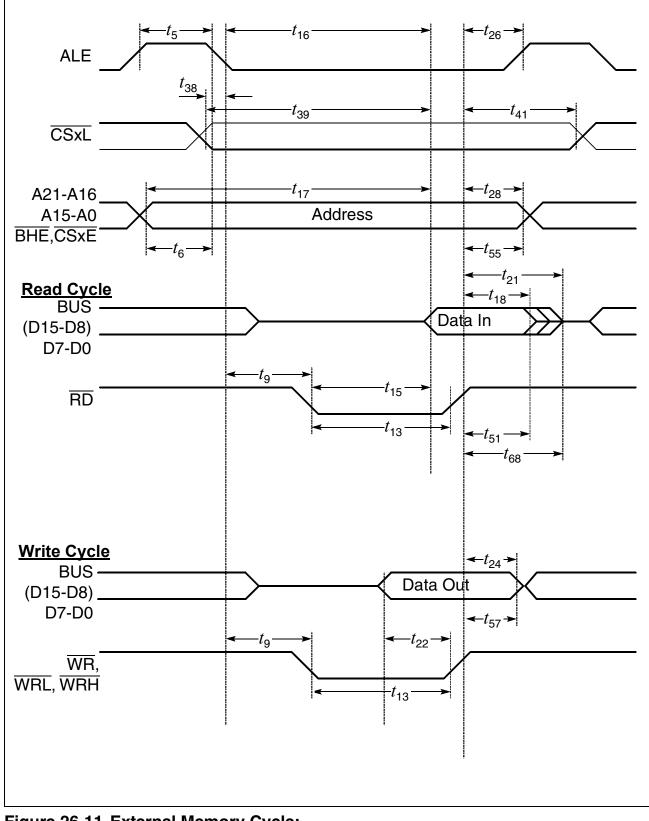

| <b>11</b><br>11.1<br>11.2<br>11.3<br>11.4                                                                                                   | The External Bus Interface         External Bus Modes         Programmable Bus Characteristics         Controlling the External Bus Controller         EBC Idle State                                                                                                                                                                                                              | . 160<br>. 168<br>. 172                                                                                                                                                                        |

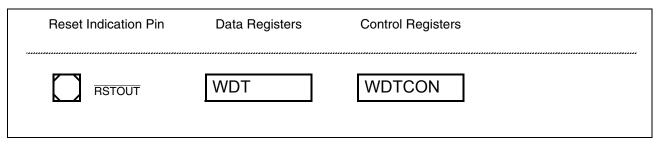

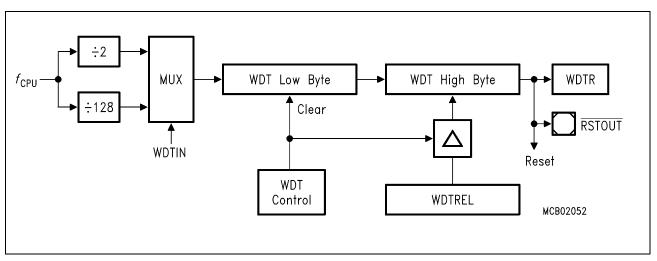

| <b>12</b><br>12.1                                                                                                                           | The Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                |

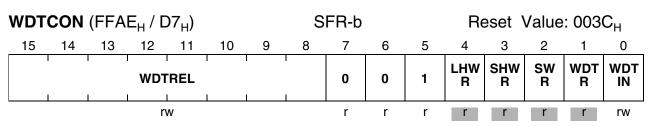

| <b>13</b><br>13.1<br>13.2<br>13.3                                                                                                           | The Bootstrap LoaderActivation of ASC Bootstrap LoaderLoading the Startup CodeTransfer of User Program                                                                                                                                                                                                                                                                             | . 183<br>. 185                                                                                                                                                                                 |

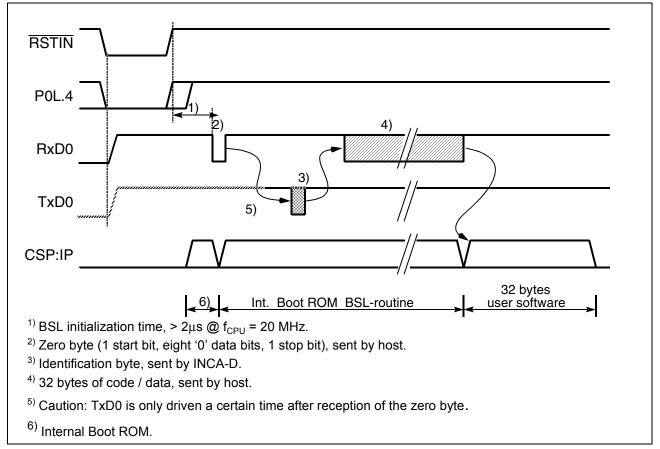

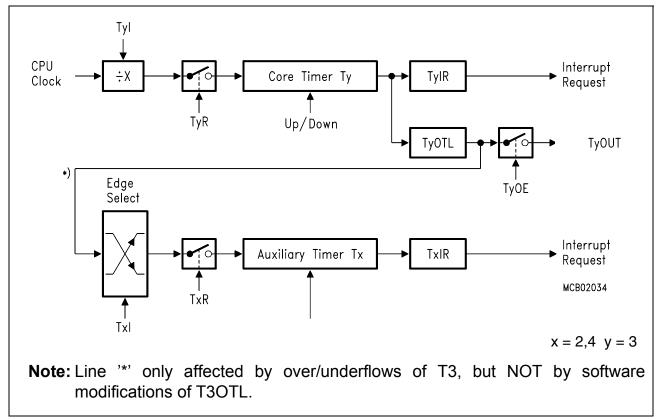

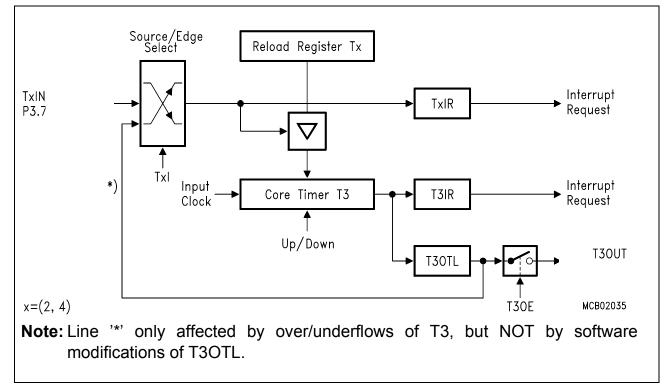

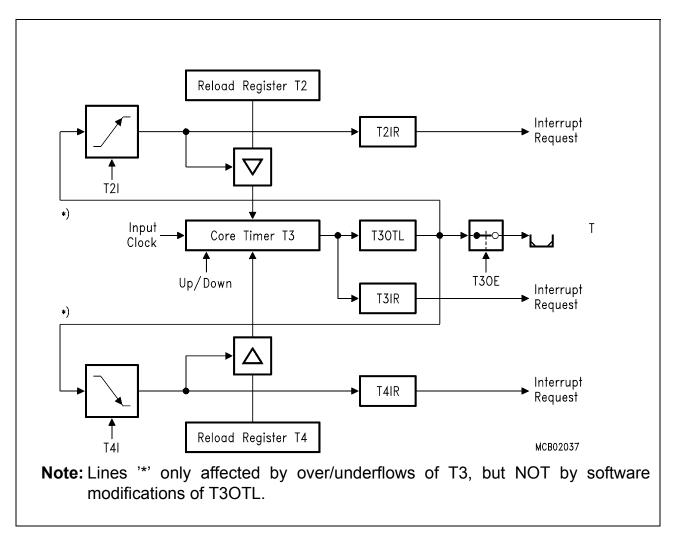

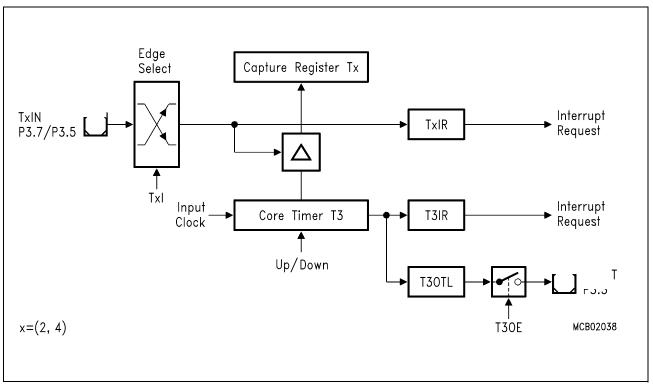

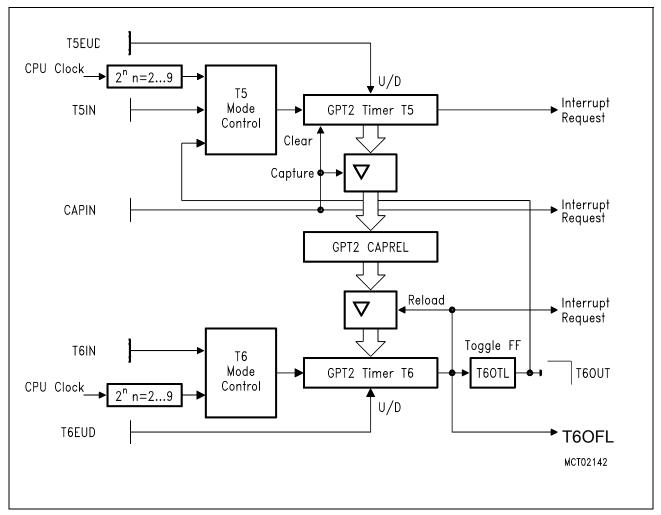

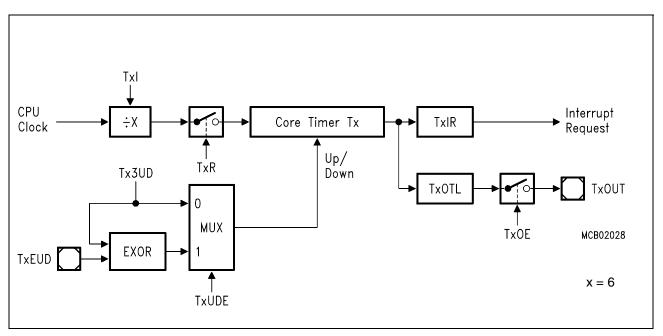

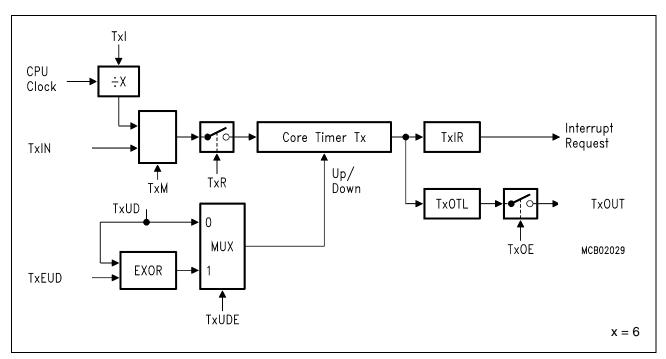

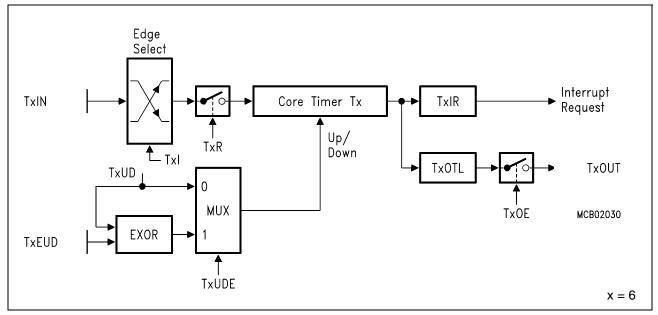

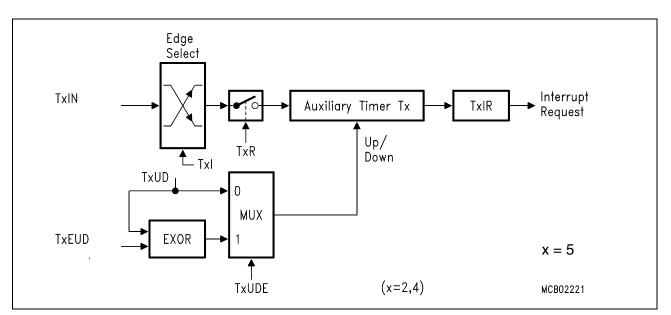

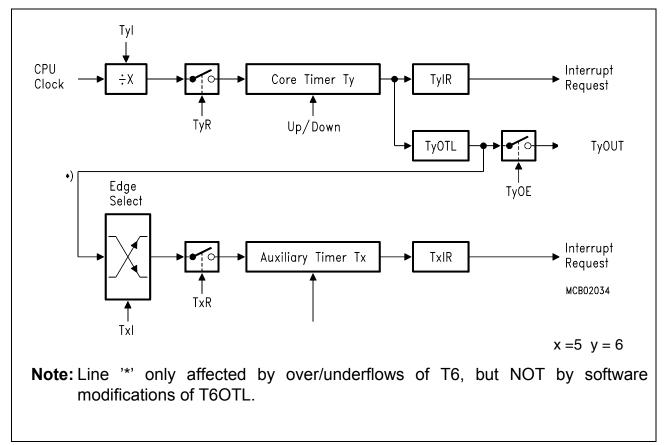

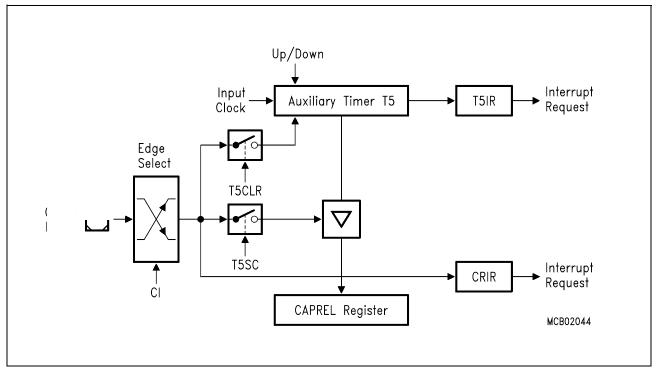

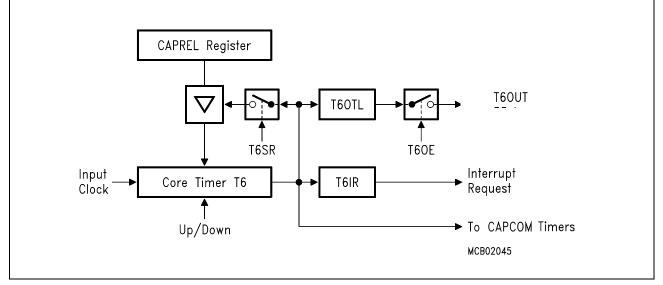

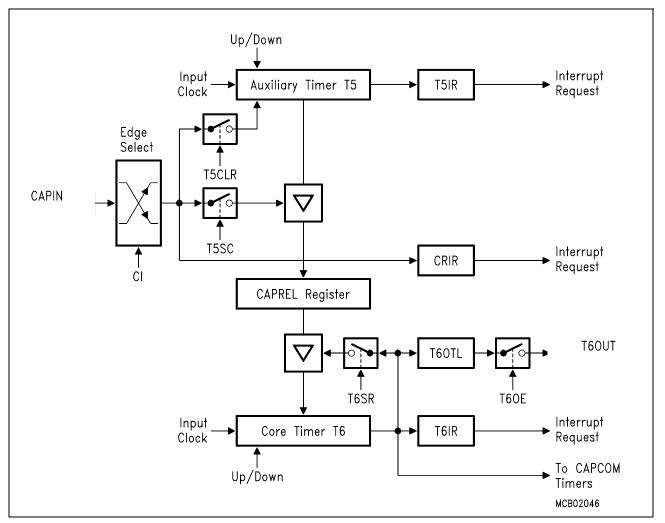

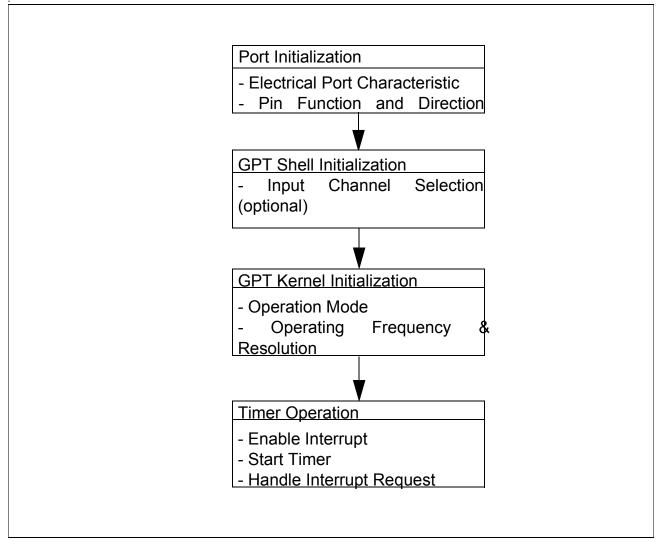

| <b>14</b><br>14.1<br>14.1.2<br>14.2<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.3<br>14.2.4<br>14.3                                               | General Purpose Timer Unit<br>Functional Description of Timer Block 1<br>Core Timer T3<br>Auxiliary Timers T2 and T4<br>Functional Description of Timer Block 2<br>Core Timer T6<br>Auxiliary Timer T5<br>Timer Concatenation<br>Programming the GPT Unit<br>GPT Registers                                                                                                         | <ul> <li>. 188</li> <li>. 189</li> <li>. 198</li> <li>. 205</li> <li>. 206</li> <li>. 209</li> <li>. 211</li> <li>. 217</li> <li>. 218</li> </ul>                                              |

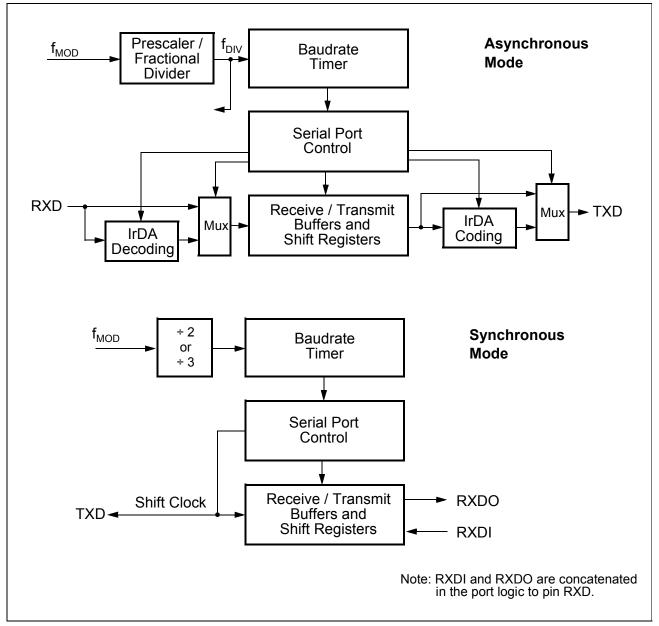

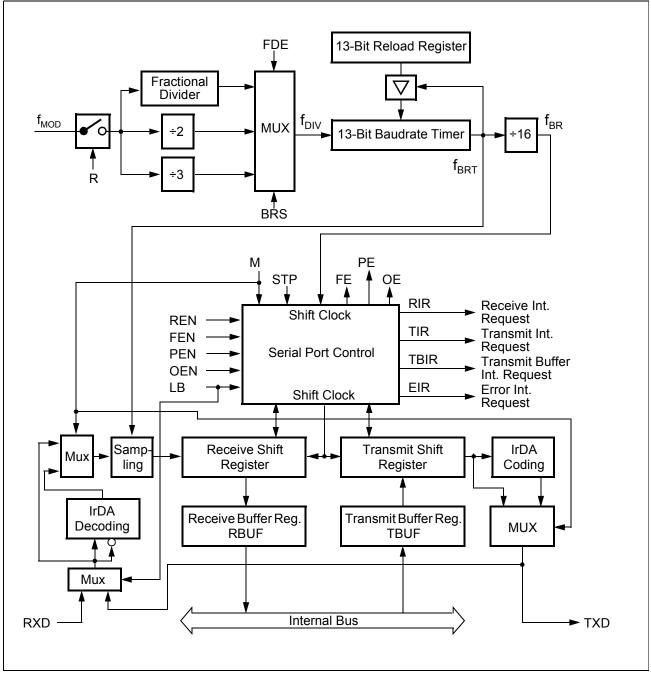

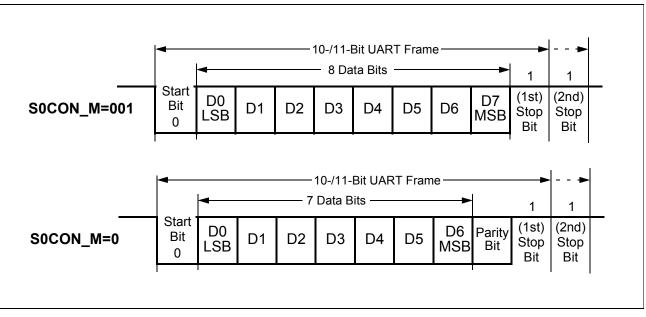

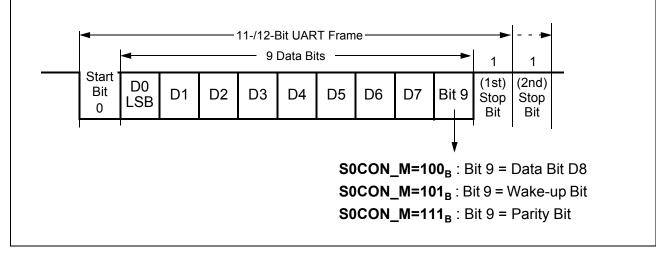

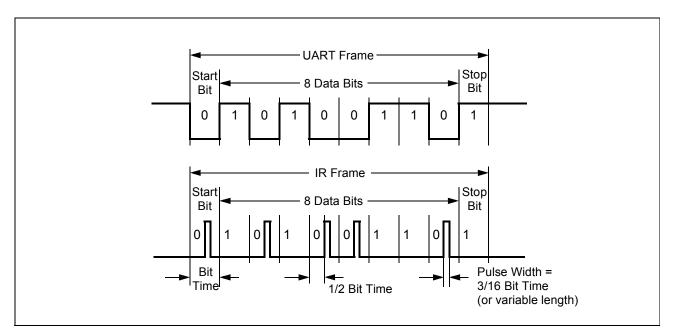

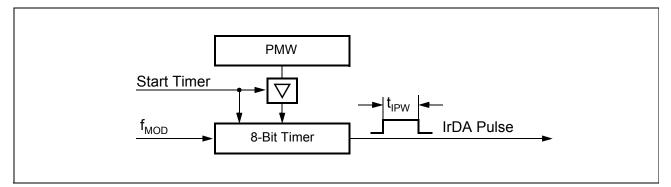

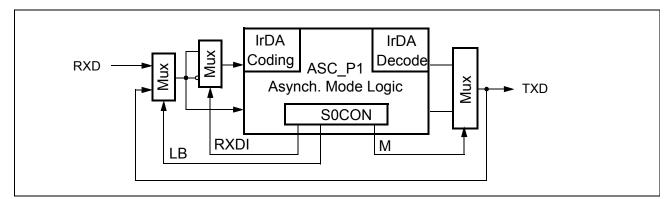

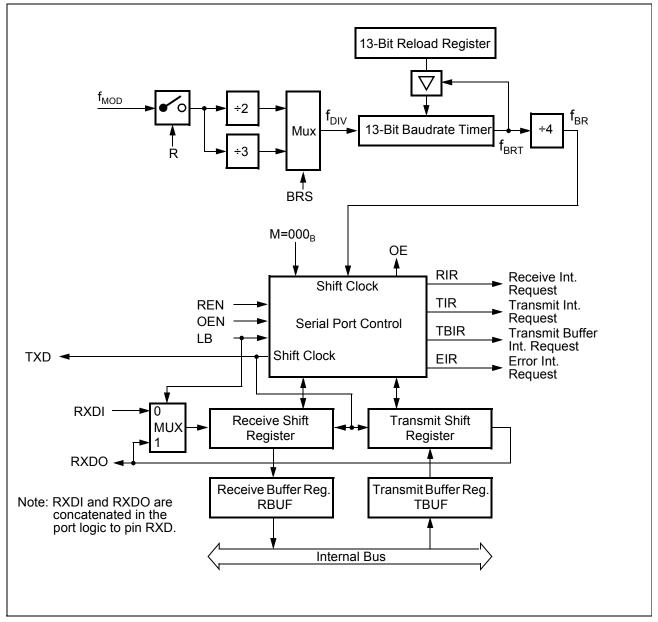

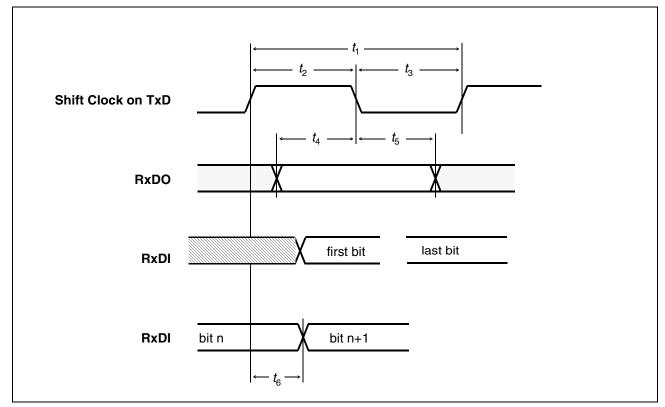

| <b>15</b><br>15.1<br>15.1.2<br>15.1.3<br>15.1.4<br>15.1.5<br>15.1.5.1<br>15.1.5.2<br>15.1.5.3<br>15.1.5.4<br>15.1.5.5<br>15.1.6<br>15.1.6.1 | The Asynchronous / Synchr. Serial Interface         Functional Description         Features         Overview         Register Description         General Operation         Asynchronous Operation         Asynchronous Data Frames         Asynchronous Transmission         IrDA Mode         RXD/TXD Data Path Selection in Asynchronous Modes         Synchronous Transmission | <ul> <li>. 229</li> <li>. 229</li> <li>. 231</li> <li>. 237</li> <li>. 237</li> <li>. 238</li> <li>. 241</li> <li>. 242</li> <li>. 242</li> <li>. 244</li> <li>. 244</li> <li>. 244</li> </ul> |

| 15.1.6.2                                                                                                                                    | Synchronous Reception                                                                                                                                                                                                                                                                                                                                                              | . 246                                                                                                                                                                                          |

Page

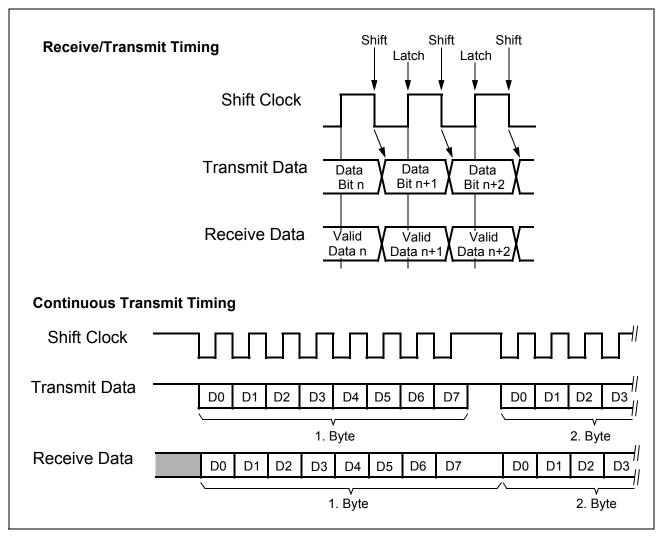

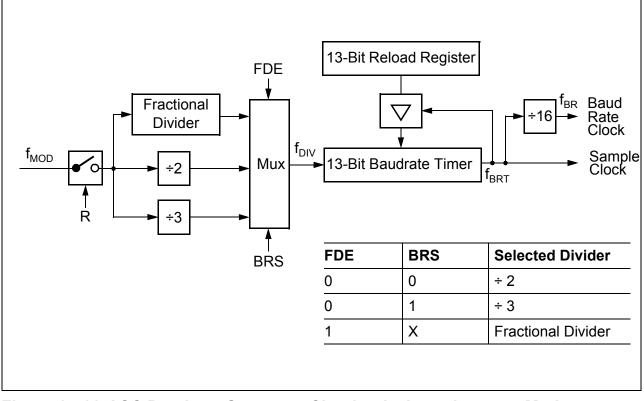

| 15.1.6.3<br>15.1.7<br>15.1.7.1<br>15.1.7.2<br>15.1.8<br>15.1.9 | Synchronous Timing<br>Baudrate Generation<br>Baudrates in Asynchronous Mode<br>Baudrates in Synchronous Mode<br>Hardware Error Detection Capabilities<br>Interrupts | 247<br>248<br>251<br>253 |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

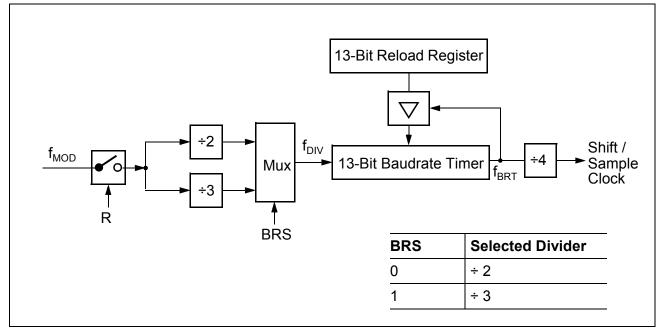

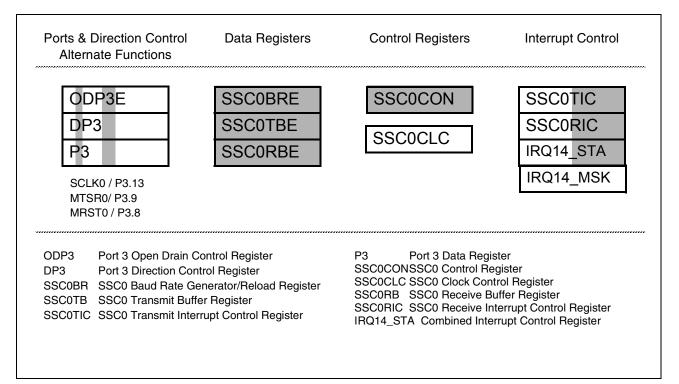

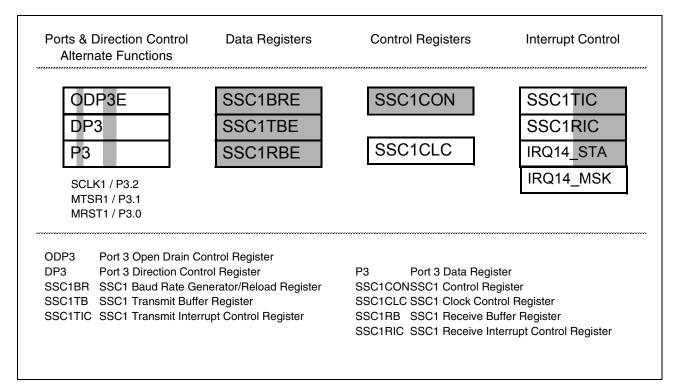

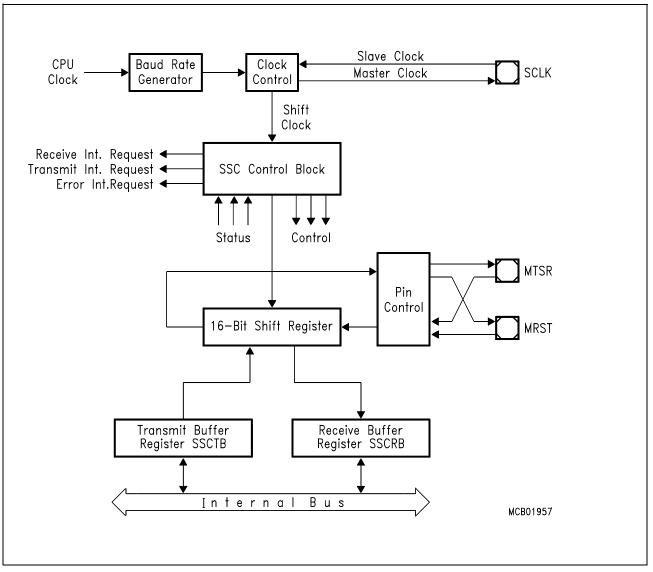

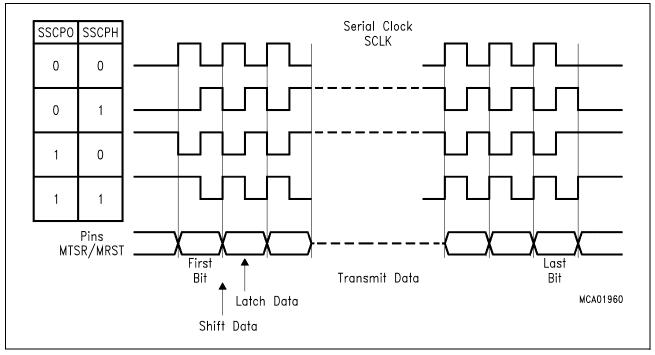

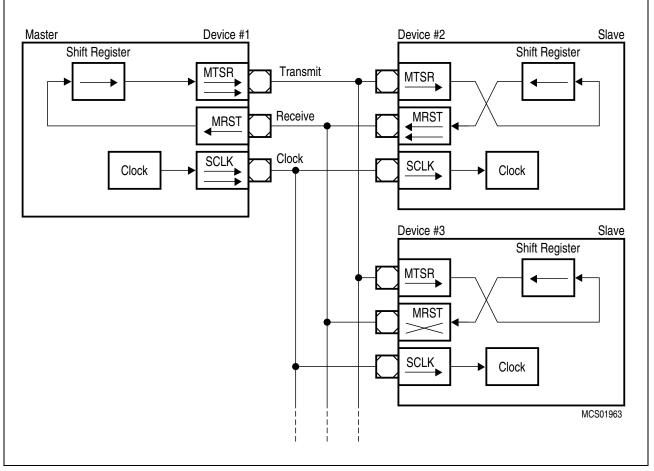

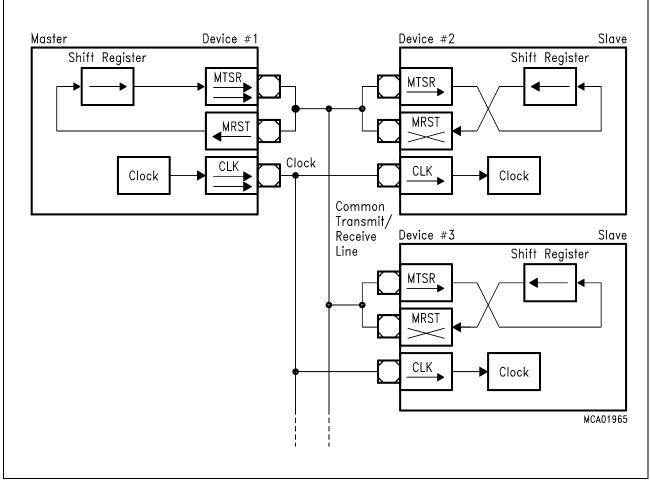

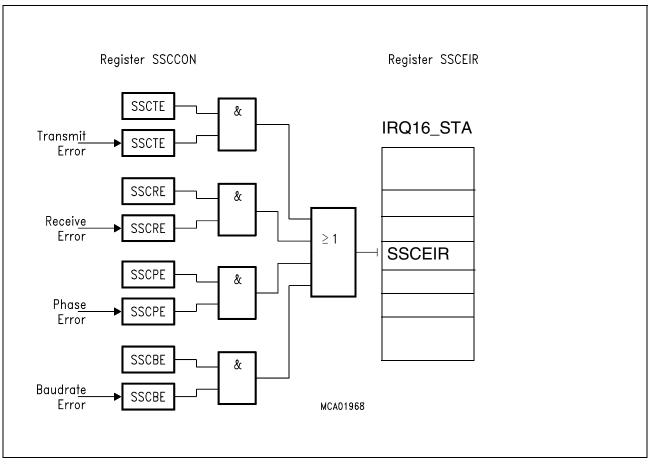

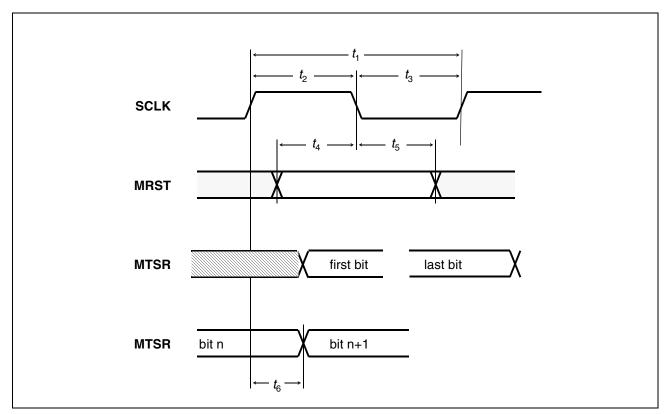

| <b>16</b><br>16.1<br>16.2<br>16.3<br>16.4<br>16.5              | The High-Speed Synchronous Serial InterfacesFull-Duplex OperationHalf Duplex OperationBaud Rate GenerationError Detection MechanismsSSCx Interrupt Control          | 262<br>265<br>267<br>268 |

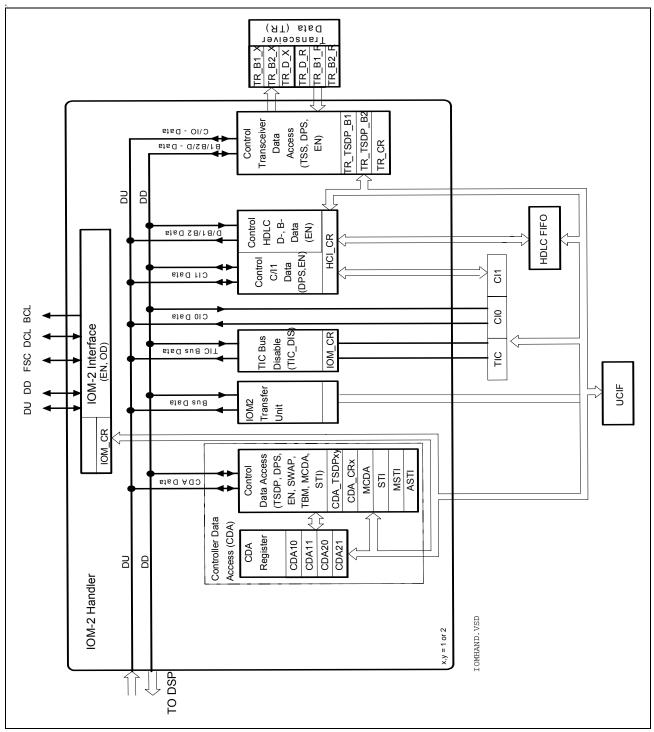

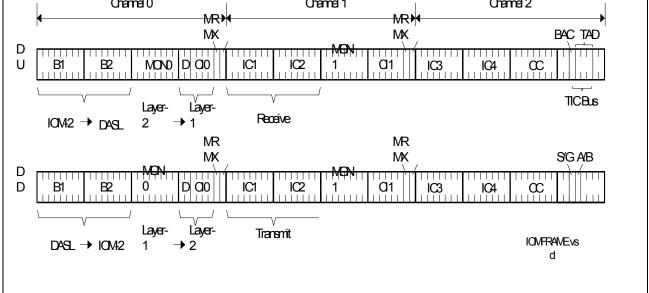

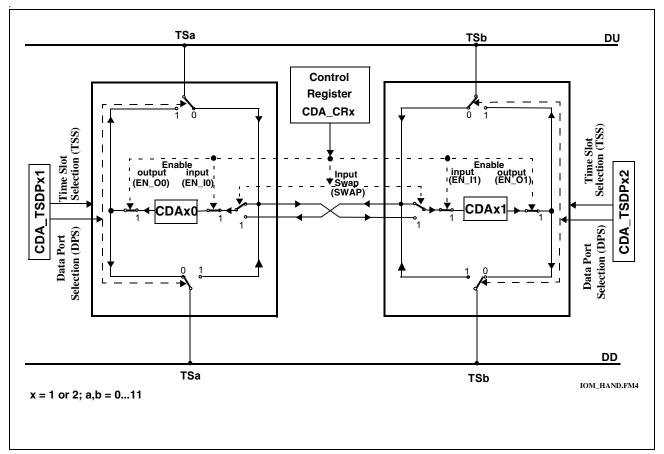

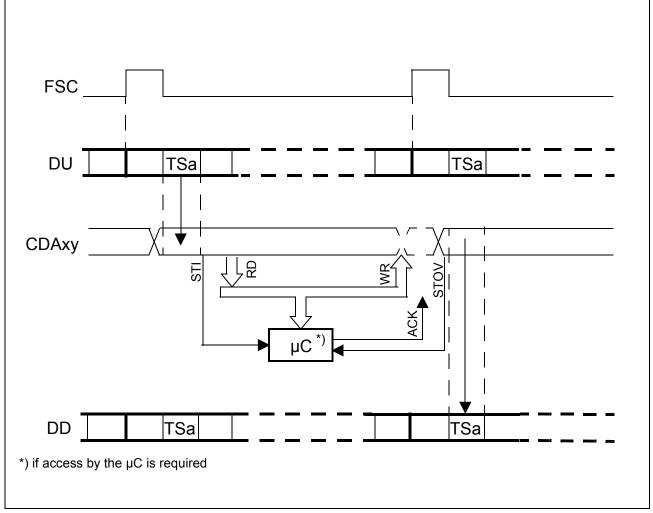

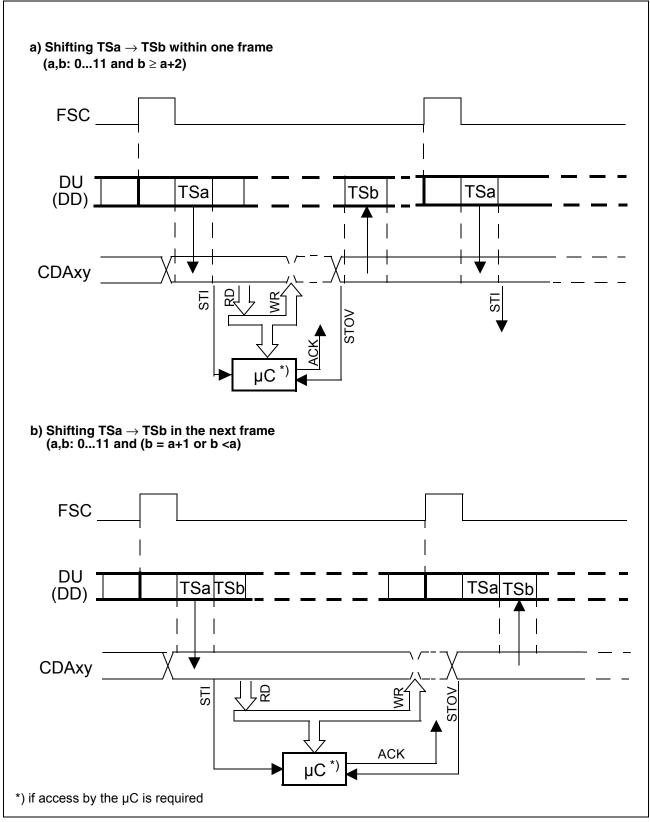

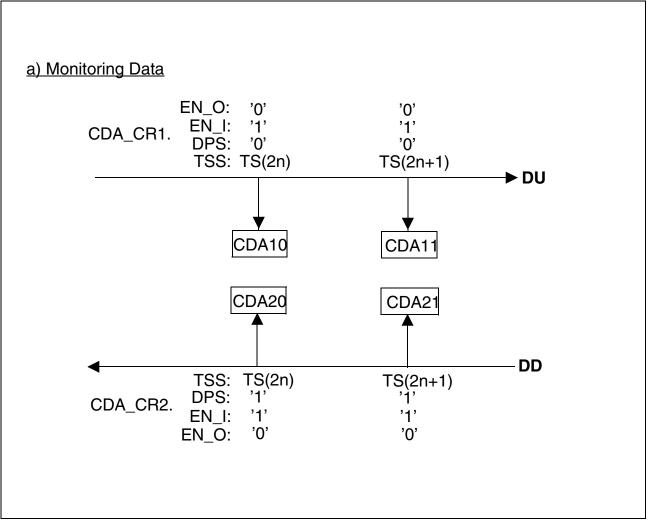

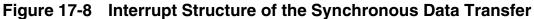

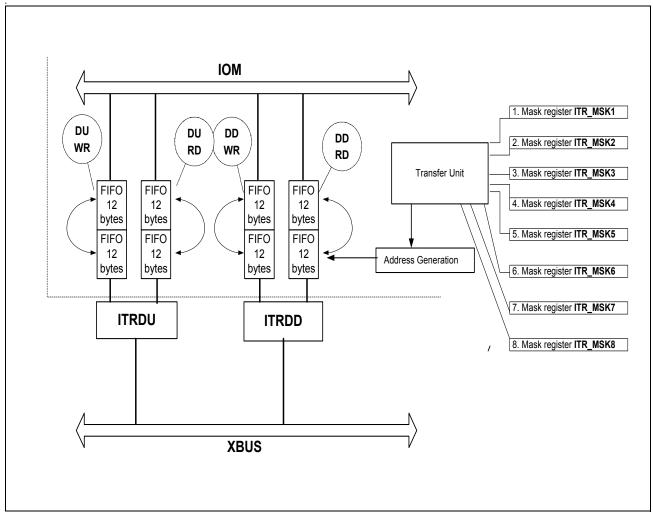

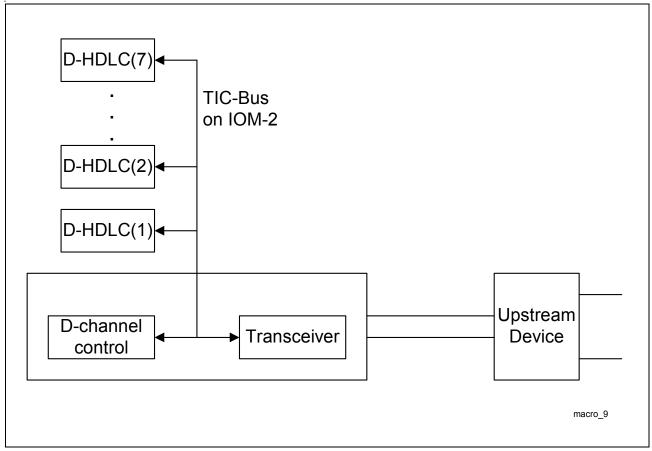

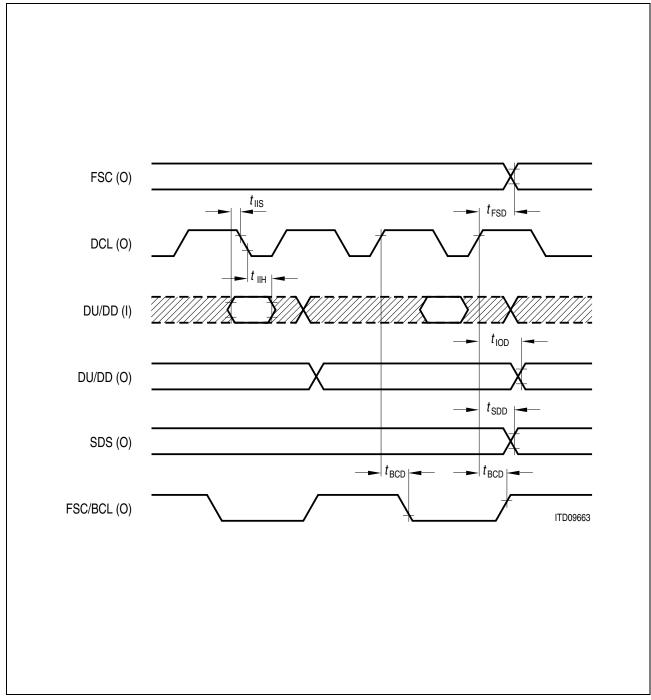

| <b>17</b><br>17.1<br>17.1.1<br>17.1.2                          | IOM-2 Handler, TIC/CI Handler and HDLC Controller         IOM2 Handler         IOM-2 Interface         Controller Data Access (CDA)                                 | 271<br>272               |

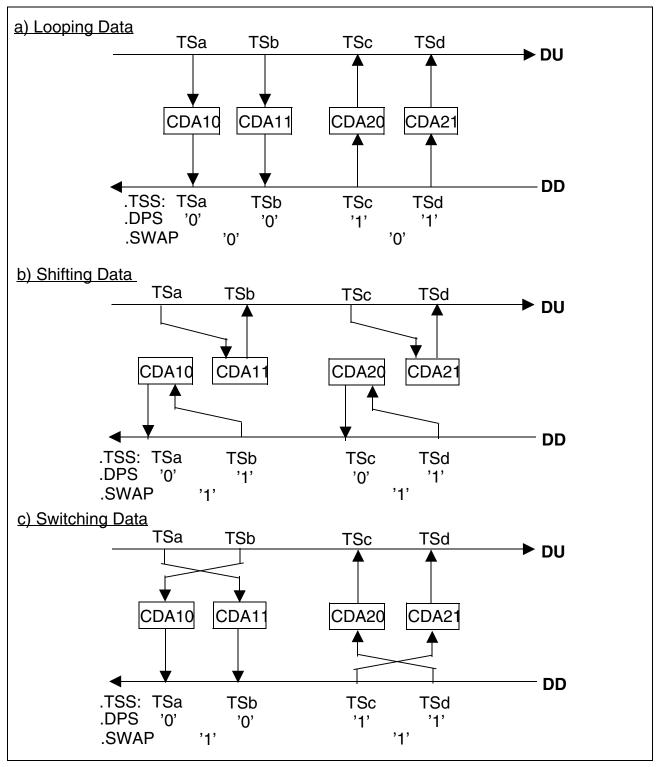

| 17.1.2.1<br>17.1.3<br>17.1.4                                   | Looping and Shifting Data                                                                                                                                           | 279<br>280               |

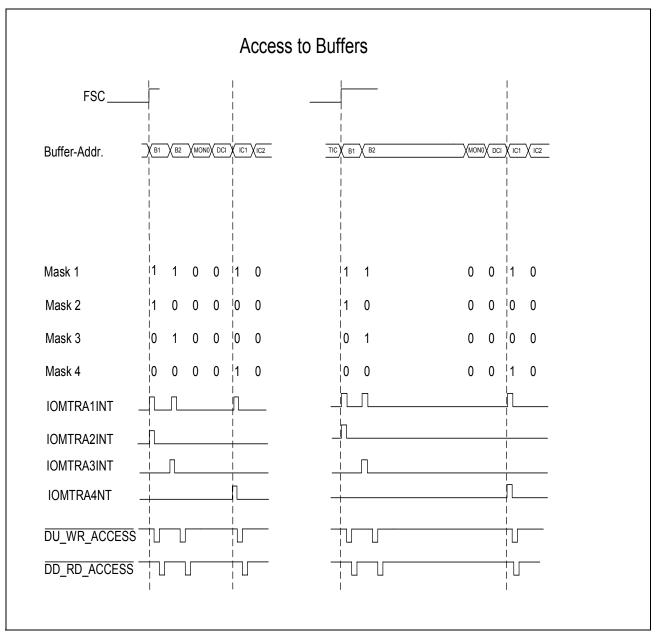

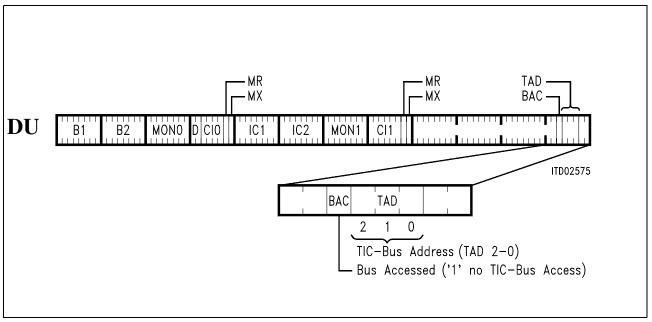

| 17.1.5<br>17.1.5.1<br>17.1.6                                   | Data transfer from and to the IOM-2 busData Access on IOM-2Compare Feature for transfer unit 0                                                                      | 283                      |

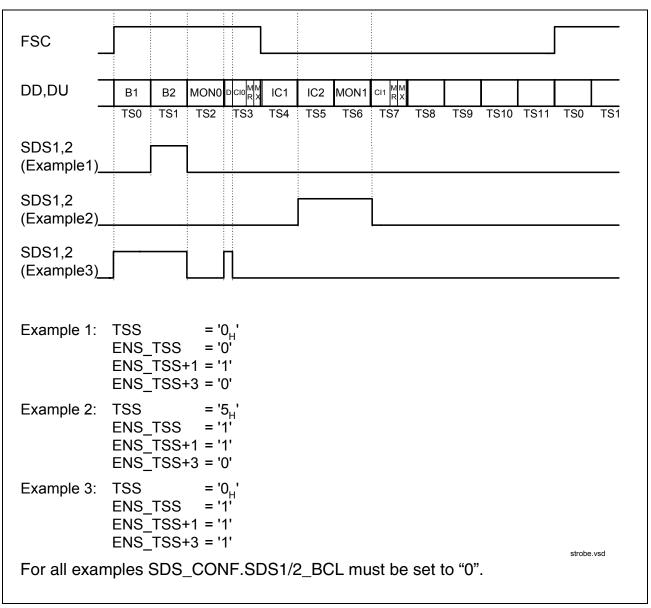

| 17.1.7<br>17.1.8<br>17.1.8.1                                   | Communication between DSP and IOM-2<br>Serial Data Strobe Signal and strobed Data Clock<br>Serial Data Strobe Signal                                                | 288<br>289               |

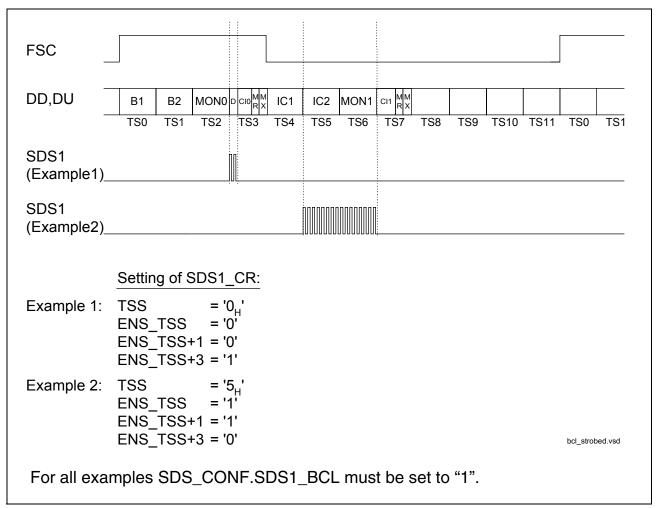

| 17.1.8.2<br>17.1.9<br>17.2                                     | Strobed IOM Bit Clock                                                                                                                                               | 290                      |

| 17.2.1<br>17.2.2<br>17.2.3                                     | Overview                                                                                                                                                            | 291<br>292               |

| 17.2.3<br>17.2.4<br>17.3                                       | CIC Interrupt Logic                                                                                                                                                 | 293<br>295               |

| 17.3.1<br>17.3.2<br>17.3.3                                     | Overview                                                                                                                                                            | 295                      |

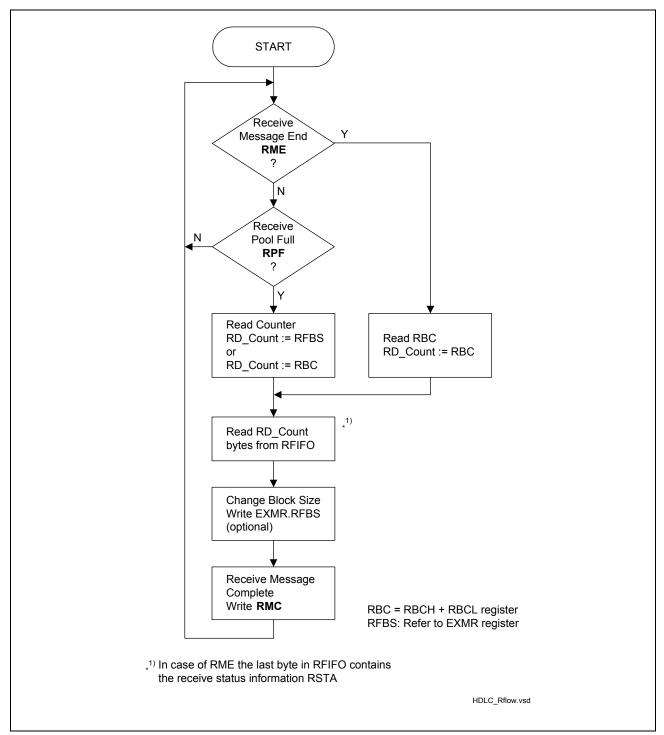

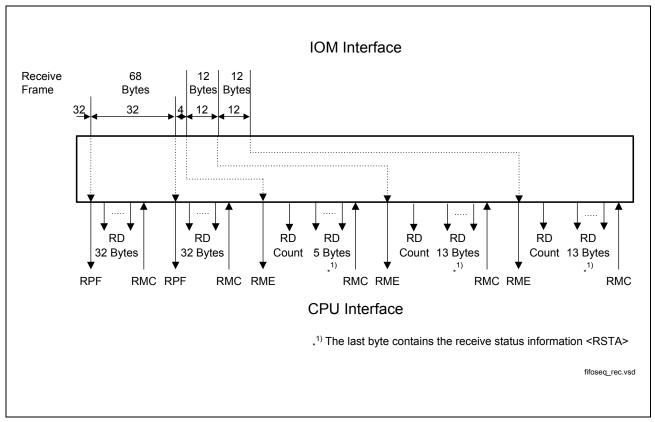

| 17.3.3.1<br>17.3.3.2                                           | General Description Possible Error Conditions during Reception of Frames                                                                                            | 298<br>301               |

| 17.3.3.3<br>17.3.4                                             | Data Reception Procedure       Receive Frame Structure                                                                                                              |                          |

#### **Table of Contents**

17.3.5

#### **Table of Contents**

#### Page

|           |                                                         | •   |

|-----------|---------------------------------------------------------|-----|

| 17.3.5.1  | General Description                                     |     |

| 17.3.5.2  | Possible Error Conditions during Transmission of Frames |     |

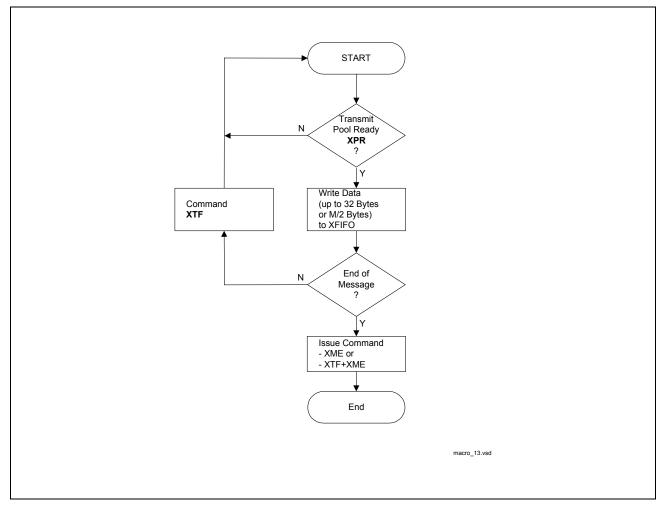

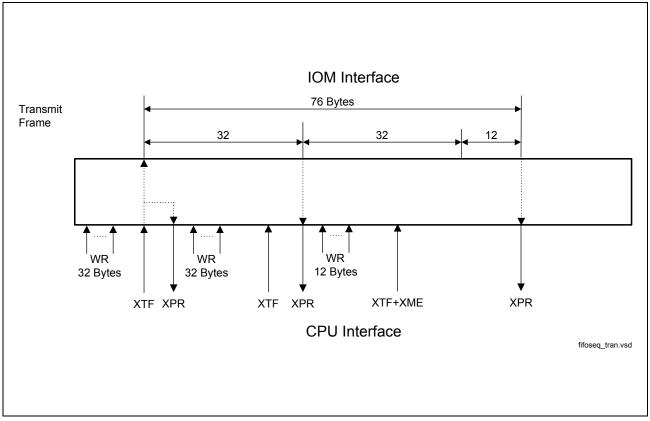

| 17.3.5.3  | Data Transmission Procedure                             | 307 |

| 17.3.5.4  | Transmit Frame Structure                                |     |

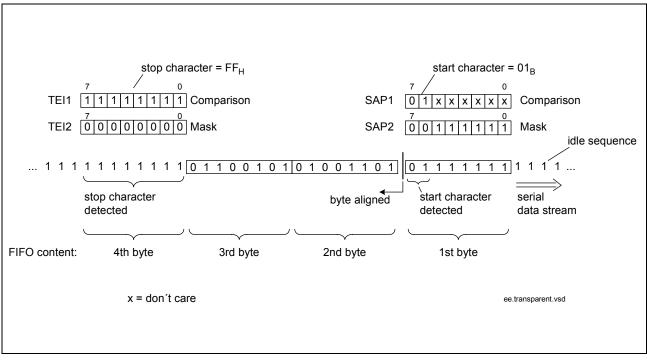

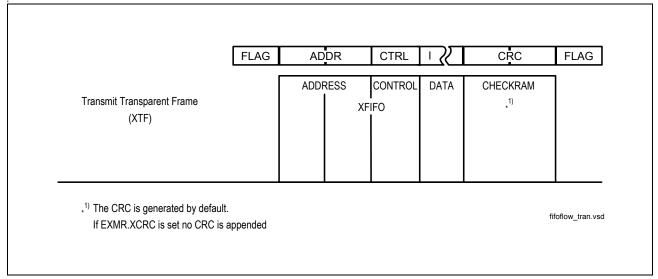

| 17.3.6    | Extended Transparent Mode                               | 310 |

| 17.3.6.1  | Transmitter                                             | 310 |

| 17.3.6.2  | Receiver                                                | 310 |

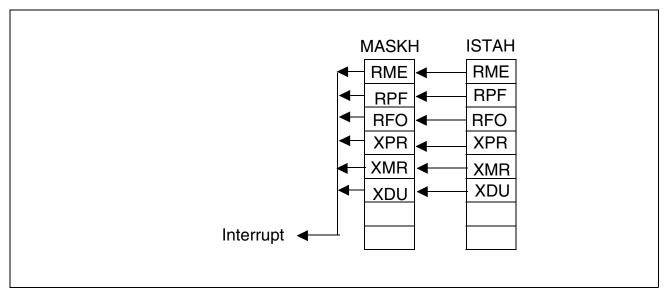

| 17.4      | HDLC Controller Interrupts                              | 311 |

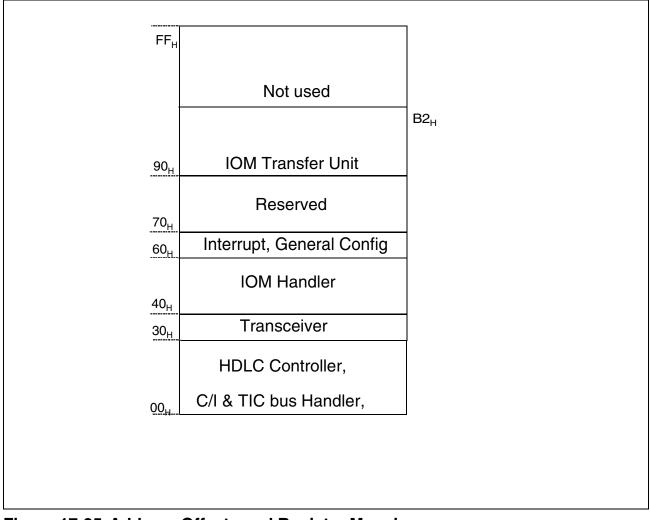

| 17.5      | Register Description                                    | 312 |

| 17.5.1    | HDLC Control and C/I Registers                          | 318 |

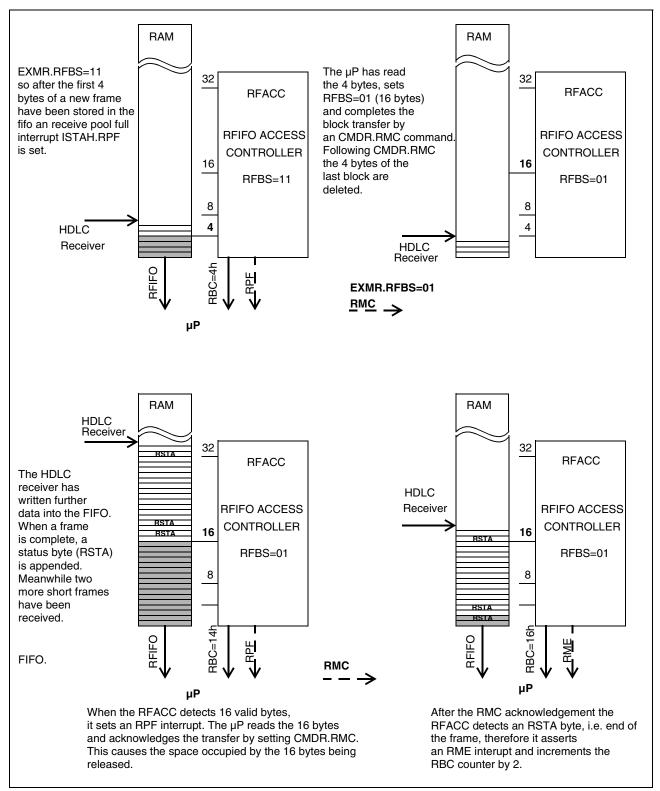

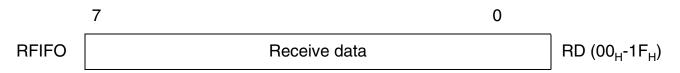

| 17.5.1.1  | RFIFO - Receive FIFO                                    | 318 |

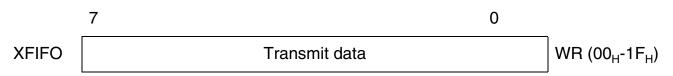

| 17.5.1.2  | XFIFO - Transmit FIFO                                   | 318 |

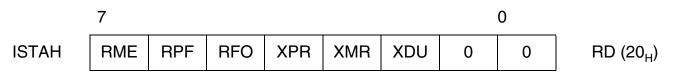

| 17.5.1.3  | ISTAH - Interrupt Status Register HDLC                  |     |

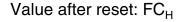

| 17.5.1.4  | MASKH - Mask Register HDLC                              | 320 |

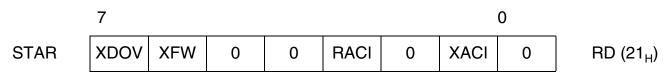

| 17.5.1.5  | STAR - Status Register                                  | 320 |

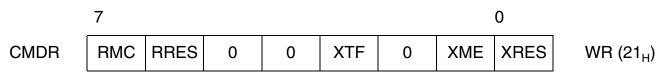

| 17.5.1.6  | CMDR - Command Register                                 |     |

| 17.5.1.7  | MODEH - Mode Register                                   |     |

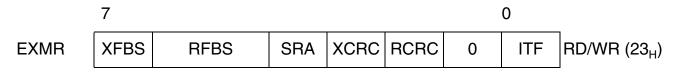

| 17.5.1.8  | EXMR- Extended Mode Register                            |     |

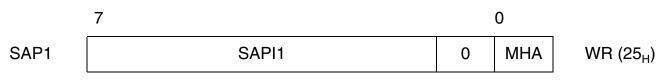

| 17.5.1.9  | SAP1 - SAPI1 Register                                   |     |

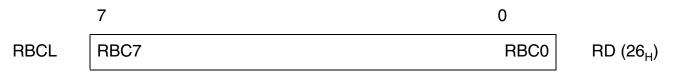

| 17.5.1.10 |                                                         |     |

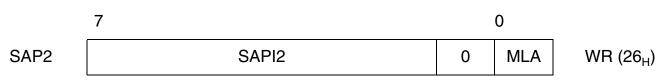

| 17.5.1.11 | SAP2 - SAPI2 Register                                   |     |

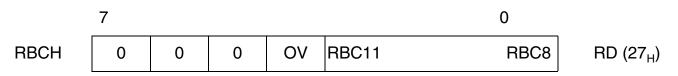

| 17.5.1.12 | U U U U U U U U U U U U U U U U U U U                   |     |

| 17.5.1.13 |                                                         |     |

| 17.5.1.14 | 5                                                       |     |

| 17.5.1.15 | -                                                       |     |

| 17.5.1.16 | Ū                                                       |     |

| 17.5.1.17 | -                                                       |     |

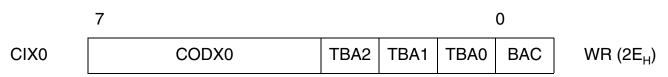

| 17.5.1.18 | CIX0 - Command/Indication Transmit 0                    |     |

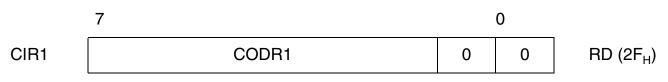

| 17.5.1.19 | CIR1 - Command/Indication Receive 1                     |     |

| 17.5.1.20 | CIX1 - Command/Indication Transmit 1                    |     |

| 17.5.2    | IOM Handler (CDA) Register                              |     |

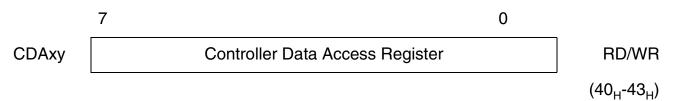

| 17.5.2.1  | CDAxy - Controller Data Access Register xy              |     |

| 17.5.2.2  | XXX_TSDPxy - Time Slot and Data Port Selection for CHxy |     |

| 17.5.2.3  | CDAx_CR - Control Register Controller Data Access CH1x  |     |

| 17.5.3    | IOM Handler (Control register)                          |     |

| 17.5.3.1  | TR_CR - Control Register Transceiver Data               |     |

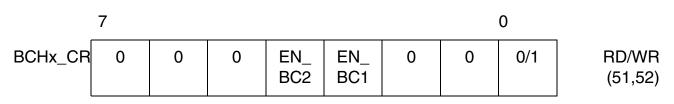

| 17.5.3.2  | BCHx_CR - Control Register B-Channel Data               |     |

| 17.5.3.3  | DCI_CR - Control Register for HDLC and Cl1 Data         |     |

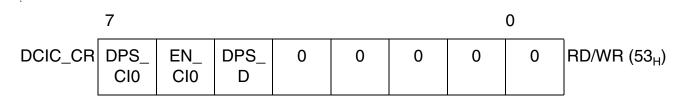

| 17.5.3.4  | DCIC_CR - Control Register for HDLC and Cl1 Data        |     |

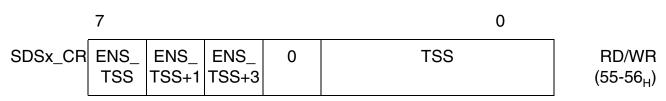

| 17.5.3.5  | SDSx_CR - Control Register Serial Data Strobe x         |     |

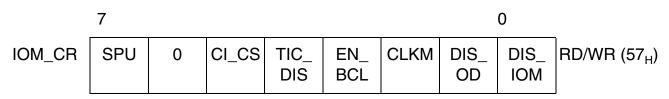

| 17.5.3.6  | IOM_CR - Control Register IOM Data                      |     |

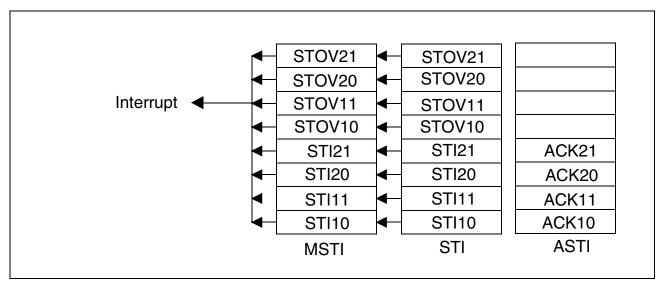

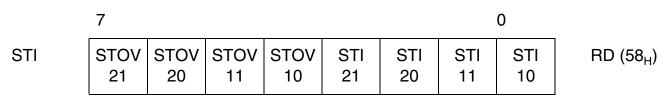

| 17.5.3.7  | STI - Synchronous Transfer Interrupt                    |     |

|           |                                                         | 000 |

#### **Table of Contents**

#### Page

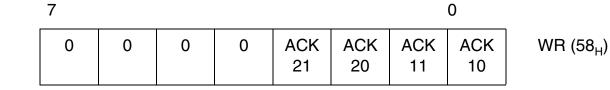

| 17.5.3.8       ASTI - Acknowledge Synchronous Transfer Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

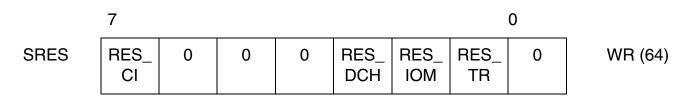

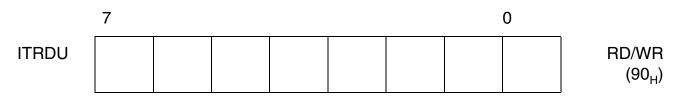

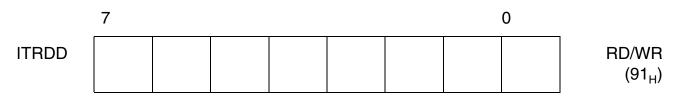

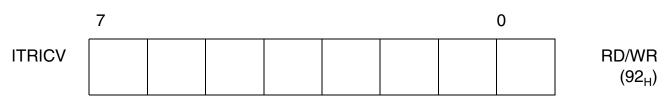

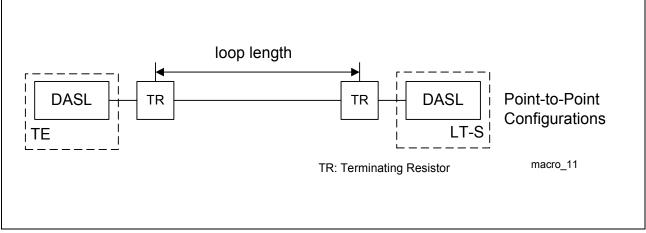

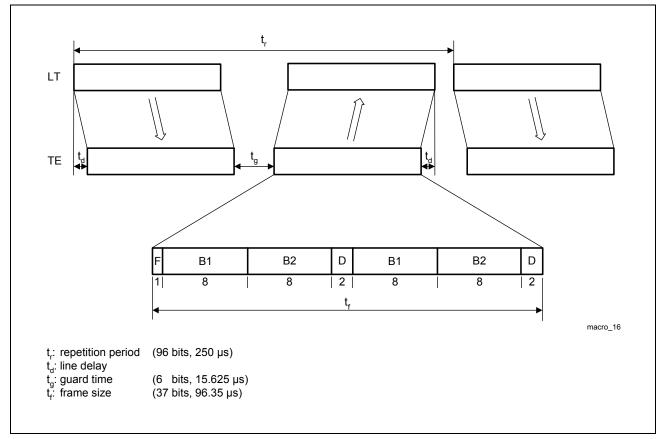

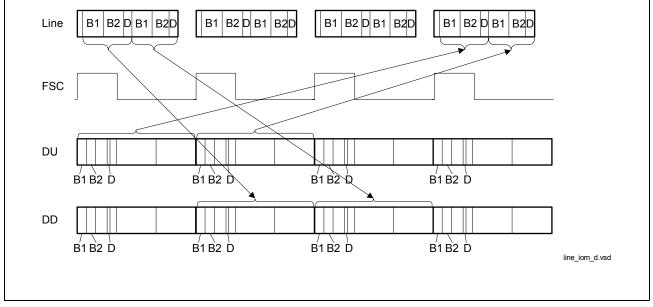

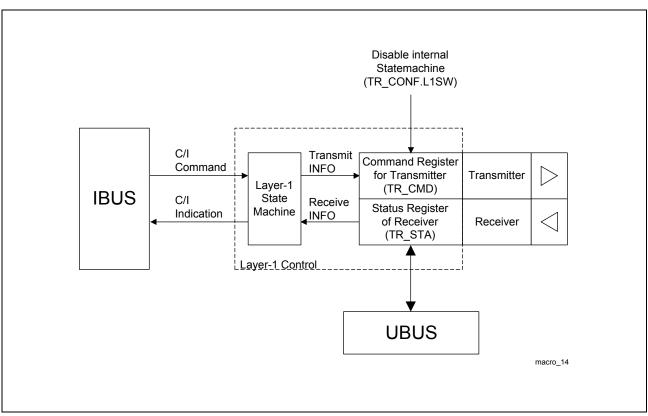

| 17.5.3.10       SDS_CONF - Configuration Register for Serial Data Strobes       341         17.5.3.11       MCDA - Monitoring CDA Bits       341         17.6       Interrupt and General Configuration       341         17.6.1       ISTA - Interrupt Status Register       341         17.6.2       MASK - Mask Register       341         17.6.3       MODE1 - Mode1 Register       342         17.6.4       ID - Identification Register       343         17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.3       ITRICV - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Control Register Register       345         17.6.6.3       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.4       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.7       IWSR - IOM waitstates register       347         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL Interfacee       349          |

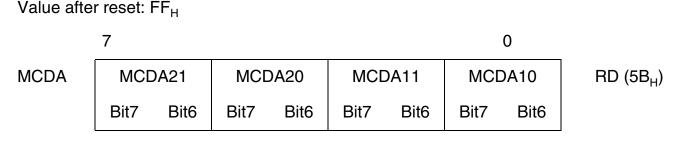

| 17.5.3.11       MCDA - Monitoring CDA Bits       341         17.6       Interrupt and General Configuration       341         17.6.1       ISTA - Interrupt Status Register       341         17.6.2       MASK - Mask Register       342         17.6.3       MODE1 - Mode1 Register       343         17.6.4       ID - Identification Register       343         17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Control Register Register       345         17.6.6.3       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.4       ITR_CR - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.5       ITR_MSK0 - IOM Variaster register       347         17.6.6.7       IWSR - IOM waitstates register       347         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL Interfacee       349         18.4 <td< td=""></td<>       |

| 17.6       Interrupt and General Configuration       341         17.6.1       ISTA - Interrupt Status Register       341         17.6.2       MASK - Mask Register       342         17.6.3       MODE1 - Mode1 Register       343         17.6.4       ID - Identification Register       343         17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.4       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.6       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL Interface       350         18.4       Control of Layer 1 / State Machine       353         18.4.1       States       353         18.4.1.2          |

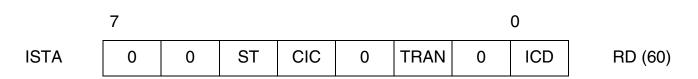

| 17.6.1       ISTA - Interrupt Status Register       341         17.6.2       MASK - Mask Register       342         17.6.3       MODE1 - Mode1 Register       343         17.6.4       ID - Identification Register       343         17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.4       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.6       ITR_MSKx - IOM waitstates register       347         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL Interfacee       349         18.4       Control of Layer 1 / State Machine       353         18.4.1       States       353         18.4.1.2       C/I Commands       357         18.4.1.3       C/I Commands       357                            |

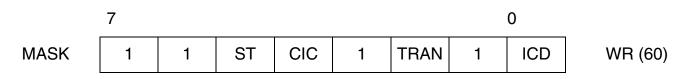

| 17.6.2       MASK - Mask Register       342         17.6.3       MODE1 - Mode1 Register       343         17.6.4       ID - Identification Register       343         17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.4       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       345         17.6.6.6       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         18.1       Wiring Configurations       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL interfacee       349         18.4       Control of Layer 1 / State Machine       353         18.4.1.1       States       353         18.4.1.2       C/I Commands       357         18.4.1.3       C/I commands       357         18.4.1.4       Receive Inf                   |

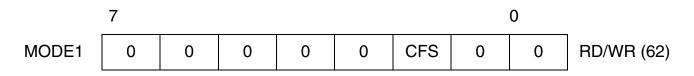

| 17.6.3       MODE1 - Mode1 Register       343         17.6.4       ID - Identification Register       343         17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Units)       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Control Register Register       345         17.6.6.4       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.6       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL interfacee       349         18.3       Data Transfer and Delay between IBUS and DASL Interface       353         18.4.1       State Machine       351         18.4.1.2       C/I Commands       355         18.4.1.3       States       353         18.4.1.4       Receive Infos on the Line (Downstream)       357         18.4.1.5       Tra                   |

| 17.6.4       ID - Identification Register       343         17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.4       ITR_MSK0 - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.6       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL interfacee       349         18.3       Data Transfer and Delay between IBUS and DASL Interface       350         18.4.1       State Machine       353         18.4.1       State Machine       353         18.4.1.2       C/I Commands       357         18.4.1.3       C/I Codes       358         <      |

| 17.6.5       SRES - Software Reset Register       344         17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Control Register Register       345         17.6.6.4       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.6       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL interface       349         18.3       Data Transfer and Delay between IBUS and DASL Interface       350         18.4.1       State Machine       353         18.4.1       State Machine       353         18.4.1.2       C/I Commands       357         18.4.1.3       C/I Indications       357         18.4.1.4       Receive Infos on the Line (Downstream)       358 |

| 17.6.6       IOM Handler (Transfer Units)       344         17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Idle Code Value for transfer unit 0       345         17.6.6.3       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.4       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.5       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         17.6.6.7       IWSR - IOM waitstates register       349         18.1       Line Transceiver       349         18.2       Line Coding, Frame Structure of the DASL interfacee       349         18.3       Data Transfer and Delay between IBUS and DASL Interface       350         18.4       Control of Layer 1 / State Machine       351         18.4.1       State Machine       353         18.4.1.1       States       353         18.4.1.2       C/I Commands       357         18.4.1.3       C/I Indications       357         18.4.1.4       Receive Infos on the Line (Downstream)       358         18.4.2       C/I Codes       358               |

| 17.6.6.1       ITRDU - IOM Transfer Unit, Read/Write Register DU       344         17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Idle Code Value for transfer unit 0       345         17.6.6.4       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.6       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         17.6.6.7       IWSR - IOM waitstates register       349         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL interfacee       349         18.3       Data Transfer and Delay between IBUS and DASL Interface       350         18.4       Control of Layer 1 / State Machine       351         18.4.1       State Machine       353         18.4.1.2       C/I Commands       357         18.4.1.3       C/I Indications       357         18.4.1.4       Receive Infos on the Line (Downstream)       358         18.4.2       C/I Codes       358         18.5       Level Detection and Power Down       359      |

| 17.6.6.2       ITRDD - IOM Transfer Unit, Read/Write Register DD       345         17.6.6.3       ITRICV - IOM Transfer Unit, Idle Code Value for transfer unit 0       345         17.6.6.4       ITR_CR - IOM Transfer Control Register Register       345         17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0       346         17.6.6.6       ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7       347         17.6.6.7       IWSR - IOM waitstates register       349         18       Line Transceiver       349         18.1       Wiring Configurations       349         18.2       Line Coding, Frame Structure of the DASL interfacee       349         18.3       Data Transfer and Delay between IBUS and DASL Interface       350         18.4       Control of Layer 1 / State Machine       353         18.4.1       States       353         18.4.1.2       C/I Commands       357         18.4.1.3       C/I Indications       357         18.4.1.4       Receive Infos on the Line (Upstream)       358         18.4.2       C/I Codes       358         18.5       Level Detection and Power Down       359                                                                                                  |

| 17.6.6.3ITRICV - IOM Transfer Unit, Idle Code Value for transfer unit 0 34517.6.6.4ITR_CR - IOM Transfer Control Register Register 34517.6.6.5ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0 34617.6.6.6ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 7 34717.6.6.7IWSR - IOM waitstates register 34918Line Transceiver 34918.1Wiring Configurations 34918.2Line Coding, Frame Structure of the DASL interfacee 34918.3Data Transfer and Delay between IBUS and DASL Interface 35018.4Control of Layer 1 / State Machine 35318.4.1.1States 35318.4.1.2C/I Commands 35718.4.1.3C/I Indications 35718.4.1.4Receive Infos on the Line (Downstream) 35718.4.1.5Transmit Infos on the Line (Upstream) 35818.4.2C/I Codes 35818.5Level Detection and Power Down 359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17.6.6.4ITR_CR - IOM Transfer Control Register Register34517.6.6.5ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0 34617.6.6.6ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 717.6.7IWSR - IOM waitstates register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17.6.6.4ITR_CR - IOM Transfer Control Register Register34517.6.6.5ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0 34617.6.6.6ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 717.6.7IWSR - IOM waitstates register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17.6.6.5       ITR_MSK0 - IOM Transfer Time Slot and Data Port Sel. Reg. 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17.6.6.6ITR_MSKx - IOM Transfer Time Slot and Data Port Sel. Reg. 1 - 734717.6.6.7IWSR - IOM waitstates register34918Line Transceiver34918.1Wiring Configurations34918.2Line Coding, Frame Structure of the DASL interfacee34918.3Data Transfer and Delay between IBUS and DASL Interface35018.4Control of Layer 1 / State Machine35118.4.1States35318.4.1.2C/I Commands35618.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35718.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17.6.6.7IWSR - IOM waitstates register34718Line Transceiver34918.1Wiring Configurations34918.2Line Coding, Frame Structure of the DASL interfacee34918.3Data Transfer and Delay between IBUS and DASL Interface35018.4Control of Layer 1 / State Machine35118.4.1State Machine35318.4.1.1States35318.4.1.2C/I Commands35718.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18Line Transceiver34918.1Wiring Configurations34918.2Line Coding, Frame Structure of the DASL interfacee34918.3Data Transfer and Delay between IBUS and DASL Interface35018.4Control of Layer 1 / State Machine35118.4.1States35318.4.1.2C/I Commands35618.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35718.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18.1Wiring Configurations34918.2Line Coding, Frame Structure of the DASL interface34918.3Data Transfer and Delay between IBUS and DASL Interface35018.4Control of Layer 1 / State Machine35118.4.1State Machine35318.4.1.1States35318.4.1.2C/I Commands35618.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35818.4.2C/I Codes35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18.2Line Coding, Frame Structure of the DASL interfacee34918.3Data Transfer and Delay between IBUS and DASL Interface35018.4Control of Layer 1 / State Machine35118.4.1State Machine35318.4.1.1States35318.4.1.2C/I Commands35618.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35718.4.1.5Transmit Infos on the Line (Upstream)35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 18.3Data Transfer and Delay between IBUS and DASL Interface35018.4Control of Layer 1 / State Machine35118.4.1State Machine35318.4.1.1States35318.4.1.2C/I Commands35618.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35718.4.1.5Transmit Infos on the Line (Upstream)35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

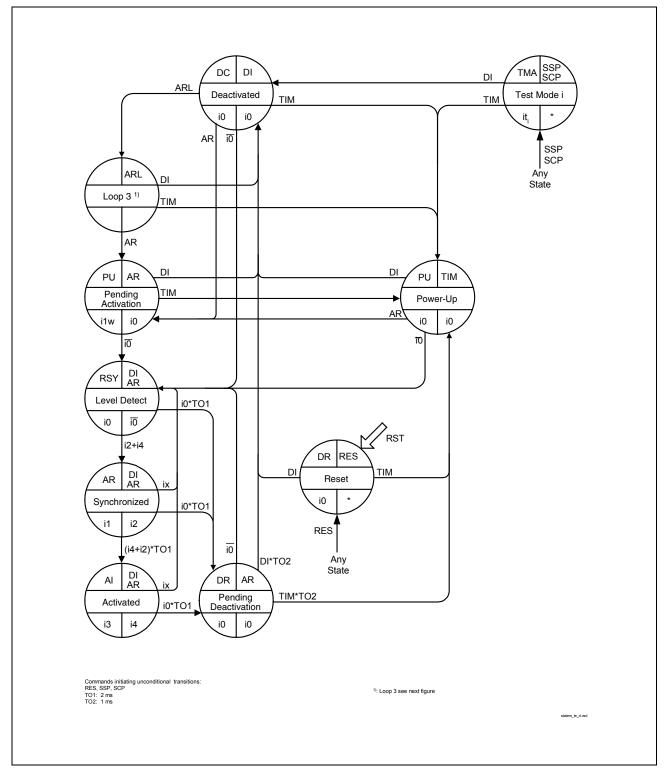

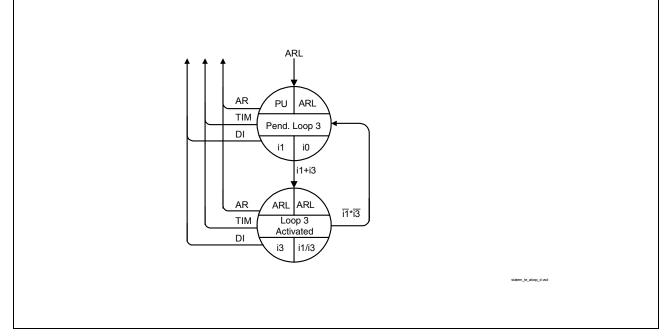

| 18.4       Control of Layer 1 / State Machine       351         18.4.1       State Machine       353         18.4.1.1       States       353         18.4.1.2       C/I Commands       356         18.4.1.3       C/I Indications       357         18.4.1.4       Receive Infos on the Line (Downstream)       357         18.4.1.5       Transmit Infos on the Line (Upstream)       358         18.4.2       C/I Codes       358         18.5       Level Detection and Power Down       359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

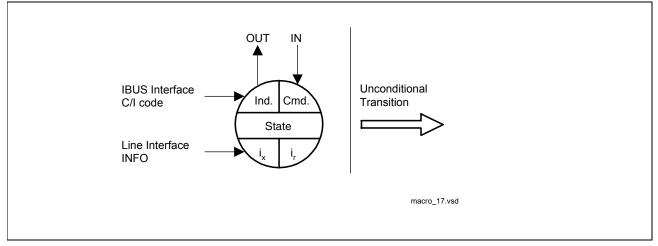

| 18.4.1       State Machine       353         18.4.1.1       States       353         18.4.1.2       C/I Commands       356         18.4.1.3       C/I Indications       357         18.4.1.4       Receive Infos on the Line (Downstream)       357         18.4.1.5       Transmit Infos on the Line (Upstream)       358         18.4.2       C/I Codes       358         18.5       Level Detection and Power Down       359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18.4.1.1       States       353         18.4.1.2       C/I Commands       356         18.4.1.3       C/I Indications       357         18.4.1.4       Receive Infos on the Line (Downstream)       357         18.4.1.5       Transmit Infos on the Line (Upstream)       358         18.4.2       C/I Codes       358         18.5       Level Detection and Power Down       359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18.4.1.2C/I Commands35618.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35718.4.1.5Transmit Infos on the Line (Upstream)35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18.4.1.3C/I Indications35718.4.1.4Receive Infos on the Line (Downstream)35718.4.1.5Transmit Infos on the Line (Upstream)35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18.4.1.4Receive Infos on the Line (Downstream)35718.4.1.5Transmit Infos on the Line (Upstream)35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 18.4.1.5Transmit Infos on the Line (Upstream)35818.4.2C/I Codes35818.5Level Detection and Power Down359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18.4.2       C/I Codes       358         18.5       Level Detection and Power Down       359                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.5Level Detection and Power Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

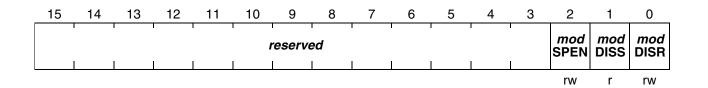

| 18.6 Transceiver Enable/Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18.7 Test Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18.7.1 Line Transceiver Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.7.2 Test Signals on the Line Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 18.8 Receive PLL (DPLL-Adjust Unit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18.9 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

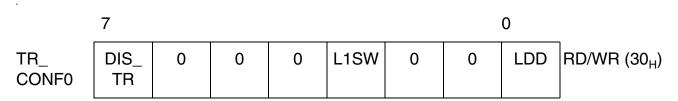

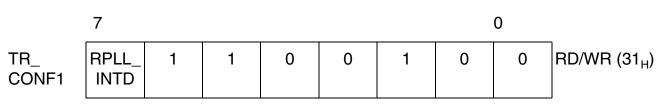

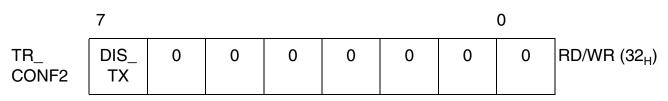

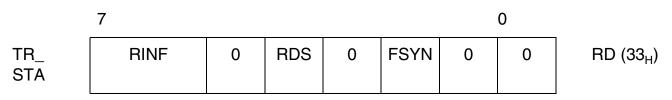

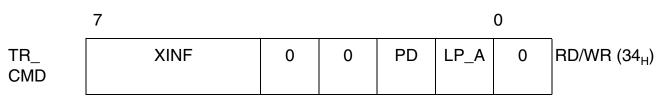

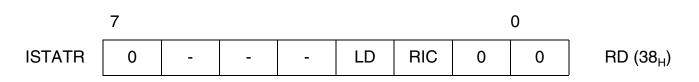

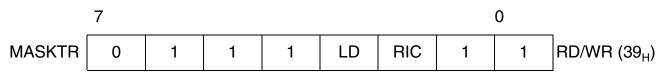

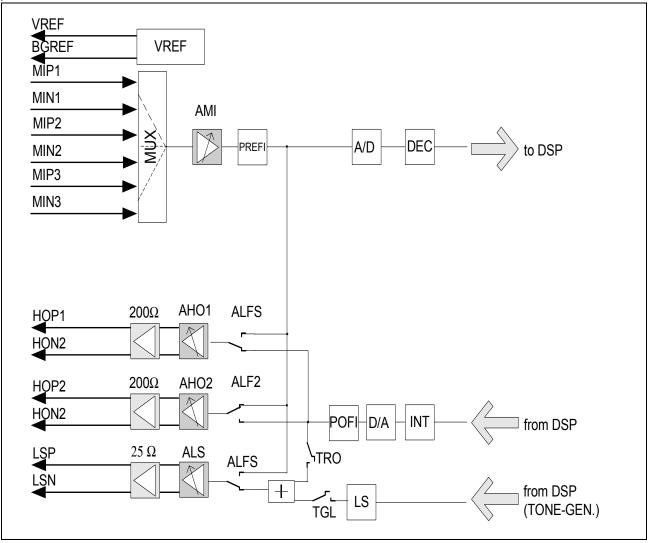

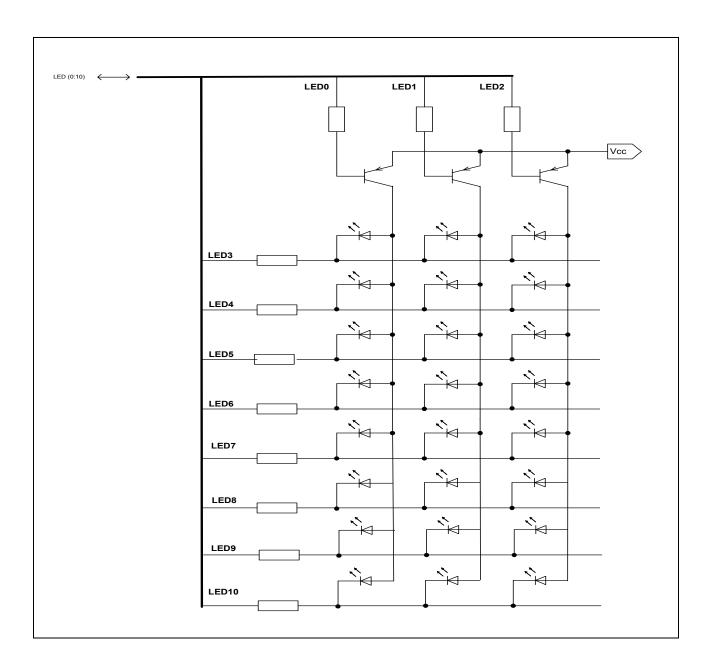

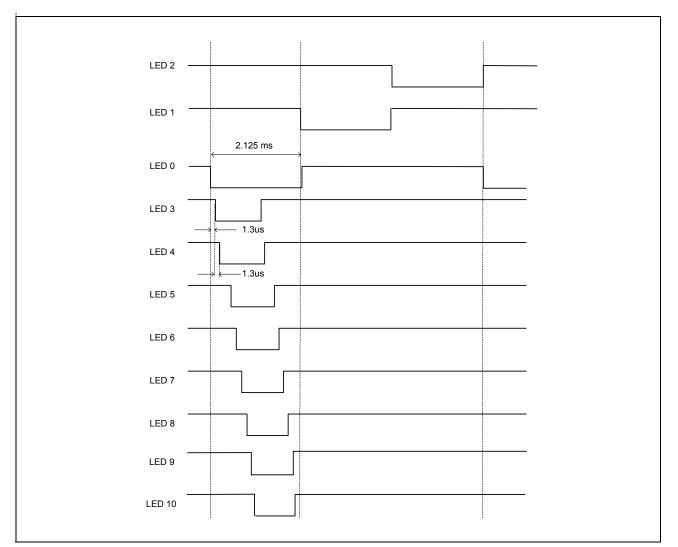

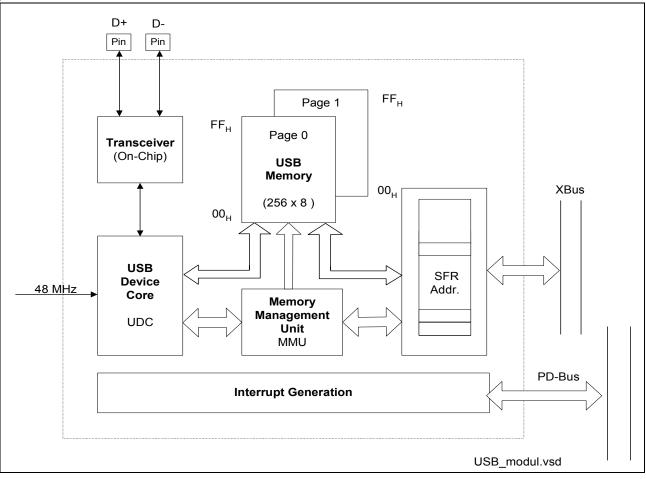

| 18.9.1 TR_CONF0 - Transceiver Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |