Datacom

#### Edition 2001-02

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81669 München, Germany © Infineon Technologies AG 2/19/01. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

QuadLIU™ Quad Line Interface Unit for E1/T1/J1 PEB 22504 Version 1.1

Datacom

#### PEB 22504

| Revision History: |                        | 2001-02                             | DS4 |  |  |

|-------------------|------------------------|-------------------------------------|-----|--|--|

| Previous Version: |                        | Data Sheet, DS3, 2000-09            |     |  |  |

| Page              | Subjects               | (major changes since last revision) |     |  |  |

|                   | 5 V supp               | ly mode is not supported            |     |  |  |

| 7                 | e-mail ad              | Idress changed                      |     |  |  |

| 60                | Global C               | onfiguration Register               |     |  |  |

| 99                | Power St               | Power Supply Range                  |     |  |  |

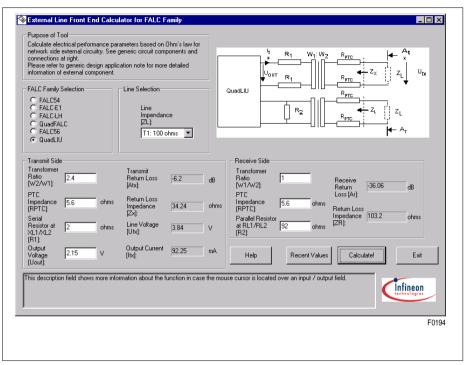

| 121               | External               | External Line Frontend Calculator   |     |  |  |

| 100               | Transmit               | Transmiter output current           |     |  |  |

| 101               | 1 Receiver sensitivity |                                     |     |  |  |

|                   |                        |                                     |     |  |  |

|                   |                        |                                     |     |  |  |

|                   |                        |                                     |     |  |  |

|                   |                        |                                     |     |  |  |

|                   |                        |                                     |     |  |  |

For questions on technology, delivery, and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

# **Preface**

The Quad Line Interface Unit PEB 22504 (QuadLIU™) is a flexible line interface unit for a wide area of telecommunication and data communication applications. The device contains four complete channels on one chip to save board space and power consumption. This document provides complete reference information to configure E1, T1, and J1 applications.

#### **Organization of this Document**

This Data Sheet is organized as follows:

#### Chapter 1. Overview

Gives a general description of the product and its family, lists the key features, and presents some typical applications.

### · Chapter 2, Pin Descriptions

Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

# • Chapter 3, Functional Description

This chapter describes the functional blocks and principal operation modes.

### • Chapter 4, Interface Description

Describes the various device interfaces.

### • Chapter 5. Operational Description

Shows the operation modes and how they are to be initialized.

### · Chapter 6, Register Description

Gives a detailed description of all implemented registers and how to use them in different applications/configurations.

### Chapter 7, Electrical Characteristics

Specifies maximum ratings, DC and AC characteristics.

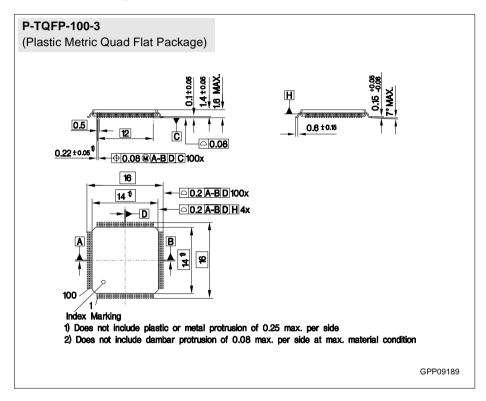

### Chapter 8, Package Outlines

Shows the mechanical values of the device package.

### Chapter 9, Appendix

Gives an example for overvoltage protection and information about application notes and other support.

- Chapter 10, Glossary

- Index

#### **Related Documentation**

This document refers to the following international standards (in alphabetical/numerical order):

ANSI/EIA-656 (page 119) ANSI T1.102 (page 115)

ANSI T1.231 (page 71, page 89, page 90)

ANSI T1.403 (page 50, page 90)

AT&T TR43802 (page 40)

AT&T TR62411 (page 40, page 44, page 49)

ESD Ass. Standard EOS/ESD-5.1-1993

(page 98)

ETSI ETS 300 011 (page 40)

ETSI ETS 300 233 (page 39, page 40, page 89)

ETSI TBR12 (page 40, page 42) ETSI TBR13 (page 40, page 42)

FCC68 (page 47)

IEEE 1149.1 (page 33)

ITU-T G.703 (page 40)

ITU-T G.736-739 (page 40)

ITU-T G.775 (page 39, page 39, page 89, page 89)

ITU-T G.823 (page 40) ITU-T G.824 (page 40)

ITU-T I.431 (page 40, page 42, page 44, page 47)

MIL-Std. 883D (page 98)

Telcordia TR-NWT-1089

TR-TSY 009 (page 40)

TR-TSY 253 (page 40)

TR-TSY 499 (page 40)

UL 1459

#### **Your Comments**

(DS4).

We welcome your comments on this document. We are continuously trying improving our documentation. Please send your remarks and suggestions by e-mail to

$com.docu\_comments@infineon.com$

Please provide in the *subject* of your e-mail: device name (QuadLIU<sup>™</sup>), device number (PEB 22504), device version (Version 1.1), and in the *body* of your e-mail: document type (Data Sheet), issue date (2001-02) and document revision number

| Table of                                                    | f Contents                                                                                                                                                                                        | Page                 |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1<br>1.1<br>1.2<br>1.3                                      | Overview . Features . Logic Symbol . Typical Applications                                                                                                                                         | 13                   |

| <b>2</b><br>2.1<br>2.2                                      | Pin Descriptions         Pin Diagram         Pin Definitions and Functions                                                                                                                        | 18                   |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3           | Functional Description Functional Overview Block Diagram Functional Blocks Microprocessor Control Unit Boundary Scan Unit Master Clocking Unit                                                    | 28<br>29<br>30<br>30 |

| <b>4</b><br>4.1                                             | Interface Description                                                                                                                                                                             | 36                   |

| 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7 | Receive Line Interface Short-haul/Long-haul Interface Receive Equalization Network Receive Line Attenuation Indication Receive Clock and Data Recovery Receive Line Coding Pulse-Density Detector | 36<br>37<br>38<br>38 |

| 4.1.8<br>4.1.9<br>4.1.10<br>4.1.11                          | Alarm Handling Jitter Attenuator Jitter Tolerance Output Jitter                                                                                                                                   | 40                   |

| 4.1.12<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3                    | Elastic Buffer Transmitter Transmit Line Interface Transmit Clock System Pulse-Density Enforcer                                                                                                   | 44<br>45<br>45       |

| 4.2.4<br>4.2.5<br>4.3                                       | Programmable Pulse Shaper and Line Build-Out Transmit Line Monitor Framer Interface                                                                                                               | 47<br>48             |

| 4.4<br>4.4.1<br>4.4.2<br>4.4.3                              | Maintenance Functions Error Counter One-Second Timer Pseudo-Random Bit Sequence Generation and Monitor                                                                                            | 49<br>49<br>49       |

| 4.4.4<br>4.4.5                                              | In-Band Loop Generation and Detection                                                                                                                                                             | 50                   |

| Table of                                                        | Contents                                                                                                                                                                                                                                                                                         | Page                                                                                          |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 4.4.6<br>4.4.7<br>4.4.8<br>4.4.9                                | Local Loop Digital Loop Alarm Simulation Transmit Data Performance Monitoring                                                                                                                                                                                                                    | 53<br>54                                                                                      |

| 5<br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2                        | Operational Description Operational Overview Device Reset Device Initialization Reset Values Basic Initialization Settings                                                                                                                                                                       | 56<br>56<br>56<br>56                                                                          |

| 6<br>6.1<br>6.2<br>6.3<br>6.4                                   | Register Description Control Register Addresses Detailed Description of Control Registers Status Register Addresses Detailed Description of Status Registers                                                                                                                                     | 59<br>60<br>88                                                                                |

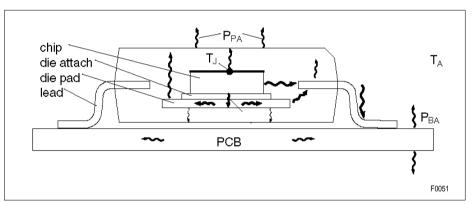

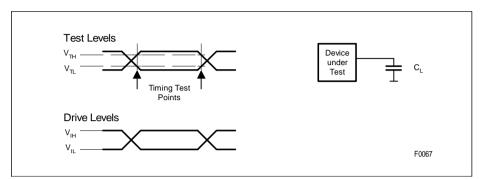

| 7.1 7.2 7.3 7.4 7.4.1 7.4.2 7.4.3 7.4.4 7.4.5 7.4.6 7.5 7.6 7.7 | Electrical Characteristics Absolute Maximum Ratings Operating Range DC Characteristics AC Characteristics Master Clock Timing JTAG Boundary Scan Interface Reset Microprocessor Interface Framer Interface Pulse Templates - Transmitter Capacitances Package Characteristics Test Configuration | . 98<br>. 99<br>. 100<br>. 103<br>. 104<br>. 105<br>. 105<br>. 110<br>. 114<br>. 116<br>. 116 |

| 8                                                               | Package Outlines                                                                                                                                                                                                                                                                                 | . 118                                                                                         |

| <b>9</b><br>9.1<br>9.2                                          | Appendix Application Notes Software Support                                                                                                                                                                                                                                                      | . 119                                                                                         |

| 10                                                              | Glossary                                                                                                                                                                                                                                                                                         | . 122                                                                                         |

| List of Figu | ures                                                | Page |

|--------------|-----------------------------------------------------|------|

| Figure 1     | Logic Symbol                                        | 15   |

| Figure 2     | QuadLIU Application                                 | 16   |

| Figure 3     | QuadLIU Repeater Application                        |      |

| Figure 4     | Pin Configuration                                   | 18   |

| Figure 5     | Block Diagram                                       | 29   |

| Figure 6     | Interrupt Status Registers                          |      |

| Figure 7     | Block Diagram of Test Access Port and Boundary Scan |      |

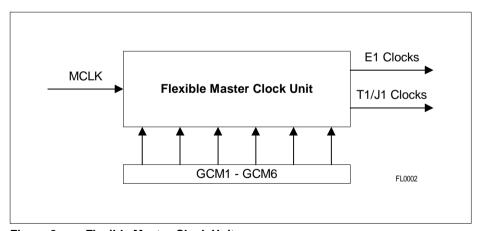

| Figure 8     | Flexible Master Clock Unit                          |      |

| Figure 9     | Receiver Configuration                              |      |

| Figure 10    | Receive Clock System                                |      |

| Figure 11    | Jitter Attenuation Performance                      |      |

| Figure 12    | Jitter Tolerance                                    |      |

| Figure 13    | Transmitter Configuration                           |      |

| Figure 14    | Transmit Clock System                               |      |

| Figure 15    | Transmit Line Monitor Configuration                 |      |

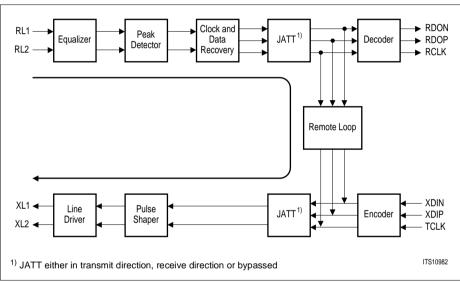

| Figure 16    | Remote Loop Signal Flow                             |      |

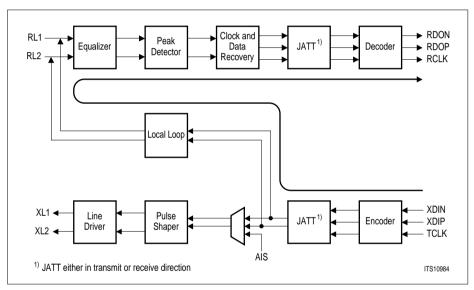

| Figure 17    | Local Loop Signal Flow                              |      |

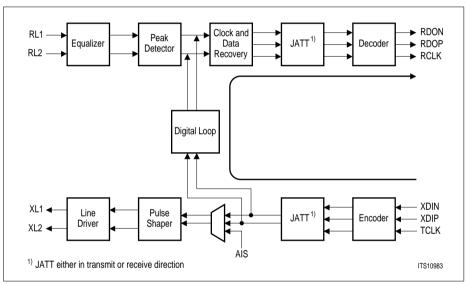

| Figure 18    | Digital Loop Signal FLow                            |      |

| Figure 19    | Transmit Data Performance Monitoring                |      |

| Figure 20    | MCLK Timing                                         |      |

| Figure 21    | JTAG Boundary Scan Timing                           |      |

| Figure 22    | Reset Timing                                        |      |

| Figure 23    | Intel Non-Multiplexed Address Timing                |      |

| Figure 24    | Intel Multiplexed Address Timing                    |      |

| Figure 25    | Intel Read Cycle Timing                             |      |

| Figure 26    | Intel Write Cycle Timing                            |      |

| Figure 27    | Motorola Read Cycle Timing                          |      |

| Figure 28    | Motorola Write Cycle Timing                         |      |

| Figure 29    | TCLK Input Timing                                   |      |

| Figure 30    | RCLK Output Timing                                  |      |

| Figure 31    | SYNC Timing                                         |      |

| Figure 32    | FSC Timing                                          |      |

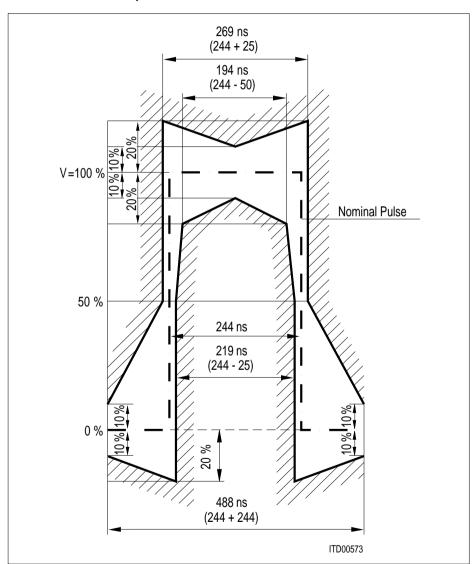

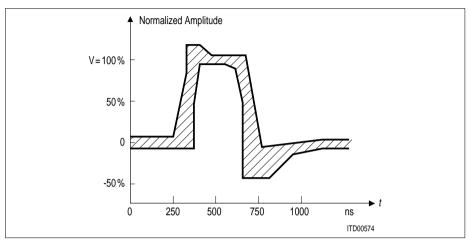

| Figure 33    | E1 Pulse Shape at Transmitter Output                |      |

| Figure 34    | T1 Pulse Shape                                      |      |

| Figure 35    | Thermal Behaviour of Package                        |      |

| Figure 36    | Input/Output Waveforms for AC Testing               |      |

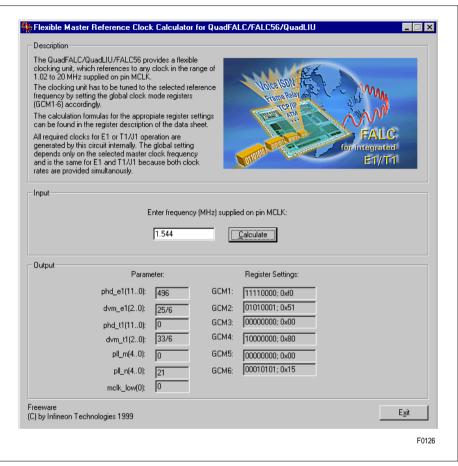

| Figure 37    | Master Clock Frequency Calculator                   |      |

| Figure 38    | External Line Frontend Calculator                   | 121  |

| List of Tab | les                                                       | Page |

|-------------|-----------------------------------------------------------|------|

| Table 1     | Control Pin Functions                                     | 19   |

| Table 2     | Signal Pin Functions                                      | 23   |

| Table 3     | Power Supply Pins                                         | 27   |

| Table 4     | Boundary Scan Pins                                        | 27   |

| Table 5     | Selectable Bus and Microprocessor Interface Configuration | 30   |

| Table 6     | TAP Controller Instruction Codes                          | 34   |

| Table 7     | Examples of External Component Values (Receive)           | 36   |

| Table 8     | Clocking Modes                                            | 41   |

| Table 9     | Output Jitter                                             | 44   |

| Table 10    | Examples of External Component Values (Transmit)          |      |

| Table 11    | Initial Values after Reset                                | 56   |

| Table 12    | Initialization Parameters                                 | 58   |

| Table 13    | Control Register Addresses                                | 59   |

| Table 14    | Pulse Shaper Programming                                  | 77   |

| Table 15    | Clock Mode Register Settings for E1 or T1/J1              | 87   |

| Table 16    | Status Register Addresses                                 | 88   |

| Table 17    | Maximum Ratings                                           | 98   |

| Table 18    | Power Supply Range                                        | 99   |

| Table 19    | DC Parameters                                             | 100  |

| Table 20    | MCLK Timing Parameter Values                              | 103  |

| Table 21    | JTAG Boundary Scan Timing Parameter Values                | 104  |

| Table 22    | Reset Timing Parameter Values                             | 105  |

| Table 23    | Intel Bus Interface Timing Parameter Values               | 107  |

| Table 24    | Motorola Bus Interface Timing Parameter Values            | 109  |

| Table 25    | TCLK Timing Parameter Values                              | 110  |

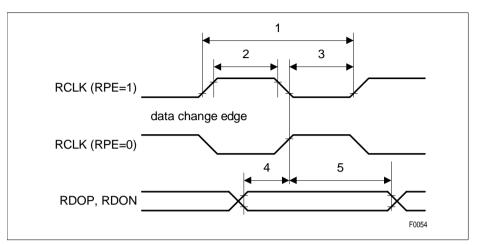

| Table 26    | RCLK Timing Parameter Values                              | 111  |

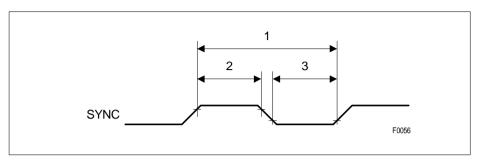

| Table 27    | SYNC Timing Parameter Values                              | 112  |

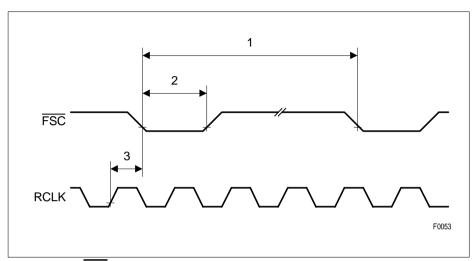

| Table 28    | FSC Timing Parameter Values                               |      |

| Table 29    | T1 Pulse Template (ANSI T1.102)                           | 115  |

| Table 30    | Pin Capacitances                                          |      |

| Table 31    | Package Characteristic Values                             |      |

| Table 32    | AC Test Conditions                                        | 117  |

# 1 Overview

The QuadLIU™ PEB 22504 Quad Line Interface Unit is a device to connect four E1/T1/ J1 framer devices to four analog or digital lines. The line interface is selectable for long-haul or short-haul applications and fulfills the relevant standards for E1, T1, and J1 systems.

The QuadLIU<sup>™</sup> comes in a high-density P-TQFP-100-3 package (SMD) to save a significant amount of board space compared to a configuration using single line-interface circuits.

Crystal-less jitter attenuation with only one master clock source further reduces the amount of required external components.

Equipped with a flexible microcontroller interface, it fits to any control processor environment.

# Quad Line Interface Unit for E1/T1/J1 QuadLIU™

PEB 22504

Version 1.1 CMOS

#### 1.1 Features

- High-density generic interface for all E1/T1/J1 applications

- Quad analog receive and transmit circuitry for longand short-haul applications

- Clock and data recovery using an integrated digital phase-locked loop

- Programmable transmit pulse shapes for E1, T1 and J1 signals

- Maximum line attenuation up to -36 dB at 1024 kHz (E1) and up to -36 dB at 772 kHz (T1/J1)

- · Noise- and crosstalk-filter, line attenuation status

- Programmable Line Build-Out for CSU signals according to ANSI T1.403 and FCC68 0dB, -7.5dB, -15dB, -22.5 dB

- Low transmitter output impedances for high transmit return loss

- · Tristate function of the analog transmit line outputs

- · Transmit line monitor protecting the device from damage

- Jitter specifications of ITU-T I.431, G.703, G.736, G.823, ETS 300011, TBR12/13 and AT&T TR62411 met

- Tolerates more than 0.4 UI high frequency input jitter

- Crystal-less wander and jitter attenuation/compensation

- Flexible master clock frequency in the range of 1.02 to 20 MHz

- · Power-down function per channel

- Dual- or single-rail digital inputs and outputs to the framer interface

- · Unipolar CMI for interfacing fiber-optical transmission routes

- Selectable line codes (HDB3, B8ZS, AMI with zero code suppression)

- Loss-of-signal indication with programmable thresholds according to ITU-T G.775, ETS300233, ANSI T1. 403 and T1.231

- Clock generator for jitter-free system/transmit clocks per channel

- · Local loop, remote loop and digital loop back for diagnostic purposes

| Туре      | Package      |

|-----------|--------------|

| PEB 22504 | P-TQFP-100-3 |

# PEB 22504 QuadLIU V1.1

Overview

- Alarm and performance monitoring per second

- Two 16-bit counters for code violations and PRBS bit errors

- Insertion and extraction of Alarm Indication Signals (AIS)

- Elastic store for receive or transmit clock wander and jitter compensation

- · Controlled slip capability and slip indication

- Programmable elastic buffer size: 256 bits/128 bits/64 bits/32 bits/bypass

- Programmable in-band loop code detection and generation according to TR 62411

- Pseudo-Random Bit Sequence (PRBS) generator and monitor

- · Flexible software controlled device configuration

### **Microprocessor Interface Mode**

- 8-bit microprocessor bus interface (Intel or Motorola type)

- · All registers directly accessible

- Multiplexed and non-multiplexed address bus operations

- · Hardware and software reset options

- · One-second timer

#### General

- Boundary scan standard IEEE 1149.1

- P-TQFP-100-3 package (body size 14 mm × 14 mm)

- Single power supply: 3.3 V

- Temperature range: -40°C to +85°C

- Low power device, typical power consumption 100 mW per channel

#### **Applications**

- · Wireless Basestations

- · ATM and frame relay gateways

- · CSUs, DSUs

- Internet access equipment

- LAN/WAN Router

- ISDN-PRI, PABX

- Digital Access Cross-connect Systems (DACS)

- SDH/SONET ADD/DROP Multiplexer

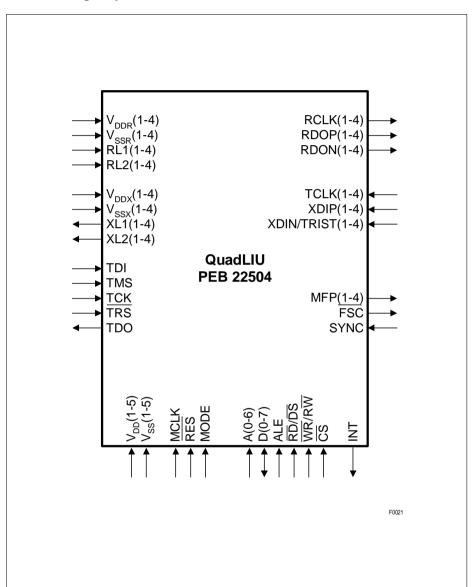

# 1.2 Logic Symbol

Figure 1 Logic Symbol

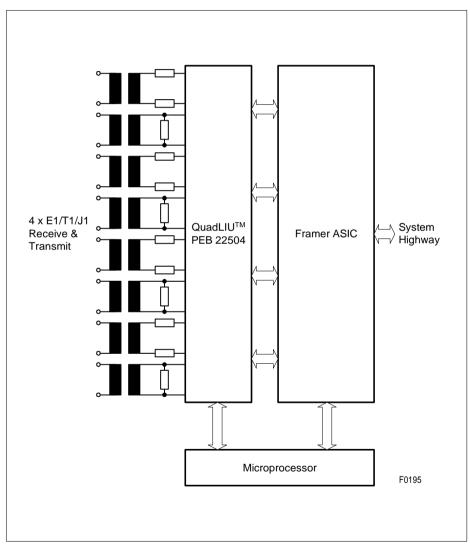

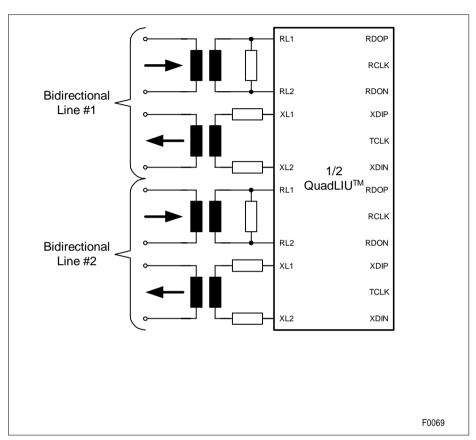

# 1.3 Typical Applications

Figure 2 shows a multiple link application using the QuadLIU™. Figure 3 shows a repeater application.

Figure 2 QuadLIU Application

Figure 3 QuadLIU Repeater Application

# 2 Pin Descriptions

### 2.1 Pin Diagram

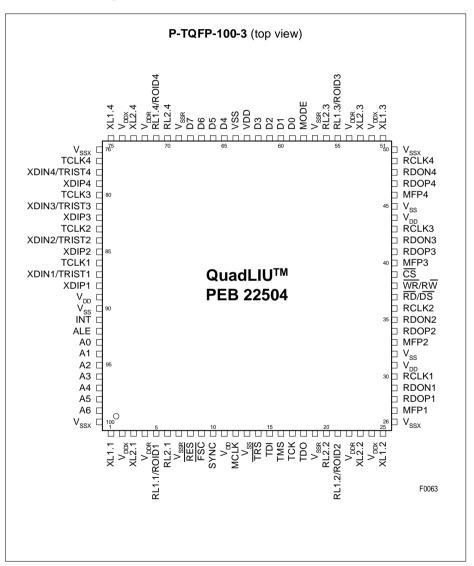

Figure 4 Pin Configuration

# 2.2 Pin Definitions and Functions

Table 1 Control Pin Functions

| Pin No.      | Signal           | Input (I) Output (O) Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9399         | A(0:6)           | I + PU                          | Address Bus Selects one of the internal registers for read or write.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5962<br>6568 | D(0:3)<br>D(4:7) | I/O + PU                        | Data Bus Eight-bit-wide bi-directional bus to be connected to the microprocessor data bus.                                                                                                                                                                                                                                                                                                                                                                                                |

| 92           | ALE              | I + PU                          | Address Latch Enable A high on this line indicates an address on the external address/data bus. The address information provided on lines A(6:0) is internally latched with the falling edge of ALE. This function allows the device to be connected directly to a multiplexed address/data bus. In this case, pins A(6:0) must be connected externally to the data bus pins. In case of demultiplexed mode, this pin has to be connected to V <sub>SS</sub> or V <sub>DD</sub> directly. |

| 39           | CS               | I + PU                          | Chip Select A low signal selects the device for read/write operations                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 37           | RD               | I + PU                          | Read Enable/Data Strobe (Intel bus mode, MODE=low) This signal indicates a read operation. When the device is selected via CS, the RD signal enables the bus drivers to output data from an internal register addressed via A(6:0) on to Data Bus.                                                                                                                                                                                                                                        |

|              | DS               | I + PU                          | Data Strobe (Motorola bus mode, MODE=high) This pin serves as input to control read/write operations.                                                                                                                                                                                                                                                                                                                                                                                     |

Table 1 Control Pin Functions (cont'd)

| Pin No. | Signal | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                      |

|---------|--------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38      | WR     | I + PU                                | WRite Enable/Read-Write Select (Intel bus mode, MODE=low) This signal indicates a write operation. When CS is active the device loads an internal register with data provided via the Data Bus.                                                                                                                               |

|         | RW     | I + PU                                | Read/Write Enable (Motorola bus mode, MODE=high) This signal distinguishes between read and write operations.                                                                                                                                                                                                                 |

| 91      | INT    | O/oD                                  | INTerrupt Request General interrupt request output for all interrupt sources. These interrupt sources can be masked individually via register IMR0/1. Interrupt status is reported via register CIS (Channel Interrupt Status) and ISR0/1.  Output characteristics of this pin can be defined to be push-pull (active high or |

|         |        |                                       | active low) or open-drain (active low) by using register IPC.                                                                                                                                                                                                                                                                 |

Table 1 Control Pin Functions (cont'd)

| Pin No.        | Signal         | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                      |

|----------------|----------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27, 33, 40, 46 | MFP(1:4)       |                                       | Multi Function Port Depending on programming of bits LIM4.PC(2:0) this multifunction port provides different status information of the device as shown in this table below. MFP1 corresponds to channel 1, MFP4 to channel 4. |

|                | LOS(1:4)       | 0                                     | Loss-of-Signal Indication LIM4.PC(2:0) = 000 Active high, if a loss-of-signal alarm is detected. This signal corresponds directly to bit LSR0.LOS.                                                                            |

|                | ALOS(1:4)      | 0                                     | Analog Loss-of-Signal Indication LIM4.PC(2:0) = 001 Active high, if the input level at RL1/2 drops below the programmed receive input threshold which is defined by register LIM2.RIL(2:0).                                   |

|                | PRBSS<br>(1:4) | 0                                     | PRBS Synchronization Status LIM4.PC(2:0) = 010 Active high if the Pseudo-Random Bit Sequence (PRBS) synchronization is achieved. This signal corresponds directly to bit LSR0.PRBSS.                                          |

|                | BPV(1:4)       | 0                                     | Bipolar Violation Indication LIM4.PC(2:0) = 011 Active high if a bipolar violation is detected. This signal corresponds directly to the increment signal of the code violation error counter.                                 |

Table 1 Control Pin Functions (cont'd)

| Pin No.                    | Signal     | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                             |

|----------------------------|------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27, 33, 40, 46<br>(cont'd) | XLS(1:4)   | 0                                     | Transmit Line Status LIM4.PC(2:0) = 100 Active high if the transmit line current limiter exceeds its maximum value. Pins XL1/2 are automatically tristated until the current drops below its maximum value ( or the "short" disappears). This signal corresponds directly to bit LSR1.XLS.           |

|                            | AIS(1:4)   | 0                                     | Alarm Indication Signal LIM4.PC(2:0) = 101 Active high if the alarm indication signal is detected. This signal corresponds directly to bit LSR0.AIS.                                                                                                                                                 |

| 10                         | SYNC       | I + PU                                | Clock Synchronization Reference clock for the internal DCOs of the device. Selectable via register GCR.SSF(1:0). Active high pulse input.                                                                                                                                                            |

| 9                          | FSC        | 0                                     | Frame Synchronization Pulse The synchronization pulse is active low for one 2.048 (E1)/1.544 MHz (T1/J1) cycle (pulse width = 488/648 ns). FSC is derived from the jitter attenuation DCO, which must be active for FSC output (8-kHz master mode only, GCR.SSF(1:0) = 10). Active low pulse output. |

| 87, 84, 81, 78             | TRIST(1:4) | I + PU                                | Transmit Line Tristate  If the single-rail data stream is selected by bit LIM0.XC(1:0), a high at these pins set the appropriate XL1/2 outputs into tristate.  TRISTi sets XL1.i/2.i of channel i into tristate, where i = 1 to 4.                                                                   |

Table 2 Signal Pin Functions

| Pin No.       | Signal    | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                              |

|---------------|-----------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 21, 55, 71 | RL1(1:4)  | I (analog)                            | Line Receiver 1 (LIM1.ECMIR = 0, default) Analog input from the external transformer (receive bipolar ring).                                                                                                                                                                                                                                          |

|               | ROID(1:4) | I                                     | Receive Optical Interface Data (LIM1.ECMIR = 1) CMI data received from fiber-optical interface with 2048 (E1)/ 1544 kbit/s (T1/J1). An internal DPLL extracts the receive route clock from the incoming data pulse. The duty cycle of the receiving signal has to be closely to 50 %. RL2 has to be connected to V <sub>SS</sub> or V <sub>DD</sub> . |

| 6, 20, 56, 70 | RL2(1:4)  | I (analog)                            | Line Receiver 2 (LIM1.ECMIR = 0, default) Analog input from the external transformer (receive bipolar tip).                                                                                                                                                                                                                                           |

| 1, 25, 51, 75 | XL1(1:4)  | O (analog)                            | Transmit Line 1 (transmit bipolar ring) (LIM1.ECMIX = 0, default) Analog output to the external transformer.                                                                                                                                                                                                                                          |

|               | XOID(1:4) | 0                                     | (LIM1.ECMIX = 1)<br>Single-ail CMI output                                                                                                                                                                                                                                                                                                             |

| 3, 23, 53, 73 | XL2 (1:4) | O (analog)                            | Transmit Line 2 (transmit bipolar tip) (LIM1.ECMIX = 0, default) Analog output to the external transformer. If single-rail CMI output is selected (LIM1.ECMIX = 1), this pis is undefined and has to be left open.                                                                                                                                    |

Table 2 Signal Pin Functions (cont'd)

| Pin No.        | Signal    | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                        |

|----------------|-----------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28, 34, 41, 47 | RDOP(1:4) | O                                     | Receive Data Output/Positive Received data at RL1/2 is sent on RDOP/ RDON in NRZ format to the framer interface. Clocking of data is done with the rising or falling edge of RCLK(1:4), selected by bit LIM4.RPE. RDOP/RDON are set low if a loss-of-signal alarm is detected. The source of the received data is selected by bit LIM2.RD(1:0). |

|                |           |                                       | LIM2.RD(1:0) = 00: Data recovered by the DPLL is AMI/HDB3/B8ZS decoded and output on RDOP; RDON is not defined.                                                                                                                                                                                                                                 |

|                |           |                                       | LIM2.RD(1:0) = 01: Dual-rail data recovered by the DPLL, not AMI/HDB3/B8ZS decoded, is output on RDOP/RDON.                                                                                                                                                                                                                                     |

|                |           |                                       | LIM2.RD(1:0) = 10: Sliced data, not recovered by the DPLL is output on RDOP/RDON. A "1" on RDOP corresponds to a positive pulse on RL1/RL2. A "1" on RDON corresponds to a negative pulse on RL1/RL2.                                                                                                                                           |

| 29, 35, 42, 48 | RDON(1:4) | 0                                     | Receive Data Output/Negative<br>LIM1.RDON(1:0) = 00 (see above)                                                                                                                                                                                                                                                                                 |

|                | BPV(1:4)  | 0                                     | Bipolar Violation Indication<br>LIM1.RDON(1:0) = 01                                                                                                                                                                                                                                                                                             |

|                | SCLKO     | 0                                     | System Clock Output<br>LIM1.RDON(1:0) = 10                                                                                                                                                                                                                                                                                                      |

|                | SCLKI     | I + PU                                | System Clock Input LIM1.RDON(1:0) = 11 Read clock for jitter attenuater buffer if internal DCO is not used (see Figure 10 on page 38).                                                                                                                                                                                                          |

Table 2 Signal Pin Functions (cont'd)

| Pin No.        | Signal         | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|----------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

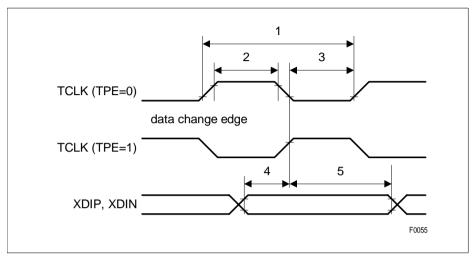

| 88, 85, 82, 79 | XDIP(1:4)      | I + PU                                | Transmit Data In Positive Transmit data received from the framer interface is output on XL1/2. NRZ data has to be provided on XDIP. Latching of data is done with the rising or falling transitions of TCLK according to LIM4.TPE.                                                                                                                                                                                               |

| 87, 84, 81, 78 | XDIN(1:4)      | I + PU                                | Transmit Data In Negative If the dual-rail data stream is selected by bits LIM0.XC(1:0) transmit data received from the framer interface is output on XL1/ 2. NRZ data (AMI negative data) has to be provided on XDIN. Latching of data is done with rising or falling transitions of TCLK according to bit LIM4.TPE.                                                                                                            |

| 30, 36, 43, 49 | RCLK(1:4)      | O                                     | Receive Clock The output functions of these ports are defined by register CMR.RS(1:0):  CMR.RS(1:0) = 00: Receive Clock extracted from the incoming data pulses.  CMR.RS(1:0) = 01: Receive Clock extracted from the incoming data pulses. RCLK is set high in case of loss-of-signal (LSR0.LOS=1).  Selected by GCR.R1S(1:0), one of the four RCLK(1:4) is output on RCLK1. The clock frequency is 2.048 (E1)/1.544 MHz (T1/J1) |

|                | SCLKO<br>(1:4) | 0                                     | CMR.RS(1:0) = 10:<br>Output of de-jittered system clock sourced<br>by DCO.<br>Clock frequency: 2.048 (E1) or 1.544 MHz<br>(T1/J1). See Figure 10 on page 38.                                                                                                                                                                                                                                                                     |

Table 2 Signal Pin Functions (cont'd)

| Pin No.        | Signal    | Input (I)<br>Output (O)<br>Supply (S) | Function                                                                                                                         |

|----------------|-----------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 86, 83, 80, 77 | TCLK(1:4) | I + PU                                | Transmit Clock Input of the working clock for the transmitter with a frequency of 2.048 (E1)/1.544 MHz (T1/J1).                  |

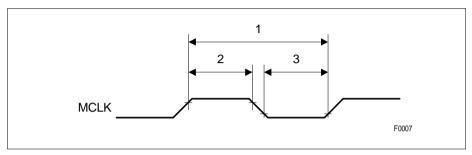

| 12             | MCLK      | I                                     | Master Clock A reference clock between 1.02 MHz and 20 MHz must be provided on this pin (32 ppm accuracy).                       |

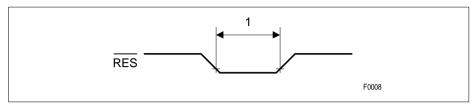

| 8              | RES       | I                                     | Hardware Reset A low signal on this pin forces the device into reset state. During reset, an active clock is needed on pin MCLK. |

| 58             | MODE      | I + PU                                | Operation Mode Select 0 = Intel bus 1 = Motorola bus                                                                             |

Table 3 **Power Supply Pins** Pin No. Signal Input (I) Function Output (O) Supply (S) S (analog) 4, 22, 54, 72  $V_{DDR}$ **Positive Power Supply** for the analog receiver 7, 19, 57, 69 **Power Supply Ground**  $V_{SSR}$ S (analog) for the analog receiver **Positive Power Supply** 2, 24, 52, 74  $V_{DDX}$ S (analog) for the analog transmitter  $V_{SSX}$ **Power Supply Ground** 26, 50, 76, S (analog) 100 for the analog transmitter  $V_{\text{DD}}$ 11, 31, 44, S **Positive Power Supply** 63, 89 for digital subcircuits

Power Supply Ground for digital subcircuits

Table 4 Boundary Scan Pins

$V_{SS}$

S

13, 32, 45,

64, 90

| Pin No. | Signal | Input (I) Output (O) Supply (S) | Function                                                                                                                             |

|---------|--------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 14      | TRS    | I + PU                          | Test Reset (Boundary Scan) active low; if the JTAG boundary scan is not used, this pin must be connected to RES or V <sub>SS</sub> . |

| 15      | TDI    | I + PU                          | Test Data Input (Boundary Scan)                                                                                                      |

| 16      | TMS    | I + PU                          | Test Mode Select (Boundary Scan)                                                                                                     |

| 17      | TCK    | I + PU                          | Test Clock (Boundary Scan)                                                                                                           |

| 18      | TDO    | 0                               | Test Data Output (Boundary Scan)                                                                                                     |

Note: oD = open-drain output

PU = input or input/output comprising an internal pullup device To override the internal pullup by an external pulldown, a resistor value of 22 k $\Omega$  is recommended.

Unused pins containing pullups can be left open. Unused receive channels have to be connected to a fixed level ( $V_{DDR}$  or  $V_{SSR}$ ).

# 3 Functional Description

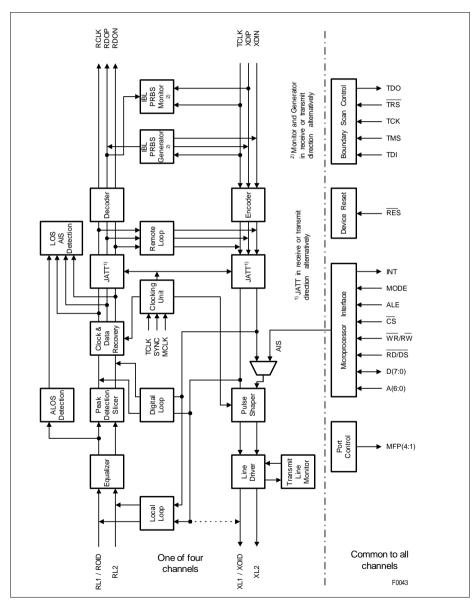

#### 3.1 Functional Overview

The QuadLIU<sup>™</sup> device contains analog and digital function blocks that are configured and controlled by an external microprocessor or microcontroller.

#### The main interfaces are

- · Receive-line Interface

- Transmit-line Interface

- · Framer interface

- Microprocessor interface

- · Boundary scan interface

as well as several control lines for reset and clocking purpose.

#### The main internal functional blocks are

- Analog line receiver with equalizer network and clock/data recovery

- · Analog line driver with programmable pulse shaper and line build out

- · Central clock-generation module

- · Jitter attenuator in receive or transmit direction

- Test functions (e.g., loop switching local remote digital)

- · Register access interface

- · Boundary scan control

# 3.2 Block Diagram

Figure 5 Block Diagram

### 3.3 Functional Blocks

# 3.3.1 Microprocessor Control Unit

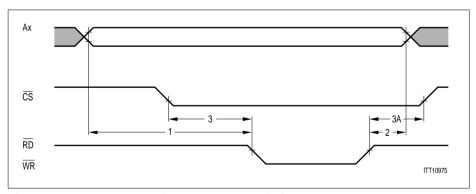

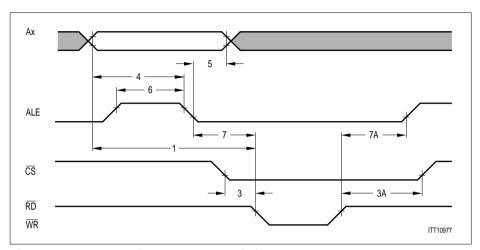

The communication between the CPU and the QuadLIU™ is done via a set of directly accessible registers. The interface may be configured as Intel or Motorola type (by control pin MODE) with a data bus width of 8 bits.

The CPU transfers data to/from the QuadLIU<sup>™</sup>, sets the operating modes, controls function sequences, and gets status information by writing or reading control/status registers. **Table 5** shows how the ALE (**A**ddress **L**atch **E**nable) and MODE lines are used to control the interface type. Switching of ALE allows the QuadLIU<sup>™</sup> to be connected directly to a multiplexed address/data bus.

Table 5 Selectable Bus and Microprocessor Interface Configuration

| ALE                             | MODE | Microprocessor interface | Bus Structure |

|---------------------------------|------|--------------------------|---------------|

| $V_{SS}$ or $V_{DD}$            | high | Motorola                 | demultiplexed |

| $\overline{V_{SS}}$ or $V_{DD}$ | low  | Intel                    | demultiplexed |

| switching                       | low  | Intel                    | multiplexed   |

# 3.3.1.1 Interrupt Interface

Special events in the QuadLIU™ are indicated by means of a single interrupt output, which requests the CPU to read status information from the QuadLIU™, or to transfer data to the QuadLIU™. The pin characteristic (open drain, push-pull) is programmable.

Since only one INT request output is provided, the cause of an interrupt must be determined by the CPU by reading the QuadLIU™'s interrupt status registers CIS and ISR(1:0). The interrupt on pin INT and the interrupt status bits are reset by reading the interrupt status registers. Registers ISR0 and ISR1 are "cleared on read".

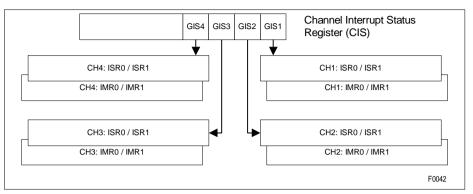

The structure of the interrupt status registers is shown in Figure 6.

Figure 6 Interrupt Status Registers

Each interrupt indication of register ISR0 and ISR1 can be masked selectively by setting the corresponding bit in the mask registers IMR0 and IMR1. If the interrupt status bits are masked, they neither generate an interrupt on pin INT nor are they visible in ISR(1:0).

The non-maskable **C**hannel **I**nterrupt **S**tatus (CIS) register serves as a pointer to pending ISRs. After the QuadLIU<sup>™</sup> has requested an interrupt by activating its INT pin, the CPU should first read the CIS register to identify the requesting channel by bit GISx (**G**lobal **I**nterrupt **S**tatus bit of channel x) After that the corresponding interrupt status register ISR(1:0) of the requesting channel should be examined. After reading the interrupt status registers ISR(1:0), the pointer in CIS is cleared or updated if another interrupt requires service.

If **all** pending interrupts are acknowledged by reading the ISRs, CIS is reset and pin INT goes inactive.

Updating of ISR(1:0) and CIS is prohibited only during read access.

## Masked Interrupts Visible in Status Registers

The CIS register indicates those channels with active interrupt indications.

An additional mode ("visible mode") may be selected via bit LIM4.VIS. In this mode, masked interrupt status bits neither generate an interrupt on pin INT nor are they visible in CIS, but are displayed in the corresponding ISR(s) ISR(1:0).

This mode is useful when some interrupt status bits are to be polled in the individual ISRs.

Note: In the visible mode, all active interrupt status bits, whether the corresponding actual interrupt is masked or not, are reset when the interrupt status register is read. Thus, when polling of some interrupt status bits is desired, care must be taken that unmasked interrupts are not lost in the process.

All unmasked interrupt statuses are treated as in normal mode.

Please note that whenever polling is used, all interrupt status registers concerned have to be polled individually (no "hierarchical" polling is possible), since CIS contains information on only those interrupts that were actually generated, i.e., unmasked interrupts.

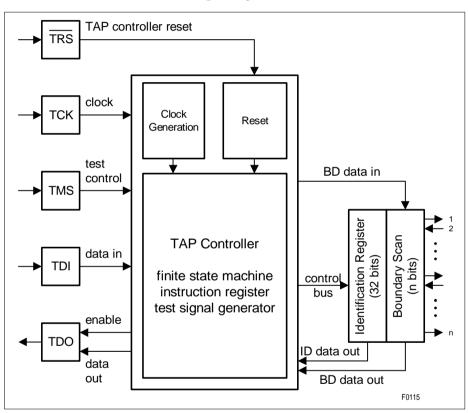

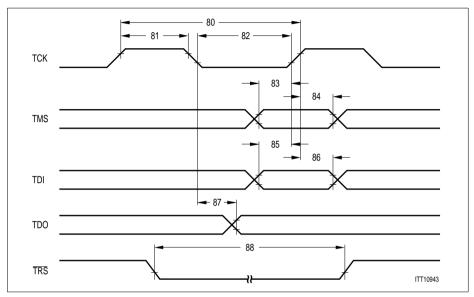

# 3.3.2 Boundary Scan Unit

In the QuadLIU<sup>™</sup> a **Test A**ccess **P**ort (TAP) controller is implemented. The essential part of the TAP is a finite state machine (16 states) controlling the different operational modes of the boundary scan. Both, TAP controller and boundary scan, meet the requirements in the JTAG standard IEEE 1149.1. **Figure 7** gives an overview.

Figure 7 Block Diagram of Test Access Port and Boundary Scan

After switching on the device (power-on), a reset signal has to be applied to  $\overline{TRS}$ , which forces the TAP controller into test logic reset state.

For normal operation without boundary scan access, the boundary reset pin  $\overline{TRS}$  can be tied to the device reset pin  $\overline{RES}$ .

The boundary length is 150.

If no boundary scan operation is used,  $\overline{TRS}$  has to be connected to  $\overline{RST}$  or  $V_{SS}$ . TMS, TCK and TDI do not need to be connected since pullup transistors ensure high input levels in this case.

Test handling (boundary scan operation) is performed via the pins TCK (Test Clock), TMS (Test Mode Select), TDI (Test Data Input) and TDO (Test Data Output) when the TAP controller is not in its reset state, that means  $\overline{\text{TRS}}$  is connected to  $V_{\text{DD}}$  or it remains unconnected due to its internal pull up. Test data at TDI is loaded with a clock signal connected to TCK. "1" or "0" on TMS causes a transition from one controller state to another; constant "1" on TMS leads to normal operation of the chip.

An input pin (I) uses one boundary scan cell (data in), an output pin (O) uses two cells (data out and enable) and an I/O-pin (I/O) uses three cells (data in, data out and enable). Note that most functional output and input pins of the QuadLIU™ are tested as I/O pins in boundary scan, hence using three cells. The desired test mode is selected by serially loading a 8-bit instruction code into the instruction register via TDI (LSB first).

**EXTEST** is used to examine the interconnection of the devices on the board. In this test mode at first all input pins capture the current level on the corresponding external interconnection line, whereas all output pins are held at constant values ("0" or "1"). Then the contents of the boundary scan is shifted to TDO. At the same time the next scan vector is loaded from TDI. Subsequently all output pins are updated according to the new boundary scan contents and all input pins again capture the current external level afterwards, and so on.

**SAMPLE** is a test mode which provides a snapshot of pin levels during normal operation.

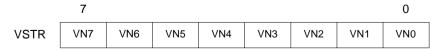

**IDCODE**: A 32-bit identification register is serially read out via TDO. It contains the version number (4 bits), the device code (16 bits) and the manufacturer code (11 bits). The LSB is fixed to "1".

The ID code field is set to: 0001 0000 0000 0101 1010 0000 1000 0011

Version =  $1_{H_1}$  Part Number =  $005A_H$ , Manufacturer =  $083_H$  (including LSB, fixed to "1")

BYPASS: A bit entering TDI is shifted to TDO after one TCK clock cycle.

An alphabetical overview of all TAP controller operation codes is given in Table 6.

Table 6 TAP Controller Instruction Codes

| TAP Instruction          | Instruction Code |  |

|--------------------------|------------------|--|

| BYPASS                   | 11111111         |  |

| EXTEST                   | 0000000          |  |

| IDCODE                   | 00000100         |  |

| SAMPLE                   | 0000001          |  |

| reserved for device test | 01010011         |  |

Data Sheet 34 2001-02

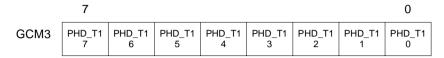

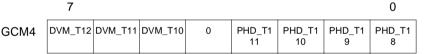

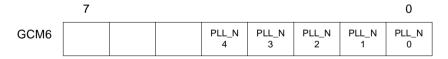

# 3.3.3 Master Clocking Unit

The QuadLIU<sup>™</sup> provides a flexible clocking unit that can use a stable reference clock in the range of 1.02 MHz to 20 MHz supplied on pin MCLK.

The clocking unit has to be tuned to the selected reference frequency by setting the Global Clock Mode registers (GCM(6:1)) accordingly.

The calculation formulas for the appropriate register settings can be found in **Chapter 6.2** on **page 87**. All required clocks for E1 and T1/J1 operation are generated internally by this circuit. The global setting depends only on the selected master clock frequency, and is the same for E1 and T1/J1 because both clock rates are provided simultaneously.

The flexible master clock unit can be disabled (GCM2.VFREQ\_EN = 0, which is the default configuration after hardware reset). In this case, a fixed reference clock of 2.048 MHz (E1) or 1.544 MHz (T1/J1) has to be supplied on pin MCLK.

Note: E1 or T1/J1 mode can be selected independently for each channel if flexible clocking is selected (GCM2.VFREQ\_EN = 1).

To meet the transmit clock and data accuracy requirements of E1/T1 in free running mode, the MCLK reference clock itself must have an accuracy of  $\pm$  32 ppm. The synthesized clock can be controlled on pin RCLK.

Figure 8 Flexible Master Clock Unit

**Interface Description**

# 4 Interface Description

#### 4.1 Receiver

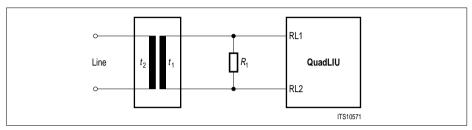

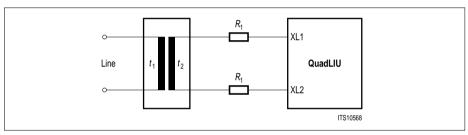

Figure 9 Receiver Configuration

Table 7 Examples of External Component Values (Receive)

| Parameter |                                               | Characteristic Impedance [ $\Omega$ ] |     |     |     |

|-----------|-----------------------------------------------|---------------------------------------|-----|-----|-----|

|           |                                               | E1                                    |     | T1  | J1  |

|           |                                               | 75                                    | 120 | 100 | 110 |

|           | $R_1$ (± 1 %) [ $\Omega$ ]                    | 75                                    | 120 | 100 | 110 |

|           | <i>t</i> <sub>2</sub> : <i>t</i> <sub>1</sub> | 1:1                                   | 1:1 | 1:1 | 1:1 |

#### 4.1.1 Receive Line Interface

Several data input types are supported:

- Ternary coded signals received at multifunction ports RL1 and RL2 from a 10 dB or -36 dB (E1)/-36 dB (T1/J1) ternary interface. The ternary interface is selected if LIM1.ECMIR is reset.

- CMI coded data on port ROID received from a fiber-optical interface. The optical interface is selected if LIM1.ECMIR is set.

The signal at the ternary interface is received on both ends of a transformer.

The line termination impedance 75  $\Omega/120~\Omega/100~\Omega$  is selectable by switching resistors in parallel. This selection does not require a change of transformers.

# 4.1.2 Short-haul/Long-haul Interface

The QuadLIU™ has an integrated short- and long-haul line interface consisting of a receive equalization network and noise filtering.

# 4.1.3 Receive Equalization Network

The QuadLIU™ automatically recovers the signals received on pins RL1/2 in a range of up to -36 dB. The maximum reachable length with a 22 AWG twisted-pair cable is 6000 feet (T1/J1). After reset the QuadLIU™ is in short-haul mode, and received signals are recovered up to a cable attenuation of -10 dB. Switching to long-haul mode is done by setting of register bit LIM1.EQON.

Noise filters eliminate the higher frequency part of the received signals. The incoming data is peak-detected and sliced at 45, 50, 55, or 67% of the peak value (programmable in four steps by LIM2.SLT(1:0)) to produce the digital data stream. The received data is then forwarded to the clock and data recovery unit (DPLL) or optionally transferred to ports RDOP/RDON directly (see LIM2.RD(1:0)).

The current equalizer status is indicated by register RES (Receive Equalizer Status).

#### 4.1.4 Receive Line Attenuation Indication

RES reports the current receive line attenuation in 25 steps of approximately 1.7 dB (E1)/1.4 dB (T1/J1) each. The least significant five bits of this register indicate the cable attenuation in dB. These five bits are only valid together with the most significant two bits (RES.EV(1:0) = 01) .

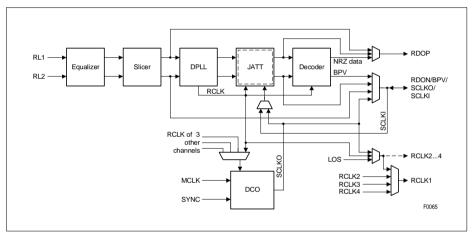

## 4.1.5 Receive Clock and Data Recovery

The analog received signal on port RL1/2 is equalized and then peak-detected to produce a digital signal. The receive clock and data recovery subcircuit extracts the route clock RCLK from the data stream received on the RL1/2 or ROID lines, and converts the data stream into a dual-rail bit stream. The clock and data recovery works with the internally generated high-frequency clock based on MCLK. Normally, the clock that is output on pin RCLK is the recovered clock from the signal provided on RL1/2, and has a duty cycle close to 50 %. The free run frequency is defined by the master clock setting [2.048 MHz (E1)/1.544 MHz (T1/J1)] in periods with no signal. The intrinsic jitter generated in the absence of any input jitter is not more than 0.02 UI (Unit Intervals).

Figure 10 Receive Clock System

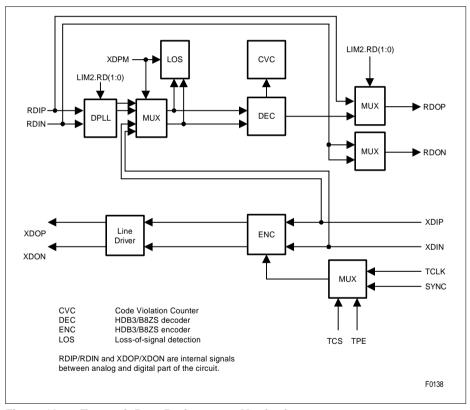

## 4.1.6 Receive Line Coding

In E1 applications, HDB3 and AMI coding is provided for the data received from the ternary interface. In T1 mode, B8ZS and AMI code is supported. In case of the optical interface, CMI Code (1T2B) with HDB3/B8ZS postprocessing is provided. If the DPLL is not bypassed, the receive route clock is recovered from the data stream. The CMI decoder does not correct any errors. The HDB3 code is used along with double violation detection or extended code violation detection (optional, see LIM0.EXZE). In B8ZS or AMI, code all code violations are detected.

Detected errors increment the code violation counter (16 bits length).

# 4.1.7 Pulse-Density Detector

Pulse-density violations of the received signal are detected according to ANSI T1.403. Violations are indicated (LSR0.PDEN, ISR0.PDENI) if the incoming signal contains:

- More than 15 consecutive zeros or

- Fewer than N ones in each and every time window of 8 × (N+1) digit time slots with N taking on all values of 1 to 23.

The indication is cleared, if the pulse-density fulfills the requirement within 23 received ones.

# 4.1.8 Alarm Handling

The receive line interface includes alarm detection for AIS (Alarm Indication Signal) and LOS (Loss Of Signal).

# 4.1.8.1 AIS (Blue Alarm) Detection

The AIS is detected according to ITU-T G.775 and ANSI T1.231.

In E1 applications, the alarm is set when the incoming signal has fewer than three zeros in each of two consecutive 512-bit periods. In T1 applications, the AIS alarm is set when fewer than 6 zeros are detected within a time interval of 3 ms received on RL1/2. AIS detection also works in the presence of a bit error rate of up to 10<sup>-3</sup>.

An AIS alarm is indicated in a Line Status Register (LSR0.AIS) and an Interrupt Status Register (ISR0.AIS).

# 4.1.8.2 LOS (Red Alarm) Detection

There are different definitions for detecting LOS alarms in the ITU-T G.775, ETS 300233, ANSI T1.403 and T1.231. The QuadLIU<sup>™</sup> covers all these standards. The LOS indication is performed by generating an interrupt (if not masked) and activating a status bit. Additionally, a LOS status change interrupt is programmable via register LIM4.SCI.

#### Detection:

In digital receive interface mode (LIM1.ECMIR = 1), an alarm is generated if the incoming data stream has no pulses (no transitions) for a certain number (N) of consecutive pulse periods. "No pulse" means a logical zero on pin ROID.

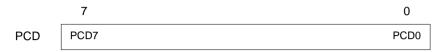

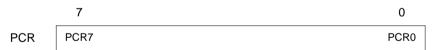

In analog receive interface mode (LIM1.ECMIR = 0), a pulse with an amplitude less than Q dB below nominal is the criteria for "no pulse". The receive signal level Q is programmable via three control bits, LIM2.RIL(2:0), related to the differential voltage between pins RL1 and RL2 (see DC Characteristics on page 100). The number N can be set via an 8-bit register, PCD. The contents of the PCD register is multiplied by 16; the product equals the number of pulse periods until the alarm has to be detected (16

to 4096 pulse periods). ETS 300233, which requires detection intervals of at least 1 ms, can be fulfilled.

#### Recovery:

The recovery procedure starts after detection of a logical "one" (digital receive interface) or a pulse (analog receive interface) with an amplitude more than Q dB (defined by LIM2.RIL(2:0)) of the nominal pulse. The value in the 8 bit register PCR defines the number of pulses (1 to 255) required to clear the LOS alarm. Additional recovery conditions may be programmed by register LIM5.LOSR(1:0).

#### 4.1.9 Jitter Attenuator

The internal PLL (**P**hase-**L**ocked **L**oop) circuitry called DCO (**D**igitally **C**ontrolled **O**scillator) generates a "jitter-free" output clock which is directly depending on the phase difference between the incoming clock and the jitter-attenuated clock. The jitter attenuator can be placed on the receive or transmit path of each channel individually. The working clock is an internally generated high-frequency clock based on the clock provided on pin MCLK. The jitter attenuator meets the requirements of ITU-T I.431, G.703, G.736-739, G.823, G.824, ETSI 300011, ETSI TBR12/13, AT&T TR62411, AT&T TR43802, TR-TSY 009, TR-TSY 253 and TR-TSY 499. The receive jitter attenuator can be synchronized either to the extracted receive clock RCLK, or to a 2.048 (E1)/1.544 MHz (T1/J1)/8 KHz (E1/T1/J1) clock provided on pin SYNC. The transmit jitter attenuator synchronizes with either the clock provided on pin TCLK, or the receive clock RCLK (remote loop/loop-timed).

Received data is written into the elastic buffer with RCLK and is read out with the dejittered clock sourced by DCO (if JATT in receive direction is selected). The jitter attenuated clock can be output on pin RCLK. An 8-kHz clock is provided on pin FSC.

Transmit data is written into the elastic buffer with TCLK and is read out with the dejittered clock sourced by DCO (if JATT in transmit direction is selected). In the loop-timed clock configuration (CMR.ELT) the DCO circuitry generates a transmit clock that is frequency synchronized to RCLK.

The DCO circuitry attenuates the incoming jittered clock starting at 2 Hz (E1)/6 Hz (T1/J1) jitter frequency with 20 dB/decade fall-off. Wander with a jitter frequency below 2/6 Hz is passed unattenuated. The intrinsic jitter in the absence of any input jitter is less than 0.02 UI.

The DCO accepts gapped clocks, which are used in ATM or SDH/SONET applications.

For some applications, it might be useful to start jitter attenuation at lower frequencies. Therefore the corner frequency is switchable by the factor of ten down to 0.2/0.6 Hz (CMR.SCF).

The jitter attenuator works in two different modes:

#### Slave mode

In slave mode (CMR.MAS = 0), the DCO is synchronized with the recovered route clock. In case of LOS (receive mode) or transmit clock is lost (transmit mode, bit LSR1.TCS = 1), the DCO switches to master mode automatically. If bit CMR.DCS is set, automatic switching from RCLK/TCLK to SYNC is disabled.

#### Master mode

In master mode (CMR.MAS = 1) the jitter attenuator is in free-running mode if no clock is supplied on pin SYNC . If there is a clock with a frequency of 2.048 (E1)/1.544 MHz (T1/J1)/8 kHz (E1/T1/J1) on the SYNC input, the DCO is synchronized with this input signal.

In some applications, it might be useful to synchronize to a gapped clock sourced by pin SYNC. In this case, the DCO circuitry would be centered to the nominal frequency. Optionally the QuadLIU<sup>TM</sup> offers the ability to disable the centering the DCO circuitry (LIM4.DCF = 1).

**Table 8** shows the clock modes with the corresponding synchronization sources.

Table 8 Clocking Modes

| Mode   | Internal<br>LOS active<br>or<br>TCS set | SYNC<br>Input   | DCO <sup>1)</sup> Output Clock                                                 |

|--------|-----------------------------------------|-----------------|--------------------------------------------------------------------------------|

| Master | no                                      | $V_{DD}$        | Free-running (DCO centered)                                                    |

| Master | no                                      | 1.544 MHz       | Synchronized with SYNC input <sup>2)</sup> GCR.SSF(1:0) = 01                   |

| Master | no                                      | 2.048 MHz       | Synchronized with SYNC input <sup>2)</sup> GCR.SSF(1:0) = 00                   |

| Master | no                                      | 8 kHz           | Synchronized with SYNC input<br>GCR.SSF(1:0) = 10                              |

|        | ·                                       |                 |                                                                                |

| Slave  | no                                      | V <sub>DD</sub> | Synchronized with line RCLK/TCLK(4:1), selected by CMR.DSS(1:0)                |

| Slave  | no                                      | 1.544 MHz       | Synchronized with line RCLK/TCLK(4:1), selected by CMR.DSS(1:0) <sup>2)</sup>  |

| Slave  | no                                      | 2.048 MHz       | Synchronized with line RCLK/TCLK(4:1) , selected by CMR.DSS(1:0) <sup>2)</sup> |

| Slave  | ves                                     | VDD             | Free running (DCO centered)                                                    |

Table 8 Clocking Modes (cont'd)

| Mode  | Internal<br>LOS active<br>or<br>TCS set | SYNC<br>Input | DCO <sup>1)</sup> Output Clock                               |

|-------|-----------------------------------------|---------------|--------------------------------------------------------------|

| Slave | yes                                     | 1.544 MHz     | Synchronized with SYNC input <sup>2)</sup> GCR.SSF(1:0) = 01 |

| Slave | yes                                     | 2.048 MHz     | Synchronized with SYNC input <sup>2)</sup> GCR.SSF(1:0) = 00 |

<sup>1)</sup> The DCO can be used either in receive or transmit direction (see Figure 10 and Figure 14)

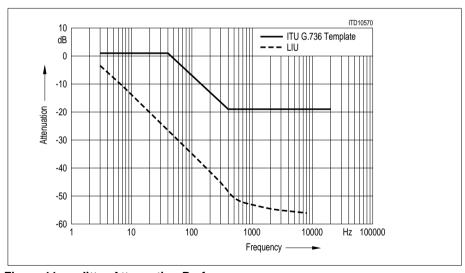

The jitter attenuator meets the jitter transfer requirements of ITU-T I.431 and G.735-739 (refer to Figure 11).

Figure 11 Jitter Attenuation Performance

Also the requirements of ETSI TBR12/13 are satisfied. The DCO starts jitter attenuation at about 2 Hz to ensure adequate margin against TBR12/13 output jitter limit with 15 UI input at 20 Hz.

<sup>2)</sup> If flexible clocking mode is selected (GCM2.VFREQ\_EN = 1), the SYNC frequency can be selected independent of E1 or T1/J1 mode.

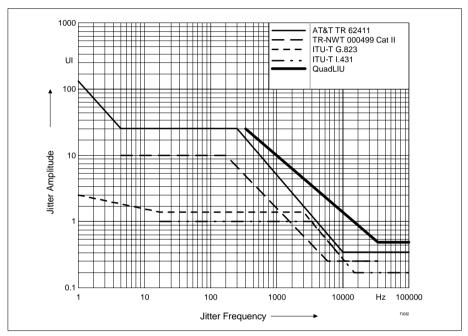

#### 4.1.10 Jitter Tolerance

The QuadLIU™ receiver's tolerance to input jitter complies with ITU for CEPT applications. Figure 12 shows the curves of different input jitter specifications as well as the QuadLIU™ performance.

Figure 12 Jitter Tolerance

## 4.1.11 Output Jitter

In the absence of any input jitter, the QuadLIU<sup>™</sup> generates the output jitter as specified in Table 9.

Table 9 Output Jitter

| Specification | Measuremer   | Output Jitter |                   |  |

|---------------|--------------|---------------|-------------------|--|

|               | Lower Cutoff | Upper Cutoff  | (UI peak to peak) |  |

| AT&T TR62411  | 10 Hz        | 8 kHz         | < 0.015           |  |

|               | 8 kHz        | 40 kHz        | < 0.015           |  |

|               | 10 Hz        | 40 kHz        | < 0.015           |  |

| ITU-T I.431   | 20 Hz        | 100 kHz       | < 0.015           |  |

|               | 700 Hz       | 100 kHz       | < 0.015           |  |

|               | Br           | < 0.02        |                   |  |

#### 4.1.12 Elastic Buffer

The elastic buffer can be placed in receive or transmit direction to generate a "jitter-free" data stream. Different buffer sizes can be programmed by LOOP.BS(1:0):

00: 256 bits

01: 128 bits

10: 64 bits

11: 32 bits

Slips are performed in all buffer modes. After a slip is detected, the read pointer is adjusted to one half of the current buffer size.

A slip condition is detected when the write pointer and the read pointer of the memory are nearly coincident. If a slip condition is detected, a negative slip or a positive slip is performed. For a negative slip, one half of the current buffer size is skipped. For a positive slip, one half of the current buffer size is read out twice. A positive or negative slip is indicated in the interrupt status bits ISR0.SLP and ISR0.SLN.

When bit CMDR.CEB is set, the data delay through the elastic buffer is set to half of the current buffer size.

#### 4.2 Transmitter

The serial bit stream is then processed by the transmitter which has the following functions:

- AIS generation (Alarm Indication Signal)

- · Generation of AMI, B8ZS, HDB3 or CMI coded signals

- Generation of IBL (In-Band Loop) code

- Generation of PRBS (Pseudo-Random Binary Sequence)

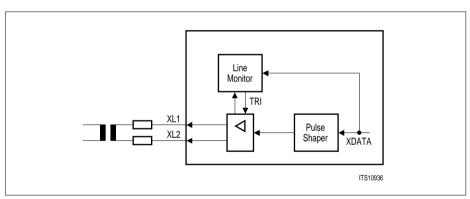

#### 4.2.1 Transmit Line Interface

The analog transmitter transforms the unipolar bit stream to ternary (alternate bipolar) return-to-zero signals of the appropriate programmable pulse shape. The unipolar data is provided by the digital transmitter.

Figure 13 Transmitter Configuration

Table 10 Examples of External Component Values (Transmit)

| Parameter |                            | Characteristic Impedance [ $\Omega$ ] |       |         |       |  |  |

|-----------|----------------------------|---------------------------------------|-------|---------|-------|--|--|

|           |                            | E                                     | 1     | T1      | J1    |  |  |

|           |                            | 75                                    | 120   | 100     | 110   |  |  |

|           | $R_1$ (± 1 %) [ $\Omega$ ] | 7.5                                   | 7.5   | 2       | 2     |  |  |

|           | t2 : t1                    | 1:2.4                                 | 1:2.4 | 1 : 2.4 | 1:2.4 |  |  |

|           | XPM2.XLHC                  | 1                                     | 1     | 1       | 1     |  |  |

In transmit direction, only the ternary or CMI interface is supported:

- Ternary signal

- The received data stream on pins XDIP or XDIP/N is converted into a ternary signal which is output on pins XL1 and XL2. In E1 mode the HDB3 and AMI line code is employed. In T1 mode, B8ZS and AMI with or without zero code suppression is supported (selected by LIM0.XC(1:0); the encoder can also be disabled).

- CMI signal

The received data stream is converted into a CMI signal with HDB3 (E1) or B8ZS (T1/J1) precoding.

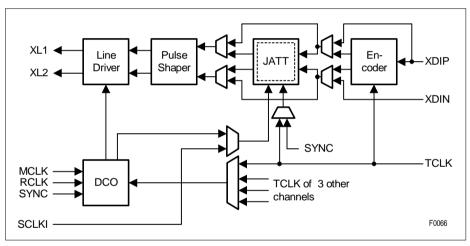

# 4.2.2 Transmit Clock System

Figure 14 Transmit Clock System

The jitter attenuator can be placed in the receive or transmit path. If placed in the transmit path, data is clocked into the JATT buffer with the transmit clock TCLK. If automatic clock-switching is enabled (LIM5.ACS = 1), TCLK is replaced by the SYNC clock automatically, if TCLK is missing. The active edge of TCLK (or SYNC, if TCLK is missing) can be programmed by LIM4.TPE.

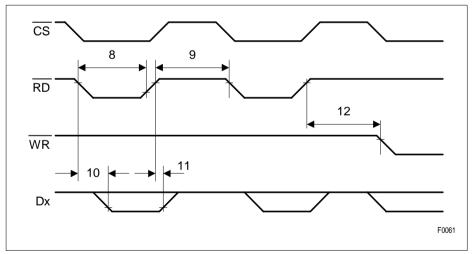

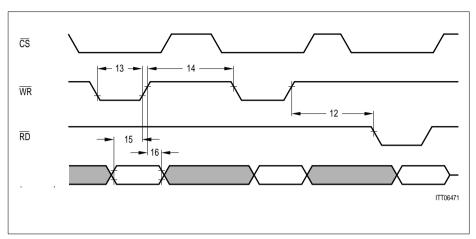

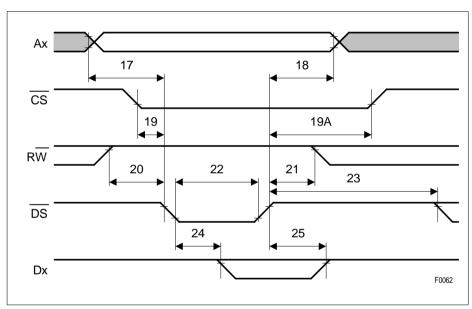

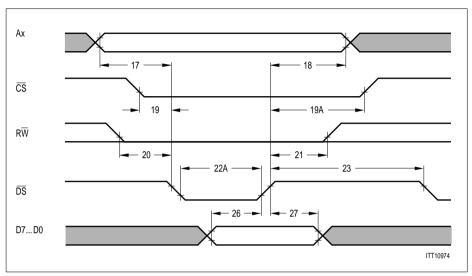

# 4.2.3 Pulse-Density Enforcer