### FDB-1022: XFP Evaluation Board

The Finisar FDB-1022 Evaluation Board is a convenient and powerful vehicle for testing and evaluating the new 10 Gigabit/s XFP optical transceivers.

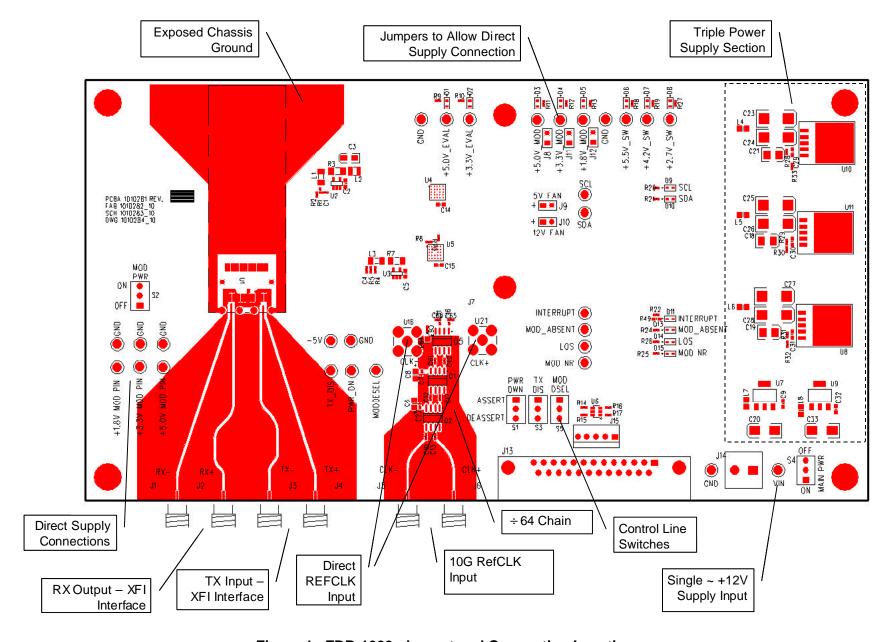

The board consists of a single XFP connector and cage, high quality transmission lines and connectors for the serial data signals, connections for reference clock inputs, all low speed status and control lines, and the 2-wire serial management interface. All pin connections are compliant with the XFP MSA Rev 1.0 Standard.

For convenience, the FDB-1022 contains onboard switching and linear power supplies to provide all three required module power supplies (1.8V, 3.3V and 5.0V) from a single external +12V connection. The outputs of each onboard supply are factory set, and may be switched off and on using S2. These supplies can be adjusted and monitored (both voltage and current) using the supplied evaluation board software. By removing jumpers J8, J11 and/or J12, the on-board supplies may be disconnected from the module and external supplies be connected at test points labeled 1.8/3.3/5.0V MOD PIN. These test points may be used to confirm the voltage at the module supply pins when using the on-board supplies. As a further convenience, a small fan is provided for cooling the module. This fan may be disabled by removing its power connector from jumper J10.

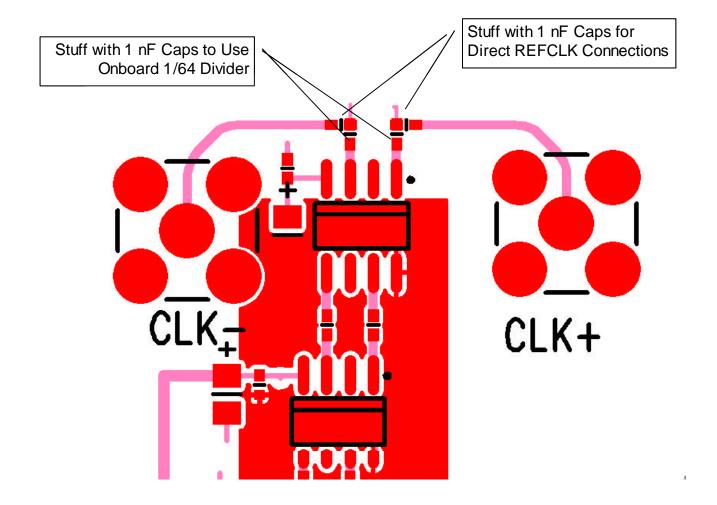

As supplied, the FDB-1022 is configured to accept a 10Gb/s differential REFCLK signal at SMA connectors J5/J6. An onboard divider converts this signal to the 1/64 rate REFCLK the XFP transceiver module requires. Alternatively, the board may be configured to allow a direct connection of a 1/64 clock through SMA connectors J16 and J21. This configuration may be setup by removing the 1nF 0402 capacitors from C11 and C16 and placing them at locations C65 and C66 (see Figure 2).

Indicators and controls are provided for all low-speed and power supply lines. Green LEDs, D1-D8, indicate the power supply state for the evaluation board, XFP module, and switching power supplies. Their assignment is clearly marked with screen-printed text on the board next to each LED. Red LEDs D11, D13, D14, and D15 show the status of the module INTERRUPT, MOD/ABSENT, LOS, and MOD\_NR output lines. Note that D11, INTERRUPT LED, is on when no interrupt is asserted, while it is off when an asserted interrupt has occurred. Further, this operation is similar to that of its counterpart LED on the GUI for the XFP Lab software that accompanies this evaluation board. There, the bright red INT LED indicates

that there is <u>no</u> interrupt asserted and will change to green when an interrupt is asserted.

All the signal lines are available on associated test points. The module PWRDWN, TXDIS, and MODDESEL lines may be manually controlled by switches S1, S3, and S5.

#### **Software Control**

The FDB-1022 evaluation board is supplied with software and a DB-25 cable for communication with a PC parallel port. This cable allows direct communication between the PC and the module via the 2-wire serial bus on pins SCL and SDA. XFP modules respond to 2-wire serial bus address A0h. Additionally, various evaluation board functions may be addressed on other I2C addresses. Contact Finisar for details on these functions.

The software included with the board provides a simple windows-based GUI and allows control and monitoring of the power supply and status functions of the evaluation board itself. Future versions of the software will allow monitoring of the Serial ID, digital diagnostics and status information available in Finisar's XFP transceivers.

### **Specifications**

The Finisar FDB-1022 evaluation board requires a +12V  $\pm 10\%$  power supply at J14. Input signals to the TX+ and TX- connectors should have an amplitude between 140mV and 700mV differential peak-to-peak (70mV to 350mV single-ended). Output signals on the RX+ and RX-connectors will have amplitudes between 180mV and 640mV single-ended.

A 10Gb/s REFCLK may be supplied at J5/J6. The onboard divider requires a signal amplitude of 200–1000 mV differential p-p (100-500mV S.E.). If a direct REFCLK connection is made, a signal of 640-1600 mV differential p-p (320 – 800 mV S.E.) is required.

## Finisar

Figure 1. FDB-1022 - Layout and Connection Locations

# Finisar

Figure 2. Coupling Capacitors for Switching Between Onboard 1/64 REFCLK Divider and Direct External REFCLK Connection