# S1F75510

# Charge-pump DC/DC Converter & Voltage Regulator

#### **■ DESCRIPTION**

The S1F75510 is a power IC designed for use with medium or small capacity TFT–LCD panel modules. A single chip of this IC is capable of generating three different levels of positive and negative output voltages simultaneously, which are necessary to drive the LCD, by use of a single input power of +2.7 through +3.6V. Since the S1F75510 does not require external transistors nor diodes as its voltage conversion circuit, its built-in CMOS transistors constituting a complete charge pump type DC/DC converter, it is most suitable for the

Moreover, the charge pump type DC/DC converter of the S1F75510 can be operated upon the frequencies, which are to be switched over by the mode changing signals, using either of the built-in clock signals or external clock signals optimal to respective cases.

This function can drastically suppress the current consumption of this IC while under light load state, thus exhibiting very high power conversion efficiencies.

#### **■ FEATURES**

- $\bullet$  Self consumption current (normal mode/blank mode) ---- 300  $\mu A$  / 30  $\mu A$  (TBD) Normal mode: Boosting by use of the internal clock

purpose of reducing the current consumption levels of the LCD modules.

Blank mode: Selectable between boosting by use of the internal clock or by use of the external clock.

- Conversion efficiency of the charge pump ------ 90% or more respectively

- Built-in voltage conversion circuits constituted by charge pump type DC/DC converter,

- x2 boosting circuit in the positive direction

- x3 boosting circuit in the positive direction

- x3 boosting circuit in the negative direction

- Built-in voltage stabilizing circuit

- Capable of outputting the positive supply voltage Vout2 for the source driver

- x2 boosting circuit in the positive direction + voltage stabilizing circuit Output voltage: +5.0V ±3% (TBD)

- Capable of outputting the positive supply voltage Vout3 for the gate driver

- x3 boosting circuit in the positive direction

Output voltage: +15V

Vout3 = Vout2 x 3

- Capable of outputting the negative supply voltage Vout4 for the gate driver

- x3 boosting circuit in the negative direction

Output voltage: -10V

$VOUT4 = VOUT2 \times -2$

- Built-in electric charge discharging circuit

- Built-in shut down function

- This IC is not of the radiation resistant design nor of the light resistance design.

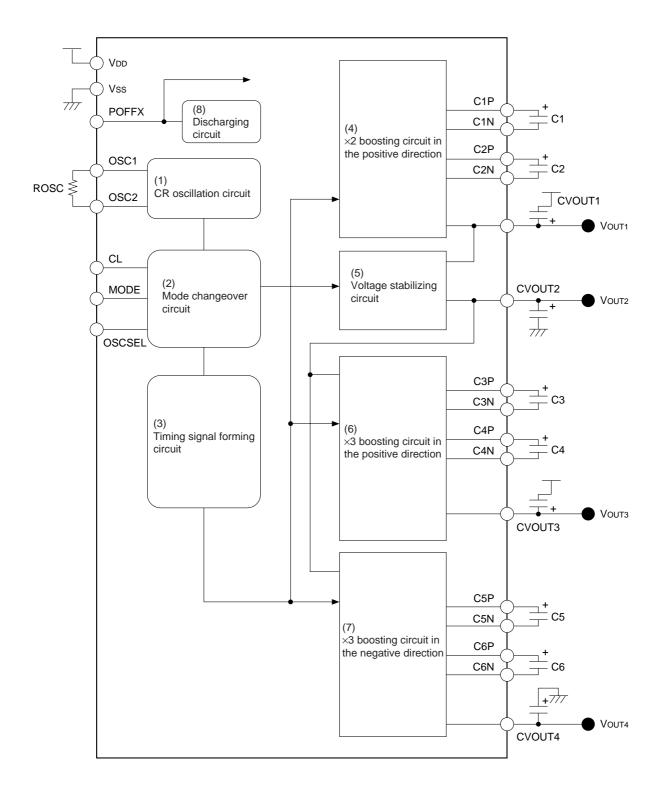

#### **■ BLOCK DIAGRAM**

Fig. 1 Block diagram

#### ■ DESCRIPTIONS FOR THE BLOCK DIAGRAM

#### (1) CR oscillation circuit

The oscillation circuit is constituted by connecting a resistor between the OSC1 pin and the OSC2 pin. The clock signals being generated by this oscillation circuit will become effective as boosting clock signals while the mode changeover signal MODE is on the VDD level (normal mode) or while the mode changeover signal MODE is on the VSS level and, at the same time, when the internal/external clock selection signal OSCSEL is on the VDD level (blank mode · internal clock). When the MODE is set to the VSS level and, at the same time, when the OSCSEL is set to the VSS level (blank mode · external clock), the oscillation will be interrupted.

#### (2) Mode changeover circuit

The operation modes of the boosting circuit and voltage stabilizing circuit are being switched over by the mode changeover signal MODE. Also, it selects the clock signals to feed to the timing signal forming circuit from either of the external clock signals or internal clock signals.

#### (3) Timing signal forming circuit

This circuit generates the charge pump boosting clock signals. This circuit outputs timing signals of the clock type (internal clock or external clock) having been selected by the mode changeover circuit to drive respective boosting circuits. When the shut down signal POFFX is set to the Vss level, the timing signal stops to interrupt the boosting operation.

#### (4) x2 boosting circuit in the positive direction

This circuit makes x2 boosting in the positive direction by charge pump boosting upon the inputted supply voltage VDD – Vss using the Vss potential as the reference voltage. The x2 boosted output will enter into the voltage stabilizing circuit.

#### (5) Voltage stabilizing circuit

This circuit generates the positive supply voltage Vout2 for the source driver. ON the basis of the built-in reference, this circuit stabilizes the output from the above "(4) X2 boosting circuit in the positive direction" by use of the series regulator.

#### (6) x3 boosting circuit in the positive direction

This circuit generates the positive supply voltage VOUT3 for the gate driver. This circuit effects X3 boosting in the positive direction by charge pump boosting upon the voltage VOUT2 – VSS using the VSS potential as the reference voltage.

#### (7) x3 boosting circuit in the negative direction

This circuit generates the negative supply voltage Vout4 for the gate driver. This circuit effects X3 boosting in the negative direction by charge pump boosting upon the voltage Vout2 – Vss using the Vout2 potential as the reference voltage.

#### (8) Electric charge discharging circuit

This circuit discharges the electric charge remaining in the Vout pin and Vout pin to the Vss level. This circuit will work when the POFFX pin is set to the Vss level.

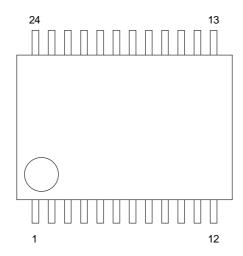

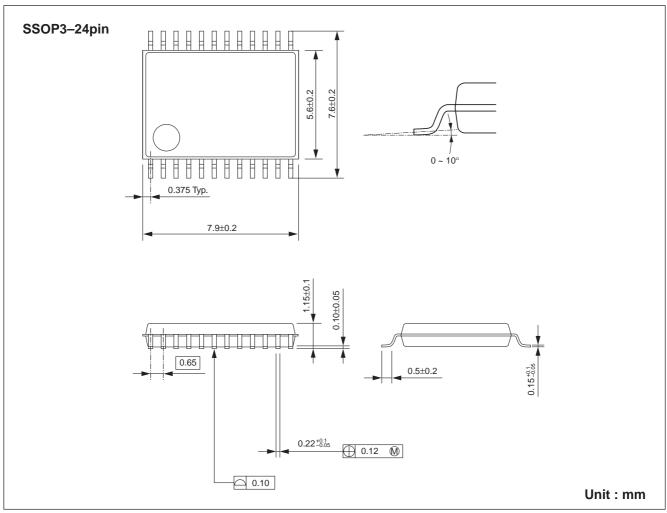

# **■ PIN ASSIGNMENT**

SSOP3-24pin S1F75510M0A0

| Pin No. | Pin name | Pin No. | Pin name |

|---------|----------|---------|----------|

| 1       | C3N      | 13      | MODE     |

| 2       | C3P      | 14      | CL       |

| 3       | C4P      | 15      | POFFX    |

| 4       | C4N      | 16      | OSC1     |

| 5       | VOUT3    | 17      | OSC2     |

| 6       | Vdd      | 18      | OSCSEL   |

| 7       | C1N      | 19      | VOUT2    |

| 8       | C1P      | 20      | VOUT4    |

| 9       | Vout1    | 21      | C6P      |

| 10      | C2P      | 22      | C6N      |

| 11      | C2N      | 23      | C5N      |

| 12      | Vss      | 24      | C5P      |

# **■ PIN DESCRIPTION**

(1) CR oscillation circuit · Mode changeover circuit · Timing signal forming circuit · Electric charge discharging circuit

| Pin name | I/O | Pin No. | Function                                                               |                                                                       |                                                                            |  |  |  |

|----------|-----|---------|------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|

| POFFX    | I   | 15      | This is the sh                                                         | This is the shut down pin. Set it to the VDD level while the IC is in |                                                                            |  |  |  |

|          |     |         | operation. When this signal is set to the Vss level, operations of all |                                                                       |                                                                            |  |  |  |

|          |     |         | the circuits w                                                         | the circuits will be interrupted bringing the IC into the shut down   |                                                                            |  |  |  |

|          |     |         | state. The ele                                                         | ectric charge o                                                       | discharging circuit discharges the electric                                |  |  |  |

|          |     |         | charge remai                                                           | ning in the Vo                                                        | оитз pin and Vouт4 pin to the Vss level.                                   |  |  |  |

| OSC1     | I   | 16      | This is the C                                                          | R oscillation of                                                      | circuit gate input pin. This is the pin to                                 |  |  |  |

|          |     |         | connect the                                                            | scillation res                                                        | sistor. Fix it to the Vss level in case the                                |  |  |  |

|          |     |         | built-in oscilla                                                       | ation circuit w                                                       | rill not be used.                                                          |  |  |  |

| OSC2     | 0   | 17      | This is the C                                                          | R oscillation of                                                      | circuit drain input pin. Connect the osci-                                 |  |  |  |

|          |     |         | llation resisto                                                        | r between th                                                          | is pin and the OSC1 pin.                                                   |  |  |  |

| CL       | I   | 14      | This is the bo                                                         | osting extern                                                         | al clock signal input pin. Input the charge                                |  |  |  |

|          |     |         | pump clock s                                                           | ignals under                                                          | the blank mode into this pin.                                              |  |  |  |

| MODE     | I   | 13      | This is the m                                                          | ode changeo                                                           | ver pin.                                                                   |  |  |  |

| OSCSEL   | I   | 18      | This is the pi                                                         | n for selection                                                       | n between the internal clock and exter-                                    |  |  |  |

|          |     |         | nal clock sigr                                                         | nals.                                                                 |                                                                            |  |  |  |

|          |     |         | MODE                                                                   | OSCSEL                                                                | Function                                                                   |  |  |  |

|          |     |         | HIGH(VDD)                                                              | HIGH(VDD)                                                             | Normal mode                                                                |  |  |  |

|          |     |         |                                                                        | LOW(Vss)                                                              | The boosting clock signals are being                                       |  |  |  |

|          |     |         |                                                                        | 1                                                                     | generated through the internal                                             |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | oscillation.                                                               |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | The built-in oscillation circuit will ope-                                 |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | rate and the voltage stabilizing circuit                                   |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | will operate.                                                              |  |  |  |

|          |     |         | LOW(Vss)                                                               | HIGH(VDD)                                                             | Blank mode (internal oscillation)                                          |  |  |  |

|          |     |         |                                                                        |                                                                       | The boosting clock signals are being                                       |  |  |  |

|          |     |         |                                                                        | 1                                                                     | generated through the internal                                             |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | oscillation.                                                               |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | The built-in oscillation circuit will                                      |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | operate and the voltage stabilizing                                        |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | circuit will operate under low current                                     |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | consumption state.                                                         |  |  |  |

|          |     |         |                                                                        | LOW(Vss)                                                              | Blank mode (external oscillation)                                          |  |  |  |

| 1        |     | i .     |                                                                        |                                                                       |                                                                            |  |  |  |

|          |     |         |                                                                        | 1                                                                     | The boosting clock signals are being                                       |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | The boosting clock signals are being generated by the external clock.      |  |  |  |

|          |     |         |                                                                        | <br>                                                                  |                                                                            |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | generated by the external clock.                                           |  |  |  |

|          |     |         |                                                                        | <br>                                                                  | generated by the external clock.  The built-in oscillation circuit will be |  |  |  |

# S1F75510

# (2) X2 boosting circuit in the positive direction

| Pin name | I/O | Pin No. | Function                                                                                                 |

|----------|-----|---------|----------------------------------------------------------------------------------------------------------|

| VOUT1    | 0   | 9       | This is the output pin of the X2 boosting circuit in the positive direction.                             |

| C1P      | (O) | 8       | This is the pin to connect the positive side of the VOUT1 output voltage generating flying capacitor C1. |

| C1N      | (O) | 7       | This is the pin to connect the negative side of the Vout1 output voltage generating flying capacitor C1. |

| C2P      | (O) | 10      | This is the pin to connect the positive side of the VOUT1 output voltage generating flying capacitor C2. |

| C2N      | (O) | 11      | This is the pin to connect the negative side of the Vout1 output voltage generating flying capacitor C2. |

# (3) Voltage stabilizing circuit

| Pin name | I/O | Pin No. | Function                                                             |  |

|----------|-----|---------|----------------------------------------------------------------------|--|

| Vout1    | I   | 9       | This is the input power pin (+) for the voltage stabilizing circuit. |  |

|          |     |         | This pin is being connected to the output pin of the x2 boosting     |  |

|          |     |         | circuit in the positive direction internally, inside this IC.        |  |

| VOUT2    | 0   | 19      | This is the output pin of the voltage stabilizing circuit.           |  |

# (4) X3 boosting circuit in the positive direction

| Pin name | I/O | Pin No. | Function                                                          |

|----------|-----|---------|-------------------------------------------------------------------|

| VOUT3    | 0   | 5       | This is the output pin of the x3 boosting circuit in the positive |

|          |     |         | direction.                                                        |

| C3P      | (O) | 2       | This is the pin to connect the positive side of the Vout3 output  |

|          |     |         | voltage generating flying capacitor C3.                           |

| C3N      | (O) | 1       | This is the pin to connect the negative side of the Vout3 output  |

|          |     |         | voltage generating flying capacitor C3.                           |

| C4P      | (O) | 3       | This is the pin to connect the positive side of the Vout3 output  |

|          |     |         | voltage generating flying capacitor C4.                           |

| C4N      | (O) | 4       | This is the pin to connect the negative side of the Vout3 output  |

|          |     |         | voltage generating flying capacitor C4.                           |

# (5) x3 boosting circuit in the negative direction

| Pin name | I/O | Pin No. | Function                                                          |

|----------|-----|---------|-------------------------------------------------------------------|

| VOUT4    | 0   | 20      | This is the output pin of the x3 boosting circuit in the negative |

|          |     |         | direction.                                                        |

| C5P      | (O) | 24      | This is the pin to connect the positive side of the Vout4 output  |

|          |     |         | voltage generating flying capacitor C5.                           |

| C5N      | (O) | 23      | This is the pin to connect the negative side of the Vout4 output  |

|          |     |         | voltage generating flying capacitor C5.                           |

| C6P      | (O) | 21      | This is the pin to connect the positive side of the Vout4 output  |

|          |     |         | voltage generating flying capacitor C6.                           |

| C6N      | (O) | 22      | This is the pin to connect the negative side of the Vout4 output  |

|          |     |         | voltage generating flying capacitor C6.                           |

# (6) Power pins

| Pin name | I/O | Pin No. | Function                         |

|----------|-----|---------|----------------------------------|

| VDD      | I   | 6       | This is the input power pin (+). |

| Vss      | I   | 12      | This is the input power pin (–). |

#### **■ FUNCTIONAL DESCRIPTION**

#### Operational description

Generating voltage levels are:

- · Positive boosting supply voltage necessary for the voltage stabilizing circuit (Vout1)

- · Positive stabilized supply voltage necessary for the source driver (Vout2)

- · Positive and negative boosting supply voltages necessary for the gate driver (Vout3 and Vout4)

The Vout1 supply voltage is being generated by the charge pump type DC/DC converter (x2 boosting circuit in the positive direction). It makes x2 boosting in the positive direction of the potential difference occurring between the VDD – Vss using the Vss potential as the reference voltage.

The Vout2 supply voltages is being generated by the series regulator stabilizing the potential difference occurring between the Vout1 – Vss using the Vss potential as the reference voltage.

The Vouts supply voltage is being generated by the charge pump type DC/DC converter (x3 boosting circuit in the positive direction). It makes x3 boosting in the positive direction of the potential difference occurring between the Vout2 – Vss using the Vss potential as the reference voltage.

The Vout4 supply voltage is being generated by the charge pump type DC/DC converter (X3 boosting circuit in the negative direction). It makes X3 boosting in the negative direction of the potential difference occurring between the Vout2 – Vss using the Vout2 potential as the reference voltage.

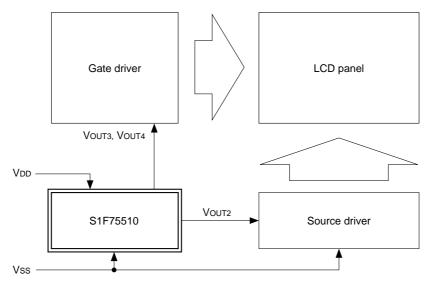

Indicated below is the system configuration diagram for the power circuit.

Fig. 2 System configuration diagram

$\times 3$  boosting in the positive direction Vouт3 ×2 boosting in the positive direction Vou<sub>1</sub> Vou<sub>t2</sub> Voltage stabilizing VDD Source driver Gate driver Vss VOUT4 ×3 boosting in the negative direction Power Supply IC (S1F75510)

Indicated below is the potential correlation diagram inside the system as is shown in Fig. 2.

Fig. 3 Potential correlation diagram inside the system

#### CR oscillation circuit

The S1F75510 incorporates a CR oscillation circuit as the oscillation circuit for the boosting clock signals. This circuit is to be used connecting the external oscillation resistor ROSC between the OSC1 pin and the OSC2 pin. The CR oscillation circuit will stop operation under the blank mode and when using the external clock (MODE = Vss level and OSCSEL = Vss level) or under the shut down state (POFFX = Vss level). Also, the oscillation will be interrupted by setting the OSC1 pin to the VSS level and, at the same time, setting the OSC2 pin into open state.

As the external oscillation resistance, we recommend use of ROSC = 1 M $\Omega$ .

#### Mode changeover circuit

By external settings of the mode changeover signal MODE and the internal/external clock selection signal OSCSEL, the charge pump boosting can be driven under optimum frequencies. Since the current consumption of the IC can be suppressed drastically under the blank mode, it is possible to achieve high power conversion efficiency even under light load operations.

| MODE pin       | OSCSEL<br>pin         | Mode name   | Max. output                                    | current                 | Built-in CR oscillation circuit | Built in voltage stabilizing circuit |

|----------------|-----------------------|-------------|------------------------------------------------|-------------------------|---------------------------------|--------------------------------------|

| HIGH(VDD)      | HIGH(VDD)<br>LOW(VSS) | Normal mode | VOUT2:(10mA)<br>VOUT3:(100μA)<br>VOUT4:(100μA) | (TBD)<br>(TBD)<br>(TBD) | In operation                    | In normal operation                  |

| 1 (0)(() (0.5) | HIGH(VDD)             | Blank mode  | VOUT2:(200μA)<br>VOUT3:(10μA)<br>VOUT4:(10μA)  | (TBD)<br>(TBD)<br>(TBD) | In operation                    | In low current consumption operation |

| LOW(Vss)       | LOW(Vss)              | Blank mode  | VOUT2:(200μA)<br>VOUT3:(10μA)<br>VOUT4:(10μA)  | (TBD)<br>(TBD)<br>(TBD) | In standstill                   | In low current consumption operation |

# Timing signal forming circuit

This circuit generates the clock signals necessary for charge pump boosting using the internal oscillation or using external clock signals.

Two different types of capacitors are being used as the charge pump capacitors, one being the flying capacitor which shifts between the charging state and the discharging state and the other being the smoothing capacitor which preserves the electric charge. The operating frequency of the flying capacitor should equal to the frequency of the charge pump clock being generated by this timing signal forming circuit.

Under the shut down state (POFFX = Vss level), the charge pump clock stops operation and all the boosting operations of this IC will be interrupted. The operating frequencies of the flying capacitor are as follows.

| MODE pin           | OSCSEL    | Mode name      | Operating frequencies of the flying capacitor |                        |                        |  |  |

|--------------------|-----------|----------------|-----------------------------------------------|------------------------|------------------------|--|--|

| MODE pill          | pin       | Wode name      | ×2 boosting in                                | ×3 boosting in         | ×3 boosting in         |  |  |

|                    | ı         |                | the positive direction                        | the positive direction | the negative direction |  |  |

| HICH(\/pp)         | HIGH(VDD) | Normal mode    | (TBD) kHz                                     | (TBD) kHz              | (TBD) kHz              |  |  |

| HIGH(VDD) LOW(Vss) | LOW(Vss)  | Normal mode    | (Typ.10 kHz)                                  | (Typ.10 kHz)           | (Typ.10 kHz)           |  |  |

|                    | HIGH(VDD) | DD) Blank mode | (TBD) kHz                                     | (TBD) kHz              | (TBD) kHz              |  |  |

|                    |           |                | (Typ.625 Hz)                                  | (Typ.625 Hz)           | (Typ.625 Hz)           |  |  |

| LOW(Vss)           |           | Blank mode     | (TBD) Hz                                      | (TBD) Hz               | (TBD) Hz               |  |  |

|                    | LOW(Vss)  | CL=(TBD) Hz    | (Min.150 Hz)                                  | (Min.150 Hz)           | (Min.150 Hz)           |  |  |

|                    | <br>      | (Min.300 Hz)   | (181111. 130 112)                             | (101111.130 112)       | (101111.130112)        |  |  |

#### X2 boosting circuit in the positive direction

The X2 boosting circuit in the positive direction generates the voltages necessary to input into the voltage stabilizing circuit. It makes X2 boosting in the positive direction of the potential difference occurring between the VDD – Vss using the Vss potential as the reference voltage to output through the Vout1 pin.

Under the blank mode, since the boosting operation is being carried out with the flying capacitor C2 stopping its operation, the current consumption can be suppressed accordingly.

The theoretical equation (output voltage value under the idealistic non-load state) for the Vout1 becomes as follows:

$$VOUT1 = (VDD - VSS) \times 2$$

Actually, when a load is connected to the Vout1, the output voltage will drop to the value represented by the equation indicated below.

Vout1 = (VDD - Vss) x 2 - RVout1 x IVout1

RVout1: Output impedance of the x2 boosting circuit in the positive direction

IVOUT1: Load current

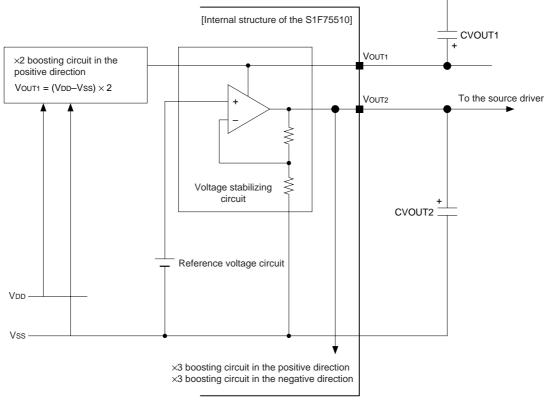

#### Voltage stabilizing circuit

The voltage stabilizing circuit stabilizes the voltage being output through the VOUT1 pin by the series regulator to output the positive supply voltage for the source driver through the VOUT2 pin.

The output voltage setting for the Vout pin should be Typ. +5.0V (TBD).

Since it is necessary to let the Vout1 satisfy the correlation of "Vout1 > Vout2 + 0.1V" in order to obtain normal output voltage value through the Vout2 pin, use the IC within the range of the max. load current (7.3).

The circuit configuration · connection diagram for the voltage stabilizing circuit is as follows:

Fig. 4 Configuration diagram of the voltage stabilizing circuit

#### X3 boosting circuit in the positive direction

The x3 boosting circuit in the positive direction generates the Vout3 output voltage, means the positive supply voltage for the gate driver. It makes x3 boosting in the positive direction of the potential difference occurring between the Vout2 – Vss using the Vss potential as the reference voltage, by charge pump boosting, to output through the Vout3 pin.

The theoretical equation (output voltage value under the idealistic non-load state) for the Vout3 becomes as follows:

```

VOUT3 = (VOUT2 - VSS) \times 3

```

Actually, when a load is connected to the VOUT3, the output voltage will drop to the value represented by the equation indicated below.

```

Vout3 = (Vout2 - Vss) x 3 - (RVout3 x IVout3)

```

RVout3: Output impedance of the x3 boosting circuit in the positive direction

IVOUT3: Load current

It means that the Vout3 voltage will drop by the load.

To acquire desired output voltage, use the IC within the range of the specified load (7.3).

#### ● ×3 boosting circuit in the negative direction

The X3 boosting circuit in the negative direction generates the Vout3 output voltage, means the negative supply voltage for the gate driver. It makes X3 boosting in the negative direction of the potential difference occurring between the Vout2 – Vss using the Vout2 potential as the reference voltage, by charge pump boosting, to output through the Vout4 pin.

The theoretical equation (output voltage value under the idealistic non-load state) for the Vout4 becomes as follows:

```

VOUT4 = (VOUT2 - VSS) X (-2) (The voltage value using the VSS potential as the reference voltage)

```

Actually, when a load is connected to the VOUT4, the output voltage will drop to the value represented by the equation indicated below.

```

VOUT4 = (VOUT2 - VSS) \times (-2) - (RVOUT4 \times IVOUT4)

```

RVout4: Output impedance of the x3 boosting circuit in the negative direction

IVout4: Load current

It means that the VouT4 voltage will drop by the load.

To acquire desired output voltage, use the IC within the range of the specified load (7.3).

#### Electric charge discharging circuit

The electric charge discharging circuit discharges the electric charge remaining in the Vout3 pin and Vout4 pin to the Vss level.

This circuit starts operation when the POFFX pin is set to the Vss level.

The discharging sequence and the discharging impedance are according to the (TBD).

#### ■ ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol |        | ing       | l l m ! t | Applicable         | Remarks   |  |

|-----------------------|--------|--------|-----------|-----------|--------------------|-----------|--|

| item                  | Symbol | Min.   | Max.      | Unit      | pin                | Remarks   |  |

| Input supply voltage  | VDD    | - 0.3  | 4.0       | V         | VDD                | _         |  |

| Output voltage 1      | VOUT1  | - 0.3  | 7.5       | V         | VOUT1              | _         |  |

| Output voltage 2      | VOUT2  | - 0.3  | 7.5       | V         | VOUT2              | _         |  |

| Output voltage 3      | VOUT3  | - 0.3  | 22.5      | V         | VOUT3              | _         |  |

| Output voltage 4      | VOUT4  | - 15.0 | 0.3       | V         | VOUT4              | _         |  |

| Input pin voltage 1   | VIN    | - 0.3  | VDD + 0.3 | V         | <note 1=""></note> | _         |  |

| Input current         | IVDD   | _      | (TBD)     | mA        | VDD                |           |  |

| Output current 1      | IVout1 | _      | (TBD)     | mA        | VOUT1              | _         |  |

| Output current 2      | IVOUT2 | _      | (TBD)     | mA        | VOUT2              | _         |  |

| Output current 3      | IVOUT3 | _      | (TBD)     | mA        | VOUT3              | _         |  |

| Output current 4      | IVOUT4 | _      | (TBD)     | mA        | VOUT4              | _         |  |

| Allowable dissipation | PD     | _      | (TBD)     | mW        | _                  | Ta ≤ 55°C |  |

| Operating temperature | Topr   | - 30   | 85        | °C        | _                  | _         |  |

| Storage temperature   | Tstg   | - 55   | 150       | °C        | _                  | _         |  |

| Soldering temperature | Tsol   | _      | 260-10    | °C-s      | _                  | At leads  |  |

| and time              |        |        |           |           |                    |           |  |

<sup>&</sup>lt;Note 1> The applicable pins are POFFX, OSC1, CL, MODE and OSCSEL.

<sup>&</sup>lt;Note 2> Do not apply external voltage to the output pins and the pin connecting to the capacitor.

<sup>&</sup>lt;Note 3> Use of the IC under any conditions exceeding the above absolute maximum ratings may cause malfunctioning or permanent breakdown. Or, even if the IC may operate normally temporarily, the reliability may greatly drop.

#### **■ ELECTRICAL CHARACTERISTICS**

#### DC characteristics

In case particular designations are not made (Note 1): Ta = -10 to  $+70^{\circ}C$

| Itam                          | Or week al | Symphol Conditions     |        | Rating |        |      |         |

|-------------------------------|------------|------------------------|--------|--------|--------|------|---------|

| Item                          | Symbol     | Conditions             | Min.   | Тур.   | Max.   | Unit | Remarks |

| Input supply voltage          | VDD        | Applicable pin: VDD    | (TBD)  | 3.0    | 3.6    | V    | _       |

| High level input voltage      | VIH        | _                      | 0.8VDD | _      | VDD    | V    | 2       |

| Low level input voltage       | VIL        | _                      | 0      | _      | 0.2VDD | V    | 2       |

| Input leak current 1          | ILKI1      | $Vss \le Vi \le Vdd$ , | - 0.5  | _      | 0.5    | μΑ   | 2       |

|                               |            | VDD = (TBD) to 3.6V    |        |        |        |      |         |

| Current consumption 1         | IOPR1      | VDD = 3.0V, no load    | _      | (TBD)  | (TBD)  | μΑ   | _       |

|                               |            | Under the normal mode  |        | (300)  |        |      |         |

| Current consumption 2         | IOPR2      | VDD = 3.0V, no load    | _      | (TBD)  | (TBD)  | μА   | _       |

|                               |            | Under the blank mode   |        | (30)   |        |      |         |

|                               |            | CL = (TBD) kHz         |        |        |        |      |         |

| Power conversion efficiency 1 | Peff1      | VDD = 3.0V             | (TBD)  | (TBD)  | (TBD)  | %    | 3       |

| (Overall efficiency including |            | Under the normal mode  |        |        |        |      |         |

| the stabilized outputs)       |            |                        |        |        |        |      |         |

| Power conversion efficiency 2 | Peff2      | VDD = 3.0V             | (TBD)  | (TBD)  | (TBD)  | %    | 4       |

| (Overall efficiency including |            | Under the blank mode   |        |        |        |      |         |

| the stabilized outputs)       |            | CL = (TBD) kHz         |        |        |        |      |         |

| Resting current               | IQ         | VDD = 3.6V             | _      | _      | (TBD)  | μΑ   | _       |

|                               |            | POFFX = LOW            |        |        | (1.0)  |      |         |

<Note 1> Conditions on the operation mode, external parts constant, pins, etc. in case particular designations are not made are as follows.

Connection and parts constant : Standard connection 1, 10.1

MODE pin : MODE = HIGH (Normal mode)

CL pin : CL = LOW (Fixed voltage)

- <Note 2> The applicable pins are XDIS, SSLP, PCK1 and CNT

- <Note 3> Load conditions: IVOUT2 = (TBD)mA, IVOUT3 = (TBD)μA, IVOUT4 = (TBD)μA

Conversion efficiency = [(VOUT2 × IVOUT2) + (VOUT3 × IVOUT3) + (VOUT4 × IVOUT4)] / (VDD\* × IVDD\*) × 100

- <Note 4> Load conditions: IVOUT2 = (TBD) $\mu$ A, IVOUT3 = (TBD) $\mu$ A, IVOUT4 = (TBD) $\mu$ A Conversion efficiency = [(VOUT2 × IVOUT2) + (VOUT3 × IVOUT3) + (VOUT4 × IVOUT4)] / (VDD\* × IVDD\*) × 100

# ● Characteristics of ×2 boosting in the positive direction + stabilized output

$Ta = -10 \text{ to } +70^{\circ}C$

| lto un                    | Symbol Conditions |                 |        | l lm!4 | Damada |      |         |

|---------------------------|-------------------|-----------------|--------|--------|--------|------|---------|

| Item                      | Symbol            | Conditions      | Min.   | Тур.   | Max.   | Unit | Remarks |

| Vout output impedance     | RVout1-1          | Applicable pin: |        | (TBD)  | (TBD)  | Ω    | 5       |

| (Normal mode)             |                   | VOUT1           |        |        |        |      |         |

| Vout output impedance     | RVout1-2          | Applicable pin: |        | (TBD)  | (TBD)  | Ω    | 6       |

| (Blank mode)              |                   | VOUT1           |        |        |        |      |         |

| VOUT2                     | VOUT2             | Applicable pin: | (TBD)  | (TBD)  | (TBD)  | V    | 7       |

| Stabilized output voltage |                   | VOUT2           | (4.90) | (5.00) | (5.20) |      |         |

| Vout2 Stabilized output   | RVout2            | Applicable pin: | _      | _      | 10     | Ω    | 8       |

| saturated resistance      |                   | VOUT2           |        |        |        |      |         |

<sup>&</sup>lt;Note 5> VDD = (TBD)V to 3.6V, Load condition: IVOUT1 = (TBD)mA

# ● Characteristics of ×3 boosting in the positive direction and ×3 boosting in he negativet direction

$Ta = -10 \text{ to } +70^{\circ}C$

| Item                   | Symbol   | Conditions      | Rating |       |       | Unit | Domorko |

|------------------------|----------|-----------------|--------|-------|-------|------|---------|

|                        |          |                 | Min.   | Тур.  | Max.  | Unit | Remarks |

| Vouts output impedance | RVout3-1 | Applicable pin: | _      | (TBD) | (TBD) | Ω    | 9       |

| (Normal mode)          |          | VOUT3           |        |       |       |      |         |

| Vout3 output impedance | RVout3-2 | Applicable pin: | _      | (TBD) | (TBD) | Ω    | 10      |

| (Blank mode)           |          | VOUT3           |        |       |       |      |         |

| Vout output impedance  | RVout4-1 | Applicable pin: | _      | (TBD) | (TBD) | Ω    | 11      |

| (Normal mode)          |          | VOUT4           |        |       |       |      |         |

| Vout output impedance  | RVout4-2 | Applicable pin: | _      | (TBD) | (TBD) | Ω    | 12      |

| (Blank mode)           |          | VOUT4           |        |       |       |      |         |

<sup>&</sup>lt;Note 9> VDD = (TBD)V to 3.6V, Load condition: IVOUT3 = (TBD) $\mu$ A

<sup>&</sup>lt;Note 6> VDD = (TBD)V to 3.6V, Load condition: IVOUT1 = (TBD)mA

<sup>&</sup>lt;Note 7> VDD = (TBD)V to 3.6V, Load condition: IVOUT2 = (TBD)mA

<sup>&</sup>lt;Note 8> VDD = (TBD)V to 3.6V, Load condition: IVOUT2 = (TBD)mA

<sup>&</sup>lt;Note 10> VDD = (TBD)V to 3.6V, Load condition: IVOUT3 = (TBD) $\mu$ A

<sup>&</sup>lt;Note 11> VDD = (TBD)V to 3.6V, Load condition: IVOUT4 = (TBD) $\mu$ A

<sup>&</sup>lt;Note 12> VDD = (TBD)V to 3.6V, Load condition: IVOUT4 = (TBD) $\mu$ A

# AC characteristics

Measurement conditions for the AC characteristics

· Input signal level VIH = 0.8 VDD (V)

VIL = 0.2 VDD(V)

$\cdot$  Input signal rise time Tr = Max. 100ns

· Input signal fall time Tf = Max. 100ns

VDD = (TBD) to 3.6V, VSS = 0V

$Ta = -10 \text{ to } +70^{\circ}C$

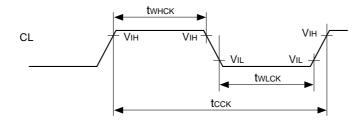

# CL inputting timing

| lt a ma                | Symbol | Rating |       |       | l lni4 | Applicable | Pomorko |  |

|------------------------|--------|--------|-------|-------|--------|------------|---------|--|

| Item                   |        | Min.   | Тур.  | Max.  | Unit   | pin        | Remarks |  |

| CL cycle               | tcck   | (TBD)  | (TBD) | (TBD) | μs     |            |         |  |

| CL High pulse duration | twnck  | (TBD)  | _     | _     | ns     | CL         | _       |  |

| CL Low pulse duration  | twick  | (TBD)  | _     | _     | ns     |            |         |  |

17

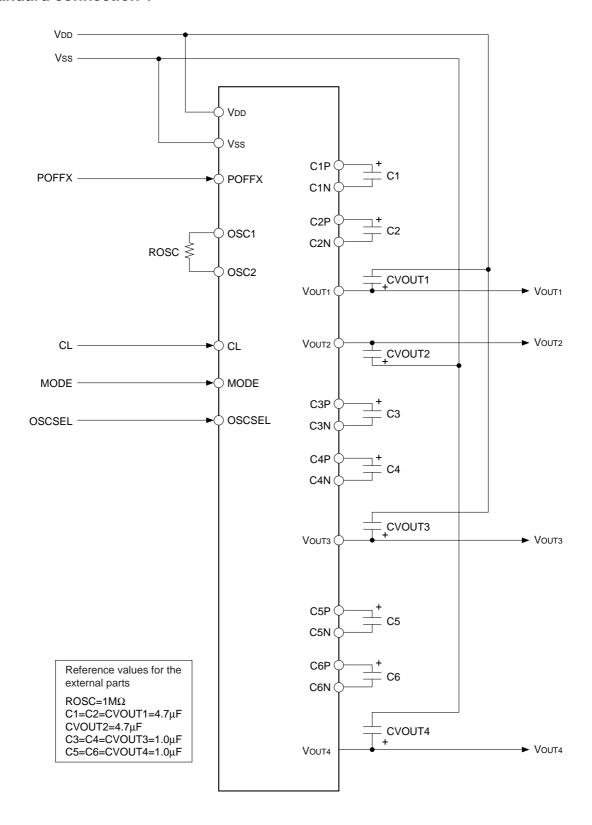

# ■ REFERENCE EXTERNAL CONNECTION (AN EXAMPLE)

# Standard connection 1

#### **■ DIMENSIONAL OUTLINE DRAWING**

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 2001, All rights reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

#### **SEIKO EPSON CORPORATION**

ELECTRONIC DEVICES MARKETING DIVISION

IC Marketing & Engineering Group

ED International Marketing Department Europe & U.S.A

421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5812 FAX: 042-587-5564

ED International Marketing Department Asia

421-8 Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5110

■ EPSON Electronic Devices Website http://www.epson.co.jp/device/