The following document contains information on Cypress products. Although the document is marked with the name "Broadcom", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

#### CONTINUITY OF SPECIFICATIONS

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

#### CONTINUITY OF ORDERING PART NUMBERS

Cypress continues to support existing part numbers. To order these products, please use only the Ordering Part Numbers listed in this document.

#### FOR MORE INFORMATION

Please visit our website at www.cypress.com or contact your local sales office for additional information about Cypress products and services.

#### **OUR CUSTOMERS**

Cypress is for true innovators - in companies both large and small.

Our customers are smart, aggressive, out-of-the-box thinkers who design and develop game-changing products that revolutionize their industries or create new industries with products and solutions that nobody ever thought of before.

#### **ABOUT CYPRESS**

Founded in 1982, Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, home automation and appliances, consumer electronics and medical products. Cypress's programmable systems-onchip, general-purpose microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first.

Cypress is committed to providing customers with the best support and engineering resources on the planet enabling innovators and out-of-the-box thinkers to disrupt markets and create new product categories in record time. To learn more, go to www.cypress.com.

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised September 19, 2016

# BROADCOM

# BCM43236/BCM43236B

# 2.4 GHz/5 GHz IEEE802.11n MAC/PHY/Radio Chip

#### GENERAL DESCRIPTION

The BCM43236/BCM43236B is a dual-band (2.4 GHz and 5 GHz) IEEE 802.11n-compliant MAC/PHY/Radio complete system-on-a-chip with 2.4 GHz and 5 GHz internal PAs. The device enables development of USB 2.0- or HSIC-based IEEE 802.11n WLAN client and router subsystem solutions. The BCM43236/ BCM43236B addresses all WLAN markets that deliver high throughput and extended range of the Broadcom second-generation MIMO solution. With MIMO, information is bidirectional over two or more antennas simultaneously using the same frequency band thus providing greater range and increasing throughput, while maintaining compatibility with legacy IEEE 802.11a/b/g devices. This is accomplished by a combination of enhanced MAC and PHY implementations including spatial transmitter/ receiver multiplexing modes and advanced DSP techniques to improve receive sensitivity.

#### 43236B Enhancements:

256 KB ROM with WLAN driver mapped to support CPU host offload for low-end SoC platforms. Improved radio for better band edge and output power performance. Open Source Linux driver support.

The BCM43236/BCM43236B architecture with its fully integrated dual-band radio transceiver supports 2 × 2 antennas for Layer 2 throughput of over 200 Mbps. State-of-the-art security is provided by industry standardized system support for WPA<sup>™</sup>, WPA2<sup>™</sup> (IEEE 802.11i), and hardware-accelerated AES encryption/ decryption, coupled with TKIP and IEEE 802.1X support. Embedded hardware acceleration enables increased performance and significant reduction in host-CPU utilization in both client and access point configurations. The BCM43236/BCM43236B also supports Broadcom's widely accepted and deployed WPS for ease-of-use wireless secured networks.

#### FEATURES

- IEEE 802.11n-compliant

- 2.4 GHz and 5 GHz internal PA

- Two-stream spatial multiplexing up to 300 Mbps

- Uses on-chip OTP (One-Time Programmable) memory instead of SROM for substantial RBOM savings.

- Supports MCS 0–15 and MCS 32 modulation and coding rates.

- Supports 20 MHz and 40 MHz channels with optional SGI.

- Support for STBC in both TX and RX

- Greenfield, mixed mode, and legacy modes supported

- Full IEEE 802.11a/b/g legacy compatibility with enhanced performance.

- Supports one USB 2.0 host or one 480 MHz HSIC port.

- UART and JTAG interface, up to eight GPIOs.

- Supports up to 32 MB of serial flash memory.

- ARM<sup>®</sup> Cortex-M3<sup>™</sup> CPU core plus 256 KB ROM and 448 KB RAM.

- 256 KB ROM supports driver ROMLIB of the latest driver for CPU host offload functionality.

- Supports Broadcom's OneDriver™ software.

- Supports WHQL certified drivers for Windows<sup>®</sup> Vista 32- and 64-bit, Windows<sup>®</sup> XP, and Windows 2000 operating systems for client applications.

- Supports Linux<sup>®</sup> and VxWorks<sup>®</sup> for access point and router applications.

- Comprehensive wireless network security support that includes WPA, WPA2, and AES encryption/ decryption coupled with TKIP and IEEE 802.1X support.

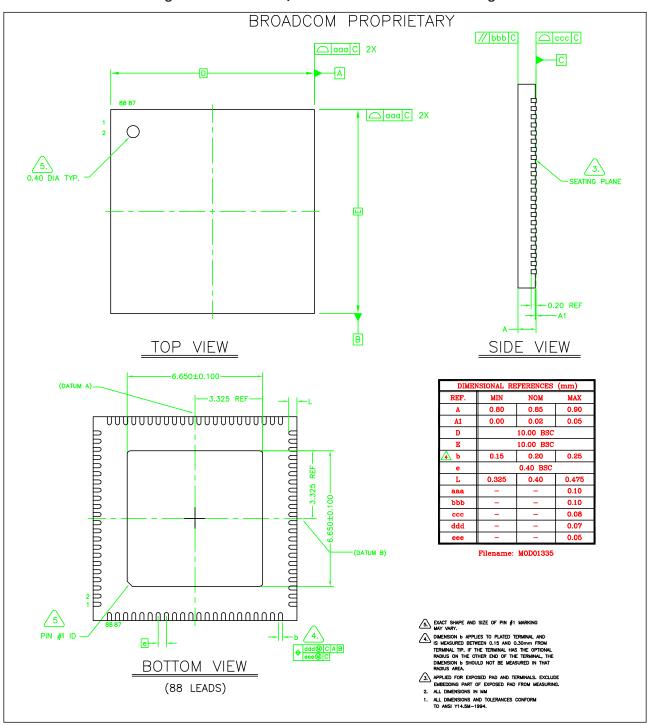

- BCM43236/BCM43236B package: 10 mm x 10 mm 88-pin QFN

#### APPLICATIONS

- USB 2.0 dongles

- HSIC media modules

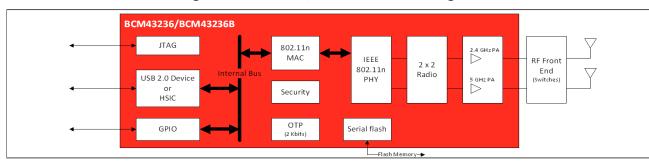

#### Figure 1: BCM43236/BCM43236B Block Diagram

Not Recommended for New Designs

Broadcom Corporation 5300 California Avenue Irvine, CA 92617

© 2013 by Broadcom Corporation All rights reserved Printed in the U.S.A.

Broadcom<sup>®</sup>, the pulse logo, Connecting everything<sup>®</sup>, and the Connecting everything logo are among the trademarks of Broadcom Corporation and/or its affiliates in the United States, certain other countries and/or the EU. Any other trademarks or trade names mentioned are the property of their respective owners.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed, intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations, pollution control, hazardous substances management, or other high-risk application. BROADCOM PROVIDES THIS DATA SHEET "AS-IS," WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT.

### **Revision History**

| Revision             | Date     | Change Description                                           |

|----------------------|----------|--------------------------------------------------------------|

| 002-14912 Rev *D     | 09/19/16 | Parts in this Datasheet are not recommended for new designs. |

| 43236_43236B-DS103-R | 09/16/13 | Updated:                                                     |

|                      |          | • Table 3: "Signal Descriptions," on page 22.                |

| 43236_43236B-DS102-R | 03/06/12 | Added:                                                       |

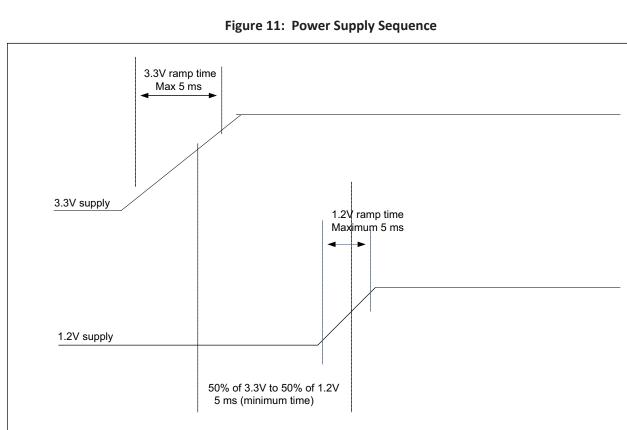

|                      |          | • Figure 11: "Power Supply Sequence," on page 37.            |

| 43236_43236B-DS101-R | 10/14/11 | Updated:                                                     |

|                      |          | • Table 5: "Absolute Maximum Ratings," on page 26.           |

| 43236_43236B-DS100-R | 6/24/11  | Initial release                                              |

# **Table of Contents**

| Recommended Operating Conditions and DC Characteristics |    |

|---------------------------------------------------------|----|

| Absolute Maximum Ratings                                | 27 |

| Section 5: Electrical Characteristics                   | 27 |

| Strapping Options                                       | 26 |

| Package Signal Descriptions                             | 22 |

| Section 4: Signal and Pin Descriptions                  | 22 |

| Signals by Pin Number                                   | 21 |

| BCM43236/BCM43236B 88-Pin QFN Assignments               | 20 |

| Section 3: Pin Assignments                              |    |

| Calibration                                             | 19 |

| Transmitter Path                                        |    |

| Receiver Path                                           |    |

| Dual-Band Radio Transceiver                             | 19 |

| IEEE 802.11n PHY Description                            | 17 |

| IEEE 802.11n MAC Description                            |    |

| Crystal Oscillator                                      | 14 |

| USB/HSIC Interface                                      | 13 |

| Serial Flash Interface                                  | 12 |

| UART Interface                                          | 12 |

| JTAG Interface                                          |    |

| OTP                                                     |    |

| Bluetooth Coexistence Interface                         |    |

| GPIO Interface                                          |    |

| Reset                                                   |    |

| Voltage Regulators                                      |    |

| Power Management                                        |    |

| Global Functions                                        |    |

| Section 2: Functional Description                       | 11 |

| Section 1: Introduction                                 | 9  |

| Technical Support                                       | 8  |

| Acronyms and Abbreviations                              | 8  |

| Purpose and Audience                                    | 8  |

| About This Document                                     | 8  |

| Current Consumption from the 3.3V Supply                                         | 28 |

|----------------------------------------------------------------------------------|----|

| Current Consumption from the 1.2V Supply                                         | 28 |

| HSIC Characteristics                                                             | 29 |

| Section 6: RF Specifications                                                     | 30 |

| 2.4 GHz Band General RF Specifications                                           | 30 |

| 2.4 GHz Band Receiver RF Specifications                                          | 31 |

| 2.4 GHz Band Transmitter RF Specifications                                       | 32 |

| 2.4 GHz Band Local Oscillator Specifications                                     | 32 |

| 5 GHz Band Receiver RF Specifications                                            | 33 |

| 5 GHz Band Transmitter RF Specifications                                         | 34 |

| 5 GHz Band Local Oscillator Frequency Generator Specifications                   | 34 |

| On-Chip Regulator Power Supply Characteristics                                   | 35 |

| Section 7: Timing Characteristics                                                | 36 |

| Reset and Clock Timing Diagram                                                   | 36 |

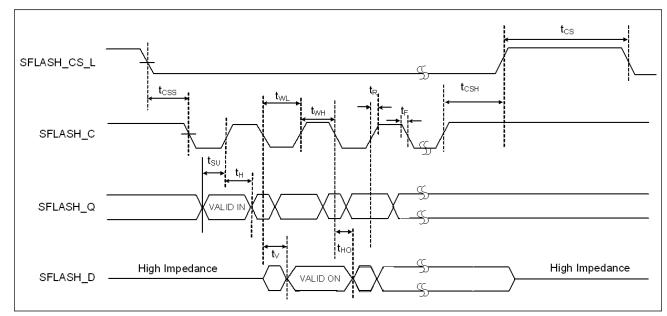

| Serial Flash Timing Diagram                                                      | 37 |

| Section 8: Thermal Information                                                   | 39 |

| Junction Temperature Estimation and PSI <sub>JT</sub> Versus Theta <sub>JC</sub> | 39 |

| Section 9: Package Information                                                   | 40 |

| Section 10: Ordering Information                                                 | 41 |

# **List of Figures**

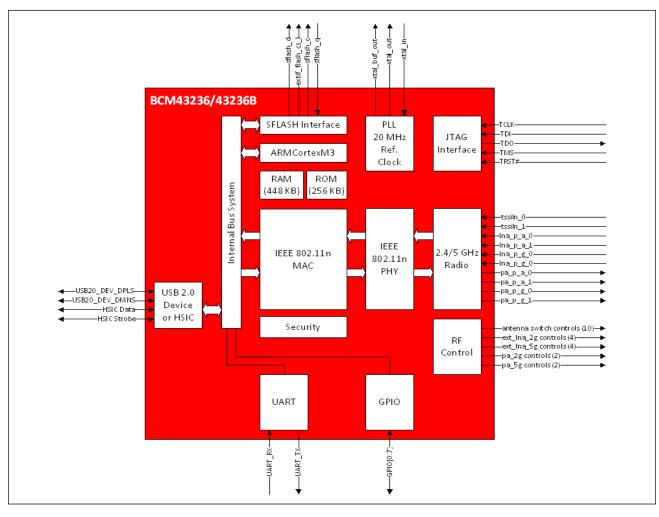

| Figure 1: | BCM43236/BCM43236B Block Diagram                              | 2   |

|-----------|---------------------------------------------------------------|-----|

| Figure 2: | MIMO System Diagram Showing 2 × 2 Antenna Configuration       | 9   |

| Figure 3: | Functional Block Diagram                                      | .10 |

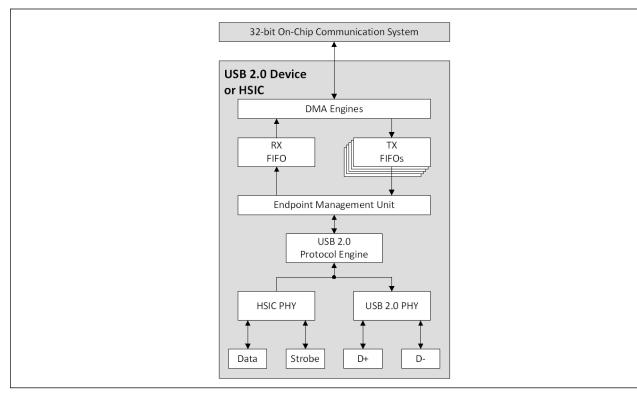

| Figure 4: | USB 2.0 Device/HSIC Core Block Diagram                        | .13 |

| Figure 5: | Recommended Oscillator Configuration                          | .15 |

| Figure 6: | Enhanced MAC Block Diagram                                    | .16 |

| Figure 7: | PHY Block Diagram                                             | .18 |

| Figure 8: | BCM43236/BCM43236B 88-Pin QFN Package                         | .20 |

| Figure 9: | Timing for the Optional External Power-On Reset               | .36 |

| Figure 10 | : Serial Flash Timing Diagram (STMicroelectronics-Compatible) | .37 |

| Figure 11 | : Power Supply Sequence                                       | .38 |

| Figure 12 | : BCM43236/BCM43236B Mechanical Drawing                       | .40 |

## **List of Tables**

| Table 1:  | Crystal Oscillator Requirements14                              |

|-----------|----------------------------------------------------------------|

| Table 2:  | Pin Assignments21                                              |

| Table 3:  | Signal Descriptions22                                          |

| Table 4:  | Strapping Options                                              |

| Table 5:  | Absolute Maximum Ratings27                                     |

| Table 6:  | Recommended Operating Conditions and DC Characteristics        |

| Table 7:  | Current Consumption from 3.3V Supply28                         |

| Table 8:  | Current Consumption from 1.2V Supply28                         |

| Table 9:  | HSIC Characteristics                                           |

| Table 10: | 2.4 GHz Band General RF Specifications                         |

| Table 11: | 2.4 GHz Band Receiver RF Specifications                        |

| Table 12: | 2.4 GHz Band Transmitter RF Specifications32                   |

| Table 13: | 2.4 GHz Band Local Oscillator Specifications                   |

| Table 14: | 5 GHz Band Receiver RF Specifications                          |

| Table 15: | 5 GHz Band Transmitter RF Specifications                       |

| Table 16: | 5 GHz Band Local Oscillator Frequency Generator Specifications |

| Table 17: | On-Chip Regulator Power Supply Characteristics                 |

| Table 18: | Ext_por and Clock Timing                                       |

| Table 19: | Serial Flash Timing                                            |

| Table 20: | 88-Pin QFN Thermal Characteristics                             |

| Table 21: | Ordering Information41                                         |

### About This Document

### **Purpose and Audience**

This document provides details of the functional, operational, and electrical characteristics of the Broadcom<sup>®</sup> BCM43236/BCM43236B. It is intended for hardware design, application, and OEM engineers.

### **Acronyms and Abbreviations**

In most cases, acronyms and abbreviations are defined on first use.

For a comprehensive list of acronyms and other terms used in Broadcom documents, go to: http://www.broadcom.com/press/glossary.php.

### **Technical Support**

Broadcom provides customer access to a wide range of information, including technical documentation, schematic diagrams, product bill of materials, PCB layout information, and software updates through its customer support portal (<u>https://support.broadcom.com</u>). For a CSP account, contact your Sales or Engineering support representative.

In addition, Broadcom provides other product support through its Downloads & Support site (http://www.broadcom.com/support/).

# **Section 1: Introduction**

The BCM43236/BCM43236B chips are the latest innovative chips from Broadcom<sup>®</sup> based on IEEE 802.11n. These chips are designed to take current WLAN systems to the next level of higher performance and greater range with Multiple Input Multiple Output (MIMO) technology, as shown in Figure 2. The IEEE 802.11n standard more than doubles the spectral efficiency compared to that of current IEEE 802.11a/g WLANs.

Employing a native 32-bit bus with Direct Memory Access (DMA) architecture, the BCM43236/BCM43236B chips offer significant performance improvements in transfer rates, CPU utilization, and flexible support for USB 2.0 devices.

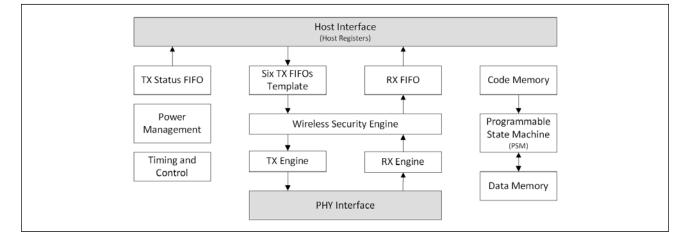

Figure 3 shows a block diagram of the device.

Figure 3: Functional Block Diagram

# Section 2: Functional Description

### **Global Functions**

### **Power Management**

The BCM43236/BCM43236B chips have been designed with the stringent power consumption requirements of battery-powered hosts in mind. All areas of the chip design were scrutinized to help reduce power consumption. Silicon processes and cell libraries were chosen to reduce leakage current and supply voltages.

The BCM43236/BCM43236B chips include an advanced Power Management Unit (PMU). The PMU provides significant power savings by putting the BCM43236/BCM43236B into various power management states appropriate to the current environment and activities that are being performed. The power management unit enables and disables internal regulators, switches, and other blocks based on a computation of the required resources and a table that describes the relationship between resources and the time needed to enable and disable them. Power-up sequences are fully programmable. Configurable, free-running counters in the PMU are used to turn on/off individual regulators and power switches. Clock speeds are dynamically changed (or gated altogether) for the current mode. Slower clock speeds are used wherever possible.

### **Voltage Regulators**

Three Low-Dropout (LDO) regulators and a PMU are integrated into the BCM43236/BCM43236B. All regulators are programmable via the PMU.

### Reset

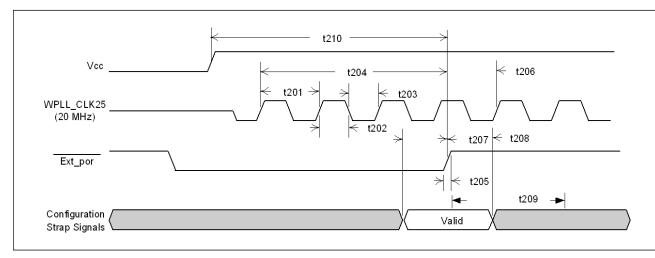

Resets are generated internally by the BCM43236/BCM43236B. An optional external power-on reset circuit can be connected to the active-low Ext\_por input pin. A 50 ms low pulse is recommended to guarantee that a sufficiently long reset is applied to all internal circuits, including integrated PHYs. The initialization process loads all pin-configurable modes, resets all internal processes, and puts the device in the idle state. During initialization, the clock source input signal must be active, and the 3.3V power supply to the device must be stable. The external power-on reset overrides the BCM43236/BCM43236B internal reset.

### **GPIO Interface**

There are eight General-Purpose I/O (GPIO) pins provided on the BCM43236/BCM43236B. They are multiplexed with the control signals. These pins can be used to attach to various external devices. Upon power-up and reset, these pins become tristated. Subsequently, they can be programmed to be either input or output pins via the GPIO control register. A programmable internal pull-up/pull-down resistor is included on each GPIO. If a GPIO output enable is not asserted, and the corresponding GPIO signal is not being driven externally, the GPIO state is determined by its programmable resistor.

### **Bluetooth Coexistence Interface**

A 5-wire handshake interface is provided to enable signalling between the device and an external Bluetooth device host to manage sharing of the wireless medium for optimum performance. The signals provided are:

- btcx\_tx\_conf

- btcx\_rf\_active

- btcx\_status

- btcx\_prisel

- btcx\_freq

$\ensuremath{\textbf{Note:}}$  These five pins are muxed with the JTAG interface.

### ΟΤΡ

The BCM43236/BCM43236B chips contain an on-chip One-Time-Programmable (OTP) area that can be used for nonvolatile storage of WLAN information such as a MAC address and other hardware-specific parameters. The total area available for programming is 2 Kbits.

### JTAG Interface

The BCM43236/BCM43236B chips support the IEEE 1149.1 JTAG boundary-scan standard for testing the device packaging and PCB manufacturing.

### **UART Interface**

One UART interface is provided that can be attached to RS-232 Data Termination Equipment (DTE) for exchanging and managing data with other serial devices. The UART interface is primarily used for debugging and development.

### **Serial Flash Interface**

Serial flash is available regardless of whether USB 2.0 operation is enabled or disabled. The flash interface is an STMicroelectronics<sup>®</sup>-compatible 4-pin interface.

### **USB/HSIC Interface**

The BCM43236/BCM43236B USB/HSIC interface can be set to operate as a USB 2.0 port or a High-Speed Inter-Chip (HSIC) port. Features of the interface are:

- USB 2.0 protocol engine:

- Parallel Interface Engine (PIE) between packet buffers and USB transceiver

- Supports up to nine endpoints, including Configurable Control Endpoint 0

- Separate endpoint packet buffers with a 512-byte FIFO buffer each

- Host-to-device communication for bulk, control, and interrupt transfers

- Configuration/status registers

- The HSIC port can communicate with an external HSIC host, such as the BCM5357 and BCM5358.

The various blocks in the USB 2.0 device/HSIC core are shown in Figure 4.

#### Figure 4: USB 2.0 Device/HSIC Core Block Diagram

The USB 2.0 PHY handles the USB protocol and the serial signaling interface between the host and device. It is primarily responsible for data transmission and recovery. On the transmit side, data is encoded, along with a clock, using the NRZI scheme with bit stuffing to ensure that the receiver detects a transition in the data stream. A SYNC field that precedes each packet enables the receiver to synchronize the data and clock recovery circuits. On the receive side, the serial data is deserialized, unstuffed, and checked for errors. The recovered data and clock are then shifted to the clock domain that is compatible with the internal bus logic.

The endpoint management unit contains the PIE control logic and the endpoint logic. The PIE interfaces between the packet buffers and the USB transceiver. It handles packet identification (PID), USB packets, and transactions.

The endpoint logic contains nine uniquely-addressable endpoints. These endpoints are the source or sink of communication flow between the host and the device. Endpoint zero is used as a default control port for both the input and output directions. The USB system software uses this default control method to initialize and configure the device information, and allows USB status and control access. Endpoint zero is always accessible after a device is attached, powered, and reset.

Endpoints are supported by 512-byte FIFO buffers, one for each IN endpoint and one shared by all OUT endpoints. Both TX and RX data transfers support a DMA burst of 4, which guarantees low latency and maximum throughput performance. The RX FIFO can never overflow by design. The maximum USB packet size cannot be more than 512 bytes.

The BCM43236/BCM43236B can be configured as a USB 2.0 device or as a PHY-less HSIC by selecting the appropriate strapping option. See Table 4 on page 26 for information on how to select the strapping options.

### **Crystal Oscillator**

Table 1 lists the requirements for the crystal oscillator.

| Parameter           | Value                                         |

|---------------------|-----------------------------------------------|

| Frequency           | 20 MHz                                        |

| Mode                | AT cut, fundamental                           |

| Load capacitance    | 16 pF                                         |

| ESR                 | 50Ω maximum                                   |

| Frequency stability | ±10 ppm at 25°C                               |

|                     | ±10 ppm at 0°C to +85°C                       |

| Aging               | ±3 ppm/year max first year, ±1 ppm thereafter |

| Drive level         | 300 μW maximum                                |

| Q-factor            | 40,000 minimum                                |

| Shunt capacitance   | < 5 pF                                        |

|                     |                                               |

#### Table 1: Crystal Oscillator Requirements

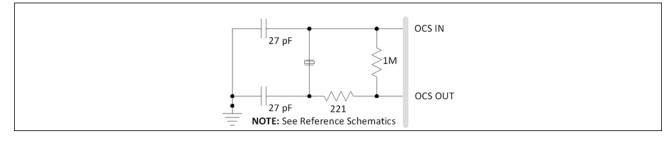

Figure 5 shows the recommended oscillator configuration.

# IEEE 802.11n MAC Description

The IEEE 802.11n MAC features include:

- Enhanced MAC for supporting IEEE 802.11n features

- Programmable Access Point (AP) or Station (STA) functionality

- Programmable Independent Basic Service Set (IBSS) or infrastructure mode

- Aggregated MPDU (MAC Protocol Data Unit) support for High-throughput (HT)

- Passive scanning

- Network Allocation Vector (NAV), Interframe Space (IFS), and Timing Synchronization Function (TSF) functionality

- RTS/CTS procedure

- Transmission of response frames (ACK/CTS)

- Address filtering of receive frames as specified by IBSS rules

- Multirate support

- Programmable Target Beacon Transmission Time (TBTT), beacon transmission/cancellation and programmable Announcement Traffic Indication Message (ATIM) window

- CF conformance: Setting NAV for neighborhood Point Coordination Function (PCF) operation

- Security through a variety of encryption schemes including WEP, TKIP, AES, WPA<sup>™</sup>, WAP2<sup>™</sup>, and IEEE 802.1X

- Power management

- Statistics counters for MIB support

The MAC core supports the transmission and reception of sequences of packets, together with related timing, without any packet-by-packet driver interaction. Time-critical tasks requiring response times of only a few milliseconds are handled in the MAC core. This achieves the required timing on the medium while keeping the host driver easier to write and maintain. Also, incoming packets are buffered in the MAC core, which allows the MAC driver to process them in bursts, enabling high bandwidth performance.

The MAC driver interacts with the MAC core to prepare queues of packets to transmit and to analyze and forward received packets to upper software layers. The internal blocks of the MAC core are connected to a Programmable State Machine (PSM) through the host interface that connects to the internal bus (see Figure 6).

#### Figure 6: Enhanced MAC Block Diagram

The host interface consists of registers for controlling and monitoring the status of the MAC core and interfacing with the TX/RX FIFOs. For transmit, a total of 128 KB FIFO buffering is available that can be dynamically allocated to six transmit queues plus template space for beacons, ACKs, and probe responses. Whenever the host has a frame to transmit, the host queues the frame into one of the transmit FIFOs with a TX descriptor containing TX control information. The PSM schedules the transmission on the medium depending on the frame type, transmission rules in IEEE 802.11 protocol, and the current medium occupancy scenario. After the transmission is completed, a TX status is returned to the host, informing the host of the result that got transmitted.

The MAC contains a single 10 KB RX FIFO. When a frame is received, it is sent to the host along with an RX descriptor that contains additional information about the frame reception conditions.

The power management block maintains the information regarding the power management state of the core (and the associated STAs in case of an AP) to help in dynamic decisions by the core regarding frame transmission.

The wireless security engine performs the required encryption/decryption on the TX/RX frames. This block supports separate transmit and receive keys with four shared keys and 50 link-specific keys. The link-specific keys are used to establish a secure link between any two STAs, with the required key being shared between only those two STAs, hence excluding all of the other STAs in the same network from deciphering the communication between those two STAs. The wireless security engine supports the following encryption schemes that can be selected on a per-destination basis:

- None: The wireless security engine acts as a pass-through

- WEP: 40-bit secure key and 24-bit IV as defined in IEEE Std. 802.11-2007

- WEP128: 104-bit secure key and 24-bit IV

- TKIP: IEEE Std. 802.11-2007

- AES: IEEE Std. 802.11-2007

The transmit engine is responsible for the byte flow from the TX FIFO to the PHY interface through the encryption engine and the addition of an FCS (CRC-32) as required by IEEE 802.11-2007. Similarly, the receive engine is responsible for byte flow from the PHY interface to the RX FIFO through the decryption engine and for detection of errors in the RX frame.

The timing block performs the TSF, NAV, and IFS functionality as described in IEEE Std. 802.11-2007.

The Programmable State Machine (PSM) coordinates the operation of different hardware blocks required for both transmission and reception. The PSM also maintains the statistics counters required for MIB support.

### **IEEE 802.11n PHY Description**

The PHY features include:

- Programmable data rates from MCS 0–15 in 20 MHz and 40 MHz channels, as specified in IEEE 802.11n.

- Support for Short Guard Interval (SGI) and Space-Time Block Coding (STBC)

- All scrambling, encoding, forward error correction, and modulation in the transmit direction, and inverse operations in the receive direction

- Advanced digital signal processing technology for best-in-class receive sensitivity

- Both mixed-mode and optional greenfield preamble of IEEE 802.11n

- Both long and optional short preambles of IEEE 802.11b

- Resistance to multipath (>250 nanoseconds RMS delay spread) with maximal ratio combining for high throughput and range performance, including improved performance in legacy mode over existing IEEE 802.11a/b/g solutions.

- Automatic Gain Control (AGC)

- Available per-packet channel quality and signal strength measurements

The dual PHYs integrated in the BCM43236/BCM43236B chips provide baseband processing at all mandatory data rates specified in IEEE 802.11n up to 300 Mbps, and the legacy rates specified in IEEE 802.11a/b/g including 1, 2, 5.5, 6, 9, 11, 12, 18, 24, 36, 48, and 54 Mbps. This core acts as an intermediary between the MAC and the dual-band 2.4/5 GHz radio, converting back and forth between packets and baseband waveforms.

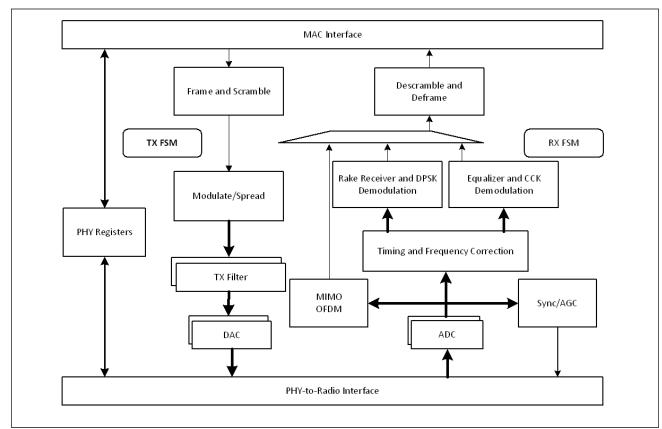

Figure 7: PHY Block Diagram

### **Dual-Band Radio Transceiver**

Integrated into the BCM43236/BCM43236B chips is Broadcom's world-class dual-band radio transceiver that ensures low power consumption and robust communications for low-cost applications operating in the 2.4 GHz and 5 GHz bands. Channel bandwidths of 20 MHz and 40 MHz are supported as specified in IEEE 802.11n.

### **Receiver Path**

The BCM43236/BCM43236B chips have a wide dynamic range, direct conversion receiver. It employs high order on-chip channel filtering to ensure reliable operation in the noisy 2.4 GHz ISM band or the entire 5 GHz U-NII band. The excellent noise figure of the receiver makes an external LNA unnecessary.

### **Transmitter Path**

Baseband data is modulated and upconverted to the 2.4 GHz ISM band or the 5 GHz U-NII bands, respectively. Linear on-chip Power Amplifiers are included, which are capable of delivering a nominal output power exceeding +15 dBm while meeting the IEEE 802.11a and 802.11g specifications. The TX gain has a 78 dB range with a resolution of 0.25 dB.

### Calibration

The BCM43236/BCM43236B chips feature dynamic on-chip calibration, eliminating process variation across components. This enables the device to be used in high-volume applications because calibration routines are not required during manufacturing testing. These calibration routines are performed periodically in the course of normal radio operation.

# **Section 3: Pin Assignments**

This sections contains pin assignments and ballout information for the BCM43236/BCM43236B (88-pin) packages.

### BCM43236/BCM43236B 88-Pin QFN Assignments

|                                  | 88                  | 87 86                       | 85               | 84 83                                     | 3 82   | 81                | 80 7         | 97            | 8 77                 | 76               | 75       | 74        | 73        | 72                   | 71       | 70 E                                 | 596        | 8 67               |                            |          |

|----------------------------------|---------------------|-----------------------------|------------------|-------------------------------------------|--------|-------------------|--------------|---------------|----------------------|------------------|----------|-----------|-----------|----------------------|----------|--------------------------------------|------------|--------------------|----------------------------|----------|

|                                  |                     | <u>, 7</u>                  |                  |                                           | -      |                   |              | -             | -                    |                  |          |           | _         |                      | _        | +                                    | _          | _                  |                            |          |

|                                  |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    |                            |          |

|                                  |                     | ant1<br>ant1                |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    |                            |          |

|                                  |                     | e 6                         |                  |                                           |        |                   |              |               |                      | E                |          |           |           | ~                    |          |                                      | ~ ~        | :                  |                            |          |

|                                  |                     | core0_                      |                  |                                           |        |                   |              |               |                      | /σοιο/οτρ_νοσ    |          | _         |           | 1p                   | s        | 20                                   |            | 2p5                |                            |          |

|                                  |                     |                             |                  |                                           |        |                   |              |               |                      | ģ                | Ë        | TRE       | AT A      |                      | NN       | 2 6                                  | įĘ         |                    |                            |          |

|                                  |                     | nimophy                     | 9                | <u>n</u> b                                | 4      | с<br>П            | 2 - 5        | 10            |                      | <u>o</u>         | Ë,       | S I       |           | 8 P                  |          | ןׂר                                  | ₹,⊵        | ₽.<br>₽            |                            |          |

|                                  | Ē                   | nin                         | gpio_6           | gpio_5<br>VDDIO                           | gpio_4 | gpio_3            | gpio_2       |               |                      | Ē                | JSB_RREF | HSIC_STRB | HSIC_DATA | JSB AVDD 1p2         | JSB_DMNS | טאט_טאני<br><u>ונים אוזההיז הי</u> ז | ISR MONCOR | JSBAVDD2p5         |                            |          |

| 1 VDDIO                          | ſ                   |                             | 100              |                                           | 100    | 00                |              | 10            |                      |                  |          |           | <u> </u>  |                      |          |                                      |            |                    | VDD                        | 66       |

| 2 sflash_cs_l                    | 1                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | mimophy_core1_ant1_rx      | 65       |

| 3 sflash_q                       | ]                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | mimophy_core1_ant1_tx      | 64       |

| 4 sflash_c                       |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | VDDIO                      | 63       |

| 5 sflash_d                       |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | UART_RX                    | 62       |

| 6 mimophy_core0_ant0_tx          |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | UART_TX                    | 61       |

| 7 mimophy_core0_ant0_rx<br>8 VDD | -                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | VDD<br>VDDPLL/RF_AVDD_1p2  | 60<br>59 |

| 9 mimophy_core1_ant0_tx          | -                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | USBLDO_2p5_out             | 58       |

| 10 mimophy_core1_ant0_rx         |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | LDO_3p3_in                 | 57       |

| 11 VDDIO                         |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | VREF                       | 56       |

| 12 VDD                           | 1                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | PAREF                      | 55       |

| 13 gpio_7                        | 1                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | PAREF_CTL1                 | 54       |

| 14 jtag_trst_l                   | 1                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | PAREF_CTL2                 | 53       |

| 15 jtag_tdi                      | 1                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | Ext_por                    | 52       |

| 16 jtag_tck                      | 1                   |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | xtal_buf_out               | 51       |

| 17 analog_wlan_iqtest_VDD1p2     |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | i_xtal_VDD2p5/o_xtal_VDD2p |          |

| 18 jtag_tms                      |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | xtal_in                    | 49       |

| 19 jtag_tdo                      |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | xtal_out                   | 48       |

| 20 analog_wlan_iqtest_qp         |                     |                             |                  |                                           |        |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | synth_VDD1p2               | 47       |

| 21 analog_wlan_iqtest_qn         |                     |                             | R                | CM                                        | 127    | 26                | /R/          | <u>ъл</u>     | 127                  | 26               | R 1      | 0.        | , 1       | n                    |          |                                      |            |                    | synth_vco_VDD1p2           | 46<br>45 |

| 22 analog_wlan_iqtest_in         | 0                   |                             |                  |                                           | TJ2    |                   |              |               |                      |                  |          |           |           |                      |          |                                      |            |                    | vreg3p3_VDD3p3             | 45       |

|                                  | it_ip               | 30.                         |                  | 1p2<br>re1                                |        | re1               | 1p2          | $\frac{2}{2}$ | 3p.                  |                  | 1p2      | reO       |           | le0                  | 1p2      | n<br>n                               |            |                    |                            |          |

|                                  | Ites                | 6                           |                  |                                           |        | Ū.                |              | ן נ           | B                    |                  | Ŕ        | <u></u> . |           | <u></u>              |          | 3                                    |            | a la               |                            |          |

|                                  |                     | l P                         |                  | ⊳_la                                      | p2     | na                | <b>۶</b> , 2 |               | , Pi                 | L                | Þ,       | u'a       | p2        | u'a                  | 5,₽      | 2                                    | _ ¤        | <u> </u>   2       |                            |          |

|                                  | vlar                | Lei,                        | Jre.             | re1<br>ten                                |        | ten               | re1          |               | )<br>Jre(            | ore(             | reO      | ten       | <u>[</u>  | ten                  | re0      | ) Le(                                |            | ext o              |                            |          |

|                                  | 5                   |                             | Ц <mark>О</mark> | al C                                      | ,Ĕ,    | an                | 8            |               | i lö                 | U<br>U<br>U<br>U | 0        | an        | ≓,[       | an                   | 8        | 5                                    | Ĭ          | ext_core           |                            |          |

|                                  | alo                 |                             | 28               | tx_5g_core1_VDD1p2<br>-f_5g_antenna_core1 | e1     | _2g_antenna_core1 | 28           | 2 6           | 1 kg                 | 5                | 50       | 20        | e'        | 28                   | 200      |                                      |            |                    |                            |          |

|                                  | Wanalog_wlan_iqtest | bGnd<br>Cpa_5g_core1_VDD3p3 | Ad               | ,<br>Z E                                  | 18     | F_                | X            |               | whom 28_core0_VDD3p3 | <u>A</u>         | Σ'       |           | <u>5</u>  | Grt_2g_antenna_core0 | Ľ,       | Hpa_zg_coreu_vuusp3                  | A D        | Prcal_res_ext_core |                            |          |

|                                  | 23                  | 2425                        | 26               | 27 28                                     | \$29   | 30                | 313          | 23            | 3 34                 | 35               | 36       | 37:       | 38        | 39                   | 404      | +1 4                                 | 124        | 3 44               |                            |          |

|                                  |                     |                             |                  |                                           |        |                   |              |               |                      |                  | -        |           |           |                      |          | _                                    |            |                    |                            |          |

Figure 8: BCM43236/BCM43236B 88-Pin QFN Package

### Signals by Pin Number

| Pin | Signal Name            | Pin Signal Name          | Pin Signal Name          | Pin Signal Name          |

|-----|------------------------|--------------------------|--------------------------|--------------------------|

| 1   | VDDIO                  | 23 analog_wlan_iqtest_ip | 46 synth_vco_VDD1p2      | 68 USB_MONCDR            |

| 2   | sflash_cs_l            | 24 Gnd                   | 47 synth_VDD1p2          | 69 USB_AVDD3p3           |

| 3   | sflash_q               | 25 pa_5g_core1_VDD3p3    | 48 xtal_out              | 70 USB_DPLS              |

| 4   | sflash_c               | 26 PA_5g_core1           | 49 xtal_in               | 71 USB_DMNS              |

| 5   | sflash_d               | 27 tx_5g_core1_VDD1p2    | 50 i_xtal_VDD2p5/        | 72 USB AVDD 1p2          |

| 6   | mimophy_core0_ant0_tx  | 28 rf_5g_antenna_core1   | o_xtal_VDD2p5            | 73 HSIC_DATA             |

| 7   | mimophy_core0_ant0_rx  | 29 core1_VDD1p2          | 51 xtal_buf_out          | 74 HSIC_STRB             |

| 8   | VDD                    | 30 rf_2g_antenna_core1   | 52 Ext_por               | 75 USB_RREF              |

| 9   | mimophy_core1_ant0_tx  | 31 tx_2g_core1_VDD1p2    | 53 PAREF_CTL2            | 76 VDDIO/OTP_VDD         |

| 10  | mimophy_core1_ant0_rx  | 32 pa_2g_core1_VDD3p3    | 54 PAREF_CTL1            | 77 VDD                   |

| 11  | VDDIO                  | 33 PA_2g_core1           | 55 PAREF                 | 78 gpio_0                |

| 12  | VDD                    | 34 pa_5g_core0_VDD3p3    | 56 VREF                  | 79 gpio_1                |

| 13  | gpio_7                 | 35 PA_5g_core0           | 57 LDO_3p3_in            | 80 gpio_2                |

| 14  | jtag_trst_l            | 36 tx_5g_core0_VDD1p2    | 58 USBLDO_2p5_out        | 81 gpio_3                |

| 15  | jtag_tdi               | 37 rf_5g_antenna_core0   | 59 VDDPLL/RF_AVDD_1p2    | 82 gpio_4                |

| 16  | jtag_tck               | 38 core0_VDD1p2          | 60 VDD                   | 83 VDDIO                 |

| 17  | analog_wlan_iqtest_VDD | 39 rf_2g_antenna_core0   | 61 UART_TX               | 84 gpio_5                |

|     | 1p2                    | 40 tx_2g_core0_VDD1p2    | 62 UART_RX               | 85 gpio_6                |

| 18  | jtag_tms               | 41 pa_2g_core0_VDD3p3    | 63 VDDIO                 | 86 mimophy_core0_ant1_tx |

| 19  | jtag_tdo               | 42 PA_2g_core0           | 64 mimophy_core1_ant1_tx | 87 mimophy_core0_ant1_rx |

| 20  | analog_wlan_iqtest_qp  | 43 gpiao_GPIO_PAD        | 65 mimophy_core1_ant1_rx | 88 VDD                   |

| 21  | analog_wlan_iqtest_qn  | 44 rcal_res_ext_core     | 66 VDD                   |                          |

| 22  | analog_wlan_iqtest_in  | 45 vreg3p3_VDD3p3        | 67 USBAVDD2p5            |                          |

#### Table 2: Pin Assignments

# Section 4: Signal and Pin Descriptions

## Package Signal Descriptions

The signal name, type, and description of each pin in the BCM43236/BCM43236B 88-pin QFN package is listed in Table 3. The symbols shown under Type indicate pin directions (I/O = bidirectional, I = input, O = output) and the internal pull-up/pull-down characteristics (PU = weak internal pull-up resistor and PD = weak internal pull-down resistor), if any. See also Table 4 on page 26 for resistor strapping options.

| Signal                 | BCM43236/<br>BCM43236B | Туре        | Description                                                                                                                                                                                  |

|------------------------|------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystal Oscillator     |                        |             |                                                                                                                                                                                              |

| xtal_in                | 49                     | I           | XTAL oscillator input. Connect a 20 MHz, 10 ppm crystal between the xtal_in and xtal_out pins.                                                                                               |

| xtal_out               | 48                     | 0           | XTAL oscillator output                                                                                                                                                                       |

| xtal_buf_out           | 51                     | 0           | Buffered XTAL output                                                                                                                                                                         |

| Serial Flash Interface |                        |             |                                                                                                                                                                                              |

| sflash_cs_l            | 2                      | O (8 mA-PU) | Serial flash chip select                                                                                                                                                                     |

| sflash_q               | 3                      | I (8 mA-PU) | Serial flash data input                                                                                                                                                                      |

| sflash_c               | 4                      | O (8 mA-PD) | Serial flash clock                                                                                                                                                                           |

| sflash_d               | 5                      | O (8 mA)    | Serial flash data output                                                                                                                                                                     |

| USB Interface          |                        |             |                                                                                                                                                                                              |

| usb_dmns               | 71                     | I/O         | USB interface port D–                                                                                                                                                                        |

| usb_dpls               | 70                     | I/O         | USB interface port D+                                                                                                                                                                        |

| usb_rref               | 75                     | 0           | During USB mode, tie this pin in parallel through a 100 pF capacitor and a 4 k $\Omega$ resistor to ground. During HSIC mode, tie this pin to a 50 $\Omega$ resistor to ground.              |

| hsic_strb              | 74                     | 0           | USB HSIC strobe                                                                                                                                                                              |

| hsic_data              | 73                     | I/O         | USB HSIC data                                                                                                                                                                                |

| usb_moncdr             | 68                     | _           | For test/diagnostic purposes only.                                                                                                                                                           |

| Miscellaneous Signals  |                        |             |                                                                                                                                                                                              |

| rcal_res_ext_core      | 44                     | 0           | Reference output, connect to ground via 15k 1% resistor.                                                                                                                                     |

| ext_por                | 52                     | I           | External power-on reset (POR) input. Active low.<br>Allows an optional external power-on reset<br>circuit to be connected. If installed, the external<br>POR will override the internal POR. |

| Table 3: | Signal | Descriptions |

|----------|--------|--------------|

|----------|--------|--------------|

| Signal                | BCM43236/<br>BCM43236B | Туре | Description                                                                                                                                                                                                                                    |

|-----------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| analog_wlan_iqtest_qp | 20                     | _    | IQ test pin                                                                                                                                                                                                                                    |

| analog_wlan_iqtest_qn | 21                     | -    | IQ test pin                                                                                                                                                                                                                                    |

| analog_wlan_iqtest_in | 22                     | -    | IQ test pin                                                                                                                                                                                                                                    |

| analog_wlan_iqtest_ip | 23                     | -    | IQ test pin                                                                                                                                                                                                                                    |

| RF Control Interface  |                        |      |                                                                                                                                                                                                                                                |

| mimophy_core0_ant0_tx | 6                      | 0    | Antenna0 TR Switch controls for core 0. These                                                                                                                                                                                                  |

| mimophy_core0_ant0_rx | 7                      | -    | pins are also used as strapping options, see<br>Table 4 on page 26.                                                                                                                                                                            |

| mimophy_core0_ant1_tx | 86                     | 0    | Antenna1 TR Switch controls for core 0. These                                                                                                                                                                                                  |

| mimophy_core0_ant1_rx | 87                     |      | pins are also used as strapping options, see<br>Table 4 on page 26.                                                                                                                                                                            |

| mimophy_core1_ant0_tx | 9                      | 0    | Antenna0 TR Switch controls for core 1. These                                                                                                                                                                                                  |

| mimophy_core1_ant0_rx | 10                     |      | pins are also used as strapping options, see<br>Table 4.                                                                                                                                                                                       |

| mimophy_core1_ant1_tx | 64                     | 0    | Antenna1 TR Switch controls for core 1. These                                                                                                                                                                                                  |

| mimophy_core1_ant1_rx | 65                     | _    | pins are also used as strapping options, see Table 4.                                                                                                                                                                                          |

| RF Signal Interface   |                        |      |                                                                                                                                                                                                                                                |

| rf_5g_antenna_core0   | 37                     |      | Chain 0 RF receive input, 5 GHz band                                                                                                                                                                                                           |

| rf_5g_antenna_core1   | 28                     |      | Chain 1 RF receive input, 5 GHz band                                                                                                                                                                                                           |

| rf_2g_antenna_core0   | 39                     |      | Chain 0 RF receive input, 2.4 GHz band                                                                                                                                                                                                         |

| rf_2g_antenna_core1   | 30                     | I    | Chain 1 RF receive input, 2.4 GHz band                                                                                                                                                                                                         |

| pa_5g_core0           | 35                     | 0    | Chain 0 RF transmit output, 5 GHz band                                                                                                                                                                                                         |

| pa_5g_core1           | 26                     | 0    | Chain 1 RF transmit output, 5 GHz band                                                                                                                                                                                                         |

| pa_2g_core0           | 42                     | 0    | Chain 0 RF transmit output, 2.4 GHz band                                                                                                                                                                                                       |

| pa_2g_core1           | 33                     | 0    | Chain 1 RF transmit output, 2.4 GHz band                                                                                                                                                                                                       |

| JTAG Interface        |                        |      |                                                                                                                                                                                                                                                |

| jtag_trst_l           | 14                     | I/O  | JTAG Reset Input. Resets the JTAG Controller. If not used, this pin should be pulled low by a 1 k $\Omega$ resistor. This pin is muxed with gpio0.                                                                                             |

| jtag_tck              | 16                     | I/O  | JTAG Test Clock Input. Used to synchronize JTAG control and data transfers. If not used, this pin should be pulled low by a 1 k $\Omega$ resistor. This pin is muxed with btcx_rf_active (Bluetooth coexistence output, RF active).            |

| jtag_tdi              | 15                     | I/O  | JTAG Test Data Input. Serial data input to the<br>JTAG TAP controller. Sampled on the rising edge<br>of TCK. If not used, it may be left unconnected.<br>This pin is muxed with btcx_tx_conf (Bluetooth<br>coexistence output, WLAN transmit). |

| Signal         | BCM43236/<br>BCM43236B | Туре          | Description                                                                                                                                                                                                                                                                                  |

|----------------|------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| jtag_tdo       | 19                     | I/O           | JTAG Test Data Output. Serial data output from<br>the JTAG TAP controller. Sampled on the rising<br>edge of TCK. If not used, it may be left<br>unconnected. This pin is muxed with btcx_prisel<br>(Bluetooth coexistence output, antenna select).                                           |

| jtag_tms       | 18                     | Ι/Ο           | JTAG Mode Select Input. Single control input to<br>the JTAG TAP controller used to traverse the test<br>logic state machine. Sampled on the rising edge<br>of TCK. If not used, it may be left unconnected.<br>This pin is muxed with btcx_status (Bluetooth<br>coexistence output, status). |

| GPIO Interface |                        |               |                                                                                                                                                                                                                                                                                              |

| gpio_0         | 78                     | I/O<br>(8 mA) | General Purpose I/O pin. This pin is tristated on<br>power-up and reset. Subsequently, it becomes<br>an input or an output through software control.<br>A programmable PU or PD resistor is available<br>for each GPIO pin. This pin is muxed with<br>wlan_led (WLAN LED output).            |

| gpio_1         | 79                     | I/O           | General Purpose I/O pin. This pin is muxed with<br>mimophy_core0_ant_shd (antenna switch<br>control for the shared [middle] antenna of a 2 of<br>3 design<br>[core 0]).                                                                                                                      |

| gpio_2         | 80                     | I/O           | General Purpose I/O pin. This pin is muxed with:                                                                                                                                                                                                                                             |

|                |                        |               | <ul> <li>mimophy_core1_ant_shd: antenna switch<br/>control for the shared (middle) antenna of a<br/>2 of 3 design<br/>(core 1).</li> </ul>                                                                                                                                                   |

|                |                        |               | <ul> <li>btcx_freq: Bluetooth coexistence RF<br/>frequency</li> </ul>                                                                                                                                                                                                                        |

| gpio_3         | 81                     | I/O           | General Purpose I/O pin.                                                                                                                                                                                                                                                                     |

| gpio_4         | 82                     | I/O           | General Purpose I/O pin. This pin is muxed with:                                                                                                                                                                                                                                             |

|                |                        |               | <ul> <li>ext_lna_2g_pu_0: 2.4 GHz band core 0<br/>power amplifier control</li> </ul>                                                                                                                                                                                                         |

|                |                        |               | <ul> <li>ext_pa_2g_0: 2.4 GHz band core 0 power<br/>amplifier control</li> </ul>                                                                                                                                                                                                             |

|                |                        |               | CS: SPI select                                                                                                                                                                                                                                                                               |

| gpio_5         | 84                     | I/O           | <ul> <li>General Purpose I/O pin. This pin is muxed with:</li> <li>ext_lna_2g_pu_1: 2.4 GHz band core 1 power amplifier control</li> </ul>                                                                                                                                                   |

|                |                        |               | <ul> <li>ext_pa_2g_1: 2.4 GHz band core 1 power<br/>amplifier control</li> </ul>                                                                                                                                                                                                             |

|                |                        |               | • SCLK: SPI clock                                                                                                                                                                                                                                                                            |

|                |                        |               | • I2C_SCL: I <sup>2</sup> C clock                                                                                                                                                                                                                                                            |

| Signal             | BCM43236/<br>BCM43236B   | Туре          | Description                                                                        |

|--------------------|--------------------------|---------------|------------------------------------------------------------------------------------|

| gpio_6             | 85                       | I/O           | General Purpose I/O pin. This pin is muxed with:                                   |

|                    |                          |               | <ul> <li>ext_lna_5g_pu_0: 5 GHz band core 0 power<br/>amplifier control</li> </ul> |

|                    |                          |               | <ul> <li>ext_pa_5g_0: 5 GHz band core 0 power<br/>amplifier control)</li> </ul>    |

|                    |                          |               | SDI: SPI data input                                                                |

| gpio_7             | 13                       | I/O           | General Purpose I/O pin. This pin is muxed with:                                   |

|                    |                          |               | <ul> <li>ext_lna_5g_pu_1: 5 GHz band core 1 power<br/>amplifier control</li> </ul> |

|                    |                          |               | <ul> <li>ext_pa_5g_1: 5 GHz band core 1 power<br/>amplifier control</li> </ul>     |

|                    |                          |               | SDO: SPI data output                                                               |

|                    |                          |               | • I2C_SDA: I <sup>2</sup> C data                                                   |

| gpiao_gpio_pad     | 43                       | _             | Connect 0.1 µF bypass cap                                                          |

| UART Interface     |                          |               |                                                                                    |

| UART_RX            | 62                       | I/O (4 mA PU) | UART receive data                                                                  |

| UART_TX            | 61                       | I/O (4 mA)    | UART transmit data                                                                 |

| Power and Ground   |                          |               |                                                                                    |

| vdd                | 8, 12, 60, 66,<br>77, 88 | PWR           | 1.2V supply input for the core logic.                                              |

| vddio              | 1, 11, 63, 83            | PWR           | 3.3V supply input for I/O logic                                                    |

| vddio/otp_vdd      | 76                       | PWR           | 3.3V supply input for I/O logic                                                    |

| usbavdd2p5         | 67                       | PWR           | USB analog power supply                                                            |

| usbldo_2p5_out     | 58                       | PWR           | USB LDO output; decouple to ground.                                                |

| usb_avdd3p3        | 69                       | PWR           | 3.3V supply input to USB interface                                                 |

| usbavdd1p2         | 72                       | PWR           | 1.2V supply input to USB interface                                                 |

| synth_vdd1p2       | 47                       | PWR           | Analog 1.2V supply input                                                           |

| synth_vco_vdd1p2   | 46                       | PWR           | Analog 1.2V supply input                                                           |

| core0_vdd1p2       | 38                       | PWR           | Analog 1.2V supply input                                                           |

| core1_vdd1p2       | 29                       | PWR           | Analog 1.2V supply input                                                           |

| tx_5g_core0_vdd1p2 | 36                       | PWR           | Analog 1.2V supply input                                                           |

| tx_5g_core1_vdd1p2 | 27                       | PWR           | Analog 1.2V supply input                                                           |

| tx_2g_core0_vdd1p2 | 40                       | PWR           | Analog 1.2V supply input                                                           |