# CY9266 HOTLink<sup>™</sup> Evaluation Board User's Guide

# **Overview**

This document describes the construction, interfaces, and operation of the CY9266–F (optical fiber), CY9266–P (plastic optical fiber), CY9266–T (shielded twisted pair/twinax), and CY9266–C (coaxial cable) HOTLink<sup>™</sup> Evaluation Boards. These boards implement a complete bidirectional parallel-to-serial and serial-to-parallel communications link, capable of operation at serial rates of 150 to 400 Mbits/second (15 to 40 Mbytes/second). The supported rate of communication may be limited by the specific type and speed-grade of optical module or copper cable type used.

The CY9266 Evaluation Boards are optically, electrically, and mechanically compatible with the ANSI T11 Fibre Channel Interface, as documented in the ANSI standard ANS X3.230–1994. It provides three different methods of access for the TTL parallel interface and supervisor functions, for testing or exercising the serial data link.

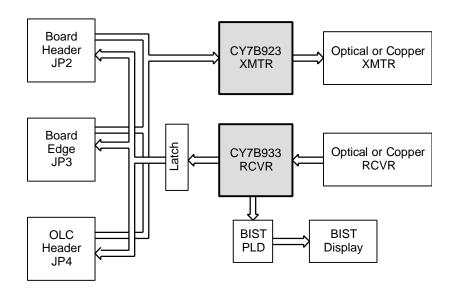

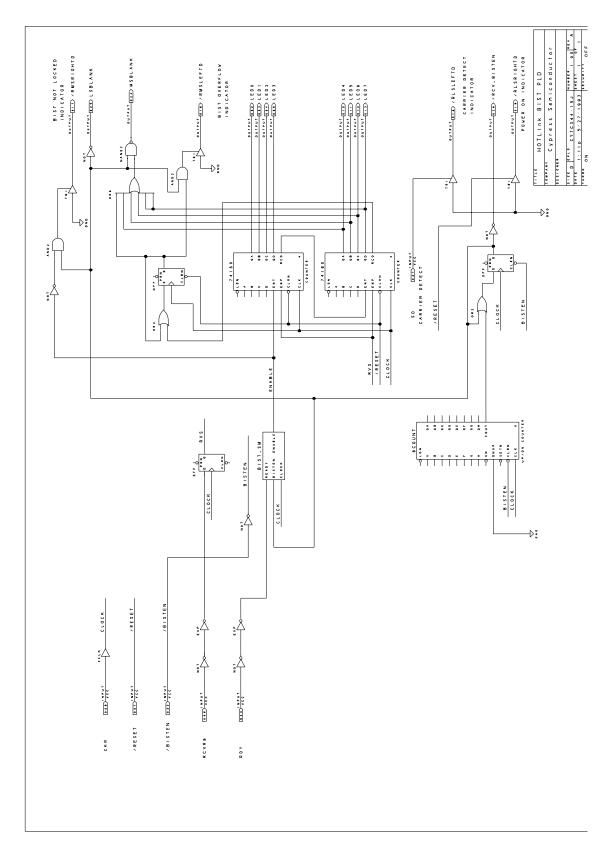

#### **Block Diagram**

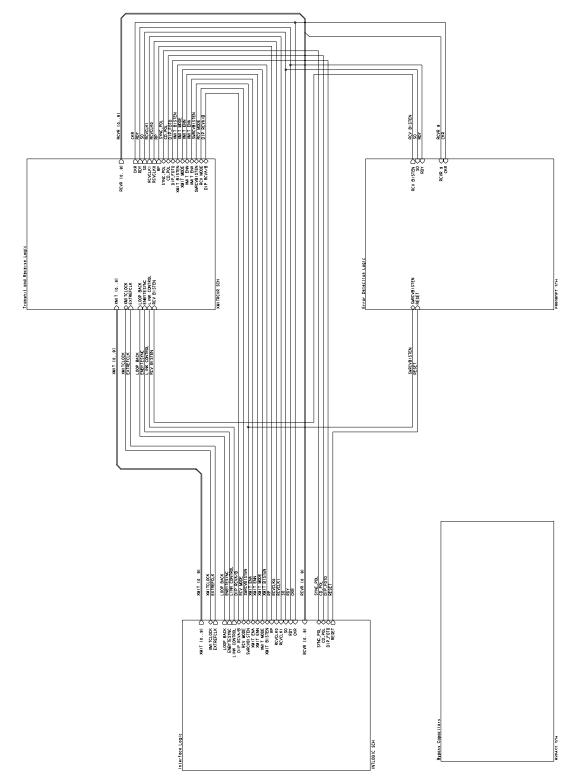

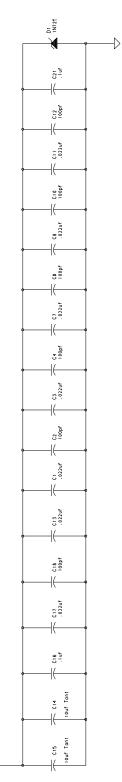

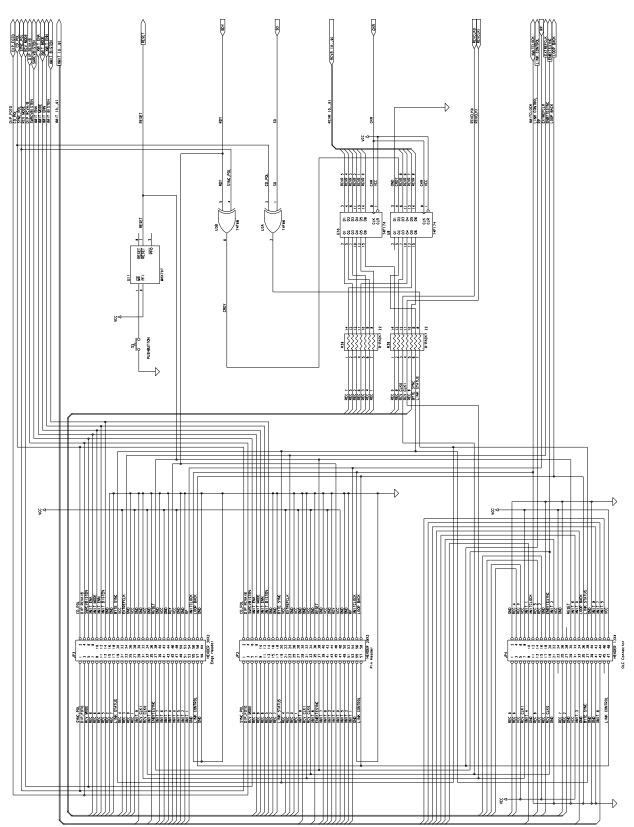

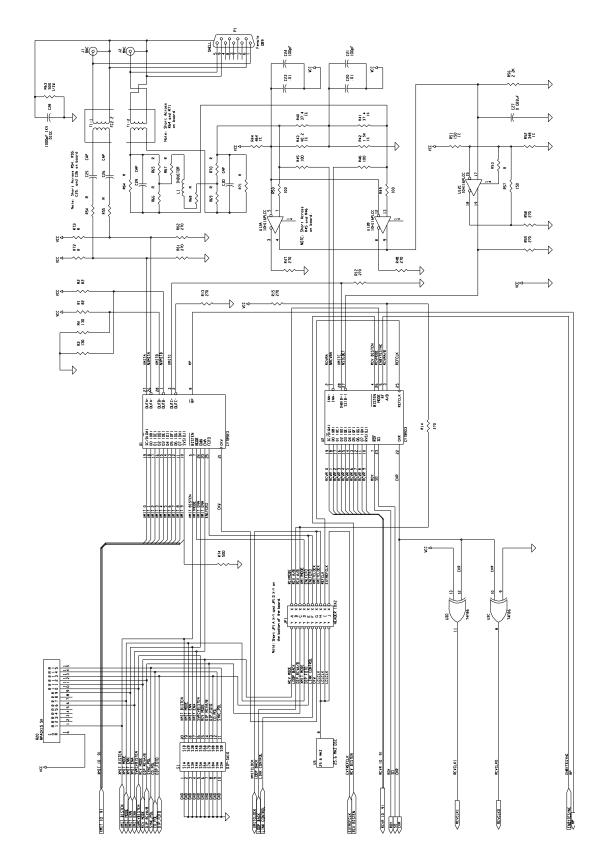

The block diagram in *Figure 1* illustrates the major functional blocks contained in the CY9266. These include:

- 10-bit TTL parallel transmit data input

- 10-bit TTL parallel receive data output

- · Selectable Encoded or Bypass operation modes

- · On-board socketed oscillator

- Selectable internal/external clocking

- Selectable signal-detect polarity

- · Selectable local loopback

- Power supply voltage monitor

- Built-in self-test (BIST) pattern generation and checking hardware with error/status display

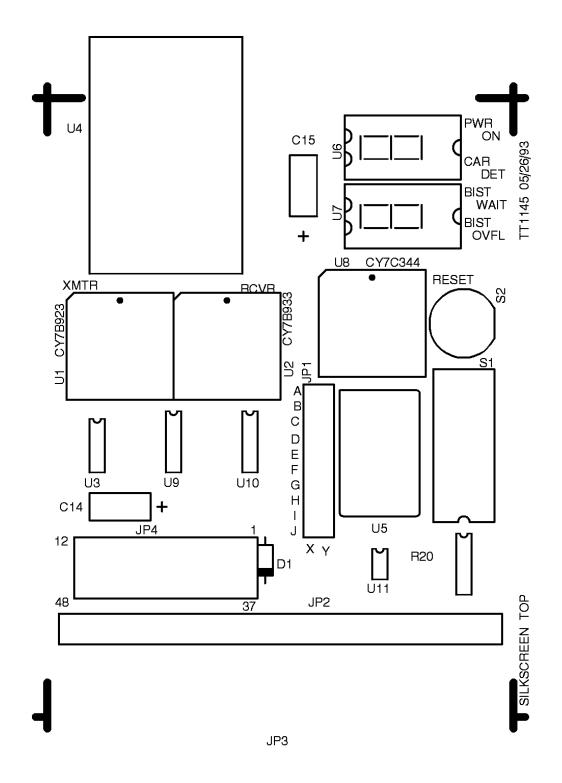

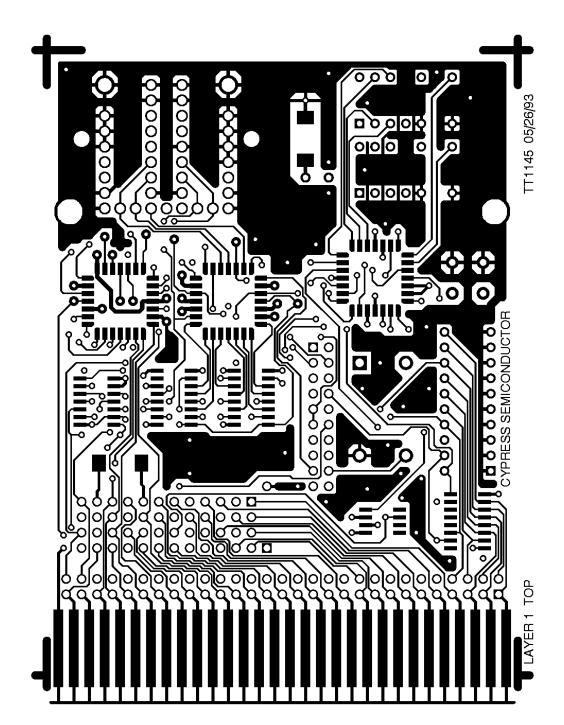

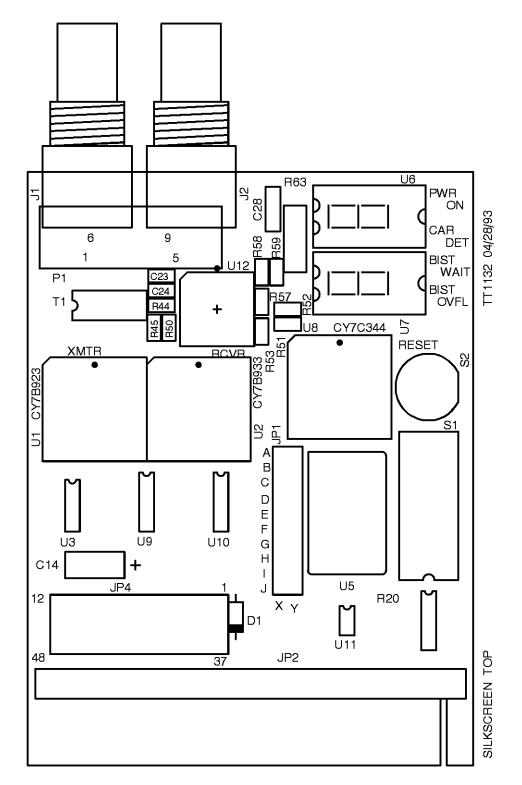

#### **Board Connectors**

This board offers three primary methods of TTL-level access:

- JP2—A 58-position (2 x 29) set of holes, capable of accepting a 0.025" sq. pin-header on the top or bottom of the board

- JP3—A 60-position (2 x 30) 0.1" spaced board-edge finger stock

- JP4—A 48-position (4 x 12 matrix) 0.025" sq. pin-header mounted on the bottom of the board

Connectors JP2 and JP3 provide access to all data input and output buses as well as all BIST, control, and clocking signals for the HOTLink Transmitter and Receiver. These connectors may be used individually or together since all signals present on JP2 are also present on JP3. Power for the board is also brought in through these same connectors.

Connector JP4 is positioned and pinned to match up with the connector and signals present on other industry-standard Fibre Channel modules. Unlike these other modules (which may contain two full-duplex channels), this evaluation board only provides a single full-duplex channel. While sufficient room exists to build a board with two channels, other functionality was added (on-board oscillator, BIST PLD and display, etc.) in this space to allow better testing and demonstration of the enhanced capabilities present in the Cypress HOTLink parts.

Figure 1. HOTLink Evaluation Board Block Diagram

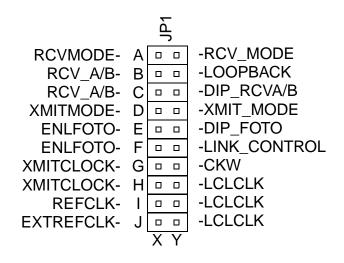

An additional jumper block (JP1) is used to configure three of the operating characteristics of the board: clock sourcing, serial output enable (FOTO), and local loopback control.

# **Optical Modules**

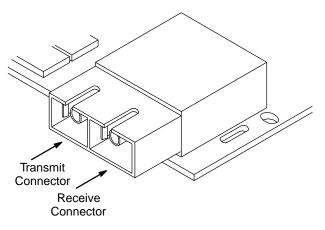

The CY9266–F Evaluation Board is designed to operate with industry-standard footprint optical modules. The evaluation board contains low-profile socket pins so the user may select and test optical modules from different vendors. This board accepts both the four-row DIP and the single-row 1X9 types of modules.

These modules are available from multiple vendors with either ST- or SC-type optical fiber connectors. Because these modules are all LED-based, they are not required to meet many of the safety standards (ANSI Z136.1 and Z136.2, F.D.A. regulation 21 CFR subchapter J, and IEC 825) necessary for LASER-based modules. These modules should be used with 62.5/125-mm multimode graded-index fiber.

For longer distance communications, LASER-based modules are also available that are compatible with the CY9266–F cards. However, when used with LASER transmitters, it is the responsibility of the user to receive what ever safety certifications are necessary.

The CY9266–P Evaluation Board is electrically identical to the CY9266–F, except that it is shipped with an optical module configured for low-cost plastic optical fiber, and set for a lower data rate (155 MBaud).

# **Coaxial Cables**

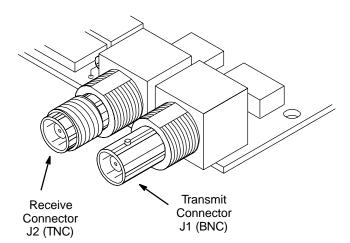

The CY9266–C Evaluation Board is configured to support 75 $\Omega$  coaxial cables that attach through BNC/TNC connectors. Other cable impedances may be used with the board by changing the value of the termination and driver bias resistors on the board.

# **Shielded-Pair Cables**

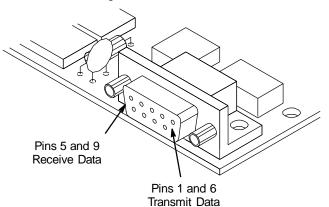

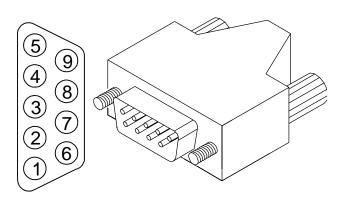

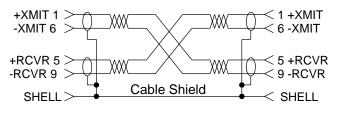

The CY9266–T Evaluation Board is configured to support  $150\Omega$  shielded twisted-pair or twinaxial cable that attaches through a 9-pin D-sub connector. Other cable impedances may be used with the board by changing the value of the termination and driver bias resistors on the board.

# **BIST Support**

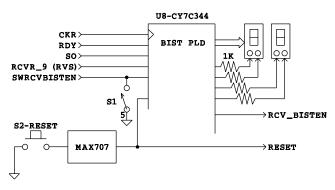

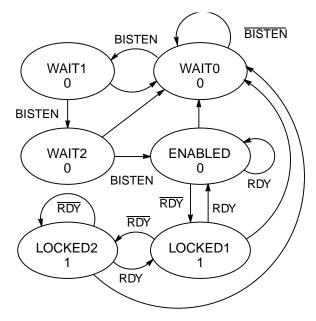

The CY9266 contains an on-board control PLD and a two-digit error-count display that are used in conjunction with the BIST (Built-In Self-Test) capability of the Cypress Semiconductor HOTLink Transmitter and Receiver. This capability allows the parts, and any serial link, to be exercised and monitored at their full data rate without the use of expensive external test equipment.

The BIST PLD (CY7C344) contains a simple state machine that monitors the HOTLink Receiver BIST state, and an error-counter that drives an external display. The complete contents of this PLD are documented in Appendix C.

This BIST PLD also drives the four decimal point LEDs on the displays. These indicators are used to present additional status information about the state of the board, the BIST state machine, and the serial link.

# **Design Criteria**

The CY9266 Evaluation Board was designed as a low-cost demonstration vehicle for the Cypress Semiconductor

HOTLink family of data communications parts. The goals of this board are to:

- Present an interface board that is fully compliant with the mechanical, electrical, optical, coding, and protocol specifications in levels 0 and 1 of the ANSI X3.230 Fibre Channel standard

- Allow full data rate testing of the serial link without expensive test equipment

- Allow the user to exercise all modes of operation of the receiver and transmitter

- Offer various parallel attachment methods for simplified system interfacing

- · Offer various media types for evaluation

- Allow simple interfacing to existing OLC-compatible test

platforms

Because of the flexibility inherent in the HOTLink parts, these goals were easily achieved.

Three electrical connection methods are provided: a 60-pin board-edge connector, a 58-pin  $(2 \times 29) \quad 0.025''$  square pin-header, and a 48-pin  $(4 \times 12) \quad 0.025''$  square pin-header. These different connectors allow the user to select the connector form that best suits their desired mode of attachment.

The HOTLink Transmitter and Receiver contain a BIST capability. This capability was designed into the HOTLink parts to allow high-speed serial testing without expensive test equipment. All hardware necessary to exercise and monitor the BIST function is present on the CY9266 board. This hardware allows a bit-error-rate (BER) test to be performed without additional equipment.

The BIST capability of the HOTLink Transmitter and Receiver allows offline testing of the transmitter, receiver, and serial link, by performing a bit-by-bit comparison of the data while a 511-character pseudo-random data stream is repeatedly sent, received, and checked.

Through use of either JP2 or JP3, users may exercise all modes of operation of the parts. JP4 is configured as a functional system interface, and thus does not include all the mode, clock, and special control signals present on JP2 and JP3, all of which may be selected or controlled in JP1 or S1.

# **Connector Pin Numbering**

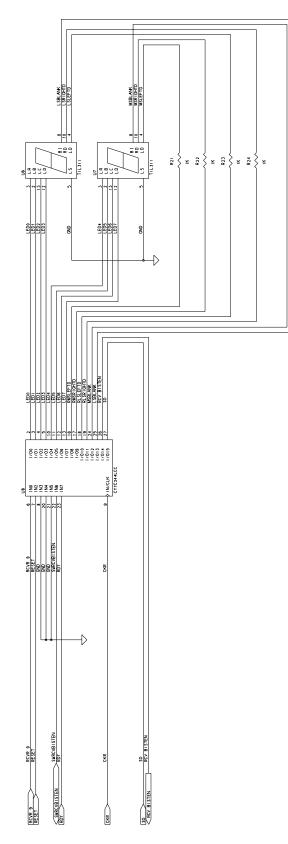

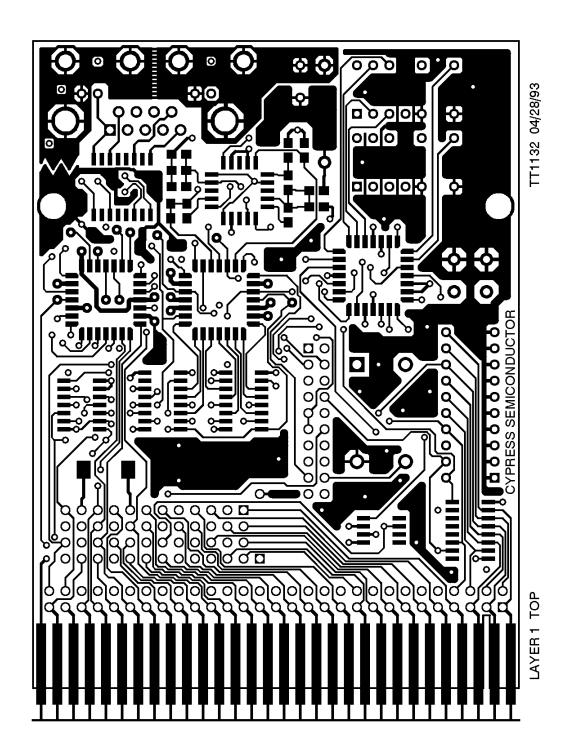

# JP2—58-Position Pin-Header

The 58-position pin-header (JP2) holes are located next to the board-edge connector. Pin 1 of this connector area is identified on the board by a square solder pad. The remaining pin locations use a round solder pad.

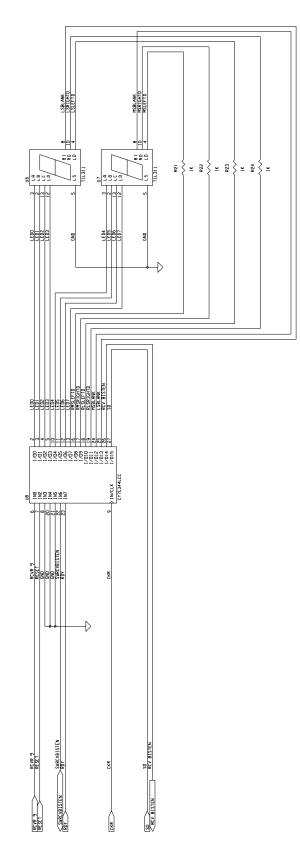

The connector hole pattern is made to accept fifty-eight 0.025" square pins soldered into the board. The numbering for this connector is shown in *Figure 2*.

**Note:** The numbering of this connector is specified to match up with standard 0.050" centerline flat cable connectors. Because of the location of pin 1 of this hole pattern, the mating pins for this connector should normally be on the bottom of the board. If a connector is instead attached to the top side of the board, the even- and odd-numbered pins of the connector are effectively swapped. This means that conductor 1 of a cable attached to the top side of the board is in reality connected to the signal listed for pin 2 in *Table 1*.

| LINK_CONTROL-57 | 00 | 58-L OOP_BACK  |

|-----------------|----|----------------|

| GND-55          | 00 | 56-XMITCL OCK  |

| XMIT_1-53       | 00 | 54-RP          |

| XMIT_2-51       | 00 | 52-GND         |

| XMIT_5-49       | 00 | 50-GND         |

| XMIT_0-47       | 00 | 48-VCC         |

| XMIT_4-45       | 00 | 46-RD Y        |

| XMIT_3-43       | 00 | 44-GND         |

| XMIT_6-41       | 00 | 42-VCC         |

| XMIT_7-39       | 00 | 40-GND         |

| ENBYTESYNC-37   | 00 | 38-RESET       |

| XMIT_8-35       | 00 | 36-GND         |

| RCV_CLK0-33     |    |                |

| RCV_CLK1-31     |    |                |

| XMIT_9-29       |    |                |

| REC_1-27        |    |                |

| REC_0-25        |    |                |

|                 |    | 24-EXTREFCLK   |

| REC_4-21        |    |                |

| LINK_STATUS-19  |    |                |

| REC_7-17        |    |                |

| REC_2-15        |    |                |

|                 |    | 14-XMIT_BISTEN |

|                 |    | 12-XMIT_ENN    |

|                 |    | 10-XMIT_MODE   |

| _               |    | 8-XMIT_ENA     |

|                 |    | 6-SWRCVBISTEN  |

|                 |    | 4-DIP_RCV A/B  |

| SYNC_POL-1      | 00 | 2-CD_POL       |

## Figure 2. JP2 Pin Numbering, Top Side of Board View

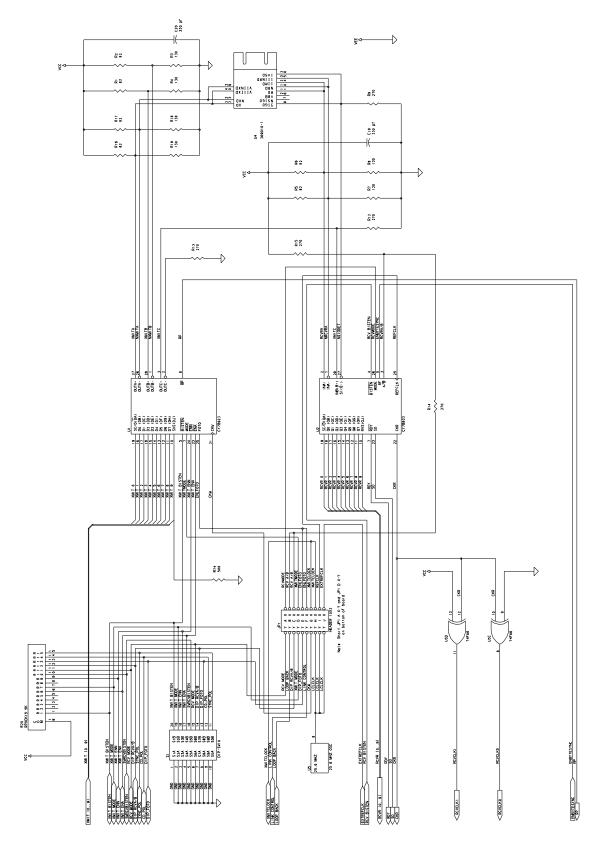

# JP3—60-Position Board-Edge

The 60-position board-edge connector (JP3) is a section of gold plated 0.062'' board finger-stock that connects to the same signals as JP2. Contact centerline for this connector is 0.1'', with even- and odd-numbered signals on opposing sides of the board.

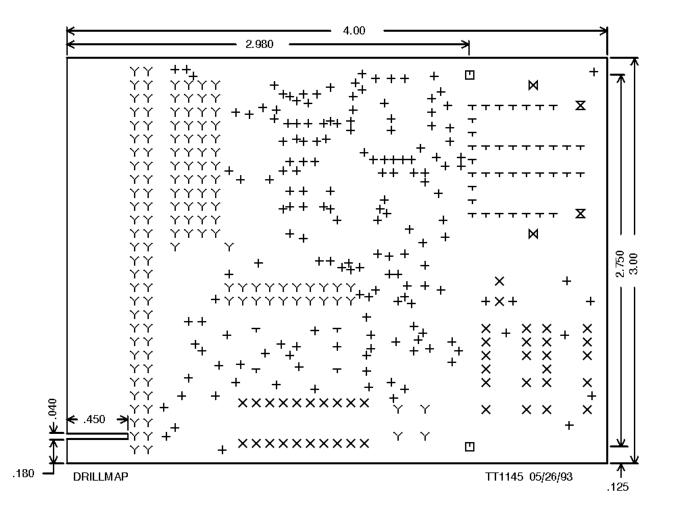

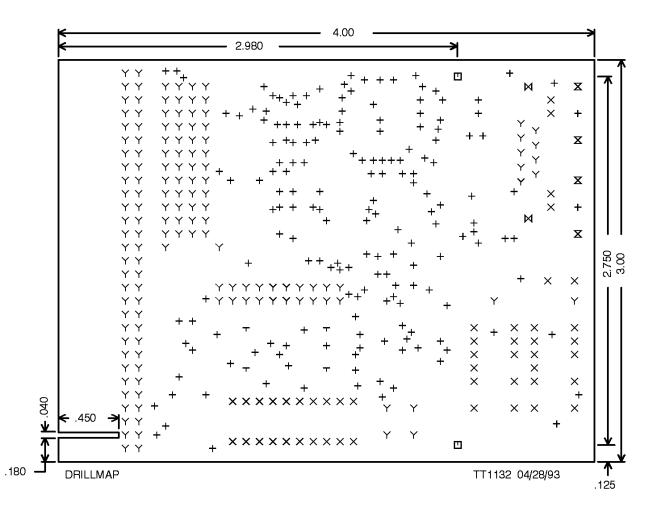

To prevent the evaluation board from being plugged into a mating connector backwards (and possibly damaging it), a  $0.040'' \times 0.450''$  keying slot is present between contacts 3/4 and 5/6. The pin numbering for this connector is shown in *Figure 3.*

**Note:** The numbering of this connector is specified to match up with standard 0.050" centerline flat-cable connectors. Because of the location of pin 1 of this board-edge connector, the mating connector would normally be a mass-terminate board-edge to flat-cable type connector. If a standard board-edge connector is used instead, the even and odd numbered pins of the connector are effectively swapped. This means that pin 1 of a standard board-edge connector is in reality connected to the signal listed for pin 2 in *Table 1*.

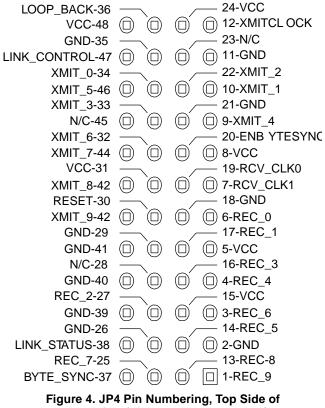

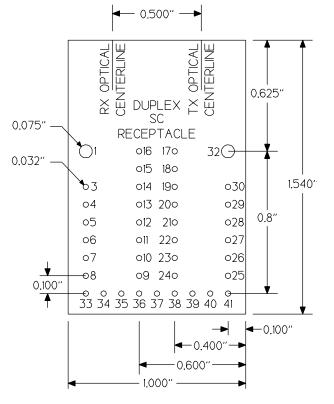

# JP4—OLC-Compatibility Connector

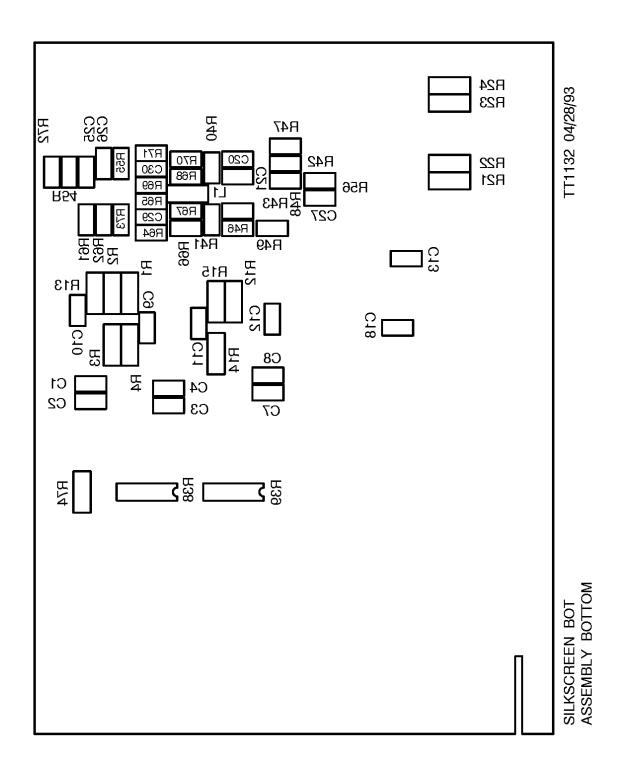

The JP4 (OLC-compatibility) connector is located on the bottom (passive-component) side of the board. Pin 1 of this connector is identified on the board by a square solder pad. The remaining pins use a round solder pad.

For the CY9266 Evaluation Board, pins of sufficient length are present so that analysis equipment may be attached to these signal pins on the top (active-component) side of the board

# Figure 3. JP3 Pin Numbering, Edge of Board

Board View (Pins Are On the Bottom)

while it is plugged into a mating connector. The numbering sequence for the JP4 connector pins is shown in *Figure 4*.

The connector is made from forty-eight 0.025" square pins soldered into the board. To allow full mating with an OLC-compatible connector, these pins must extend at least 0.250" beyond the bottom surface of the board.

# **Connector Pinouts**

The CY9266 provides three interface connectors to the user: JP2, JP3, and JP4. *Table 1* shows which signal is present on each connector pin.

| Pin<br>No. | JP3         | JP2         | JP4        | Pin<br>No. | JP3          | JP2          | JP4          |

|------------|-------------|-------------|------------|------------|--------------|--------------|--------------|

| 1          | SYNC_POL    | SYNC_POL    | REC_9      | 31         | RCV_CLK1     | RCV_CLK1     | VCC          |

| 2          | CD_POL      | CD_POL      | GND        | 32         | GND          | GND          | XMIT_6       |

| 3          | DIP_FOTO    | DIP_FOTO    | REC_6      | 33         | RCV_CLK0     | RCV_CLK0     | XMIT_3       |

| 4          | DIP_RCVA/B  | DIP_RCVA/B  | REC_4      | 34         | VCC          | VCC          | XMIT_0       |

| 5          | RCV_MODE    | RCV_MODE    | VCC        | 35         | XMIT_8       | XMIT_8       | GND          |

| 6          | SWRCVBISTEN | SWRCVBISTEN | REC_0      | 36         | GND          | GND          | LOOP_BACK    |

| 7          | REC_9       | REC_9       | RCV_CLK1   | 37         | ENBYTESYNC   | ENBYTESYNC   | BYTE_SYNC    |

| 8          | XMIT_ENA    | XMIT_ENA    | VCC        | 38         | RESET        | RESET        | LINK_STATUS  |

| 9          | REC_6       | REC_6       | XMIT_4     | 39         | XMIT_7       | XMIT_7       | GND          |

| 10         | XMIT_MODE   | XMIT_MODE   | XMIT_1     | 40         | GND          | GND          | GND          |

| 11         | REC_8       | REC_8       | GND        | 41         | XMIT_6       | XMIT_6       | GND          |

| 12         | XMIT_ENN    | XMIT_ENN    | XMITCLOCK  | 42         | VCC          | VCC          | XMIT_9       |

| 13         | REC_5       | REC_5       | REC_8      | 43         | XMIT_3       | XMIT_3       | XMIT_8       |

| 14         | XMIT_BISTEN | XMIT_BISTEN | REC_5      | 44         | GND          | GND          | XMIT_7       |

| 15         | REC_2       | REC_2       | VCC        | 45         | XMIT_4       | XMIT_4       | N/C          |

| 16         | GND         | GND         | REC_3      | 46         | RDY          | RDY          | XMIT_5       |

| 17         | REC_7       | REC_7       | REC_1      | 47         | XMIT_0       | XMIT_0       | LINK_CONTROL |

| 18         | GND         | GND         | GND        | 48         | VCC          | VCC          | VCC          |

| 19         | LINK_STATUS | LINK_STATUS | RCV_CLK0   | 49         | XMIT_5       | XMIT_5       |              |

| 20         | BYTE_SYNC   | BYTE_SYNC   | ENBYTESYNC | 50         | GND          | GND          |              |

| 21         | REC_4       | REC_4       | GND        | 51         | XMIT_2       | XMIT_2       |              |

| 22         | VCC         | VCC         | XMIT_2     | 52         | GND          | GND          |              |

| 23         | REC_3       | REC_3       | N/C        | 53         | XMIT_1       | XMIT_1       |              |

| 24         | EXTREFCLK   | EXTREFCLK   | VCC        | 54         | RP           | RP           |              |

| 25         | REC_0       | REC_0       | REC_7      | 55         | GND          | GND          |              |

| 26         | GND         | GND         | GND        | 56         | XMITCLOCK    | XMITCLOCK    |              |

| 27         | REC_1       | REC_1       | REC_2      | 57         | LINK_CONTROL | LINK_CONTROL |              |

| 28         | VCC         | VCC         | N/C        | 58         | LOOP_BACK    | LOOP_BACK    |              |

| 29         | XMIT_9      | XMIT_9      | GND        | 59         | GND          |              |              |

| 30         | GND         | GND         | RESET      | 60         | GND          |              |              |

## Table 1. I/O Connector Pinouts

# **Signal Naming Conventions**

There are three types of signal names used throughout this document: I/O connector pin names, on-board signal names, and HOTLink Transmitter and Receiver pin names. Except for the transmit and receive data buses, these names are unique.

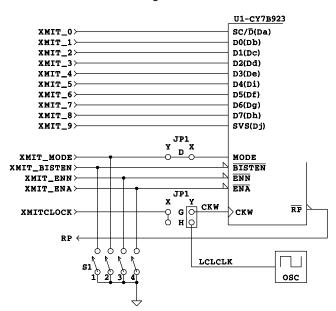

The names used for the transmit and receive data bus pins on connectors JP2, JP3, and JP4 are different from the signal names present on the HOTLink Transmitter and Receiver. The functional names for these signals also change depending on the current operating mode of the HOTLink Transmitter or Receiver. *Table 2* lists the transmit data bus signals and the names mapped to them in each transmitter mode.

The output data bus from the HOTLink Receiver is pipelined with a single register stage between the receiver outputs and the board output pins. *Table 3* lists the receive data bus signals and the names mapped to them in each receiver mode.

| Transmit Bus   | HOTLink Transı | mitter Pin Name |

|----------------|----------------|-----------------|

| Input Pin Name | Encoded Mode   | Bypass Mode     |

| XMIT_0         | SC/D           | Da              |

| XMIT_1         | D0             | Db              |

| XMIT_2         | D1             | Dc              |

| XMIT_3         | D2             | Dd              |

| XMIT_4         | D3             | De              |

| XMIT_5         | D4             | Di              |

| XMIT_6         | D5             | Df              |

| XMIT_7         | D6             | Dg              |

| XMIT_8         | D7             | Dh              |

| XMIT_9         | SVS            | Dj              |

Table 2. Transmit Bus Signal Name Map

| Receive Bus     | HOTLink Receiver Pin Name |             |  |  |

|-----------------|---------------------------|-------------|--|--|

| Output Pin Name | Decode Mode               | Bypass Mode |  |  |

| REC_0           | SC/D                      | Qa          |  |  |

| REC_1           | Q0                        | Qb          |  |  |

| REC_2           | Q1                        | Qc          |  |  |

| REC_3           | Q2                        | Qd          |  |  |

| REC_4           | Q3                        | Qe          |  |  |

| REC_5           | Q4                        | Qi          |  |  |

| REC_6           | Q5                        | Qf          |  |  |

| REC_7           | Q6                        | Qg          |  |  |

| REC_8           | Q7                        | Qh          |  |  |

| REC_9           | RVS                       | Qj          |  |  |

# Table 3. Receive Bus Signal Name Map

# **Signal Descriptions**

The I/O signals listed in *Table 1* fall into six groups: power, switched control, control, status, clock, and data. These signals are described in *Table 4*.

# Table 4. I/O Signal Descriptions

| Signal Name     | Group                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | Power                      | +5 VDC @ 1.0A typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GND             | Power                      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XMIT_BISTEN     | Input, Switched<br>Control | <b>Transmitter BIST Enable (S1-1).</b> When this signal is LOW, the HOTLink Transmitter is placed into its BIST mode. Exact operation of the transmitter is also determined by the settings of the ENA (S1-4) and ENN (S1-3) signals. With both ENA and ENN HIGH, the transmitter outputs an alternating 0–1 pattern (D10.2 or D21.5). If either ENA or ENN is LOW, the transmitter sends a repeating 511-character test sequence. The receiver contains a matching mode that allows this transmitter BIST mode to be used to test the entire serial link without external hardware. The transmitter BIST enable is kept separate from the receiver BIST enable on this board to allow each component to be tested with external patterns that are not part of the BIST sequence. |

| XMIT_MODE       | Input, Switched<br>Control | <b>Encoder Mode Select (S1-2).</b> This signal is used to select whether pre-encoded (10-bit) or non-encoded (8-bit) data is clocked into the HOTLink Transmitter. When LOW (Encoded mode), this input enables the internal 8B/10B encoder and accepts 8-bit parallel data from the transmitter data bus (D0–D7 as listed in <i>Table 2</i> ). When HIGH (Bypass mode), the encoder is bypassed and a 10-bit pattern is accepted (Da–Dj as listed in <i>Table 2</i> ).                                                                                                                                                                                                                                                                                                            |

| XMIT_ENN        | Input, Switched<br>Control | <b>Enable Next Parallel Transmitter Data (S1-3).</b> This signal is used to control when data is loaded into the HOTLink Transmitter. When this signal is LOW at the rising edge of CKW, the data present on the transmitter inputs at the next rising edge of CKW is loaded, processed, and sent. When this signal is HIGH, the transmitter ignores the data present on its inputs at the next rising edge of CKW and instead inserts a SYNC character (K28.5) to fill in the data stream. When ENA is used for data control, the ENN signal should be tied HIGH, but may be used to enable BIST mode.                                                                                                                                                                           |

| XMIT_ENA        | Input, Switched<br>Control | <b>Enable Parallel Transmitter Data (S1-4).</b> This signal is used to control when data is loaded into the HOTLink Transmitter. When LOW at the rising edge of CKW, the data present on the transmitter inputs is loaded, processed, and sent. When this signal is HIGH, the transmitter ignores the data present on its inputs and instead inserts a SYNC character (K28.5) to fill in the data stream. When ENN is used for data control, the ENA signal should be tied HIGH, but may be used to enable BIST mode.                                                                                                                                                                                                                                                             |

| SWRCVBISTEN     | Input, Switched<br>Control | <b>Receiver BIST Enable (S1-5).</b> When this signal is LOW, the HOTLink Receiver monitors the data stream for the BIST loop initialization character (D0.0). This signal also enables the BIST PLD (CY7C344–U8), which is used to monitor the progress and status of the BIST loop through the receiver RDY and RVS outputs. When the receiver detects the initialization character, it begins comparing received data with a built-in data sequence that can be used to verify the proper functionality of the transmitter, receiver, and the serial link connecting them. The receiver BIST enable is kept separate from the transmitter BIST enable on this board to allow each component to be tested with external patterns that are not part of the BIST sequence.         |

| RCV_MODE        | Input, Switched<br>Control | <b>Receiver Mode Select (S1-6).</b> This signal is used to select whether encoded (10-bit) or non-encoded (8-bit) data is output from the receiver. When LOW (Decode mode), this input enables the internal 10B/8B decoder and outputs 8-bit parallel data (Q0–Q7 as listed in <i>Table 3</i> ). When HIGH (Bypass mode), the decoder is bypassed and a 10-bit pattern is output (Qa–Qj as listed in <i>Table 3</i> ).                                                                                                                                                                                                                                                                                                                                                            |

# Table 4. I/O Signal Descriptions (continued)

| Signal Name | Group                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

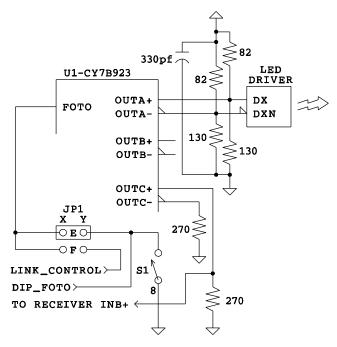

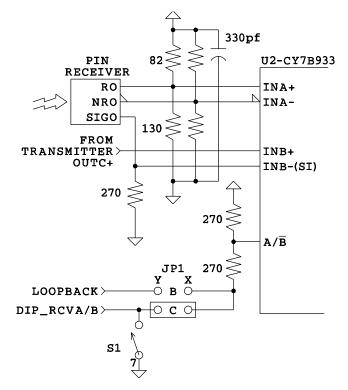

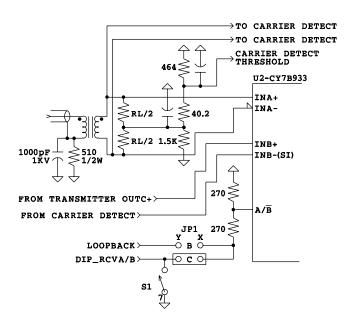

| DIP_RCVA/B  | Input, Switched<br>Control | <b>DIP-Switch Controlled Receiver</b> $A/\overline{B}$ <b>Port Select (S1-7).</b> This signal is used to determine which port (INA± or INB±) the receiver uses for the input serial data stream. When LOW, this signal selects the receiver B port that is directly connected to the C port on the transmitter. When HIGH, this signal selects the receiver A port that is connected to the optical receiver output. This signal is also routed through jumper block JP1. In order for this signal to control the port selection of the receiver, it is necessary to have a shorting jumper across the X and Y pins of JP1-C. To allow the LOOP_BACK signal on the I/O connectors (JP2, JP3, and JP4) to control the $A/\overline{B}$ port selection, this jumper should be moved to JP1-B.                                                                                                                                                                                                                                                 |

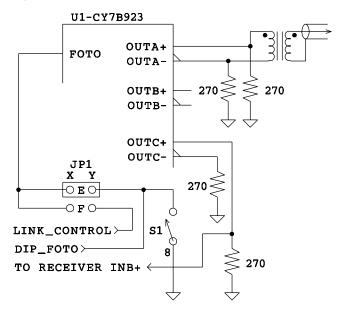

| DIP_FOTO    | Input, Switched<br>Control | <b>DIP-Switch Controlled FOTO (S1-8).</b> This signal is used to enable the A and B differential output drivers of the HOTLink Transmitter. When this signal is LOW, the differential outputs are allowed to follow the pattern of the data serialized by the transmitter. When this signal is HIGH, the A and B differential outputs of the transmitter are driven to a logic zero state (+ output is logic HIGH, – output is logic LOW). This places an attached optical transmitter in a state where no light is output. This signal is also routed through jumper block JP1. In order for this signal to control the FOTO (fiber-optic transmitter-off) enable on the transmitter, it is necessary to have a shorting jumper across the X and Y pins of JP1-E. To allow the LINK_CONTROL signal on the I/O connectors (JP2, JP3, and JP4) to control the FOTO enable, this jumper should be moved to JP1-F.                                                                                                                             |

| CD_POL      | Input, Switched<br>Control | <b>Signal-Detect Polarity Select (S1-9).</b> This input selects the output polarity of the LINK_STATUS signal. When LOW, the LINK_STATUS signal is HIGH when a valid signal is present. When HIGH, the LINK_STATUS signal is LOW when a valid signal is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SYNC_POL    | Input, Switched<br>Control | <b>Byte Sync Polarity Select (S1-10).</b> This input, in conjunction with the HOTLink Receiver MODE input, selects the active level of the BYTE_SYNC signal. When LOW with the receiver in Bypass mode, the BYTE_SYNC signal is LOW when a K28.5 SYNC character is present on the receive data bus. When HIGH with the receiver in Bypass mode, the BYTE_SYNC signal is HIGH when a K28.5 SYNC character is present on the receive data bus. When HIGH with the receiver in Bypass mode, the BYTE_SYNC signal is HIGH when a K28.5 SYNC character is present on the receive data bus. When LOW with the receiver in Decode mode, the BYTE_SYNC output remains HIGH for strings of K28.5 SYNC characters, or while awaiting the first K28.5 SYNC character after being placed into Reframe mode (RF is set HIGH). When HIGH with the receiver in Decode mode, the BYTE_SYNC output remains LOW for strings of K28.5 SYNC characters, or while awaiting the first K28.5 SYNC character after being placed into Reframe mode (RF is set HIGH). |

| LOOP_BACK   | Input, Control             | <b>Loopback Control.</b> This signal is used to determine which port (A or B) the HOTLink Receiver uses for the input serial data stream. When LOW, this signal selects the receiver B port that is connected directly to the transmitter C port. When HIGH, this signal selects the receiver A port that is connected to the optical receiver output. This signal is also routed through jumper block JP1. In order for this signal to control the port selection of the receiver, it is necessary to have a shorting jumper across the X and Y pins of JP1-B. To allow the DIP_RCVA/B signal (S1-7, also present on JP2 and JP3) to control the A/B port selection, this jumper should be moved to JP1-C.                                                                                                                                                                                                                                                                                                                                 |

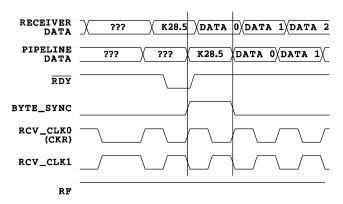

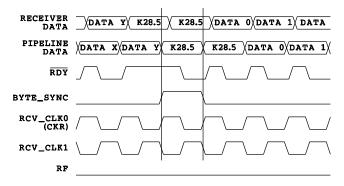

| ENBYTESYNC  | Input, Control             | <b>Enable Byte Sync Detect.</b> This signal controls when the HOTLink Receiver is allowed to reframe to the incoming serial data (e.g., acquire character sync). When this signal is HIGH, each K28.5 SYNC character received in the shifter will frame the data that follows. When this signal is LOW, the framing logic in the receiver is disabled. Because the CKR output of the receiver must line up with the reframed data, it is possible to generate significant phase jumps in the CKR clock. To prevent the generation of very short high or low pulses on the CKR output (which could cause timing violations in downstream logic) the Cypress HOTLink Receiver uses look-ahead hardware to prevent these short pulses. Instead, a portion of the clock period for the character preceding the reframed data is lengthened.                                                                                                                                                                                                     |

| Table 4. | I/O Signal Descriptions | (continued) |

|----------|-------------------------|-------------|

|----------|-------------------------|-------------|

| Signal Name      | Group                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LINK_<br>CONTROL | Input, Control          | Link Control. This signal is used to enable the A and B differential output drivers<br>of the HOTLink Transmitter. When this signal is LOW, the differential outputs are<br>allowed to follow the pattern of the data serialized by the transmitter. When this<br>signal is HIGH, the A and B differential outputs of the transmitter are driven to a<br>logic zero state (+ output is logic HIGH, – output is logic LOW). This places an<br>attached optical transmitter in a state where no light is output. This signal is also<br>routed through jumper block JP1. In order for this signal to control the FOTO enable<br>on the transmitter, it is necessary to have a shorting jumper across the X and Y<br>pins of JP1-F. To allow the DIP_FOTO signal on the I/O connectors (JP2 and JP3)<br>to control the FOTO enable, this jumper should be moved to JP1-E.                                                                           |  |

| RESET            | Output, Status          | <b>Reset/Power OK.</b> This output is used to emulate the voltage monitor function present on the OLC card. It remains active (LOW) until the $V_{CC}$ input to the board is above 4.65V DC. This output also becomes active when the BIST RESET switch (S2) is pressed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| LINK_STATUS      | Output, Status          | <b>Link Status.</b> This signal operates as a signal-detect status for the serial interface.<br>The polarity of this signal is determined by the CD_POL input (S1-9). When<br>CD_POL is LOW, LINK_STATUS drives HIGH when a signal is present. When<br>CD_POL is HIGH, LINK_STATUS drives LOW when a signal is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| RP               | Output, Clock           | <b>Read Pulse.</b> This is a 60% LOW duty-cycle pulse train suitable for clocking data out of Cypress's CY7C42X family of asynchronous FIFOs. This pulse is generated by the HOTLink Transmitter in response to the XMIT_ENA input being active at the rising edge of CKW. For repeated pulses the RP period is the same as CKW, yet is totally independent of the duty cycle of CKW. When the transmitter is in BIST mode, the RP signal remains HIGH for all but the last character of the BIST loop, where it pulses LOW.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| XMITCLOCK        | Input, Output,<br>Clock | <b>Transmitter External Clock.</b> This is the external character-rate clock input. This clock is used to drive the transmitter CKW input. To allow for operation using the on-board oscillator, the XMITCLOCK signal is run through jumper block JP1. To operate using an external HOTLink Transmitter clock source, a shorting jumper should be placed across pins X and Y of JP1-G. To use the on-board oscillator instead, this shorting jumper should be moved to connect pin JP1-GY to JP1-HY. When operated from XMITCLOCK, the receiver REFCLK may also be set to use this same clock. This is done by placing a shorting jumper across pins JP1-HX and JP1-IX. To allow the receiver REFCLK to operate from the on-board oscillator, this jumper should be moved to connect the X and Y pins of JP1-I. The on-board oscillator may also be driven out on the XMITCLOCK line by placing a shorting jumper across pins X and Y of JP1-H.  |  |

| EXTREFCLK        | Input, Output,<br>Clock | <b>External Reference Clock.</b> This character-rate clock is used to drive the HOTLink Receiver REFCLK from an external source other than XMITCLOCK. This input may be used to test the tracking and capture range of the receiver PLL. It may also be used to operate the receiver at a different data rate from the transmitter. To allow the receiver PLL to properly lock to the received serial stream, this clock must be within 0.1% of the clock used to generate the received serial data. To drive the receiver REFCLK from this clock source, a shorting jumper should be placed across pins JP1-IX and JP1-JX.<br>The on-board oscillator may also be selected to drive the EXTREFCLK line by placing a shorting jumper across pins X and Y of JP1-J. With this jumper in place it is still possible to drive the receiver REFCLK input from the on-board oscillator by placing a shorting jumper across the X and Y pins of JP1-I. |  |

| RCV_CLK0         | Output, Clock           | <b>Receive Clock 0.</b> This is the character-rate recovered clock used for received data. The period of this clock is determined by the serial data rate entering the HOTLink Receiver. The duty-cycle of this signal is determined by the receiver and is fixed at 50%. This clock may experience a large phase jump when reframing to a serial data stream. The phasing on this clock is such that the rising edge of the clock occurs coincident with the start of each interval where a character is present on the output received data bus. This signal is a buffered form of the HOTLink Receiver CKR clock.                                                                                                                                                                                                                                                                                                                             |  |

| Table 4. | I/O Signal Descriptions | (continued) |

|----------|-------------------------|-------------|

|----------|-------------------------|-------------|

| Signal Name | Group         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCV_CLK1    | Output, Clock | <b>Receive Clock 1.</b> This is the character-rate recovered clock used for received data. The period of this clock is determined by the serial data rate entering the HOTLink Receiver. The duty-cycle of this signal is determined by the receiver and is fixed at 50%. This clock may experience a large phase jump when reframing to a serial data stream. The phasing on this clock is such that the rising edge of the clock occurs near the center of each interval where a character is present on the output received data bus. This signal is a buffered and inverted form of the HOTLink Receiver CKR clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RDY         | Output, Clock | <b>RDY</b> (Ready). This signal is used both as a HOTLink Receiver data output clock<br>and a status indicator for the receiver when in BIST mode. This is an unbuffered<br>output from the receiver. It is normally used to clock valid data from the receiver<br>data bus into synchronous FIFOs. Because of the additional pipeline register in the<br>data bus (added for OLC compatibility) this signal will operate one character <i>prior</i><br>to the data being available at the I/O connectors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BYTE_SYNC   | Output, Data  | <b>Byte Sync Detected.</b> This signal is a pipelined form of the receiver RDY output.<br>This additional pipeline stage for the RDY signal (and the rest of the receiver data<br>bus) was added to match the specific timing of the OLC Byte Sync signal. The<br>active level of this output is determined both by the operating mode of the HOTLink<br>Receiver and by the state of the SYNC_POL input.<br>With the HOTLink Receiver in Bypass mode, the BYTE_SYNC signal is used as a<br>K28.5 SYNC character indicator. With SYNC_POL LOW, BYTE_SYNC is LOW<br>when a K28.5 SYNC character is present on the receive data bus. With SYNC_POL<br>HIGH, BYTE_SYNC is HIGH when a K28.5 SYNC character is present on the<br>receive data bus.<br>With the receiver in Decode mode, the BYTE_SYNC signal is used as a valid data<br>indicator. With SYNC_POL LOW, BYTE_SYNC is LOW whenever a usable data<br>character is present on the receive data bus. With SYNC_POL HIGH, BYTE_SYNC<br>is HIGH whenever a usable data character is present on the receive data bus. |

| REC_9       | Output, Data  | <b>RVS(Qj).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver RVS(Qj) signal. This termination and additional pipeline stage for the RVS(Qj) signal (and the rest of the receive data bus) was added to match the specific timing and signal characteristics of the OLC card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| REC_8       | Output, Data  | <b>Q7(Qh).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q7(Qh) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_7       | Output, Data  | <b>Q6(Qg).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q6(Qg) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_6       | Output, Data  | <b>Q5(Qf).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q5(Qf) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_5       | Output, Data  | <b>Q4(Qi).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q4(Qi) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_4       | Output, Data  | <b>Q3(Qe).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q3(Qe) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_3       | Output, Data  | <b>Q2(Qd).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q2(Qd) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_2       | Output, Data  | <b>Q1(Qc).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q1(Qc) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_1       | Output, Data  | <b>Q0(Qb).</b> This signal is a series-terminated, pipelined form of the HOTLink Receiver Q0(Qb) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REC_0       | Output, Data  | <b>SC/D</b> (Qa). This signal is a series-terminated, pipelined form of the HOTLink Receiver SC/D(Qa) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XMIT_9      | Input, Data   | <b>SVS(Dj).</b> This signal is the SVS(Dj) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Table 4. | I/O Signal Descriptions | (continued) |

|----------|-------------------------|-------------|

|----------|-------------------------|-------------|

| Signal Name | Group       | Description                                                                                                                                                                                                        |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XMIT_8      | Input, Data | <b>D7(Dh).</b> This signal is the D7(Dh) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_7      | Input, Data | <b>D6(Dg).</b> This signal is the D6(Dg) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_6      | Input, Data | <b>D5(Df).</b> This signal is the D5(Df) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_5      | Input, Data | <b>D4(Di).</b> This signal is the D4(Di) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_4      | Input, Data | <b>D3(De).</b> This signal is the D3(De) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_3      | Input, Data | <b>D2(Dd).</b> This signal is the D2(Dd) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_2      | Input, Data | <b>D1(Dc).</b> This signal is the D1(Dc) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_1      | Input, Data | <b>D0(Db).</b> This signal is the D0(Db) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by ENA or ENN.                                               |

| XMIT_0      | Input, Data | <b>SC/D</b> (Da). This signal is the SC/D(Da) input to the HOTLink Transmitter. It is latched into the transmitter in the rising edge of CKW, when enabled by $\overline{\text{ENA}}$ or $\overline{\text{ENN}}$ . |

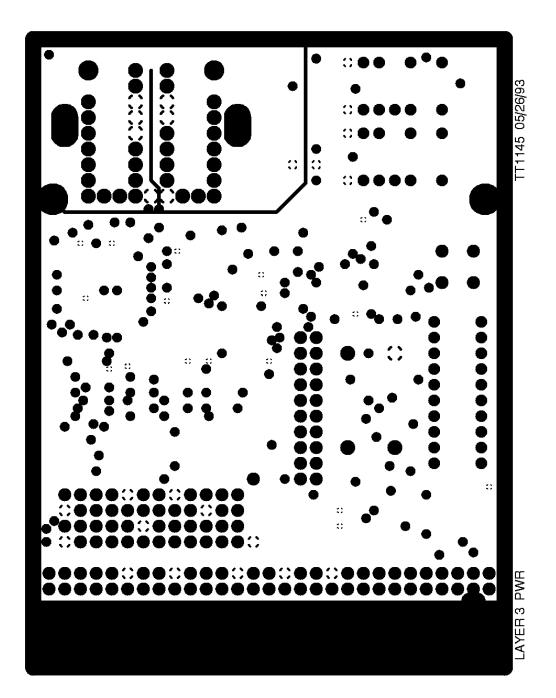

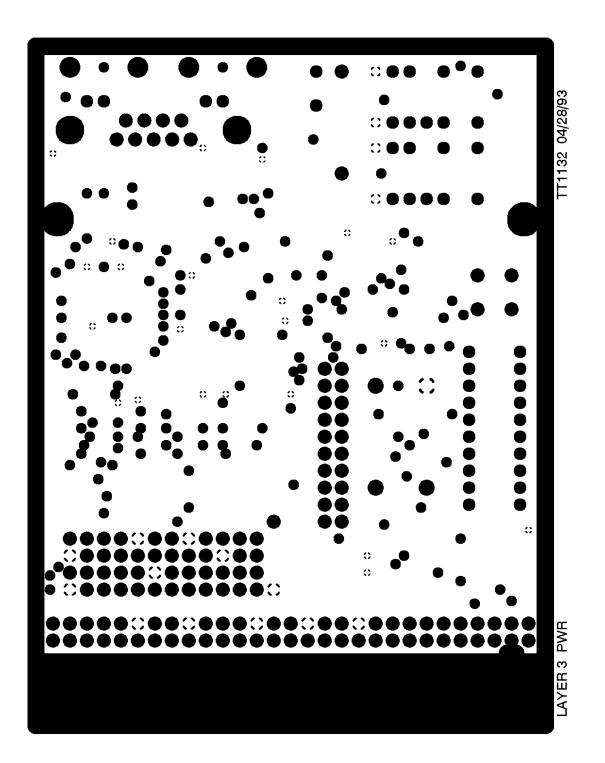

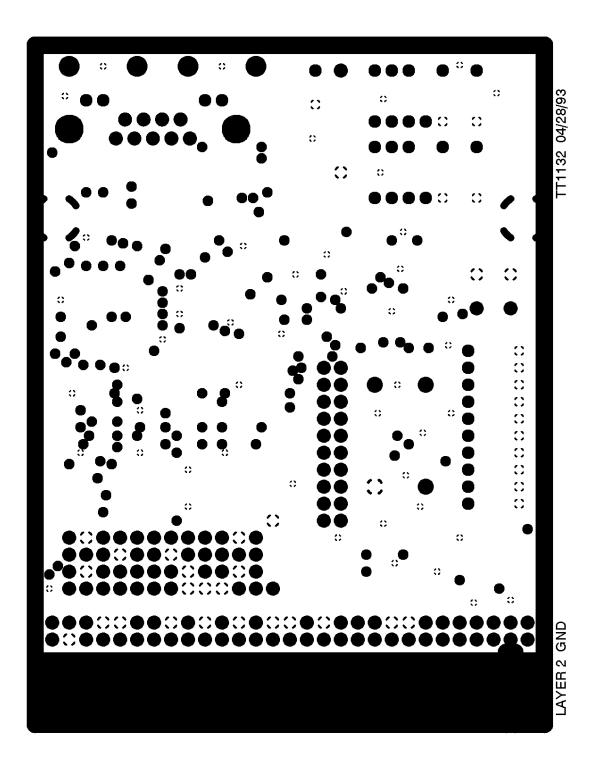

# **Power Signals**

The CY9266 Evaluation Board is designed to operate from a single +5V  $\pm$ 10% DC supply capable of delivering 1.0A (typical). All V<sub>CC</sub> and GND pins on JP2, JP3, and JP4 are (respectively) common to each other. There are no distinctions made for separate supplies pins for the different logic sections.

# Switched Control Signals

The CY9266 Evaluation Board contains a 10-position DIP switch (S1). This switch is connected in parallel with a number of control signals on JP2 and JP3. Each of these control signals is pulled-up by a 5-k $\Omega$  resistor through R-pack R20. None of these Switched Control signals are available at the JP4 connector.

The signals present in this group are:

- XMIT\_BISTEN (S1-1)

- XMIT\_MODE (S1-2)

- XMIT\_ENN (S1-3)

- XMIT\_ENA (S1-4)

- SWRCVBISTEN (S1-5)

- RCV\_MODE (S1-6)

- DIP\_RCVA/B (S1-7)

- DIP\_FOTO (S1-8)

- CD\_POL (S1-9)

- SYNC\_POL (S1-10)

To allow these signals to be controlled through the external connectors (JP2 and JP3), the corresponding S1 switch must be in the off (open) position. Care should be taken when driving these signals, as any switch inadvertently left in the closed position will present a direct short to ground for an attached driver.

# **Control Signals**

In addition to the Switched Control signals that are only present on JP2 and JP3, three additional control inputs are present that connect to JP2, JP3, and JP4.

These control signals are:

- LOOP\_BACK

- ENBYTSYNC

- LINK\_CONTROL

These control inputs are connected directly to the HOTLink Transmitter or Receiver. Because the HOTLink parts contain internal pull-up resistors on their TTL compatible inputs, these signals may be driven with either open-collector buffers, CMOS, or TTL drive levels.

# **Status Signals**

Two status output signals (RESET and LINK\_STATUS) are provided at all three I/O connectors. The RESET signal is a slow-speed signal and does not require the series termination used with LINK\_STATUS.

# **Clock Signals**

Six signals are available at the I/O connectors that are used as clocks in some form. Two of these (XMITCLOCK and EXTREFCLK) are input/output clocks that are routed through the JP1 jumper block, and three are output clocks.

These clock signals are:

- XMITCLOCK

- EXTREFCLK

- RP

- RDY

- RCV\_CLK0

- RCV\_CLK1

Of the output clocks, the  $\overline{RP}$  and  $\overline{RDY}$  signals are only available at JP2 and JP3. The  $\overline{RP}$  signal is generated in the HOTLink Transmitter and is used for reading data from asynchronous FIFOs, while the  $\overline{RDY}$  signal is generated in the HOTLink Receiver and is used for writing data into asynchronous FIFOs. When interfacing to synchronous FIFOs, the  $\overline{RP}$  signal is not normally used. Because these signals are not present in JP4, they are not series terminated.

The other two output clocks (RCV\_CLK0 and RCV\_CLK1) are a buffered form of the recovered CKR clock from the receiver. The RCV\_CLK1 signal is an inverted form of RCV\_CLK0.

# **Data Signals**

The CY9266 Evaluation Board has two data buses: one input (to the HOTLink Transmitter) and one output (from the HOTLink Receiver).

The input data bus consists of ten parallel transmit data signals that are sampled at the rising edge of the HOTLink Transmitter CKW clock. In addition to these ten signals, ENN and ENA (while part of the Switched Control signals) may also be considered part of the data bus as they are also sampled at this same time. While the XMIT\_BISTEN input is also sampled at this same time, it is not normally used to transfer data and is therefore not considered part of the input data bus.

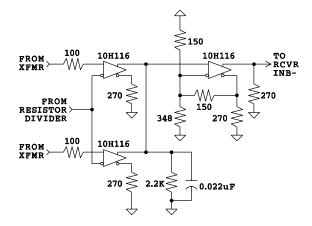

The output data bus is comprised of ten parallel received data signals that are synchronous to the HOTLink Receiver CKR clock. To meet specific timing requirements for OLC compatibility, there is also an external pipeline register between the HOTLink Receiver data bus output, and the received data bus connected to JP2, JP3, and JP4.

One other signal, BYTE\_SYNC, is also clocked through this pipeline register and is thus considered part of the data bus.

All signals on this output bus are series-terminated with a  $22\Omega$  inline resistor to minimize transmission line ringing.

# **Configuration Settings**

The CY9266 board may be user-configured to allow many modes of operation. This configuration is performed through the jumper block JP1 and the option select switch S1.

# JP1 Jumper Block

The JP1 jumper block is used for configuring those options of the CY9266 that are (primarily) either to protect the board from signal contention, or for those signals having multiple sources and destinations. These functions are:

- Receiver Mode Select

- Receiver Loopback Source Select

- Transmitter Mode Select

- Transmitter FOTO Source Select

- Transmitter Clock (CKW) Source Select

- Receiver Reference Clock (REFCLK) Source Select

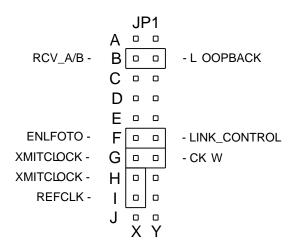

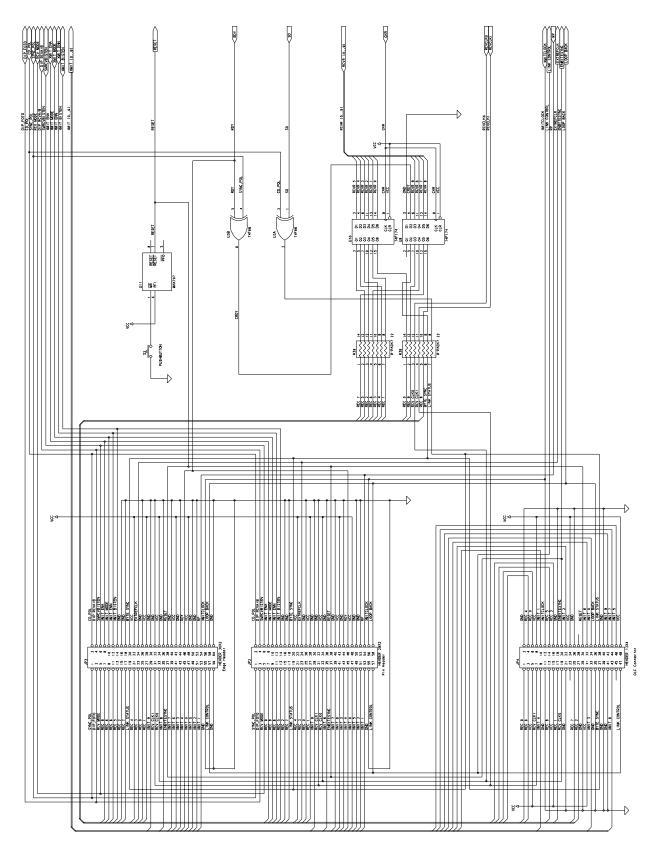

JP1 exists as a 2 x 10 matrix of 0.025" square pins on the top of the board. The rows in this matrix are identified on the top silk screen as A through J. The columns are identified as X and Y. A drawing of the JP1 jumper block is shown in *Figure 5*.

# Receiver Mode Select

This jumper ties pins X and Y of JP1-A together. It is used to connect the receiver's MODE select pin to the option select

Figure 5. JP1, Top Side View

switch (S1-6), and to allow the HOTLink Receiver mode to be set to the clock Test mode (see *Figure 13*). The three modes of receiver operation are:

- Decode Mode—S1-6 ON (closed)

- Bypass Mode—S1-6 OFF (open)

- Test Mode—JP1-A, X and Y open

Because this clock Test mode is not normally used for communications testing, the jumper (JP1-A) is permanently wired in place with a foil trace on the bottom of the board. For those users who wish to actually place the receiver in Test mode, it may be necessary to cut this foil on the back of the board.

Once this foil has been cut, it will be necessary to use a shorting jumper across pins X and Y of JP1-A to allow the two data modes of the receiver to be set by the option select switch (S1-6) and the RCV\_MODE signal on JP2 and JP3.

#### Receiver Source Loopback Select

This function uses two positions (JP1-B and JP1-C) of the jumper block to select the source of the HOTLink Receiver loopback signal. Because this jumper is used to select between one of two sources, only one of these two positions (JP1-B or JP1-C) may contain a shorting jumper at any one time (see *Figures 10* and *11*).

By placing a shorting jumper across pins X and Y of JP1-B, the receiver loopback (A/B) input is then controlled by the LOOP\_BACK signal on JP2, JP3, and JP4. If this shorting jumper is moved to JP1-C, then the receiver loopback input is controlled by the option select switch (S1-7) and the RCV\_MODE signal on JP2 and JP3. If a jumper is not present in either position, the INA± path is selected (external serial data).

#### Transmitter Mode Select

This jumper ties pins X and Y of JP1-D together. It is used to connect the transmitter MODE select pin to the option select switch, and to allow the HOTLink Transmitter mode to be set to the clock Test mode (see *Figure 7*). The three modes of transmitter operation are:

Encode Mode—S1-2 ON (closed)

- Bypass Mode—S1-2 OFF (open)

- Test Mode—JP1-D, X and Y open

Because this clock Test mode is not expected to be used for normal data communications testing, the jumper (JP1-D) is permanently wired in place with a foil trace on the bottom of the board. For those users who wish to actually place the transmitter in Test mode, it may be necessary to cut this foil on the back of the board.

Once this foil has been cut, it will be necessary to use a jumper across JP1-D to allow the two data modes of the transmitter to be set by the option select switch (S1-2) and the XMIT\_MODE signal on JP2 and JP3.

#### Transmitter FOTO Source Select

This function uses two positions (JP1-E and JP1-F) of the jumper block to select the source of the HOTLink Transmitter FOTO signal. Because this jumper is used to select from one of two sources, only one of these two positions (E or F) may contain a jumper at any one time (see *Figures 8* and *9*).

By placing a shorting jumper across pins X and Y of JP1-F, the HOTLink Transmitter FOTO signal is then controlled by the LINK\_CONTROL signal on JP2, JP3, and JP4. If this shorting jumper is moved to JP1-E, then the transmitter FOTO signal is controlled by the option select switch (S1-8) and the DIP\_FOTO signal on JP2 and JP3. If a jumper is not present in either position, the transmitter OUTA± and OUTB± differential drivers are placed in a mode where a differential logic 0 is driven.

## Transmitter Clock Source Select

The HOTLink Transmitter CKW clock can be sourced from two different signals: LCLCLK from the on-board oscillator and XMITCLOCK from JP2, JP3, and JP4 (see *Figure 7*).

To select the on-board oscillator, a shorting jumper should be placed across pins JP1-GY and JP1-HY. To select the XMITCLOCK signal, this shorting jumper should be moved to connect pins X and Y of JP1-G. To allow the transmitter to operate, it is necessary for a jumper to be in one (and only one) of these two positions.

#### Receiver Reference Clock Source Select

The HOTLink Receiver REFCLK signal can be sourced from three different signals: LCLCLK from the on-board oscillator, XMITCLOCK (from JP2, JP3, and JP4), and EXTREFCLK (from JP2 and JP3) (see *Figure 13*).

To select the on-board oscillator, a shorting jumper should be placed across the X and Y pins of JP1-I. To select the XMITCLOCK signal, this shorting jumper should be moved to connect pin X of JP1-I to pin X of JP1-H. To select the EXTREFCLK signal (used for PLL range testing), the shorting jumper should be placed across pin X of JP1-I and pin X of JP1-J. To allow the receiver to operate it is necessary for a jumper to be in one (and only one) of these three positions.

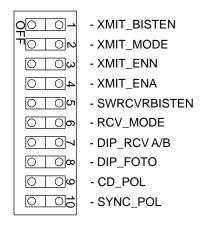

# S1 Option Select Switch

The S1 Option Select Switch is used for configuring those options of the CY9266 that may be changed on a regular basis or are used to operate the board in a standalone mode. These functions are:

- Transmitter BIST Enable

- Encoder Mode Select

- Enable Next Parallel Transmitter Data

- Enable Parallel Transmitter Data

- Receiver BIST Enable

- Receiver Mode Select

- Receiver A/B Port Select

- Transmitter FOTO Enable

- Signal-Detect Polarity

- Byte Sync Polarity

S1 exists as a 10-position DIP switch. The switch positions (numbered 1 through 10) are identified on the top of the switch. When a switch is on (closed), the signal connected to that switch is tied directly to ground. When a switch is off (open), the signal on that switch is pulled up through a 5-k $\Omega$  resistor in R-pack R20.

These signals are also connected to pins on JP2 and JP3 to allow external logic to control these functions. A drawing of the S1 option select switch is shown in *Figure 6*.

Figure 6. S1 Option Select Switch

# Transmitter BIST Enable

Switch S1-1 (XMIT\_BISTEN) is used to enable the HOTLink Transmitter BIST function. When this switch is on (closed), the BISTEN input to the transmitter is pulled LOW, placing the transmitter into its BIST loop. The exact patterns transmitted are determined by the levels on the XMIT\_ENN and XMIT\_ENA signals, located on S1-3 and S1-4 respectively (see *Figure 7*).

# Encoder Mode Select

Switch S1-2 (XMIT\_MODE) is used to select the data encoding mode of the HOTLink Transmitter. When this switch is on (closed), the internal 8B/10B encoder is enabled and the 8-bit data characters are encoded into 10-bit transmission characters. When this switch is off (open), the encoder is bypassed and the transmitter accepts 10-bit patterns for direct serialization (see *Figure 7*).

# Enable Next Parallel Transmitter Data

Switch S1-3 (XMIT\_ENN) is used, along with S1-1 (transmitter BIST enable) and S1-4 (XMIT\_ENA), to select which data patterns are sent during HOTLink Transmitter BIST operations (see *Figure 7*).

If BIST is enabled (S1-1 on and S1-4 off), setting this switch off (open) causes the transmitter to send an alternating 1-0 pattern (D10.2 or D21.5). When turned on (closed), it enables an internal pattern generator in the transmitter that generates a repeating sequence of 511 10-bit patterns.

For normal data transfer operations this switch should remain off, with the XMIT\_ENN signal controlled externally through JP2 and JP3.

## Enable Parallel Transmitter Data

Switch S1-4 (XMIT\_ENA) is used, along with S1-1 (transmitter BIST enable) and S1-3 (XMIT\_ENN), to select which data patterns are sent by the HOTLink Transmitter during BIST operations (see *Figure 7*).

If BIST is enabled (S1-1 on and S1-3 off), setting S1-4 off (open) causes the transmitter to send an alternating 1-0 pattern (D10.2 or D21.5). When turned on (closed), it enables an internal pattern generator in the transmitter that produces a repeating sequence of 511 10-bit patterns.

For normal data transfer operations this switch should remain off, with the XMIT\_ENA signal controlled externally through JP2 and JP3.

When operated from the JP4 system connector, this switch should be turned on (closed), because the system hardware is required to provide a valid 10-bit transmission character or data character for each CKW clock.

#### Receiver BIST Enable

Switch S1-5 (SWRCVBISTEN) is used to enable the HOTLink Receiver BIST function (see *Figure 13*). When this switch is on (closed), the receiver awaits a D0.0 transmission character (sent once per BIST loop). When this character is detected the BIST state machine in the receiver begins matching the following received transmission characters with its internal pattern generator. This pattern generator follows the same sequence of patterns as those sent by the HOTLink Transmitter when sending its BIST sequence.

When this switch is off (open), the HOTLink Receiver operates in one of its two data modes (Decode or Bypass).

# Receiver Mode Select