# 128 Kb Dual-Port SRAM with PCI Bus Controller (PCI-DP)

#### **Features**

- 128 Kb of dual-ported shared memory

- Master and Target PCI Specification 2.2 compliant interface

- Embedded host bridge capability

- Direct interface to many microprocessors

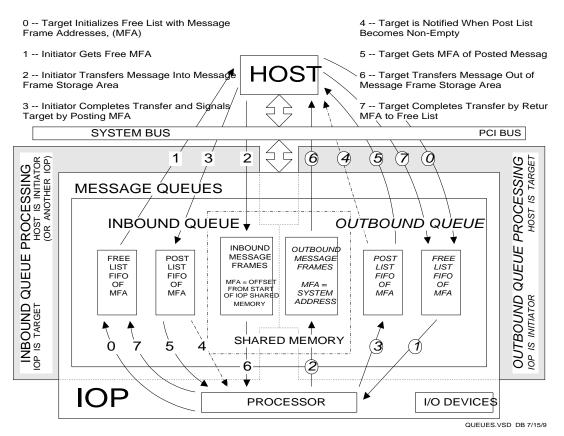

- I<sub>2</sub>O message transport unit; includes four 32-bit, 32-entry FIFO

- · Local bus clock rates up to 50 MHz

- Single 3.3V Power Supply including compatibility with 3V and 5V PCI Bus signaling

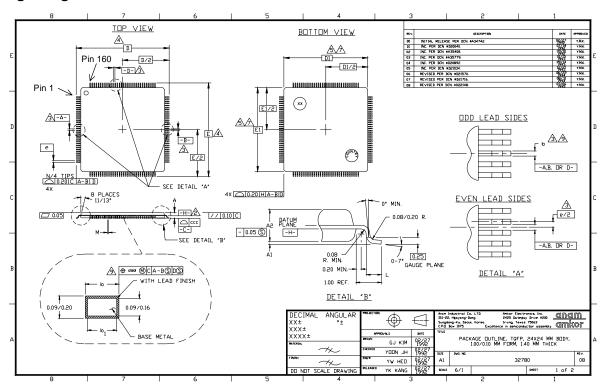

- · 160-pin thin plastic quad flat package

#### Introduction

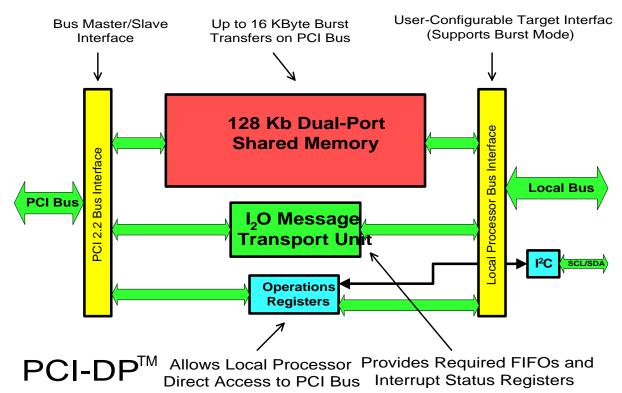

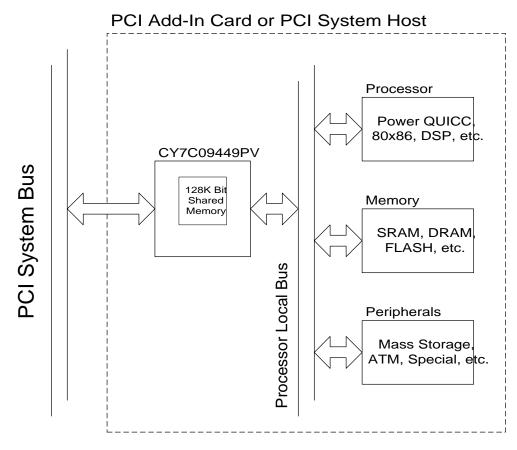

The CY7C09449PV is one of the PCI interface controllers in the Cypress Semiconductor PCI-DP™ family. The CY7C09449PV provides a PCI master/target interface with direct connections to many popular microprocessors. It provides 128 Kb of dual-port SRAM that is used as shared memory between the local microprocessor and the PCI bus. An I₂O message unit, complete with message queues and interrupt capability, is also provided. The CY7C09449PV allows the designer to interface an application to the PCI bus in a straightforward, inexpensive way.

#### **Functional Overview**

The CY7C09449PV is composed of a number of shared resources that allow effective data movement between the local bus and the PCI bus.

A primary resource within the CY7C09449PV is its 128 Kb of dual-port memory. This memory is interfaced to both the PCI bus and to a local microprocessor bus. This shared memory can be accessed as a target from both buses at the same time for inter-process communication. From either the local or PCI bus the CY7C09449PV can be directed to become a PCI bus master to move data into or out of the internal shared memory as a direct memory access (DMA). The CY7C09449PV can DMA across the PCI bus any number of 32-bit double words (DWORD), up to 16K bytes. It uses the full bursting capabilities of the PCI bus for maximum efficiency and can transfer data over the full 32-bit PCI address space.

The CY7C09449PV implements optional requirements of the PCI specification by selecting the optimum PCI command for each transaction it masters to the PCI bus. This maximizes overall efficiency of the system platform. PCI bridging functions (PCI-to-PCI and Host-to-PCI bridges) use the commands to enhance prefetch and cache coherency operations. The CY7C09449PV requests and gains access to the PCI bus as any master. It does not, within itself, include a PCI bus arbitration function. Standard PC PCI buses include this function; embedded systems may need to implement this function.

The CY7C09449PV provides a direct access mechanism from the local bus to the PCI bus. With it, the local processor can direct the CY7C09449PV to run a PCI bus master cycle of any kind to any address. This means that the CY7C09449PV can run PCI configuration cycles allowing it to be used as a host bridge.

#### **Table of Contents**

| Features                                            | 1  |

|-----------------------------------------------------|----|

| Introduction                                        | 1  |

| Functional Overview                                 | 1  |

| Pin Configuration                                   | 4  |

| Pin Description                                     | 5  |

| PCI Bus                                             | 9  |

| Local Bus                                           | 12 |

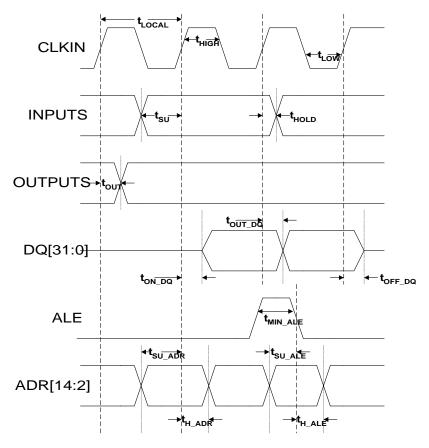

| Timing Diagrams                                     | 16 |

| I <sup>2</sup> C Serial Port and Auto-Configuration | 27 |

| Operations Registers                                | 29 |

| Performance Characteristics                         | 41 |

| CY7C09449PV Operations                              | 46 |

| Ordering Information                                | 48 |

| Package Diagram                                     | 48 |

AN3042\_BD.vs

Four First-In First-Out (FIFO) storage elements provide another resource to the user. These are accessible from either the PCI bus or the Local bus. When the  $\rm I_2O$  messaging unit functionality of the CY7C09449PV is to be used, the four FIFOs become part of the  $\rm I_2O$  messaging unit of the CY7C09449PV. The  $\rm I_2O$  messaging unit consists of the four FIFOs and the  $\rm I_2O$  system interrupt registers. The shared memory of the CY7C09449PV may be used to store  $\rm I_2O$  message frame buffers while most of shared memory is still available for generals purpose use. Efficient  $\rm I_2O$  messaging is realized when the local processor uses the CY7C09449PV direct access mechanism. It can be used to retrieve and post  $\rm I_2O$  message pointers to other  $\rm I_2O$  agents. Data transfer of the messages themselves is made very efficient using the CY7C09449PV PCI DMA controller to burst the message frames to other  $\rm I_2O$  agents.

Interprocess communication is supported by two resources of the CY7C09449PV: the mailbox registers and the arbitration flags. By writing to the mailbox registers, a method is available for the local processor to pass data while causing an interrupt to the host, and vice versa. This is enabled by the interrupt mask located in the CY7C09449PV Operations Registers. The arbitration flags are four pairs of bits that can be used to manage resource allocation and sharing between software and system processes.

The CY7C09449PV includes an interrupt controller. There are separate interrupt mask and command/status registers for the

PCI bus and the Local bus. The interrupt sources are DMA completion, mailbox, FIFO not empty (also for  $\rm I_2O$ ), FIFO overflow, PCI master abort, PCI target abort, and there is an external interrupt input pin. This interrupt controller is used to signal interrupts onto the PCI bus and the Local bus. The CY7C09449PV interrupt controller does not perform the interrupt controller function for the PCI bus system. Standard PC PCI systems include this function; embedded systems may need to implement this function.

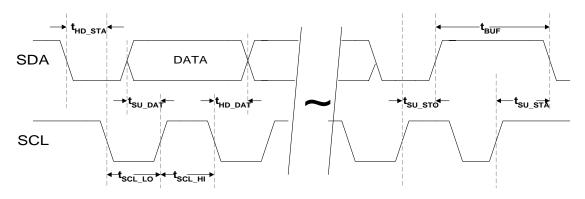

An I<sup>2</sup>C-compatible serial interface is provided to allow the use of a serial EEPROM for non-volatile storage of CY7C09449PV initialization parameters. The parameters are PCI configuration and local bus settings. The CY7C09449PV will optionally access the EEPROM after reset and download initialization information before responding to PCI or local bus transactions. A wide variety of available I<sup>2</sup>C-compatible serial components are available to the local and host processor when connected through this interface.

The CY7C09449PV local bus is a flexible, configurable interface that is designed to readily connect to many industry standard microprocessors. In most cases, no external interface logic ("glue") is needed.

The following block diagram illustrates a generic application for the CY7C09449PV.

3042APP.VSD DB 6/02

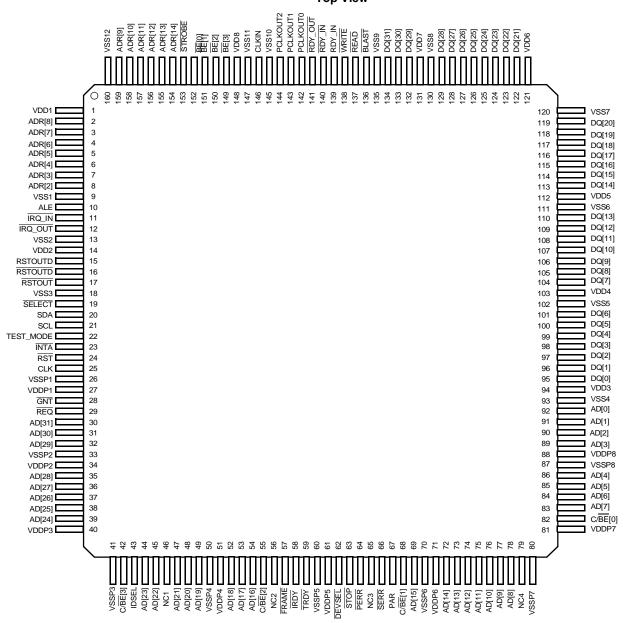

# **Pin Configuration**

#### 160-Lead TQFP (A160) for CY7C09449PV Top View

# **Pin Description**

The Pin Type for CY7C09449PV is defined as follows:

| in    | Input is a standard input-only signal.                                                                                                                                                                                                                                             |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| out   | Standard output driver.                                                                                                                                                                                                                                                            |

| t/s   | Three-state is an output or bidirectional signal.                                                                                                                                                                                                                                  |

| s/t/s | Sustained Three-State is an active LOW, three-state capable signal driven by only one bus agent at a time. When ownership is passed to another agent, the signal is driven HIGH for one clock, and then three-stated for an additional clock before being driven by the new owner. |

| o/d   | Open Drain signals allow multiple devices to share the pin as a wired-OR.                                                                                                                                                                                                          |

| o/c   | Open Collector signals allow multiple devices to share the pin as a wired-OR.                                                                                                                                                                                                      |

# **PCI Bus Signals**

| Signal Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CLK         | in    | Clock: This is the PCI Bus clock and is the timing reference for all PCI bus transactions. The CY7C09449PV can operate with a 33-MHz PCI bus interface.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| RST         | in    | <b>RESET:</b> This signal is the PCI bus reset. It is one of the few PCI signals which may be asserted or deasserted asynchronously to the PCI bus clock (CLK).                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| AD[31:0]    | t/s   | Address and Data: These signals represent the PCI bus address and data signals multiplexed on the same PCI pins. Information on these pins is identified as an address during the clock cycle in which the signal FRAME is first asserted. This is termed the "address phase" of a bus transaction. Information on these pins represents valid read or write data when both IRDY and TRDY are asserted, based on the current cycle type as defined on the C/BE lines during the address phase. This condition is termed the "data phase" of a bus transaction. |  |  |  |  |

| C/BE[3:0]   | t/s   | <b>Command and Byte Enables:</b> These pins are used with the AD[31:0] pins. During the address phase of a bus operation, they identify the bus command to be performed. During the data phase of a bus operation they identify which bytes are involved.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| PAR         | t/s   | <b>Parity:</b> This PCI bus pin represents the even parity across the A/D[31:00] and C/BE[3:0] pins (36 pins) and is generated with a one clock delay.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| FRAME       | s/t/s | Cycle Frame: This PCI bus pin is asserted by the current bus master to signify the beginning of a bus transaction. Data transfers may continue in burst mode while FRAME remains asserted. When FRAME is deasserted it indicates that the transaction is in the final data phase.                                                                                                                                                                                                                                                                              |  |  |  |  |

| IRDY        | s/t/s | <b>Initiator Ready:</b> This signal is driven by the current bus master (initiator) and asserted to indicate its ability to complete the current data phase. Data is transferred when both IRDY and TRDY are asserted, otherwise wait cycles will occur.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| TRDY        | s/t/s | <b>Target Ready:</b> This signal is driven by the selected bus target and asserted when that target is ready to complete the current data phase. Data is transferred when both IRDY and TRDY are asserted, otherwise wait cycles will occur.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| STOP        | s/t/s | <b>Stop:</b> The STOP signal is driven by the selected bus target and is asserted when it wishes to ceal the current data transaction.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| IDSEL       | in    | Initialization Device Select: This signal is used to gain access to the PCI configuration register space of a given PCI Bus agent.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| DEVSEL      | s/t/s | <b>Device Select:</b> The DEVSEL signal is driven and asserted by the currently selected PCI bus target based on the current address and that target's assigned address range. Bus masters examine this signal to determine whether the desired device is present.                                                                                                                                                                                                                                                                                             |  |  |  |  |

# PCI Bus Signals (continued)

| Signal Name | Туре  | Description                                                                                                                                                                                          |  |  |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REQ         | t/s   | <b>Request:</b> This signal indicates to the bus arbiter that this device wishes to use the bus. It is a point-to-point signal that is driven whenever RST is not asserted.                          |  |  |

| GNT         | t/s   | <b>Grant:</b> This point-to-point signal indicates that the bus has been granted to the requester. It is driver thenever RST is not asserted and is ignored during the assertion of RST.             |  |  |

| PERR        | s/t/s | <b>Parity Error:</b> This signal indicates that a parity error has occurred. It is driven by the target or mast that is the receiver of data at the clock after the PAR signal becomes valid.        |  |  |

| SERR        | o/d   | System Error: This open drain signal is driven by any device that detects odd parity during an address phase.                                                                                        |  |  |

| ĪNTA        | o/d   | Interrupt A: This signal is asserted when interrupt servicing of the CY7C09449PV device is required. The INTA pin is a shared PCI bus signal and utilizes an open-drain element to allow a wired-OR. |  |  |

# **Local Bus Interface Signals**

| Signal Name      | Type             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADR[14:2]        | in               | <b>Address:</b> These signals identify the local memory location. When the local processor outputs multiplexed address and data, those lines need to be tied to both the DQ[14:2] and ADR[14:2].                                                                                                                                                                                                                                                          |  |  |  |

| BE[3:0]          | in               | <b>Byte Enables:</b> The Byte Enable inputs identify the specific bytes involved in an access. The pins may be configured as byte lane enables, directly, or used as size and encoded byte lane enables when interfacing to certain Motorola processors; see the Local Bus section for definition.                                                                                                                                                        |  |  |  |

| DQ[31:0]         | t/s              | <b>Data:</b> CY7C09449PV data input and output are provided on these bidirectional pins. This bus remains in high impedance during power-up and active Reset (RST) and only drives during read transactions.                                                                                                                                                                                                                                              |  |  |  |

| SELECT           | in               | <b>Chip Select:</b> This signal must be asserted for the full duration of any access. The polarity is programmable; the default is active LOW.                                                                                                                                                                                                                                                                                                            |  |  |  |

| ALE              | in               | Address Latch Enable: The local address provided on ADR[14:2] is latched on the trailing edge (from active to inactive) of this signal. The polarity is programmable; the default is active HIGH.                                                                                                                                                                                                                                                         |  |  |  |

| STROBE           | in               | Address Strobe: The assertion of this signal begins a memory access and indicates that a valid address has been latched through ALE or is provided at the pins (if ALE is not used and is tied active). The address is provided on the ADR[14:2] pins (during non-multiplexed mode), or on the DQ[14:2] (during multiplexed mode). Outside the address phase, the level of STROBE is don't care. The polarity is programmable; the default is active LOW. |  |  |  |

| WRITE<br>READ    | in               | Write and Read Signals: These signals control the transfer of data to and from the local data b WRITE and READ are sampled in the address phase and are don't cares during the remainder the bus transaction. The polarity and function of these signals is programmable so that they can interfaced to processors that support WR/RD or RD/WR, as well as separate RD/RD and WR/V signals.                                                               |  |  |  |

| BLAST            | in               | <b>Burst Last:</b> The signal indicates the end of a burst transfer. This signal has two modes. It can be active during the burst and go inactive when the burst is over, or it can go active during the last data phase of the burst. The polarity is programmable; the default is active LOW.                                                                                                                                                           |  |  |  |

| RDY_IN<br>RDY_IN | in               | <b>Ready In:</b> The assertion of these signals indicates that the local processor is prepared to complete the current data transaction.                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RDY_OUT          | out<br>or<br>t/s | <b>Ready Out:</b> When this signal is asserted it indicates that the CY7C09449PV is ready to complete the current access. The polarity is programmable; the default is active LOW. This signal is also programmable to three-state when inactive; the default is to three-state when inactive.                                                                                                                                                            |  |  |  |

#### **Local System Signals**

| Signal Name                      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

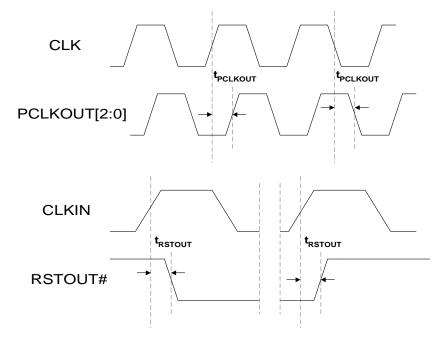

| PCLKOUT2<br>PCLKOUT1<br>PCLKOUT0 | out  | Clock Outputs: These pins provide three buffered copies of the PCI bus clock.                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CLKIN                            | in   | Clock In: This pin provides the timing reference for local bus signals. The CLKIN pin can be driven by an external clock. Also, one of the buffered copies of the PCI clock, PCLKOUT[2:0], may be used its input to CLKIN. This clock must be toggling for proper start-up operation of the CY7C09449PV is well as for PCI access to resources other than the dual-ported shared memory.                   |  |  |  |

| RSTOUT                           | out  | Reset Out: This pin provides a buffered version of the PCI bus signal, RST.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| RSTOUTD<br>RSTOUTD               | out  | Reset Out Delayed: These pins are similar to the RSTOUT pin described above, however RSTOUTD and RSTOUTD remain asserted until released by the host interface via software control. This allows the CY7C09449PV to hold the local processor in reset until the host processor is ready to release it.                                                                                                      |  |  |  |

| ĪRQ_OUT                          | t/s  | Interrupt Request Out: This signal may be used to trigger an interrupt on the local microprocessor. A variety of host-triggered events can be used to cause the assertion of this interrupt request output. This signal may be masked using the Local Interrupt Control/Status Register. When in the inactive state, this signal is three-stated. The polarity is programmable; the default is active LOW. |  |  |  |

| ĪRQ_IN                           | in   | Interrupt Request In: This signal, when asserted, will result in the CY7C09449PV driving the PCI bus INTA signal and therefore cause an interrupt of the host system. This signal may be masked using the Host Interrupt Control/Status Register.                                                                                                                                                          |  |  |  |

| TEST_MODE                        | in   | <u>Test Mode:</u> When HIGH, this pin puts the CY7C09449PV into a factory test mode. When HIGH and READ is LOW, all outputs are set to high impedance except RDY_OUT will continue to drive if Operations Register LBUSCFG bit 16 is '0'. This is the only test mode available to the user. The user must drive this signal LOW if unused.                                                                 |  |  |  |

#### **Local Configuration Signals**

| Signal Name | Туре | Description                                                                                                                                                              |  |  |  |  |

|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SCL         | o/c  | <b>Serial Clock:</b> This pin is the clock output to be used with an external I <sup>2</sup> C-compatible serial memory device. A pull-up resistor is required.          |  |  |  |  |

| SDA         | o/c  | <b>Serial Data:</b> This pin is the bidirectional data pin to be used with an external I <sup>2</sup> C-compatible serial memory device. A pull-up resistor is required. |  |  |  |  |

#### **Power Pins**

| Signal Name                | Туре  | Description                                           |

|----------------------------|-------|-------------------------------------------------------|

| VSSP1-VSSP8,<br>VSS1-VSS12 | GND   | Ground: These pins are ground pins (0 volts).         |

| VDDP1–VDDP8,<br>VDD1–VDD8  | POWER | Power: These pins provide power, nominally 3.3 volts. |

#### **Other Pins**

| Signal Name | Туре | Description                                                   |

|-------------|------|---------------------------------------------------------------|

| NC1-NC4     | NC   | No Connect: These pins are not to be used; leave unconnected. |

#### **Signal Terminations**

PCI Bus signals should be terminated according to the PCI 2.2 specification. Generally, termination is provided by the PCI system. If the CY7C09449PC is used as a PCI add-in card or other device as part of a PCI bus, no termination should be used. For embedded systems, then terminations are part of the system design; they are not particular to the CY7C09449PV. Any PCI system must include a single pull-up on each PCI bus control signal used. These signals are FRAME, TRDY, IRDY, DEVSEL, STOP, SERR, PERR, LOCK, INTA, INTB, INTC, INTD, REQ64, and ACK64. Refer to Sec-

tion 4.3, System (Motherboard) Specification, of the PCI 2.2 specification for detailed requirements.

All Local System and Local Bus Interface input signals must be driven at all times. If they are unused inputs, then they may be driven either HIGH or LOW (pull-up or pull-down,  $V_{DD}$  or Ground).

SCL and SDA must have a pull-up in the range of 2.2 k $\Omega$  to 10 k $\Omega$  to V<sub>DD</sub>. These pull-ups are required whether the signals are to be used or not.

# **Pin List**

| Pin Name  | No. | Pin Name | No. | Pin Name | No. | Pin Name | No. |

|-----------|-----|----------|-----|----------|-----|----------|-----|

| VDD1      | 1   | VSSP3    | 41  | VDDP7    | 81  | VDD6     | 121 |

| ADR[8]    | 2   | C/BE[3]  | 42  | C/BE[0]  | 82  | DQ[21]   | 122 |

| ADR[7]    | 3   | IDSEL    | 43  | AD[7]    | 83  | DQ[22]   | 123 |

| ADR[6]    | 4   | AD[23]   | 44  | AD[6]    | 84  | DQ[23]   | 124 |

| ADR[5]    | 5   | AD[22]   | 45  | AD[5]    | 85  | DQ[24]   | 125 |

| ADR[4]    | 6   | NC1      | 46  | AD[4]    | 86  | DQ[25]   | 126 |

| ADR[3]    | 7   | AD[21]   | 47  | VSSP8    | 87  | DQ[26]   | 127 |

| ADR[2]    | 8   | AD[20]   | 48  | VDDP8    | 88  | DQ[27]   | 128 |

| VSS1      | 9   | AD[19]   | 49  | AD[3]    | 89  | DQ[28]   | 129 |

| ALE       | 10  | VSSP4    | 50  | AD[2]    | 90  | VSS8     | 130 |

| ĪRQ_IN    | 11  | VDDP4    | 51  | AD[1]    | 91  | VDD7     | 131 |

| ĪRQ_OUT   | 12  | AD[18]   | 52  | AD[0]    | 92  | DQ[29]   | 132 |

| VSS2      | 13  | AD[17]   | 53  | VSS4     | 93  | DQ[30]   | 133 |

| VDD2      | 14  | AD[16]   | 54  | VDD3     | 94  | DQ[31]   | 134 |

| RSTOUTD   | 15  | C/BE[2]  | 55  | DQ[0]    | 95  | VSS9     | 135 |

| RSTOUTD   | 16  | NC2      | 56  | DQ[1]    | 96  | BLAST    | 136 |

| RSTOUT    | 17  | FRAME    | 57  | DQ[2]    | 97  | READ     | 137 |

| VSS3      | 18  | IRDY     | 58  | DQ[3]    | 98  | WRITE    | 138 |

| SELECT    | 19  | TRDY     | 59  | DQ[4]    | 99  | RDY_IN   | 139 |

| SDA       | 20  | VSSP5    | 60  | DQ[5]    | 100 | RDY_IN   | 140 |

| SCL       | 21  | VDDP5    | 61  | DQ[6]    | 101 | RDY_OUT  | 141 |

| TEST_MODE | 22  | DEVSEL   | 62  | VSS5     | 102 | PCLKOUT0 | 142 |

| ĪNTA      | 23  | STOP     | 63  | VDD4     | 103 | PCLKOUT1 | 143 |

| RST       | 24  | PERR     | 64  | DQ[7]    | 104 | PCLKOUT2 | 144 |

| CLK       | 25  | NC3      | 65  | DQ[8]    | 105 | VSS10    | 145 |

| VSSP1     | 26  | SERR     | 66  | DQ[9]    | 106 | CLKIN    | 146 |

| VDDP1     | 27  | PAR      | 67  | DQ[10]   | 107 | VSS11    | 147 |

| GNT       | 28  | C/BE[1]  | 68  | DQ[11]   | 108 | VDD8     | 148 |

| REQ       | 29  | AD[15]   | 69  | DQ[12]   | 109 | BE[3]    | 149 |

| AD[31]    | 30  | VSSP6    | 70  | DQ[13]   | 110 | BE[2]    | 150 |

| AD[30]    | 31  | VDDP6    | 71  | VSS6     | 111 | BE[1]    | 151 |

| AD[29]    | 32  | AD[14]   | 72  | VDD5     | 112 | BE[0]    | 152 |

| VSSP2     | 33  | AD[13]   | 73  | DQ[14]   | 113 | STROBE   | 153 |

| VDDP2     | 34  | AD[12]   | 74  | DQ[15]   | 114 | ADR[14]  | 154 |

| AD[28]    | 35  | AD[11]   | 75  | DQ[16]   | 115 | ADR[13]  | 155 |

| AD[27]    | 36  | AD[10]   | 76  | DQ[17]   | 116 | ADR[12]  | 156 |

| AD[26]    | 37  | AD[9]    | 77  | DQ[18]   | 117 | ADR[11]  | 157 |

| AD[25]    | 38  | AD[8]    | 78  | DQ[19]   | 118 | ADR[10]  | 158 |

| AD[24]    | 39  | NC4      | 79  | DQ[20]   | 119 | ADR[9]   | 159 |

| VDDP3     | 40  | VSSP7    | 80  | VSS7     | 120 | VSS12    | 160 |

### **Memory Map**

CY7C09449PV resources are accessed from the PCI bus as an offset from Base Address Register 0 (BAR 0), unless otherwise indicated. Resources are also accessed from the Local bus when the SELECT pin is active. PCI I/O access to this memory map is also available via PCI I/O pointers located at Base Address Register 1 (BAR 1). The memory map covers a continuous 32KB address space.

#### **PCI Bus**

The PCI bus of the CY7C09449PV operates per the PCI Specification revision 2.2. This section describes the specific PCI functions supported by the CY7C09449PV. Reference URL: http://www.pcisig.com/

| Memory Contents                                                                                                     | Address [14:0],<br>Byte Offset | Size  |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------|-------|

| I <sub>2</sub> O Specific Registers                                                                                 | 0x0000 - 0x03FF                | 1 KB  |

| Operations Registers                                                                                                | 0x0400 - 0x07FF                | 1 KB  |

| reserved                                                                                                            | 0x0800 - 0x1FFF                | 6 KB  |

| Direct Access to PCI Bus<br>(this is a window into PCI<br>space; this window is only<br>available to the Local bus) | 0x2000 - 0x3FFF                | 8 KB  |

| Shared Memory                                                                                                       | 0x4000 - 0x7FFF                | 16 KB |

# **PCI Configuration Space**

|                            |                        | PCI Configuration Sp | ace                 |                         |

|----------------------------|------------------------|----------------------|---------------------|-------------------------|

| 31                         | 16                     | 15                   | 0                   | Address,<br>Byte Offset |

| Device ID, RO              | <u> </u>               | Vendor ID, RO        |                     | 0x00                    |

| Status, CS                 |                        | Command, CS          |                     | 0x04                    |

| Class Code,<br>RO          |                        |                      | Revision ID, RO     | 0x08                    |

| BIST (not used) 24<br>0x00 | ⊞ader Type<br>0x00     | Latency Timer, 8 RW  | Cache Line Size, RW | 0x0C                    |

| Base Address Register      | r #0 32KBytes Memory   | Space, <i>RW</i>     |                     | 0x10                    |

| Base Address Register      | r #1 8 Bytes I/O Space | , RW                 |                     | 0x14                    |

| Base Address Register      | 0x18                   |                      |                     |                         |

| Base Address Register      | r #3 (not used) 0x0000 |                      |                     | 0x1C                    |

| Base Address Register      | r #4 (not used) 0x0000 |                      |                     | 0x20                    |

| Base Address Register      | 0x24                   |                      |                     |                         |

| Cardbus CIS Pointer, F     | 70                     |                      |                     | 0x28                    |

| Subsystem Device ID,       | 0x2C                   |                      |                     |                         |

| Expansion ROM Base         | 0x30                   |                      |                     |                         |

| Reserved 0x0000            | 0x34                   |                      |                     |                         |

| Reserved 0x0000            |                        |                      |                     | 0x38                    |

| MAX_LAT,<br>RO             | 0x3C                   |                      |                     |                         |

| Legend for PCI Configuration Space Table |                                                                                             |  |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| 0x00 or 0x0000                           | Hardwired to zero                                                                           |  |  |  |  |

| RO                                       | Read-only: may be initialized by EEPROM across I <sup>2</sup> C-compatible serial interface |  |  |  |  |

| CS                                       | Control and status register                                                                 |  |  |  |  |

| RW                                       | Read/write                                                                                  |  |  |  |  |

#### **Vendor ID**

Address: 0x01 - 0x00 Default Value: 0x12BE

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface

This 2-byte register contains the Vendor ID assigned by the PCI SIG. The default value is the Cypress Semiconductor Vendor ID. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own vendor ID.

#### **Device ID**

Address: 0x03 - 0x02 Default Value: 0x3042

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface

This 2-byte register contains the device ID assigned by the manufacturer. The default value is the CY7C09449PV chip device ID. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own device ID.

#### Command

Address: 0x05 - 0x04 Default Value: 0x0000

Read/Write

This 2-byte register contains bits for device control. These bits are normally set by the system BIOS. The following bits are supported:

Bit 0: Enable response to I/O space accesses.

Bit 1: Enable response to Memory space accesses.

Bit 2: Enable PCI bus master operation (may be initialized over the  $I^2$ C-compatible serial interface).

Bit 3: Enable special cycle monitoring, (but CY7C09449PV performs no special function as a target).

Bit 4: Enable bus master use of the Memory Write and Invalidate command.

Bit 6: Enable the PERR signal for host notification of data parity errors.

Bit 8: Enable the SERR signal for host notification of system errors.

Bit 9: Enable fast back-to-back transactions to different agents (but CY7C09449PV does not generate).

#### **Status**

Address: 0x07 - 0x06 Default Value: 0x0280

Read-only and Write-1-to-Clear except as indicated.

This 2-byte register contains bits for device status. The following bits are supported:

Bit 7: Read-only bit set to indicate, as a target, the chip can accept fast back-to-back transactions.

Bit 8: Set when PERR is asserted.

Bits 10 and 9: Read-only bits set to 0x1 indicating medium response timing for DEVSEL.

Bit 12: Set when, as a master, the chip's transaction has been terminated with Target-Abort.

Bit 13: Set when, as a master, the chip terminates a transaction with Master-Abort.

Bit 14: Set when SERR is asserted.

Bit 15: Set whenever a parity error is detected.

#### **Revision ID**

Address: 0x08

Default Value: 0x02

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This 1-byte register contains the Revision ID assigned by the manufacturer. The default value is set by Cypress Semiconductor at manufacturing time. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own Revision ID.

#### **Class Code**

Address: 0x0B - 0x09 Default Value: 0x0E0001

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This 3-byte register contains the class code assigned by the manufacturer. The default value indicates an  $I_2O$  base class (0x0E), a sub-class of 0x00, and the programming interface that supports system interrupt capability (0x01). Using the  $I^2C$ -compatible serial interface for initialization provides a method to allow a manufacturer to load their own class code.

#### **Cache Line Size**

Address: 0x0C Default Value: 0x00

Read/Write

This register contains the cache line size in DWORDs. The only valid size is 0x08; any other value written will result in a 0x00 being written to the register. The value in this register is used to control when the master can perform Memory Write and Invalidate cycles. Additionally, the type of memory read command is determined by this value; (i.e., Memory Read, Memory Read Line, or Memory Read Multiple).

#### **Latency Timer**

Address: 0x0D

Default Value: 0x00

Read/Write

This register controls how quickly the master must get off the bus if GNT is removed. The CY7C09449PV implements bits [7:3] of this register, providing a granularity of eight clocks.

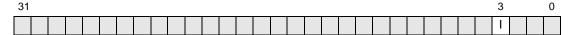

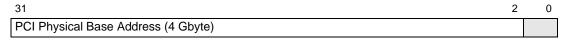

# Base Address Register 0 (Memory Type Access)

Address: 0x13 - 0x10

Default Value: 0x00000000

Read all 32 bits, Write bits [31–15]

This register provides the base address of the CY7C09449PV memory map. Bits [31–15] are read/write, indicating to the system BIOS that the shared memory space is 32 K bytes. If a PCI memory transaction has address bits [31–15] matching the contents of this register and memory accesses are enabled (by Command register bit 1), then the CY7C09449PV chip will acknowledge and accept the transfer.

#### Base Address Register 1 (I/O Type Access)

Address: 0x17 - 0x14

Default Value: 0x00000001

Read all 32 bits, Write bits [31–3]

This register provides the base address of the CY7C09449PV I/O pointer space. Bits [31–3] are read/write, indicating to the system BIOS that the I/O pointer space is 8 bytes. If a PCI I/O transaction has address bits [31–3] matching the contents of this and I/O accesses are enabled (by Command register bit

0), then the CY7C09449PV will acknowledge and accept the

transfer.

#### **Cardbus CIS Pointer**

Address - 0x2B - 0x28 Default Value: 0x00000000

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This register contains the Cardbus Card Information Structure (CIS). Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own CIS pointer value.

#### **Subsystem Vendor ID**

Address: 0x2D - 0x2C Default Value: 0x0000

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This 2-byte register contains the subsystem vendor ID chosen by the manufacturer. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own subsystem vendor ID.

#### **Subsystem Device ID**

Address: 0x2F - 0x2E Default Value: 0x0000

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This 2-byte register contains the subsystem device ID chosen by the manufacturer. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own subsystem device ID.

#### Interrupt Line

Address: 0x3C

Default Value: 0x00

Read/Write

This single-byte register contains the interrupt line routing.

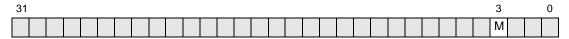

#### Interrupt Pin

Address: 0x3D Default Value: 0x00

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This single-byte register contains the interrupt pin information. The default value indicates that the CY7C09449PV chip is not connected to the interrupts on the PCI bus. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to specify which interrupt pin is on the bus. Only bits [2–0] <u>are implemented</u>. All four Interrupt numbers are supported, (INTA through INTD).

#### MIN GNT

Address: 0x3E

Default Value: 0x00

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This single-byte register contains the minimum grant time in 1/4 microsecond increments needed for efficient operation. The default value indicates the add-in card has no major requirements for the setting of the latency timer. The latency timer governs how long a burst transaction may use the PCI bus. Whatever the value, the CY7C09449PV itself does not use the MIN\_GNT data. It is used as a means to communicate system requirements to the host. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own minimum grant time reflective of their add-in card requirements.

#### MAX LAT

Address: 0x3F Default Value: 0x00

Read-only: Can be initialized from the external memory accessed via the I<sup>2</sup>C-compatible serial interface.

This single-byte register contains the minimum latency time in 1/4 microsecond increments needed for efficient operation. The default value indicates the add-in card has no major requirements for how soon it needs access to the PCI bus once it has requested an access. Whatever the value, the CY7C09449PV itself does not use MAX\_LAT data. It is used as a means to communicate system requirements to the host. Using the I<sup>2</sup>C-compatible serial interface for initialization provides a method to allow a manufacturer to load their own minimum latency time reflective of their add-in card requirements.

#### **PCI Bus Commands**

All Memory and I/O commands are supported as target and master.

| I/O Read                                 | $C/\overline{BE}[3:0] = 0x2$ |

|------------------------------------------|------------------------------|

|                                          |                              |

| • I/O Write                              | $C/\overline{BE}[3:0] = 0x3$ |

| <ul> <li>Memory Read</li> </ul>          | $C/\overline{BE}[3:0] = 0x6$ |

| <ul> <li>Memory Write</li> </ul>         | $C/\overline{BE}[3:0] = 0x7$ |

| <ul> <li>Memory Read Multiple</li> </ul> | $C/\overline{BE}[3:0] = 0xC$ |

| <ul> <li>Memory Read Line</li> </ul>     | $C/\overline{BE}[3:0] = 0xE$ |

| · Memory Write and Invalidate            | $C/\overline{BE}[3:0] = 0xF$ |

All Configuration commands are supported as target and master. Additionally, the CY7C09449PV can perform these ac-

cesses on its own PCI Configuration space. Control originates from the Local bus using the CY7C09449PV Direct Access feature. This is a necessary feature for the CY7C09449PV to perform as a Host Bridge device. Type 0 and Type 1 PCI configuration commands may be generated by the CY7C09449PV. For details, see the Direct Access and Host Bridge descriptions in the CY7C09449PV Operations section.

Configuration Read C/BE[3:0] = 0xA

Configuration Write C/BE[3:0] = 0xB

Interrupt Acknowledge and Special Cycle are supported on master cycles. As a target, no action is performed by the CY7C09449PV.

Interrupt AcknowledgeC/BE[3:0] = 0x0

Special Cycle C/BE[3:0] = 0x1

The following command is not supported, a target access will result in no response by the CY7C09449PV as per the PCI specification.

• Dual-Address Cycle C/BE[3:0] = 0xD

The following commands are PCI Reserved and are not responded to as per PCI specification.

Reserved

Reserved

Reserved

Reserved

C/BE[3:0] = 0x5

C/BE[3:0] = 0x8

Reserved

C/BE[3:0] = 0x9

#### **PCI I/O Pointers**

Utilization of PCI I/O access is not generally recommended by the PCI special interest group. New system designs should use the PCI Memory access rather than PCI I/O access. In general, this is provided as a support to legacy systems. The CY7C09449PV Base Address Register 1 (BAR1) is the offset reference for PCI I/O access to this device.

I/O Address Pointer Address: 0x1 - 0x0

Default Value: unknown, not initialized

Write-only

The value written to this location is the offset into the CY7C09449PV Memory Map. Bit 15 is "don't care."

I/O Data Pointer

Address: 0x7 - 0x4

Default Value: unknown, not initialized

Read/Write

Upon a write to the pointer, the data shall be written to the location in the CY7C09449PV Memory Map specified by the contents of the I/O address pointer. If an I/O read access to the pointer, then the data at the location in the CY7C09449PV Memory Map which is specified by the contents of the I/O address pointer shall be returned.

#### **Local Bus**

#### **General Description**

The CY7C09449PV provides a configurable local processor bus interface which can provide direct connection to several processor types. The interface is synchronous to the CLKIN signal. The CLKIN signal can be tied to the local processor's

clock, a derivative, or an independent clock source. To run the local interface at PCI clock speeds, any one of the PCLKOUT[2:0] pins should be connected to CLKIN.

The basic local processor bus transaction consists of an address phase, followed by one or more data phases. The interface signals are generally divided into those signals that qualify the address phase (ALE, STROBE, SELECT, READ, WRITE, and ADR[14:2]), and those that qualify data phases, (RDY\_IN, RDY\_IN, BLAST, BE[3:0], and DQ[31:0]). The CY7C09449PV drives RDY\_OUT to signal the need for wait states on the local processor bus as well as an indication of valid data on DQ[31:0] during read access of the CY7C09449PV. Note that several of the CY7C09449PV local bus signals have configurable polarity. These are: ALE, BLAST, RDY\_OUT, and STROBE. Also, the READ and WRITE signals have special combined signal modes.

The basic local-bus cycle starts with the address phase. The address phase is defined as both STROBE and SELECT active at the rising edge of CLKIN. Also sampled at this time are the READ and WRITE signals to determine if the access is a read or write. If the access is a read, then the CY7C09449PV will begin driving the DQ bus at the next CLKIN rising edge.

There are two ways to get an address into the CY7C09449PV. With ALE tied active, the address is latched during the address phase. That is, when STROBE and SELECT are active, the address on the ADR[14:2] pins is latched on the rising edge of CLKIN. The second way is to use the trailing edge of ALE to latch the address. The CY7C09449PV still needs a valid address phase (STROBE and SELECT active at the rising edge of CLKIN) before it will begin processing the address. A valid and stable address must occur before the trailing edge of ALE and before the rising edge of CLKIN where STROBE and SELECT are active.

After the address phase come wait states and data phases. The STROBE signal can be active or inactive during wait and data phases. A data phase occurs when the RDY\_IN and RDY\_IN inputs and the RDY\_OUT output are all active at the rising edge of CLKIN. If any ready signal is inactive, then the next clock cycle is a wait state. The BE[3:0] pins are sampled during the data phase of write cycles to determine which data bytes are to be written. The data on the DQ pins is also latched at this time.

The BLAST signal is sampled during the data phase to determine if the last data phase is occurring. In one mode, an inactive level during the data phase indicates that there are more data phases in the transaction and that the address that was captured in the address phase should be updated. When BLAST is active during the data phase, it indicates that this is the last data phase of the transaction. In the other mode, BLAST is active during every data phase and goes inactive at the end of the last data phase. In both cases, if the access is a read, then the CY7C09449PV will stop driving the DQ bus synchronously with the rising edge of CLKIN for that data phase.

#### **Interface Definitions**

#### 8-Bit Interface

The 8-bit interface option is selected by setting bits BW[1:0] = '00' in the Local Bus Configuration Register. Only data lines DQ[7:0] are used. The unused portion of the data bus, DQ[31:8] must be tied HIGH or LOW; the bits cannot be left

floating. The least two significant bits of the local address bus should be connected to the byte enable pins  $\overline{\text{BE}}[3:2]$ .  $\overline{\text{BE}}[0]$  should be tied to  $\overline{\text{RDY\_IN}}$  which is connected normally.

#### Connect

- BE[3] = A1

- BE[2] = A0

- BE[1] = Logic HIGH

- $\overline{BE}[0] = \text{Tie to } \overline{RDY}_{IN}$

| BW[1:0] | BEMODE | A1, A0<br>(BE[3],<br>BE[2]) | DQ [7:0]<br>Accessed Data |

|---------|--------|-----------------------------|---------------------------|

| 00      | Χ      | 00                          | Data[7:0]                 |

| 00      | Х      | 01                          | Data[15:8]                |

| 00      | Х      | 10                          | Data[23:16]               |

| 00      | Х      | 11                          | Data[31:24]               |

#### 16-Bit Interface

The 16-bit interface option is selected by setting bits BW[1:0] = '01' in the Local Bus Configuration Register. Only data lines DQ[15:0] are used. The unused portion of the data bus, DQ[31:16] must be tied HIGH or LOW; the bits cannot be left floating. There are two basic modes for 16-bit operation. One is for Motorola-style encoded byte enables and the other is for direct byte enables. This is configured with the Byte Enable mode bit, BEMODE. There is an exception to the data bus wiring for Motorola-style buses if a 32-bit processor bus is configured to only use 16 data bits. The upper 16 bits of the processor bus are connected rather than the lower 16 bits. See the description for BEMODE='1' below.

BEMODE = '0' is for operation of other than Motorola-style byte enables. The table below shows where data on the 16-bit bus is routed within the CY7C09449PV internal data structures.

#### Connect

- BE[3] = A1

- BE[2] = Not used, should be tied HIGH

• BE[1] = BE1, UDS, BHE (Byte Enable 1, Upper Data Strobe, Byte High Enable)

• BE[0] = BE0, LDS, DEN (Byte Enable 0, Lower Data Strobe, Data Enable, A0)

| BW[1:0 | BE-<br>MODE | A1<br>(BE[3<br>]) | DQ [15:0] Bus Accessed<br>Data |

|--------|-------------|-------------------|--------------------------------|

| 01     | 0           | 0                 | CY7C09449PV Data[15:0]         |

| 01     | 0           | 1                 | CY7C09449PV Data[31:16]        |

#### Notes:

BE[1:0] are used as byte enables. If the processor always does 16-bit accesses, then these can be tied active LOW. These byte enables can also be used for Upper Data Strobe (UDS) and Lower Data Strobe (LDS) for processors which produce these signals.

The least significant bit of the local address bus is tied to  $\overline{BE}[3]$ , and it *must be valid during the address phase.* This input must be incremented (toggled) at the end of each data phase. Bursts to the 16-bit interface do not need to start on a DWORD boundary. The internal DWORD address will automatically increment after a data phase where  $\overline{BE}[3]$  is HIGH.

BEMODE = '1' is for operation of Motorola-style byte enables. The tables below show where data on the 16-bit bus is placed in the CY7C09449PV internal data structures. For the case where a 32-bit Motorola processor bus is to be configured for 16-bit bus operation, then connect the processor D[31:16] to CY7C09449PV DQ[15:0]. For instance, the Motorola 68360 processor may be operated in this mode. The tables show this mode of operation.

# Connect for encoded byte enables

BE[3] = SIZ1 (Operand Transfer Size, bit 1)

BE[2] = SIZ0 (Operand Transfer Size, bit 0)

• BE[1] = A1

• BE[0] = A0

| BW[1:0] | BEMODE | Interpretation          |

|---------|--------|-------------------------|

| 01      | 1      | Use the following table |

| CY7C09449PV External | Interpretation 'byte' terminology here uses byte 3 as least signifi-                                                                         | CY7C09449PV Internal |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| BE[3:0]              | cant byte of the processor's internal 32-bit data structure; the signals show pins on the processor.                                         | BE[3:0] for writes   |

| 0000                 | all-byte write starting at byte 0 (D[31:16]) (truncated to two bytes)                                                                        | 0011                 |

| 0001                 | all-byte write starting at byte 1 (D[23:16]) (truncated to one byte)                                                                         | 1011                 |

| 0010                 | all-byte write starting at byte 2 (D[31:16]) (truncated to two bytes)                                                                        | 1100                 |

| 0011                 | all-byte write starting at byte 3 (D[23:16]) (truncated to one byte)                                                                         | 1110                 |

| 0100                 | single-byte write starting at byte 0 (D[31:24])                                                                                              | 0111                 |

| 0101                 | single-byte write starting at byte 1 (D[23:16])                                                                                              | 1011                 |

| 0110                 | single-byte write starting at byte 2 (D[31:24])                                                                                              | 1101                 |

| 0111                 | single-byte write starting at byte 3 (D[23:16])                                                                                              | 1110                 |

| 1000                 | two-byte write starting at byte 0 (D[31:16])                                                                                                 | 0011                 |

| 1001                 | two-byte write starting at byte 1 (D[23:16]) (truncated to one byte)                                                                         | 1011                 |

| 1010                 | two-byte write starting at byte 2 (D[31:16])                                                                                                 | 1100                 |

| 1011                 | two-byte write starting at byte 3 (D[23:16]) (truncated to one byte)                                                                         | 1110                 |

| 1100                 | three-byte write starting at byte 0 (D[31:16]) (truncated to two bytes)                                                                      | 0011                 |

| 1101                 | three-byte write starting at byte 1 (D[23:16]) (truncated to one byte)                                                                       | 1011                 |

| 1110                 | three-byte write starting at byte 2 (D[31:16]) (truncated to two bytes)                                                                      | 1100                 |

| 1111                 | three-byte write starting at byte 3 (D[31:24]) (truncated to one byte) three-byte read starting at byte 3 (D[23:16]) (truncated to one byte) | 1110                 |

#### 32-Bit Interface

The 32-bit interface option is selected by setting bits BW[1:0] = '10' or BW[1:0] = '11' in the Local Bus Configuration Register. Data lines DQ[31:0] are used. With BW[1:0] = '10', the byte enables are used directly as byte write enables. With BW[1:0] = '11', however, the meaning of the byte enables is determined from the following tables (based on BEMODE).

For 32-bit processor bus interfaces like the Motorola 68020 or 68030, BW = '11' and BEMODE = '0' settings are used. This supports a special style of using byte addressing instead of fully decoded byte enables. The SIZ1 and SIZ0 signals of the 68020 are connected to the  $\overline{\text{BE}}$ [3] and  $\overline{\text{BE}}$ [2] pins, respectively,

and the A1 and A0 signals are connected to the  $\overline{BE}[1]$  and  $\overline{BE}[0]$  pins on the CY7C09449PV.

#### Connect for encoded byte enables

BE[3] = SIZ1 (Operand Transfer Size, bit 1)

BE[2] = SIZ0 (Operand Transfer Size, bit 0)

• BE[1] = A1

• BE[0] = A0

| BW[1:0] | BEMODE | Interpretation                        |

|---------|--------|---------------------------------------|

| 10      | Х      | Use byte enables for all 4 byte lanes |

| 11      | 0      | Use the following table               |

| CY7C09449PV External BE[3:0] | Interpretation 'byte' terminology here uses byte 3 as least significant byte of the processor's internal 32-bit data structure; the signals show pins on the processor | CY7C09449PV Internal BE[3:0] for writes |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 0000                         | all-byte write starting at byte 0 (D[31:0])                                                                                                                            | 0000                                    |

| 0001                         | all-byte write starting at byte 1 (D[23:0]) (truncated to three bytes)                                                                                                 | 1000                                    |

| 0010                         | all-byte write starting at byte 2 (D[15:0]) (truncated to two bytes)                                                                                                   | 1100                                    |

| 0011                         | all-byte write starting at byte 3 (D[7:0]) (truncated to one byte)                                                                                                     | 1110                                    |

| 0100                         | single-byte write starting at byte 0 (D[31:24])                                                                                                                        | 0111                                    |

| 0101                         | single-byte write starting at byte 1 (D[23:16])                                                                                                                        | 1011                                    |

| 0110                         | single-byte write starting at byte 2 (D[15:8])                                                                                                                         | 1101                                    |

| 0111                         | single-byte write starting at byte 3 (D[7:0])                                                                                                                          | 1110                                    |

| 1000                         | two-byte write starting at byte 0 (D[31:16])                                                                                                                           | 0011                                    |

| 1001                         | two-byte write starting at byte 1 (D[23:8])                                                                                                                            | 1001                                    |

| 1010                         | two-byte write starting at byte 2 (D[15:0])                                                                                                                            | 1100                                    |

| 1011                         | two-byte write starting at byte 3 (D[7:0]) (truncated to one byte)                                                                                                     | 1110                                    |

| 1100                         | three-byte write starting at byte 0 (D[31:8])                                                                                                                          | 0001                                    |

| 1101                         | three-byte write starting at byte 1 (D[23:0])                                                                                                                          | 1000                                    |

| 1110                         | three-byte write starting at byte 2 (D[15:0]) (truncated to two bytes)                                                                                                 | 1100                                    |

| 1111                         | three-byte write starting at byte 3 (D[7:0]) (truncated to one byte)                                                                                                   | 1110                                    |

For 32-bit processor bus interfaces like the Motorola 68040, BW = '11' and BEMODE = '1' settings are used. This supports a special style of using byte addressing instead of fully decoded byte enables. The SIZ1 and SIZ0 signals of the 68040 are connected to the BE[3] and BE[2] pins, respectively, and the A1 and A0 signals are connected to the BE[1] and BE[0] pins on the CY7C09449PV. A cache-line fill is triggered using the SIZ1 and SIZ0 pins on the 68040-type bus. When these bits

are set to '11', the CY7C09449PV will interpret this as a burst-of-four, ignoring the burst last signal BLAST.

| BW[1:0] | BEMODE | Interpretation          |  |  |  |

|---------|--------|-------------------------|--|--|--|

| 11      | 1      | Use the following table |  |  |  |

| CY7C09449PV External BE[3:0] | Interpretation the signals show pins on the processor | CY7C09449PV Internal BE[3:0] for writes |

|------------------------------|-------------------------------------------------------|-----------------------------------------|

| 00xx                         | 32-bit write D[31:0]                                  | 0000                                    |

| 0100                         | 8-bit write D[31:24]                                  | 0111                                    |

| 0101                         | 8-bit write D[23:16]                                  | 1011                                    |

| 0110                         | 8-bit write D[15:8]                                   | 1101                                    |

| 0111                         | 8-bit write D[7:0]                                    | 1110                                    |

| 100x                         | 16-bit write D[31:16]                                 | 0011                                    |

| 101x                         | 16-bit write D[15:0]                                  | 1100                                    |

| 11xx <sup>[1]</sup>          | burst of four 32-bit writes, BLAST not used           | 0000                                    |

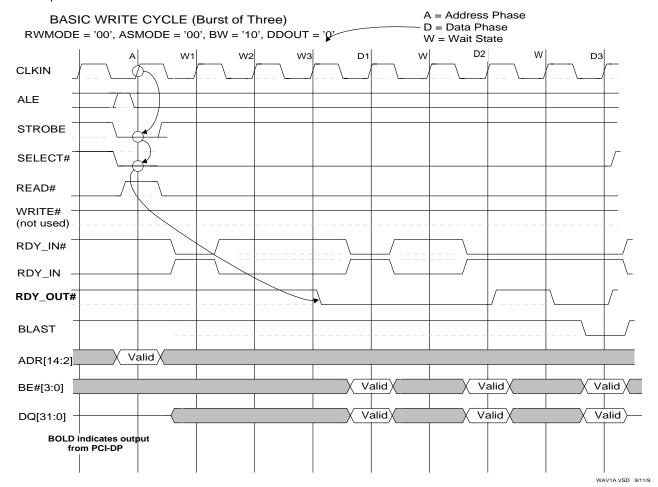

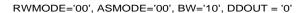

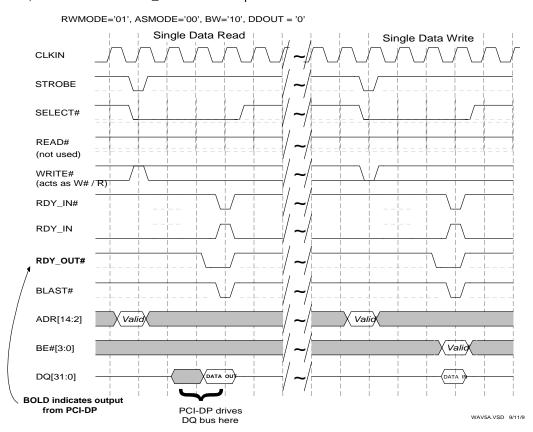

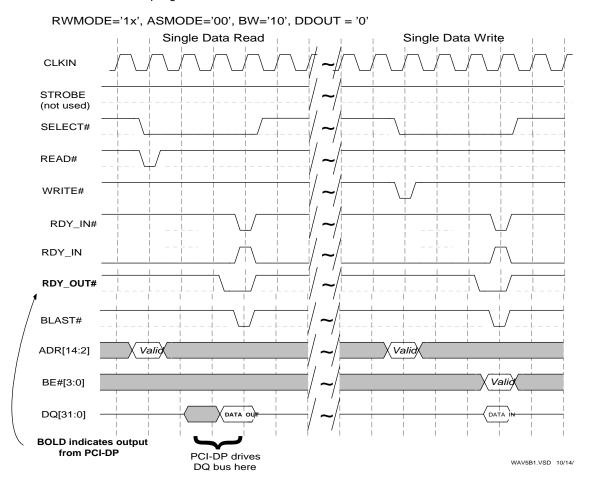

# **Timing Diagrams**

# **Write Cycle**

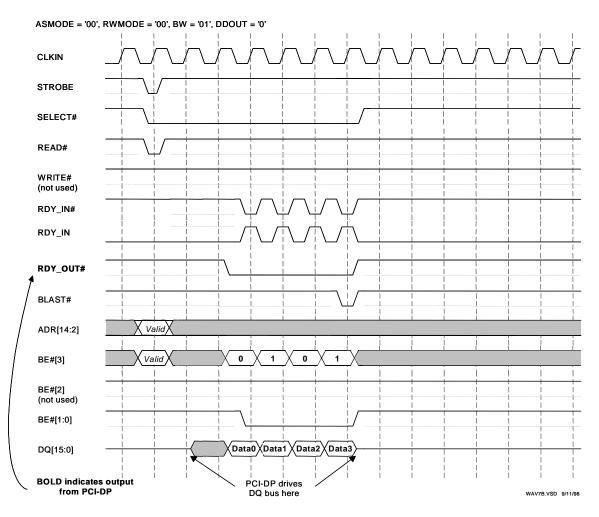

A basic write cycle is illustrated below. It includes a burst of three data phases on a 32-bit wide bus.

#### Note:

1. This encoding, {BW[1:0], BEMODE, BE[3:2]} = {'111111'}, results in a burst of four DWORD. BLAST should remain active.

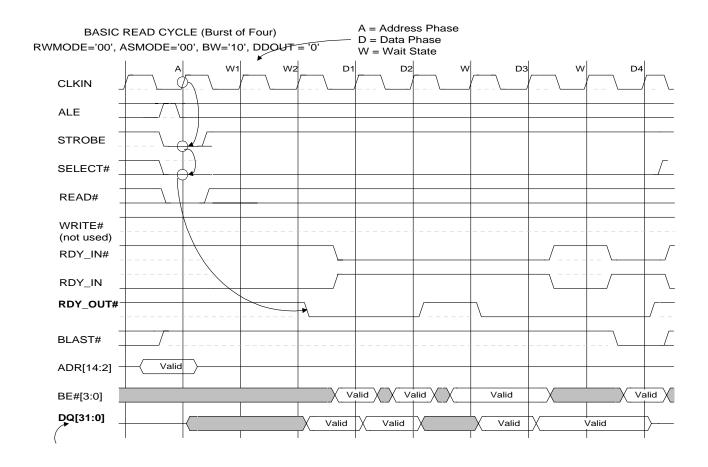

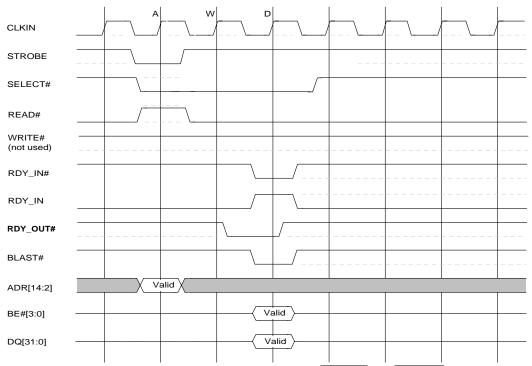

# **Read Cycle**

The basic read cycle differs from the write cycle only in the level of the READ and  $\overline{\text{WRITE}}$  signals, and the timing and

driving of the data bus DQ. A basic read burst of four data phases on a 32-bit wide bus is illustrated.

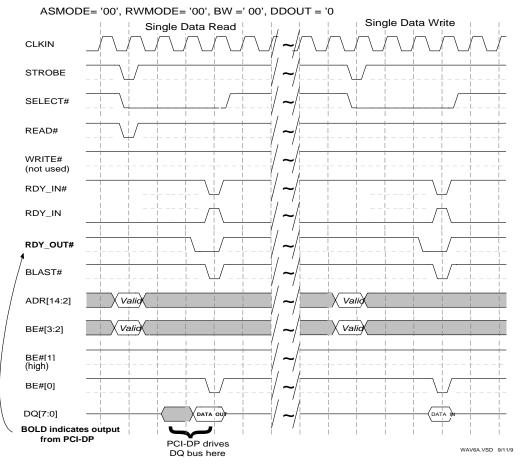

#### **Basic 8-bit Interface**

The following two waveforms illustrate the operation of the 8-bit interface mode. Note that only data lines DQ[7:0] are used. DQ[31:8] are unused and must be tied high or low; they cannot be left floating. The least significant bits of the local address, A[1] and A[0], must be connected to the byte enable pins  $\overline{BE}[3]$  and  $\overline{BE}[2]$ , respectively. These must be valid during the address phase.

In burst operation, BE#[3:2] are inputs used at A1 and A0 of the local address bus. Bursts to the 8-bit interface do not need to start on a DWORD boundary. The internal DWORD address will automatically increment after a data phase where  $\overline{\text{BE}}$ [3:2] equals '11', (A[1:0] = '11').

The first waveform illustrates single cycle operation and the second illustrates data burst operation.

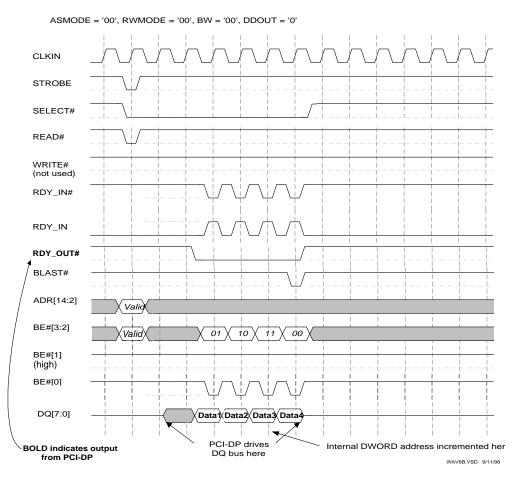

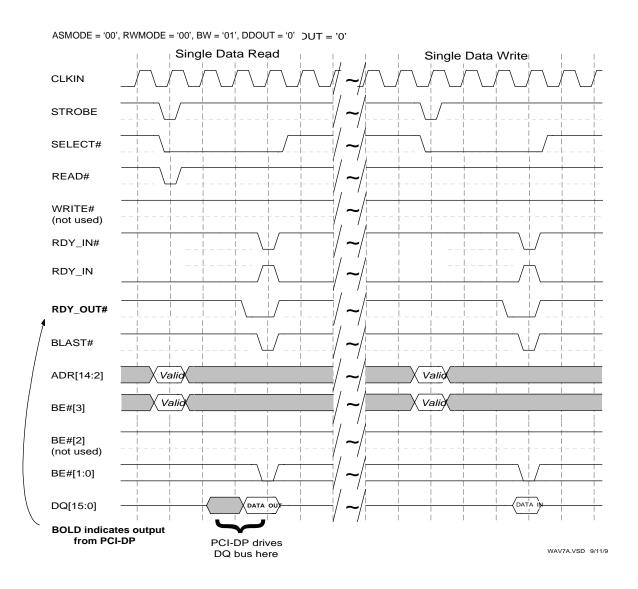

#### **Basic 16-bit Interface**

The following two waveforms illustrate the operation of the 16-bit interface mode. Note that only data lines DQ[15:0] are used. DQ[31:16] are unused and must be tied HIGH or LOW; they cannot be left floating. The least significant bit of the local address of the 16-bit bus, A[1], must be connected to the byte enable pin  $\overline{\text{BE}}$ [3]. It must be valid during the address phase.

Note that  $\overline{\text{BE}}[1:0]$  are used as byte enables. If the processor always does 16-bit accesses, then these can be tied active LOW. These byte enables can also be used for Upper Data

Strobe (UDS) and Lower Data Strobe (LDS) for processors which produce these signals.

In burst operation,  $\overline{BE}[3]$  must be incremented (toggled) at the end of each data phase. Bursts to the 16-bit interface do not need to start on a DWORD boundary. The internal DWORD address will automatically increment after a data phase where  $\overline{BE}[3]$  equals '1', (A[1] = '1').

The first waveform illustrates single cycle operation and the second illustrates data burst operation.

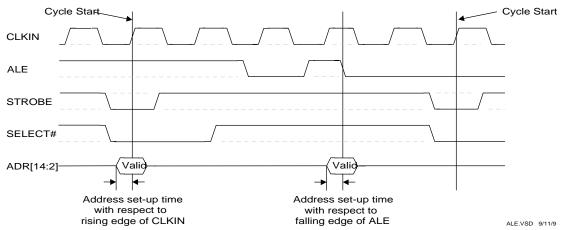

#### **ALE—Address Latch Enable**

The ALE signal may be used in two modes. With ALE tied active, the address is latched during the address phase. That is, when the STROBE and SELECT signals are active, the address on the ADR[14:2] pins is latched on the rising edge of CLKIN. The second way is to use the trailing edge of ALE to latch the address. The CY7C09449PV still needs a valid ad-

dress phase (STROBE and SELECT active at the rising edge of CLKIN) before it will begin processing the address. A valid and stable address must occur before the trailing edge of ALE and before the rising edge of CLKIN where STROBE and SELECT are active. The active polarity of ALE is defined in the Operations Registers: ALE\_POL of the Local Bus Configuration Register.

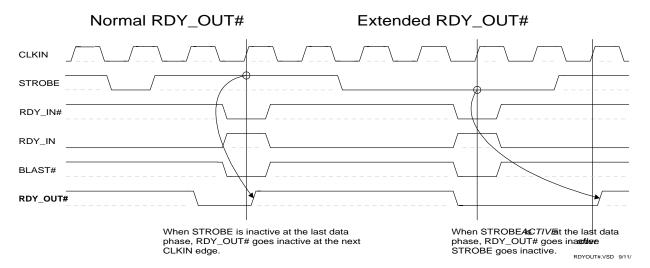

#### RDY\_OUT\_OE—Ready Out Three-state Mode

The RDY\_OUT signal may be configured to drive at all times or to three-state when inactive. The three-state mode is a sustained deasserted function. In three-state mode, when RDY\_OUT is to go inactive, RDY\_OUT is driven to the deasserted level for one clock, and then three-stated. It remains three-stated until RDY\_OUT is to be asserted. The logic polarity of RDY\_OUT is programmable. The mode (RDY\_OUT\_OE) and polarity (RDYOUT\_POL) controls are set in the Local Bus Configuration Register, LBUSCFG, of the Operations Registers.

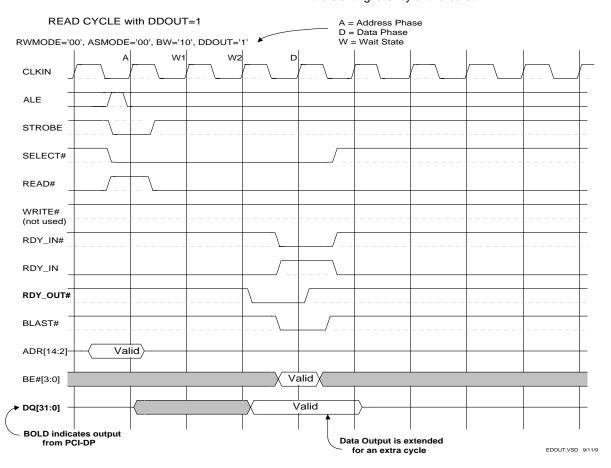

#### **DDOUT—Delayed Data Out**

The delayed data out control defines when the CY7C09449PV drives the DQ bus during a local bus read. The control is defined in the Operations Registers: DDOUT of the Local Bus Configuration Register. When DDOUT = '0', the CY7C09449PV will drive the DQ bus during a read starting one clock after the address phase and stop driving at the clock edge where both of the ready inputs and BLAST# are active. When DDOUT = '1', the CY7C09449PV will drive the DQ bus during a read starting one CLKIN clock after the address phase and stop driving one clock after the clock edge where the two ready inputs and  $\overline{BLAST}$  are active. The data is driven for one clock period after the signal that the transaction is over. In the case of multiple data phases, it adds one clock cycle to the starting latency of the burst.

#### RDY\_OUT—Ready Out

STROBE can be active or inactive during data phases. However, if STROBE is active during the data phase when BLAST is active AND the extended ready out control (XTND\_RDY\_OUT) is set, the CY7C09449PV keeps RDY\_OUT active until STROBE goes inactive. In the case of a read, the CY7C09449PV will continue to drive the data on DQ until STROBE is deasserted.

#### LINE\_WRAP\_DIS—Cache Line Wrap Disable

This setting is used to disable cache line wrapping, LINE\_WRAP\_DIS = '1'. Cache line wrapping only occurs when the local bus interface is set for 32 bit width with encoded byte enables, using the Motorola byte enable encoding, and the bus SIZ bits indicate a cache line access. Specifically, this is when BW = '11', BEMODE = '0', and BE[3] = BE[2] = '1.' If a cache line access is made and cache line wrapping is disabled, then the burst will proceed linearly with no implicit address wraparound at the 4 DWORD boundary.

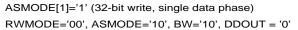

# **ASMODE**—Address Strobe Mode

The address strobe mode control defines the polarity and the timing used to sample the CY7C09449PV address strobe input signal, STROBE. The two-bit control field is defined in the Operations Registers: ASMODE of the Local Bus Configuration Register.

ASMODE[0] defines the polarity of the STROBE input signal; '0' = active LOW and '1' = active HIGH.

ASMODE[1] controls the sampling edge of the STROBE signal. Logic LOW indicates that the signal is sampled using the rising edge of CLKIN. A logic HIGH indicates that the signal is sampled with the falling edge of CLKIN. Sampling on the falling edge should only be used when the required minimum setup time with respect to the clock rising edge cannot be met on the signals.

The following waveform illustrates the operation of the ASMODE[1] pin. ADR and READ are sampled at E2, and a valid write occurs at E4. Note that STROBE is captured at the negative edge labeled NE1 and that the ADR and READ signals are sampled at the positive clock edge labeled E2. Also note that the ready signals are sampled at the negative edge labeled NE4 and not at the positive edge labeled E5. STROBE is active LOW since ASMODE[0] = '0.'

# <u>Falling Edge Sampling for RDY\_IN, RDY\_IN, SELECT, and STROBE</u>

These signals may be configured for falling edge sampling within the Local Bus Configuration Register (LBUSCFG) of the Operations Registers. RDY\_IN and RDY\_IN sampling is configured by the RDY\_IN\_FALL bit, SELECT sampling is configured by the SELECT\_FALL bit, and STROBE sampling is configured by the ASMODE[1] bit. Setting any one or all of these bits will not effect the sampling of other signals on the local bus. That is, all other signals that are synchronous inputs are sampled on the rising edge of the local bus clock, CLKIN. When a negative edge sample is used, the other signals are qualified by that sample on the immediately following rising edge of CLKIN. For example, study the prior waveform illustrating operation of ASMODE. In that diagram, STROBE is configured to sample on the falling edge of CLKIN because

ASMODE[1]='1'. An active STROBE indicates an address phase. The valid address is captured on the first rising clock edge after STROBE is sampled active.

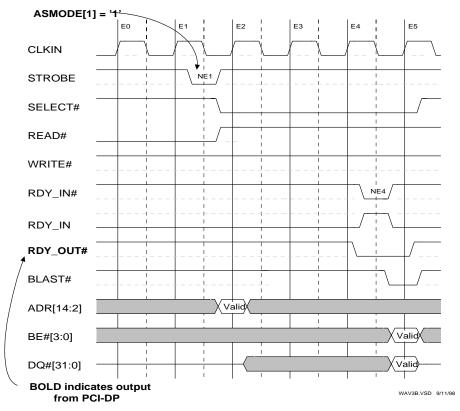

# **RWMODE—Read Write Mode**