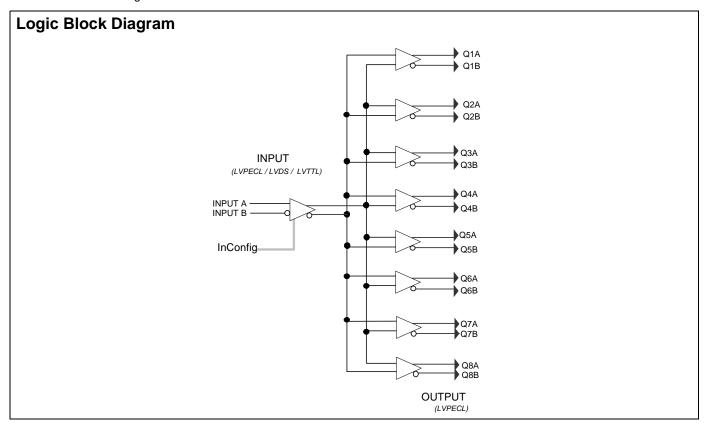

# 1:8 Clock Fanout Buffer

## **Features**

- Low-voltage operation V<sub>DD</sub> = 3.3V

- 1:8 fanout

- Operation to 350 MHz

- Single input configurable for LVDS, LVPECL, or LVTTL

- 8 pair of LVPECL outputs

- Drives a 50 ohm load

- Low input capacitance

- Low output skew

- Low propagation delay (tpd = 4 ns, typical)

- Commercial and Industrial temperature ranges

- 38-Pin TSSOP Package

# **Description**

The Cypress CY2DP818 fanout buffer features a single LVDS or a single ended LVTTL compatible input and eight LVPECL output pairs.

Designed for data-communications clock management applications, the large fanout from a single input reduces loading on the input clock.

The CY2DP818 is ideal for both level translations from single ended to LVPECL and/or for the distribution of LVPECL based clock signals.

The Cypress CY2DP818 has configurable input functions. The input is user configurable via the InConfig pin for single ended or differential input.

# **Pinouts**

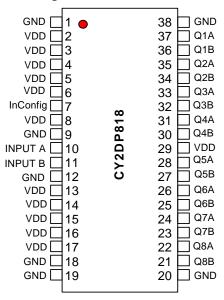

# **Pin Configuration**

Figure 1. 38-Pin TSSOP

# **Pin Description**

| Pin Number                                                              | Pin Name                                                                     | Туре                                                         | Description                                                                                                                                |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9, 12, 18, 19, 20, 38                                                | GND                                                                          | POWER                                                        | Ground                                                                                                                                     |

| 2, 3, 4, 5, 6, 8, 13, 14, 15, 16, 17, 29                                | VDD                                                                          | POWER                                                        | Power Supply                                                                                                                               |

| 10, 11                                                                  | Input A, Input B                                                             | Default: LVPECL/LDVS<br>Optional: LVTTL/LVCMOS<br>single pin | Clock Input. Either differential LVPECL/LVDS or single-ended LVTTL/LVCMOS, as determined by InConfig. See Table 1 and Table 2 for details. |

| 37, 36, 35, 34,<br>33, 32, 31, 30,<br>28, 27, 26, 25,<br>24, 23, 22, 21 | Q1(A,B), Q2(A,B)<br>Q3(A,B), Q4(A,B)<br>Q5(A,B), Q6(A,B)<br>Q7(A,B), Q8(A,B) | LVPECL                                                       | Differential Output Clocks                                                                                                                 |

| 7                                                                       | InConfig                                                                     | LVTTL/LVCMOS                                                 | Control Input. Selects input type: either differential LVPECL/LVDS or single-ended LVTTL/LVCMOS See Table 1 and Table 2 for details.       |

Table 1. Input Receiver Configuration for Differential or LVTTL/LVCMOS

| InConfig (Pin 7) Input Receiver Family |   |                 | Input Receiver Type                                              |  |  |  |

|----------------------------------------|---|-----------------|------------------------------------------------------------------|--|--|--|

|                                        | 1 | LVTTL or LVCMOS | Single ended, non-inverting or inverting, void of bias resistors |  |  |  |

|                                        | 0 | LVDS or LVPECL  | Differential, void of internal termination                       |  |  |  |

Table 2. Single ended LVTTL/LVCMOS Input Logic (InConfig = 1)

| •                  | . • •              | • ,                   |

|--------------------|--------------------|-----------------------|

| Input A (+) Pin 10 | Input B (-) Pin 11 | Output Clock QnA Pins |

| Input              | Ground             | True                  |

| Input              | VDD                | Invert                |

| Ground             | Input              | Invert                |

| VDD                | Input              | True                  |

Document #: 38-07061 Rev. \*B Page 2 of 7

# Maximum Ratings<sup>[1]</sup>

| Storage Temperature:               | –65°C to + 150°C |

|------------------------------------|------------------|

| Ambient Temperature:               | –40°C to +85°C   |

| Supply Voltage to Ground Potential |                  |

| (Inputs and V <sub>DD</sub> only)  | 0.3V to 4.6V     |

| Supply Voltage to Ground Potential |                                |

|------------------------------------|--------------------------------|

| (Outputs only)                     | $-0.3V$ to $V_{DD} + 0.3V$     |

| DC Input Voltage                   | 0.3V to V <sub>DD</sub> + 0.3V |

| DC Output Voltage                  | 0.3V to V <sub>DD</sub> + 0.9V |

| Power Dissipation                  | 0.75W.                         |

### **Table 3. Power Supply Characteristics**

| Parameter | Description                                 | Test Conditions                                                                                       | Min | Тур | Max | Unit       |

|-----------|---------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------------|

| ICC       | Dynamic Power Supply Current                | V <sub>DD</sub> = Max<br>Input toggling 50% Duty Cycle,<br>Outputs Open                               |     | 1.5 | 2.0 | mA/<br>MHz |

| IC        | Total Power Supply Current                  | V <sub>DD</sub> = Max<br>Input toggling 50% Duty Cycle,<br>Outputs 50 ohms<br>fL=100 MHz              |     |     | 350 | mA         |

| IC Core   | Core current when output loads are disabled | V <sub>DD</sub> = Max<br>Input toggling 50% Duty Cycle,<br>Outputs not connected to VTT<br>fL=100 MHz |     |     | 50  | mA         |

# **DC Electrical Specifications**

# Table 4. LVDS Input, $V_{DD} = 3.3V \pm 5\%$ , $T_{\Delta} = 0^{\circ}C$ to $70^{\circ}C$ or $-40^{\circ}C$ to $85^{\circ}C$

| IUDIO TI ETD    | 14516 4. EVB6 Input, V <sub>DD</sub> = 0.6V 2676, 1 <sub>A</sub> = 0.0 to 10.00 1. 40.0 to 00.00 |                                 |         |               |     |      |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------|---------------------------------|---------|---------------|-----|------|--|--|--|--|

| Parameter       | Description                                                                                      | Conditions                      | Min     | Тур           | Max | Unit |  |  |  |  |

| V <sub>ID</sub> | Magnitude of Differential Input Voltage                                                          |                                 | 100     |               | 600 | mV   |  |  |  |  |

| V <sub>IC</sub> | Common-mode of Differential Input<br>VoltageIV <sub>ID</sub> I (min and max)                     |                                 | IVIDI/2 | 2.4-(IVIDI/2) |     | V    |  |  |  |  |

| V <sub>IH</sub> | Input High Voltage                                                                               | Guaranteed Logic High Level     | 2       |               |     | V    |  |  |  |  |

| V <sub>IL</sub> | Input Low Voltage                                                                                | Guaranteed Logic Low Level      |         |               | 0.8 | V    |  |  |  |  |

| I <sub>IH</sub> | Input High Current                                                                               | $V_{DD} = Max, V_{IN} = V_{DD}$ |         | ±10           | ±20 | μА   |  |  |  |  |

| I <sub>IL</sub> | Input Low Current                                                                                | $V_{DD} = Max, V_{IN} = V_{SS}$ |         | ±10           | ±20 | μА   |  |  |  |  |

# Table 5. LVPECL Input, $V_{DD}$ = 3.3V ±5%, $T_A$ = 0°C to 70°C or -40°C to 85°C

| Parameter       | Description                    | Conditions                      | Min  | Тур | Max  | Unit |

|-----------------|--------------------------------|---------------------------------|------|-----|------|------|

| V <sub>ID</sub> | Differential Input Voltage p-p | Guaranteed Logic High Level     | 400  |     | 2600 | mV   |

| V <sub>IH</sub> | Input High Voltage             | Guaranteed Logic High Level     | 2.15 |     | 2.4  | V    |

| V <sub>IL</sub> | Input Low Voltage              | Guaranteed Logic Low Level      | 1.5  |     | 1.8  | V    |

| I <sub>IH</sub> | Input High Current             | $V_{DD} = Max, V_{IN} = V_{DD}$ |      | ±10 | ±20  | μΑ   |

| I <sub>IL</sub> | Input Low Current              | $V_{DD} = Max, V_{IN} = V_{SS}$ |      | ±10 | ±20  | μА   |

| $V_{CM}$        | Common-mode Voltage            |                                 |      |     | 225  | mV   |

# Table 6. LVTTL/LVCMOS Input, $V_{DD}$ = 3.3V ±5%, $T_A$ = 0°C to 70°C or -40°C to 85°C

| Parameter       | Description        | Conditions                    | Min | Тур | Max | Unit |

|-----------------|--------------------|-------------------------------|-----|-----|-----|------|

| V <sub>IH</sub> | Input High Voltage |                               | 2   |     |     | V    |

| V <sub>IL</sub> | Input Low Voltage  |                               |     |     | 0.8 | V    |

| I <sub>IH</sub> | Input High Current | $V_{DD} = Max, V_{IN} = 2.7V$ |     |     | 1   | μΑ   |

| I <sub>IL</sub> | Input Low Current  | $V_{DD} = Max, V_{IN} = 0.5V$ |     |     | -1  | μΑ   |

Document #: 38-07061 Rev. \*B Page 3 of 7

<sup>1.</sup> Stresses greater than those listed under absolute maximum ratings may cause permanent damage to the device. This is intended to be a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# Table 6. LVTTL/LVCMOS Input, $V_{DD}$ = 3.3V ±5%, $T_A$ = 0°C to 70°C or -40°C to 85°C

| Parameter       | Description         | Conditions                           | Min | Тур  | Max  | Unit |

|-----------------|---------------------|--------------------------------------|-----|------|------|------|

| I <sub>I</sub>  | Input High Current  | $V_{DD} = Max, V_{IN} = V_{DD}(Max)$ |     |      | 20   | μΑ   |

| V <sub>IK</sub> | Clamp Diode Voltage | $V_{DD} = Min, I_{IN} = -18mA$       |     | -0.7 | -1.2 | V    |

| V <sub>H</sub>  | Input Hysteresis    |                                      |     | 80   |      | mV   |

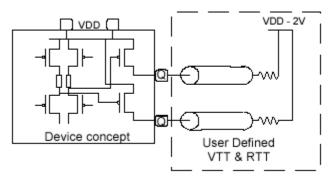

# Table 7. LVPECL Output, $V_{DD} = 3.3V \pm 5\%$ , $T_A = 0$ °C to 70°C or -40°C to 85°C

| Parameter                      | Description                            | Conditions                                                                  | Min  | Тур | Max  | Unit |

|--------------------------------|----------------------------------------|-----------------------------------------------------------------------------|------|-----|------|------|

| V <sub>OD</sub>                | Driver Differential Output voltage p-p | $V_{DD} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}, R_L = 50 \Omega$         | 1000 |     | 3600 | mV   |

| V <sub>OC</sub>                | Driver common-mode p-p                 | $V_{DD} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}, R_L = 50 \Omega$         |      |     | 300  | mV   |

| t <sub>R</sub>                 | Rise Time                              | Differential 20% to 80%, C <sub>L</sub> = 10 pF to GND,                     | 300  |     | 1200 | ps   |

| t <sub>F</sub>                 | Fall Time                              | $R_L = 50 \Omega$ to GND                                                    |      |     |      |      |

| V <sub>OH</sub>                | Output High Voltage                    | $V_{DD} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}, I_{OH} = -12 \text{ mA}$ | 2.1  |     | 3.0  | V    |

| V <sub>OL</sub> <sup>[2]</sup> | Output Low Voltage                     | $V_{DD} = Min, V_{IN} = V_{IH} \text{ or } V_{IL}$                          | 0.8  |     | 1.3  | V    |

| I <sub>OS</sub>                | Short Circuit Current                  | V <sub>DD</sub> = Max, V <sub>OUT</sub> = GND                               | -125 |     | -150 | mA   |

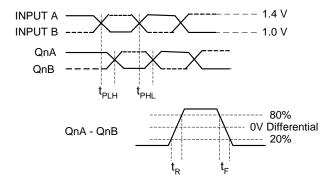

# **AC Switching Characteristics**

# Table 8. $V_{DD}$ = 3.3V ±5%, $T_A$ = 0°C to 70°C or -40°C to 85°C

| Parameter          | Description                                                                                                                                                       | Conditions                | Min | Тур | Max | Unit |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|-----|-----|------|

| t <sub>PLH</sub>   | Propagation Delay – Low to High                                                                                                                                   | $V_{ID} = 100 \text{ mV}$ | 3   | 4   | 5   | ns   |

| t <sub>PHL</sub>   | Propagation Delay – High to Low                                                                                                                                   | $V_{ID} = 100 \text{ mV}$ | 3   | 4   | 5   | ns   |

| t <sub>SK(0)</sub> | Output Skew: Skew between outputs of the same package (in phase)                                                                                                  |                           |     |     | 0.2 | ns   |

| t <sub>SK(p)</sub> | Pulse Skew: Skew between opposite transitions of the same output (t <sub>PHL</sub> -t <sub>PLH</sub> )                                                            |                           |     | 0.2 |     | ns   |

| t <sub>SK(t)</sub> | Package Skew: Skew between outputs of different packages at the same power supply voltage, temperature and package type. Same input signal level and output load. | V <sub>ID</sub> = 100 mV  |     |     | 1   | ns   |

## **Table 9. High frequency Parametrics**

| Parameter | Description                              | Conditions                                  | Min | Тур | Max | Unit |

|-----------|------------------------------------------|---------------------------------------------|-----|-----|-----|------|

| Fmax      | Maximum frequency V <sub>DD</sub> = 3.3V | 45%–55% duty cycle<br>Standard load circuit |     |     | 350 | MHz  |

### Note

Document #: 38-07061 Rev. \*B Page 4 of 7

<sup>2.</sup>  $V_{OL}$  levels are dependent on the termination voltage  $V_{TT}$  and termination resistance  $R_{TT}$ . Changing either of these values will affect  $V_{OL}$ .

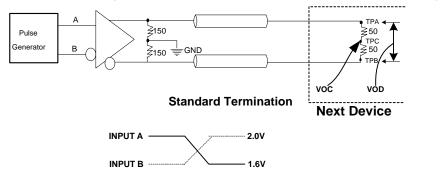

Figure 2. Driver Design

Figure 3. Standard Termination

Figure 4. Differential Receiver to Driver Propagation Delay and Driver Transition Time<sup>[3,4,5,6]</sup>

Figure 5. Test Circuit and Voltage Definitions for the Driver Common Mode Output Voltage [3,4,5,6]

### Notes

- 3. All input pulses are supplied by a frequency generator with the following characteristics:  $t_R$  and  $t_F \le 1$  ns; pulse rerate = 50 Mpps; pulse width =  $10 \pm 0.2$  ns.

- 4. RL = 50 ohm  $\pm$  1%; Zline = 50 ohm 6".

- 5. CL includes instrumentation and fixture capacitance within 6 mm of the UT.

- 6. TPA and B are used for prop delay and Rise/Fall measurements. TPC is used for VOC measurements only and is otherwise connected to V<sub>DD</sub> 2V.

# **Ordering Information**

| Part Number  | Package Type               | Product Flow             |

|--------------|----------------------------|--------------------------|

| CY2DP818ZI   | 38-pin TSSOP               | Industrial, -40° to 85°C |

| CY2DP818ZIT  | 38-pin TSSOP-Tape and Reel | Industrial, –40° to 85°C |

| CY2DP818ZC   | 38-pin TSSOP               | Commercial, 0°C to 70°C  |

| CY2DP818ZCT  | 38-pin TSSOP-Tape and Reel | Commercial, 0°C to 70°C  |

| Pb-Free      |                            |                          |

| CY2DP818ZXI  | 38-pin TSSOP               | Industrial, -40° to 85°C |

| CY2DP818ZXIT | 38-pin TSSOP-Tape and Reel | Industrial, –40° to 85°C |

| CY2DP818ZXC  | 38-pin TSSOP               | Commercial, 0°C to 70°C  |

| CY2DP818ZXCT | 38-pin TSSOP-Tape and Reel | Commercial, 0°C to 70°C  |

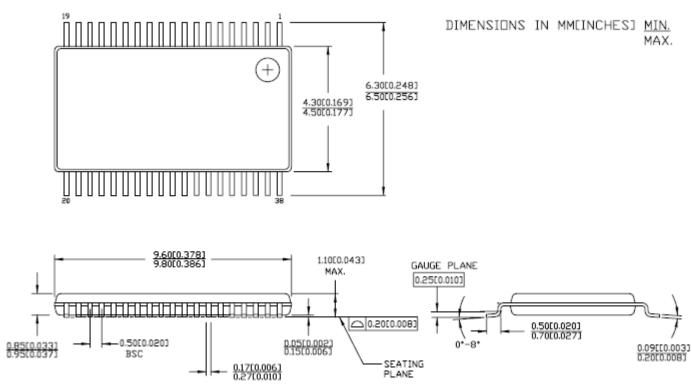

# **Package Drawing and Dimensions**

Figure 6. 38-Pin TSSOP (4.40 mm Body) Z38 and ZZ38

51-85151-\*A

# **Document History Page**

| Document Title: CY2DP818 1:8 Clock Fanout Buffer Document Number: 38-07061 |         |                 |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------------------------------------------------------------------------|---------|-----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision                                                                   | ECN     | Orig. of Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| **                                                                         | 107086  | 06/07/01        | IKA                | New Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| *A                                                                         | 115913  | 07/11/02        | CTK                | IC, VCM, VOC, Rise/Fall Time Fmax (20)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| #*************************************                                     | 2748606 | 08/05/09        | KVM                | Deleted references to ComLink Minor edits to page 1 text Instances of VCC changed to VDD Changed table sequence to be more logical Edited Table 1 on page 2 and reformatted Table 2 on page 2 for clarity Added voltage and temperature specs to heading of all DC and AC tables Added commercial temp range to DC and AC table headings Clarified wording for IC Core Removed duplicate I <sub>I</sub> (input high current) parameter from LVPECL & LVDS Removed T <sub>PE</sub> and T <sub>PD</sub> parameters from AC table Cleaned up waveform drawings Removed figures showing inputs for different InConfig values because Table 1 on page 2 and Table 2 on page 2 are more complete Added part numbers CY2DP818ZXC, CY2DP818ZXCT, CY2DP818ZXI and CY2DP818ZXIT to the ordering information table Revised Package Diagram |  |  |  |

# Sales, Solutions, and Legal Information

### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

### **Products**

PSoC psoc.cypress.com

Clocks & Buffers clocks.cypress.com

Wireless wireless.cypress.com

Memories memory.cypress.com

Image Sensors image.cypress.com

© Cypress Semiconductor Corporation, 2001-2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 38-07061 Rev. \*B

Revised August 5, 2009

Page 7 of 7