# FailSafe™ PacketClock™ Global Communications Clock Generator

#### **Features**

- Fully integrated phase-locked loop (PLL)

- FailSafe<sup>™</sup> output

- PLL driven by a crystal oscillator that is phase aligned with external reference

- Output frequencies selectable and/or programmed to standard communication frequencies

- · Low-jitter, high-accuracy outputs

- Commercial and Industrial operation

- 3.3V ± 5% operation

- 16-lead TSSOP

#### **Benefits**

Integrated high-performance PLL tailored for telecommunications frequency synthesis eliminates the need for external loop filter components

- When reference is in range, SAFE pin is driven high.

- When reference is off, DCXO maintains clock outputs. SAFE pin is low.

- DCXO maintains continuous operation should the input reference clock fail

- Glitch-free transition simplifies system design

- Selectable output clock rates include T1/DS1, E1, T3/DS3, E3, and OC-3.

- Works with commonly available, low-cost 18.432-MHz crystal

- · Zero-ppm error for all output frequencies

- Performance guaranteed for applications that require an extended temperature range

- · Compatible across industry standard design platforms

- Industry standard package with 6.4 x 5.0 mm<sup>2</sup> footprint and a height profile of just 1.1 mm.

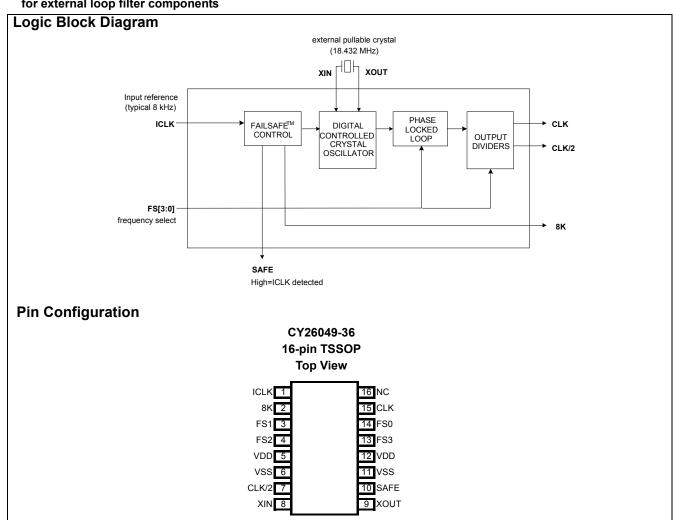

#### **Pin Definitions**

| Pin Name | Pin Number | Pin Description                                                        |  |  |  |

|----------|------------|------------------------------------------------------------------------|--|--|--|

| ICLK     | 1          | erence Input Clock; 8 kHz or 10 to 60 MHz.                             |  |  |  |

| 8K       | 2          | Clock Output; 8 kHz or high impedance in buffer mode.                  |  |  |  |

| FS1      | 3          | Frequency Select 1; Determines CLK outputs per Table 1.                |  |  |  |

| FS2      | 4          | Frequency Select 2; Determines CLK outputs per Table 1.                |  |  |  |

| VDD      | 5          | Voltage Supply; 3.3V.                                                  |  |  |  |

| VSS      | 6          | Ground                                                                 |  |  |  |

| CLK/2    | 7          | Clock Output; Frequency per Table 1.                                   |  |  |  |

| XIN      | 8          | Pullable Crystal Input; 18.432 MHz.                                    |  |  |  |

| XOUT     | 9          | Pullable Crystal Output; 18.432 MHz.                                   |  |  |  |

| SAFE     | 10         | High = reference ICLK within range, Low = reference ICLK out of range. |  |  |  |

| VSS      | 11         | Ground                                                                 |  |  |  |

| VDD      | 12         | Voltage Supply; 3.3V.                                                  |  |  |  |

| FS3      | 13         | Frequency Select 3; Determines CLK outputs per Table 1.                |  |  |  |

| FS0      | 14         | uency Select 0; Determines CLK outputs per Table 1.                    |  |  |  |

| CLK      | 15         | k Output; Frequency per Table 1.                                       |  |  |  |

| NC       | 16         | No Connect                                                             |  |  |  |

### **Selector Guide**

| Part Number | Input Frequency Range                                          |  | Output Frequencies               |  |

|-------------|----------------------------------------------------------------|--|----------------------------------|--|

|             | 8 kHz or 10 to 60 MHz Reference Input                          |  | 8 kHz to 155.52 MHz              |  |

|             | Crystal: 18.432-MHz pullable Crystal per Cypress Specification |  | Selectable (see <i>Table 1</i> ) |  |

#### **Functional Description**

CY26049 is a FailSafe frequency synthesizer with a reference clock input and three clock outputs. The device provides an optimum solution for applications where continuous operation is required in the event of a primary clock failure. The continuous, glitch-free operation is achieved by using a DCXO which serves as a primary clock source. The FailSafe control circuit synchronizes the DCXO with the reference as long as the reference is within the pull range of the crystal.

In the event of a reference clock failure the DCXO maintains the last frequency and phase information of the reference clock. The unique feature of the CY26049-36 is that the DCXO

is in fact the primary clocking source. When the reference clock is restored, the DCXO automatically re-synchronizes to the reference. The status of the reference clock input, as detected by the CY26049-36, is reported by the SAFE pin.

In the buffer mode (FS3:FS0 = 1110 or 1111), the CY26049-36 can be used as a jitter attenuator. In this mode, extensive jitter on the input clock will be "filtered", resulting in a low-jitter output clock.

## **Frequency Select Tables**

Table 1. CY26049-36 Frequency Select-Output Decoding Table-External Mode (MHz except as noted)

| ICLK  | FS3 | FS2 | FS1 | FS0 | CLK/2                 | CLK                   | 8K                    | Crystal |

|-------|-----|-----|-----|-----|-----------------------|-----------------------|-----------------------|---------|

| 8 kHz | 0   | 0   | 0   | 0   | 1.544                 | 3.088                 | 8 kHz                 | 18.432  |

| 8 kHz | 0   | 0   | 0   | 1   | 2.048                 | 4.096                 | 8 kHz                 | 18.432  |

| 8 kHz | 0   | 0   | 1   | 0   | 22.368                | 44.736                | 8 kHz                 | 18.432  |

| 8 kHz | 0   | 0   | 1   | 1   | 17.184                | 34.368                | 8 kHz                 | 18.432  |

| 8 kHz | 0   | 1   | 0   | 0   | 77.76                 | 155.52                | 8 kHz                 | 18.432  |

| 8 kHz | 0   | 1   | 0   | 1   | 16.384                | 32.768                | 8 kHz                 | 18.432  |

| 8 kHz | 0   | 1   | 1   | 0   | 14.352                | 28.704                | 8 kHz                 | 18.432  |

| 8 kHz | 0   | 1   | 1   | 1   | High Z <sup>[1]</sup> | High Z <sup>[1]</sup> | High Z <sup>[1]</sup> | 18.432  |

| 8 kHz | 1   | 0   | 0   | 0   | 18.528                | 37.056                | 8 kHz                 | 18.432  |

| 8 kHz | 1   | 0   | 0   | 1   | 12.352                | 24.704                | 8 kHz                 | 18.432  |

| 8 kHz | 1   | 0   | 1   | 0   | 7.68                  | 15.36                 | 8 kHz                 | 18.432  |

| 8 kHz | 1   | 0   | 1   | 1   | High Z <sup>[1]</sup> | High Z <sup>[1]</sup> | High Z <sup>[1]</sup> | 18.432  |

| 8 kHz | 1   | 1   | 0   | 0   | 12.288                | 24.576                | 8 kHz                 | 18.432  |

| 8 kHz | 1   | 1   | 0   | 1   | 16.384                | 32.768                | 8 kHz                 | 18.432  |

Table 2. CY26049-36 Frequency Select-Output Decoding Table-Buffer Mode

| ICLK     | FS3 | FS2 | FS1 | FS0 | CLK/2  | CLK    | 8K                    | Crystal |

|----------|-----|-----|-----|-----|--------|--------|-----------------------|---------|

| 20 to 60 | 1   | 1   | 1   | 0   | ICLK/2 | ICLK   | High Z <sup>[1]</sup> | ICLK/2  |

| 10 to 30 | 1   | 1   | 1   | 1   | 2*ICLK | 4*ICLK | High Z <sup>[1]</sup> | ICLK    |

#### Note:

<sup>1.</sup> High Z = high impedance.

## **Absolute Maximum Conditions**

| Supply Voltage (V <sub>DD</sub> ) | 0.5 to +7.0V                 |

|-----------------------------------|------------------------------|

| DC Input Voltage                  | 0.5V to V <sub>DD</sub> +0.5 |

| Storage Temperature (Non-Conden   | sing)55°C to +125°C          |

| Junction Temperature              | 40°C to +125°C               |

| Data Retention @ Tj=125°C                                            | .>10 years  |

|----------------------------------------------------------------------|-------------|

| Package Power Dissipation                                            | 350 mW      |

| ESD (Human Body Model) MIL-STD-883                                   | 2000V       |

| (Above which the useful life may be impaired. For lines, not tested. | user guide- |

## Recommended Pullable Crystal Specifications<sup>[2]</sup>

| Parameter                      | Description                                              | Comments                                                                             | Min. | Тур.   | Max. | Units |

|--------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|------|--------|------|-------|

| F <sub>NOM</sub>               | Nominal crystal frequency                                | Parallel resonance, fundamental mode, AT cut                                         | -    | 18.432 | -    | MHz   |

| C <sub>LNOM</sub>              | Nominal load capacitance                                 |                                                                                      | -    | 14     | -    | pF    |

| R <sub>1</sub>                 | Equivalent series resistance (ESR)                       | Fundamental mode                                                                     | -    | _      | 25   | Ω     |

| R <sub>3</sub> /R <sub>1</sub> | Ratio of third overtone mode ESR to fundamental mode ESR | Ratio used because typical R <sub>1</sub> values are much less than the maximum spec | 3    | _      | -    |       |

| DL                             | Crystal drive level                                      | No external series resistor assumed                                                  | -    | 0.5    | 2    | mW    |

| F <sub>3SEPHI</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | High side                                                                            | 400  | _      | -    | ppm   |

| F <sub>3SEPLO</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | Low side                                                                             | -    | -      | -200 | ppm   |

| C <sub>0</sub>                 | Crystal shunt capacitance                                |                                                                                      | -    | _      | 7    | pF    |

| C <sub>0</sub> /C <sub>1</sub> | Ratio of shunt to motional capacitance                   |                                                                                      | 180  | _      | 250  |       |

| C <sub>1</sub>                 | Crystal motional capacitance                             |                                                                                      | 14.4 | 18     | 21.6 | fF    |

## **Recommended Operating Conditions**

| Parameter          | Description                                                                                                | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{DD}$           | Operating Voltage                                                                                          | 3.15 | 3.3  | 3.45 | V    |

| T <sub>AC</sub>    | Ambient Temperature (Commercial Temperature)                                                               | 0    | _    | 70   | ° C  |

| T <sub>AI</sub>    | Ambient Temperature (Industrial Temperature)                                                               | -40  | _    | 85   | ° C  |

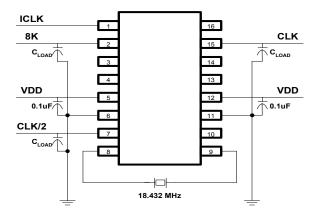

| C <sub>LOAD</sub>  | Max Output Load Capacitance                                                                                | _    | _    | 15   | pF   |

| t <sub>pu</sub>    | Power-up time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | _    | 500  | ms   |

| t <sub>ER(I)</sub> | 8 kHz Input Edge Rate, 20% to 80% of $V_{DD}$ = 3.3V                                                       | 0.07 | _    | _    | V/ns |

## **DC Electrical Specifications** (Commercial Temp: 0° to 70°C)

| Parameter       | Description            | Test Conditions                                                     | Min. | Тур. | Max. | Unit     |

|-----------------|------------------------|---------------------------------------------------------------------|------|------|------|----------|

| Гон             | Output High Current    | $V_{OH} = V_{DD} - 0.5$ , $V_{DD} = 3.3V$ (source)                  | 12   | 24   | _    | mA       |

| l <sub>OL</sub> | Output Low Current     | $V_{OL} = 0.5, V_{DD} = 3.3V (sink)$                                | 12   | 24   | -    | mA       |

| V <sub>IH</sub> | Input High Voltage     | CMOS Levels                                                         | 0.7  | _    | _    | $V_{DD}$ |

| V <sub>IL</sub> | Input High Voltage     | CMOS Levels                                                         | _    | _    | 0.3  | $V_{DD}$ |

| I <sub>IH</sub> | Input High Current     | V <sub>IH</sub> =V <sub>DD</sub>                                    | _    | 5    | 10   | μА       |

| I <sub>IL</sub> | Input Low Current      | V <sub>IL</sub> =0V                                                 | _    | 5    | 10   | μА       |

| C <sub>IN</sub> | Input Capacitance      |                                                                     | _    | _    | 7    | pF       |

| l <sub>oz</sub> | Output Leakage Current | High Z <sup>[1]</sup> output                                        | _    | ± 5  | _    | μΑ       |

| I <sub>DD</sub> | Supply Current         | C <sub>LOAD</sub> = 15 pF, V <sub>DD</sub> = 3.45V, FS [3:0] = 0100 | _    | _    | 45   | mA       |

|                 |                        | C <sub>LOAD</sub> = 15 pF, V <sub>DD</sub> = 3.45V, FS [3:0] = 1101 | _    | -    | 30   | mA       |

#### Note:

<sup>2.</sup> Ecliptek ECX-5761-18.432 M and ECX-5762-18.432 M meets these specifications.

## DC Electrical Specifications (Industrial Temp: -40° to 85°C)

| Parameter       | Description            | Test Conditions                                                          | Min. | Тур. | Max. | Unit     |

|-----------------|------------------------|--------------------------------------------------------------------------|------|------|------|----------|

| I <sub>OH</sub> | Output High Current    | V <sub>OH</sub> = V <sub>DD</sub> - 0.5, V <sub>DD</sub> = 3.3V (source) | 10   | 20   | _    | mΑ       |

| l <sub>OL</sub> | Output Low Current     | $V_{OL} = 0.5, V_{DD} = 3.3V (sink)$                                     | 10   | 20   | -    | mΑ       |

| V <sub>IH</sub> | Input High Voltage     | CMOS Levels                                                              | 0.7  | -    | -    | $V_{DD}$ |

| V <sub>IL</sub> | Input High Voltage     | CMOS Levels                                                              | _    | -    | 0.3  | $V_{DD}$ |

| I <sub>IH</sub> | Input High Current     | $V_{IH} = V_{DD}$                                                        | _    | 5    | 10   | μА       |

| I <sub>IL</sub> | Input Low Current      | V <sub>IL</sub> = 0V                                                     | _    | 5    | 10   | μА       |

| C <sub>IN</sub> | Input Capacitance      |                                                                          | _    | _    | 7    | pF       |

| l <sub>OZ</sub> | Output Leakage Current | High Z <sup>[1]</sup> output                                             | _    | ± 5  | -    | μА       |

| I <sub>DD</sub> | Supply Current         | C <sub>LOAD</sub> = 15 pF, V <sub>DD</sub> = 3.45V, FS [3:0] = 0100      | _    | -    | 50   | mΑ       |

|                 |                        | C <sub>LOAD</sub> = 15 pF, V <sub>DD</sub> = 3.45V, FS [3:0] = 1101      | _    | _    | 35   | mΑ       |

## AC Electrical Specifications (Commercial Temp: 0° to 70° C and Industrial Temp: -40° to 85°C)

| Parameter            | Description                        | Test Conditions                                                                                         | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| f <sub>ICLK-E</sub>  | Frequency, Input Clock             | Input Clock Frequency, External Mode                                                                    | 1    | 8.00 | -    | kHz  |

| f <sub>ICLK-B</sub>  | Frequency, Input Clock             | Input Clock Frequency, Buffer Mode                                                                      | 10   | _    | 60   | MHz  |

| LR                   | FailSafe Lock Range <sup>[3]</sup> | Range of reference ICLK for Safe = High                                                                 | -250 | _    | +250 | ppm  |

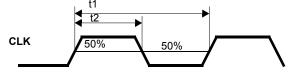

| $DC = t_2/t_1$       | Output Duty Cycle                  | Duty Cycle defined in Figure 1, measured at 50% of $V_{DD}$                                             | 45   | 50   | 55   | %    |

| T <sub>PJIT1</sub>   | Clock Jitter; output > 5 MHz       | Period Jitter, Peak to Peak, 10,000 periods                                                             | 1    | _    | 250  | ps   |

|                      |                                    | RMS Period Jitter, RMS                                                                                  | _    | _    | 50   | ps   |

| T <sub>PJIT2</sub>   | Clock Jitter; output <5 MHz        | Period Jitter, Peak to Peak, 10,000 periods                                                             | 1    | _    | 500  | ps   |

|                      |                                    | RMS Period Jitter, RMS                                                                                  | 1    | _    | 100  | ps   |

| t <sub>6</sub>       | PLL Lock Time                      | Time for PLL to lock within ± 150 ppm of target frequency                                               | _    | _    | 3    | ms   |

| t <sub>fs_lock</sub> | Failsafe Lock Time                 | Time for PLL to lock to ICKL (outputs phase aligned with ICKL and Safe = High)                          | ı    | _    | 7    | S    |

| f <sub>error</sub>   | Frequency Synthesis Error          | Actual mean frequency error vs. target                                                                  | -    | 0    | _    | ppm  |

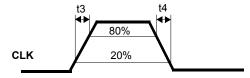

| ER                   | Rising Edge Rate                   | Output Clock Edge Rate, Measured from 20% to 80% of $V_{DD}$ , $C_{LOAD}$ = 15 pF See <i>Figure 2</i> . | 0.8  | 1.4  | 2    | V/ns |

| EF                   | Falling Edge Rate                  | Output Clock Edge Rate, Measured from 20% to 80% of $V_{DD}$ , $C_{LOAD}$ = 15 pF See <i>Figure 2</i> . | 0.8  | 1.4  | 2    | V/ns |

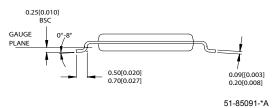

## **Voltage and Timing Definitions**

Figure 1. Duty Cycle Definition; DC = t2/t1

Figure 2. Rise and Fall Time Definitions: ER =  $0.6 \times VDD / t3$ , EF =  $0.6 \times VDD / t4$

#### Note

Document #: 38-07415 Rev. \*C

<sup>3.</sup> Dependent on crystals chosen and crystal specs.

### **Test Circuit**

### **Ordering Information**

| Ordering Code  | Package Type                | Operating Temperature Range |

|----------------|-----------------------------|-----------------------------|

| CY26049ZC-36   | 16-lead TSSOP               | Commercial 0 to 70°C        |

| CY26049ZC-36T  | 16-lead TSSOP-Tape and Reel | Commercial 0 to 70°C        |

| CY26049ZI-36   | 16-lead TSSOP               | Industrial –40 to 85°C      |

| CY26049ZI-36T  | 16-lead TSSOP-Tape and Reel | Industrial –40 to 85°C      |

| Lead Free      | ·                           | ·                           |

| CY26049ZXC-36  | 16-lead TSSOP               | Commercial 0 to 70°C        |

| CY26049ZXC-36T | 16-lead TSSOP-Tape and Reel | Commercial 0 to 70°C        |

| CY26049ZXI-36  | 16-lead TSSOP               | Industrial –40 to 85°C      |

| CY26049ZXI-36T | 16-lead TSSOP-Tape and Reel | Industrial –40 to 85°C      |

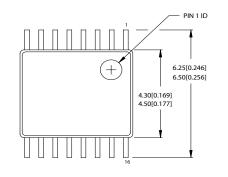

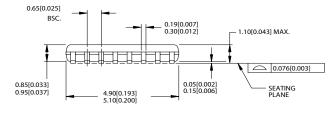

### **Package Diagram**

## 16-lead TSSOP 4.40 MM Body Z16.173

DIMENSIONS IN MM[INCHES] MIN.

MAX.

REFERENCE JEDEC MO-153

PACKAGE WEIGHT 0.05 gms

PART #

| PART #   |                |  |

|----------|----------------|--|

| Z16.173  | STANDARD PKG.  |  |

| ZZ16.173 | LEAD FREE PKG. |  |

FailSafe and PacketClock are trademarks of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

# **Document History Page**

| Document Title: CY26049-36 FailSafe™ PacketClock™ Global Communications Clock Generator Document Number: 38-07415 |         |            |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------|---------|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                                                                                              | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| **                                                                                                                | 114749  | 08/08/02   | CKN                | New Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *A                                                                                                                | 120067  | 01/06/03   | CKN                | Changed "FailSafe is a trademark of Silicon Graphics, Inc." to read "FailSafe is a trademark of Cypress Semiconductor"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *B                                                                                                                | 128000  | 07/15/03   | IJA                | Changed Benefits to read "When reference is in range, SAFE pin is driven high" Changed first sentence to "CY26049 is a FailSafe frequency synthesizer with a reference clock input and three clock outputs" Changed title from "Failsafe™ PacketClock™ Global Communications Clocks" to "FailSafe™ PacketClock™ Global Communications Clock Generator" Changed definitions in Pin Description Table Replaced format for Absolute Maximum Conditions Replaced Recommended Pullable Crystal Specifications table Added t <sub>pu</sub> to Recommended Operating Conditions Added I <sub>IH</sub> and I <sub>IL</sub> to DC Electrical Specifications Replaced AC Electrical Specifications from Cy26049-16 data sheet Changed Voltage and Timing Definitions to match CY2410 data sheet |

| *C                                                                                                                | 244412  | See ECN    | RGL                | Spec. $(t_{\text{ER(I)}})$ Input Edge Rate in the Recommended Operating Conditions Table Added Lead Free Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |