### CTSLV363 Low Phase Noise LVPECL Buffer and Translator SON8

### **FEATURES**

- LVPECL Outputs Optimized for Very Low Phase Noise (-165dBc/Hz)

- > Up to 1GHz Bandwidth

- Selectable ÷1, ÷2 Output

- Selectable Enable Logic

- 3.0V to 3.6V Operation

- RoHS Compliant Pb Free Packages

### **DESCRIPTION**

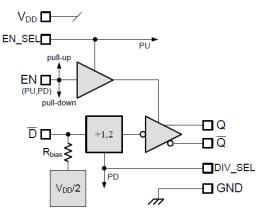

The CTSLV363 is a sine wave/CMOS to LVPECL buffer/translator optimized for very low phase noise (-165dBc/Hz). It is particularly useful in converting crystal or SAW based oscillators into LVPECL outputs for greater than 1GHz of bandwidth.

The <u>CTSLV363</u> is one of a family of parts that provide options of fixed ÷1, fixed ÷2 and selectable ÷1, ÷2 modes as well as active high enable or active low enable to oscillator designers. Refer to Table 1 for the comparison of parts within the CTSLV35x and CTSLV363 family.

# **ENGINEERING NOTES**

#### Functionality

Table 1 details the differences between the family parts to assist designers in selecting the optimal part for their design.

Table 2 lists the specific CTSLV363 functional operation.

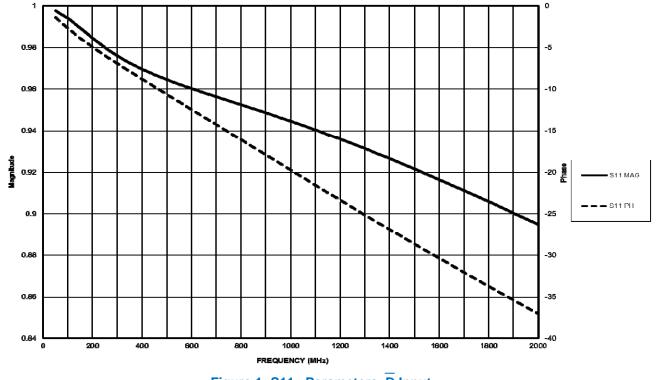

Figure 1 plots the S-parameters of the D input.

| Part Number | Divide Ratio        | EN Logic    | EN Pull-Up /<br>Pull-Down | Bandwidth |

|-------------|---------------------|-------------|---------------------------|-----------|

| CTSLV351    | ÷1                  | active HIGH | Pull-up                   | > 800MHz  |

| CTSLV353    | Selectable ÷1 or ÷2 | selectable  | selectable                | > 800MHz  |

| CTSLV363    | Selectable ÷1 or ÷2 | selectable  | selectable                | ≥ 1GHz    |

#### Table 1

|             | Inputs   |                 |       | Outputs      |      |  |

|-------------|----------|-----------------|-------|--------------|------|--|

| Part Number | EN_SEL   | EN              | D     | Q            | `Q   |  |

|             | High, NC | Low, NC         | Low   | Low          | High |  |

|             |          |                 | High  | High         | Low  |  |

| CTSLV363    |          | High            | Х     | Z            | Z    |  |

|             |          | High, NC<br>Low | Low   | Low          | High |  |

|             | Low      |                 | High  | High         | Low  |  |

|             |          | Low             | х     | Z            | Z    |  |

|             | Ľ        | DIV_SEL         | -     | Divide Ratio |      |  |

|             | l        | _ow, NC         | NC ÷1 |              |      |  |

|             | High     |                 |       |              | ÷2   |  |

# Table 2 – CTSLV363 Functional Operation, ÷1 mode

Figure 1- S11, Parameters, D Input

North Americas: +1-800-757-6686 • International: +1-508-435-6831 • Asia: +65-655-17551 • www.ctscorp.com/semiconductors Specifications are subject to change without notice.

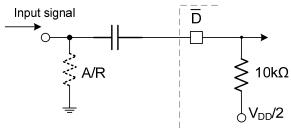

### **Input Termination**

The D input bias is  $V_{DD}/2$  fed through an internal  $10k\Omega$  resistor. For clock applications, an input signal of at least 750mV<sub>PP</sub> ensures the CTSLV363 meets AC specifications. The input should also be AC coupled to maintain a 50% duty cycle on the outputs. The input can be driven to any voltage between 0V and  $V_{DD}$  without damage or waveform degradation.

Figure 2 - Input Termination

#### **Output Termination Techniques**

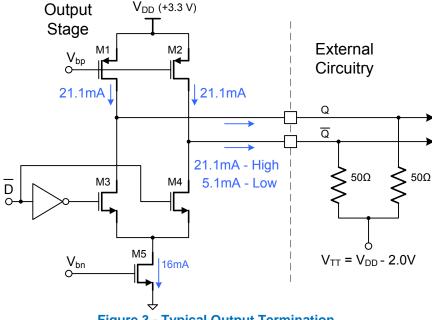

The LVPECL compatible output stage of the CTSLV363 uses a current drive topology to maximize switching speed as illustrated below in Figure 3. Two current source PMOS transistors (M1-M2) feed the output pins. M5 is an NMOS current source which is switched by M3 and M4. When M4 is on, M5 takes current from M2. This produces an output current of 5.1mA (low output state). M3 is off, and the entire 21.1mA flows through the output pin. The associated output voltage swings match LVPECL levels when external 50 $\Omega$  resistors terminate the outputs.

Both Q and  $\overline{Q}$  should always be terminated identically to avoid waveform distortion and circulating current caused by unsymmetrical loads. This rule should be followed even if only one output is in use.

**Figure 3 - Typical Output Termination**

CTSLV363 Low Phase Noise LVPECL Buffer and Translator SON8

### **Dual Supply LVPECL Output Termination**

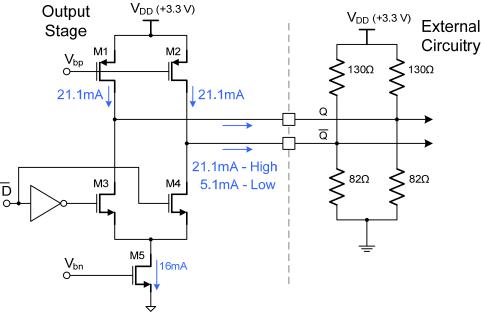

The standard LVPECL loads are a pair of  $50\Omega$  resistors connected between the outputs and V<sub>DD</sub>-2.0V (Figure 3). The resistors provide both the DC and the AC loads, assuming  $50\Omega$  interconnect. If an additional supply is available within the application, a four resistor termination configuration is possible (Figure 4).

**Figure 4 - Dual Supply Output Termination**

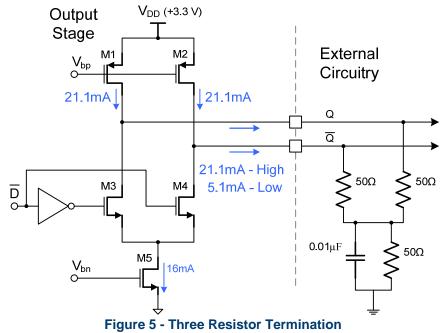

#### **Three Resistor Termination**

Another termination variant eliminates the need for the additional supply (Figure 5). Alternately three resistors and one capacitor accomplish the same termination and reduce power consumption.

North Americas: +1-800-757-6686 • International: +1-508-435-6831 • Asia: +65-655-17551 • www.ctscorp.com/semiconductors Specifications are subject to change without notice.

### **Evaluation Board (EBP63)**

CTS's evaluation board EBP63 provides the most convenient way to test and prototype CTSLV363 series circuits. Built for the CTSLV363Q 1.5x1.0 mm package, it is designed to support both dual and single supply operation. Dual supply operation ( $V_{DD}$ =+2.0V,  $V_{SS}$ =-1.3V) enables direct coupling to 50 $\Omega$  time domain test equipment (Figure 6).

Figure 6 - Split Supply LVPECL Output Termination

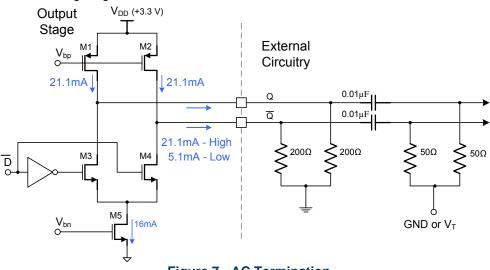

### **AC** Termination

Clock applications or phase noise/frequency domain testing scenarios typically require AC coupling. Figure 7 below shows the AC coupling technique. The  $200\Omega$  resistors form the required DC loads, and the  $50\Omega$ resistors provide the AC termination. The parallel combination of the 200 $\Omega$  and 50 $\Omega$  resistors results in a net  $40\Omega$  AC load termination. In many cases this will work well. If necessary, the  $50\Omega$  resistors can be increased to about 56Ω. Alternately, bias tees combined with current setting resistors will eliminate the lowered AC load impedance. The 50 $\Omega$  resistors are typically connected to ground but can be connected to the bias level needed by the succeeding stage.

Figure 7 - AC Termination

North Americas: +1-800-757-6686 • International: +1-508-435-6831 • Asia: +65-655-17551 • www.ctscorp.com/semiconductors Specifications are subject to change without notice. 5

# **ELECTRICAL SPECIFICATIONS**

### **Absolute Maximum Ratings**

#### Absolute Maximum Ratings are those values beyond which device life may be impaired.

| Symbol             | Characteristic              | Rating                        | Unit |

|--------------------|-----------------------------|-------------------------------|------|

| V <sub>DD</sub>    | Power Supply                | 0 to +5.5                     | V    |

| VI                 | Input Voltage               | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| T <sub>A</sub>     | Operating Temperature Range | -40 to +85                    | °C   |

| T <sub>STG</sub>   | Storage Temperature Range   | -65 to +150                   | С°   |

| ESD <sub>HBM</sub> | Human Body Model            | 2500                          | V    |

| ESD <sub>MM</sub>  | Machine Model               | 200                           | V    |

| ESD <sub>CDM</sub> | Charged Device Model        | 2500                          | V    |

### **DC Characteristics**

## DC Characteristics ( $V_{DD}$ = 3.0V to 3.6V unless otherwise specified, $T_A$ = -40°C to +85°C)

| Symbol            | Characteristic                                     | Conditions                                          |                        | Min   | Тур  | Max   | Unit |

|-------------------|----------------------------------------------------|-----------------------------------------------------|------------------------|-------|------|-------|------|

|                   |                                                    | -40°C                                               |                        | 2.05  |      | 2.415 |      |

| V <sub>OH</sub>   | Output HIGH Voltage <sup>1</sup>                   | +25°C                                               | V <sub>DD</sub> = 3.3V | 2.05  |      | 2.48  | V    |

|                   |                                                    | +85°C                                               |                        | 2.05  |      | 2.54  |      |

|                   |                                                    | -40°C                                               |                        | 1.365 |      | 1.615 |      |

| V <sub>OL</sub>   | Output LOW Voltage <sup>1</sup>                    | +25°C                                               | V <sub>DD</sub> = 3.3V | 1.43  |      | 1.68  | V    |

|                   |                                                    | +85°C                                               |                        | 1.49  |      | 1.74  |      |

| Ι <sub>Ζ</sub>    | Output Leakage Current, Tri-<br>state <sup>2</sup> | EN=Disable                                          |                        | -10   |      | 10    | μA   |

| V                 |                                                    | EN_SEL                                              |                        | 2     |      |       | V    |

| V <sub>IH</sub>   | High Level Input Voltage                           | DIV_SEL                                             |                        |       |      |       | v    |

| V <sub>IL</sub>   | Low Level Input Voltage                            | EN                                                  |                        |       |      | 0.8   | V    |

| I <sub>PU</sub>   | Pull-up Current                                    | EN_SEL                                              |                        |       | 2.2  |       | μA   |

| I <sub>PD</sub>   | Pull-down Current                                  | DIV_SEL                                             |                        |       | -2.2 |       | μA   |

| I <sub>P</sub>    | Pull-up / Pull-down Current                        | EN                                                  |                        |       | ±2.2 |       | μA   |

| R <sub>BIAS</sub> | Bias Resistor                                      | D Input to Internal V <sub>DD</sub> /2<br>Reference |                        |       | 10k  |       | Ω    |

| I <sub>DD</sub>   | Power Supply Current                               |                                                     |                        |       | 22   | 35    | mA   |

| I <sub>DDZ</sub>  | Power Supply Current –                             | DI                                                  | וput ≤ V <sub>IL</sub> |       |      | 8     | mA   |

| 002               | Outputs Tri-state <sup>1</sup>                     | EN=Disable                                          |                        |       |      | _     |      |

<sup>1</sup> Specified with outputs terminated through 50 $\Omega$  resistors to V<sub>DD</sub> -2V or Thevenin equivalent.

<sup>2</sup> Measured at Q /  $\overline{Q}$  pins.

# **AC Characteristics**

# AC Characteristics ( $V_{DD}$ = 3.0V to 3.6V, $T_A$ = -40°C to +85°C)

AC Specifications guaranteed by design

| Symbol                          | Characteristic                                   | Min  | Тур | Max             | Unit            |  |

|---------------------------------|--------------------------------------------------|------|-----|-----------------|-----------------|--|

| + / +                           | Output Rise/Fall <sup>1, 2</sup>                 | 00   |     | 250             | 20              |  |

| t <sub>r</sub> / t <sub>f</sub> | (20% - 80%)                                      | 80   |     | 250             | ps              |  |

|                                 | Maximum Input Frequency - Sine wave <sup>2</sup> |      |     |                 |                 |  |

| <b>f</b> <sub>MAX</sub>         | f <sub>MAX</sub> ÷1                              |      |     | 800             | MHz             |  |

|                                 | ÷2                                               |      |     | 1300            |                 |  |

| V <sub>INMAX</sub>              | Maximum Recommended Input Signal                 |      |     | V <sub>DD</sub> | V <sub>PP</sub> |  |

| V <sub>INMIN</sub>              | Minimum Recommended Input Signal                 | 0.2  |     |                 | V <sub>PP</sub> |  |

| t <sub>PLH</sub>                | Propagation Delay                                | 938  |     | 1614            | ps              |  |

| t <sub>PHL</sub>                | Propagation Delay                                | 938  |     | 1614            | ps              |  |

| Ĵrмs                            | RMS Jitter: 12kHz - 20MHz, 155MHz Center<br>Freq | r 36 |     |                 | fs              |  |

| n <sub>P</sub>                  | Phase Noise <sup>1, 2</sup> - 1MHz offset        | -165 |     | dBc/Hz          |                 |  |

<sup>1</sup> Specified with outputs terminated through 50W resistors to  $V_{CC}$  -2V or Thevenin equivalent.

$^{2}$  1.5 V<sub>P-P</sub> sine wave input, AC coupled to D pin.

CTS

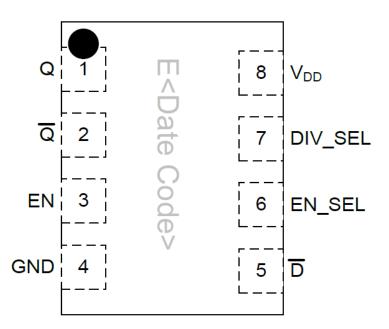

# **Pin Description and Configuration**

| Pin | Name            | Туре   | Function           |

|-----|-----------------|--------|--------------------|

| 1   | Q               | Output | LVPECL Output      |

| 2   | Q               | Output | LVPECL Output      |

| 3   | EN              | Input  | Enable             |

| 4   | GND             | Power  | Negative Supply    |

| 5   | D               | Input  | Sine or CMOS Input |

| 6   | EN_SEL          | Input  | Enable Select      |

| 7   | DIV_SEL         | Input  | Divide Select      |

| 8   | V <sub>DD</sub> | Power  | Positive Supply    |

### **Pin Assignments**

# PART ORDERING INFORMATION

| Part Number | Package | Marking |

|-------------|---------|---------|

| CTSLV363QG  | SON8    | EYW     |

North Americas: +1-800-757-6686 • International: +1-508-435-6831 • Asia: +65-655-17551 • www.ctscorp.com/semiconductors Specifications are subject to change without notice.

CTS

# CTSLV363 Low Phase Noise LVPECL Buffer and Translator SON8

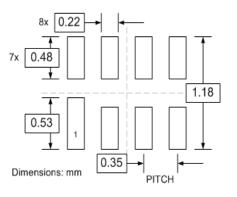

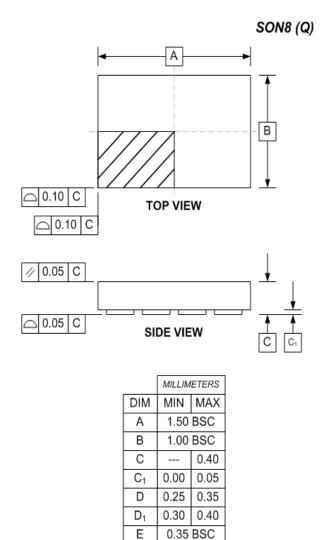

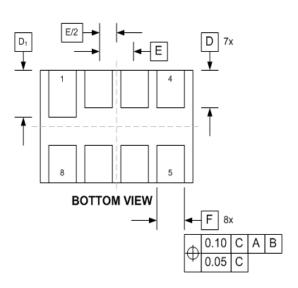

# **PACKAGE DIMENSIONS**

F

0.15 0.25

PCB LAND PATTERN/FOOTPRINT