# ExpressLane PEX 8509-AA 8-Lane/8-Port PCI Express Gen 1 Switch Data Book

Version 1.1

April

2009

Website

www.plxtech.com

Technical Support

www.plxtech.com/support

Phone

800 759-3735

408 774-9060

408 774-2169

Copyright  $\textcircled{\sc 0}$  2009 by PLX Technology, Inc. All Rights Reserved – Version 1.1 April, 2009

#### **Revision History**

| Version | Date           | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | November, 2007 | Production Release, Silicon Revision AA.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1     | April, 2009    | Production update, Silicon Revision AA.<br>Reorganized chapter sequence, omitted the Software Architecture chapter,<br>and renumbered all chapters accordingly.<br>Changed register offsets 208h and 20Ch to <i>Factory Test Only</i> .<br>Replaced mechanical drawing (updated Table 16-2 and Figure 16-1), and omitted<br>references to heat spreader.<br>Applied miscellaneous corrections, changes, and enhancements throughout data book. |

#### **Copyright Information**

Copyright © 2007 - 2009 PLX Technology, Inc. All Rights Reserved. The information in this document is proprietary and confidential to PLX Technology. No part of this document may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from PLX Technology.

PLX Technology provides this documentation without warranty, term or condition of any kind, either express or implied, including, but not limited to, express and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and no representations or warranties of accuracy or completeness are made. In no event will PLX Technology be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. PLX Technology may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

PLX Technology retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. PLX Technology assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX Technology products.

PLX Technology and the PLX logo are registered trademarks and ExpressLane is a trademark of PLX Technology, Inc.

PCI Express is a trademark of the PCI Special Interest Group (PCI-SIG).

EUI-64 is a trademark of The Institute of Electrical and Electronics Engineers, Inc. (IEEE)

All product names are trademarks, registered trademarks, or service marks of their respective owners.

Document Number: 8509-AA-SIL-DB-P1-1.1

#### Preface

The information in this data book is subject to change without notice. This PLX data book to be updated periodically as new information is made available.

#### Audience

This data book provides functional details of PLX Technology's ExpressLane PEX 8509-AA 8-Lane/ 8-Port PCI Express Gen 1 Switch, for hardware designers and software/firmware engineers.

#### **Supplemental Documentation**

This data book assumes that the reader is familiar with the following documents:

• PLX Technology, Inc. (PLX)

870 W Maude Avenue, Sunnyvale, CA 94085 USA

Tel: 800 759-3735 (domestic only) or 408 774-9060, Fax: 408 774-2169, <u>www.plxtech.com</u>

The <u>PLX PEX 8509 Toolbox</u> includes this data book, as well as other PEX 8509 documentation, including the Errata.

PCI Special Interest Group (PCI-SIG)

3855 SW 153rd Drive, Beaverton, OR 97006 USA

Tel: 503 619-0569, Fax: 503 644-6708, www.pcisig.com

- PCI Local Bus Specification, Revision 3.0

- PCI Bus Power Management Interface Specification, Revision 1.2

- PCI to PCI Bridge Architecture Specification, Revision 1.2

- PCI Express Base Specification, Revision 1.1

- PCI Express Card Electromechanical Specification, Revision 1.0a

- <u>– PCI Express Architecture PCI Express Jitter and BER White Paper, Revision 1.0</u>

- The Institute of Electrical and Electronics Engineers, Inc. (IEEE)

445 Hoes Lane, Piscataway, NJ 08854-4141 USA

Tel: 800 701-4333 (domestic only) or 732 981-0060, Fax: 732 981-9667, www.ieee.org

- IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture, 1990

- IEEE Standard 1149.1a-1993, IEEE Standard Test Access Port and Boundary-Scan Architecture

- IEEE Standard 1149.1-1994, Specifications for Vendor-Specific Extensions

- IEEE Standard 1149.6-2003, IEEE Standard Test Access Port and Boundary-Scan Architecture Extensions

- NXP Semiconductors

www.standardics.nxp.com

<u>– The I2C-Bus Specification, Version 2.1</u>

| Abbreviation              | Document                                                                 |

|---------------------------|--------------------------------------------------------------------------|

| PCI r3.0                  | PCI Local Bus Specification, Revision 3.0                                |

| PCI Power Mgmt. r1.2      | PCI Bus Power Management Interface Specification, Revision 1.2           |

| PCI-to-PCI Bridge r1.2    | PCI to PCI Bridge Architecture Specification, Revision 1.2               |

| PCI Express Base r1.1     | PCI Express Base Specification, Revision 1.1                             |

| PCI ExpressCard CEM r1.1  | PCI Express Card Electromechanical Specification, Revision 1.1           |

| IEEE Standard 1149.1-1990 | IEEE Standard Test Access Port and Boundary-Scan Architecture            |

| IEEE Standard 1149.6-2003 | IEEE Standard Test Access Port and Boundary-Scan Architecture Extensions |

| $I^2C$ Bus v2.1           |                                                                          |

| $I2C Bus v2.1^a$          | The $I^2C$ -Bus Specification, Version 2.1                               |

*Note:* In this data book, shortened titles are associated with the previously listed documents. The following table lists these abbreviations.

a. Due to formatting limitations, the specification name may appear without the superscripted "2" in its title.

#### **Terms and Abbreviations**

The following table lists common terms and abbreviations used in this data book. Terms and abbreviations defined in the *PCI Express Base r1.1* are not included in this table.

| Terms and<br>Abbreviations | Definitions                                                                                                                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMCAM                      | Address mapping CAM that determines a memory Request route. Contains mirror copies of the PCI-to-PCI bridge <b>Memory Base</b> and <b>Limit</b> registers in the switch.                            |

| BAR                        | Base Address register.                                                                                                                                                                              |

| BusNoCAM                   | Bus Number mapping CAM that determines the completion route. Contains mirror copies of the PCI-to-PCI bridge <b>Secondary Bus Number</b> and <b>Subordinate Bus Number</b> registers in the switch. |

| САМ                        | Content Addressable Memory.                                                                                                                                                                         |

| CSRs                       | Configuration Space registers.                                                                                                                                                                      |

| Downstream<br>Station      | A station that contains only downstream ports.                                                                                                                                                      |

| ECC                        | Error-Correcting Code.                                                                                                                                                                              |

| GPIO                       | General-Purpose Input/Output.                                                                                                                                                                       |

| GPU                        | Graphics Processing Unit.                                                                                                                                                                           |

| IOAMCAM                    | I/O Address mapping CAM that determines an I/O Request route. Contains mirror copies of the PCI-to-PCI bridge <b>I/O Base</b> and <b>Limit</b> registers in the switch.                             |

| Lane                       | A bidirectional pair of differential PCI Express I/O signals.                                                                                                                                       |

| Local                      | Reference to PCI Express attributes (such as, credits) that belong to the PCI Express station.                                                                                                      |

| LTSSM                      | Link Training and Status State Machine.                                                                                                                                                             |

| Terms and<br>Abbreviations | Definitions                                                                                                                                                                                                                                                            |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

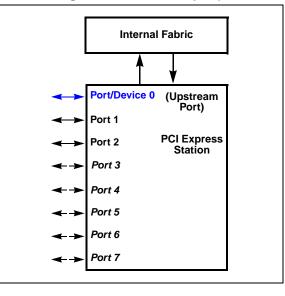

| PCI Express<br>Station     | A functional unit that provides the PCI Express conforming system interface. Includes the Serializer and De-serializer (SerDes) hardware interface modules and PCI Express interface, which provides the Physical Layer, Data Link Layer, and Transaction Layer logic. |

| PEX                        | PCI Express.                                                                                                                                                                                                                                                           |

| РНҮ                        | Physical Layer.                                                                                                                                                                                                                                                        |

| Port                       | Ports are a collection of lanes configured at startup which contain the functional logic and memory resources to communicate with like resources in other PCI Express devices.                                                                                         |

| PRBS                       | Pseudo-Random Bit Sequence.                                                                                                                                                                                                                                            |

| QoS                        | Quality of Service.                                                                                                                                                                                                                                                    |

| RoHS                       | Restrictions on the use of certain Hazardous Substances (RoHS) Directive.                                                                                                                                                                                              |

| RAS                        | Reliability, Availability, and Serviceability.                                                                                                                                                                                                                         |

| RM                         | Read Margin.                                                                                                                                                                                                                                                           |

| RR                         | Round-Robin scheduling.                                                                                                                                                                                                                                                |

| SerDes                     | Serializer and De-serializer. A high-speed differential-signaling parallel-to-serial and serial-to-parallel conversion logic attached to lane pads.                                                                                                                    |

| TC                         | Traffic Class.                                                                                                                                                                                                                                                         |

| TDM                        | Time Division Multiplexing.                                                                                                                                                                                                                                            |

| TLC                        | Transaction Layer Control. The module performing PCI Express Transaction Layer functions.                                                                                                                                                                              |

| TLP                        | Transaction Layer Packet. PCI Express packet formation and organization.                                                                                                                                                                                               |

| Upstream station           | Upstream station. Contains the component's upstream port. An upstream station might contain downstream ports.                                                                                                                                                          |

| UTP                        | User Test Pattern.                                                                                                                                                                                                                                                     |

| VC                         | Virtual Channel.                                                                                                                                                                                                                                                       |

| WRR                        | Weighted Round-Robin scheduling.                                                                                                                                                                                                                                       |

#### **Data Book Notations and Conventions**

| Notation / Convention      | Description                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blue text                  | Indicates that the text is hyperlinked to its description elsewhere in the data book. Left-click the blue text to learn more about the hyperlinked information. This format is often used for register names, register bit and field names, register offsets, chapter and section titles, figures, and tables.                                                                |

| PEX_XXXn[x]<br>PEX_XXXp[x] | When the signal name appears in all CAPS, with the primary Port description listed first, field $[x]$ indicates the number associated with the signal balls/pads assigned to a specific SerDes module/Lane. The lowercase "n" (negative) or "p" (positive) suffix indicates the differential pair of signals, which are always used together.                                 |

| # = Active-Low signals     | Unless specified otherwise, Active-Low signals are identified by a "#" appended to the term ( <i>for example</i> , PEX_PERST#).                                                                                                                                                                                                                                               |

| Program/code samples       | Monospace font ( <i>program or code samples</i> ) is used to identify code samples or programming references. These code samples are case-sensitive, unless specified otherwise.                                                                                                                                                                                              |

| command_done               | Interrupt format.                                                                                                                                                                                                                                                                                                                                                             |

| Command/Status             | Register names.                                                                                                                                                                                                                                                                                                                                                               |

| Parity Error Detected      | Register parameter [field] or control function.                                                                                                                                                                                                                                                                                                                               |

| Upper Base Address[31:16]  | Specific Function in 32-bit register bounded by bits [31:16].                                                                                                                                                                                                                                                                                                                 |

| Number multipliers         | $\begin{aligned} k &= 1,000 \ (10^3) \text{ is generally used with frequency response.} \\ K &= 1,024 \ (2^{10}) \text{ is used for memory size references.} \\ KB &= 1,024 \text{ bytes.} \\ M &= \text{meg.} \\ &= 1,000,000 \text{ when referring to frequency (decimal notation)} \\ &= 1,048,576 \text{ when referring to memory sizes (binary notation)} \end{aligned}$ |

| 1Fh                        | h = suffix which identifies hex values.<br>Each prefix term is equivalent to a 4-bit binary value (nibble).<br>Legal prefix terms are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F.                                                                                                                                                                                         |

| 1010b                      | b = suffix which identifies binary notation ( <i>for example</i> , 01b, 010b, 1010b, and so forth). Not used with single-digit values of 0 or 1.                                                                                                                                                                                                                              |

| 0 through 9                | Decimal numbers, or single binary numbers.                                                                                                                                                                                                                                                                                                                                    |

| byte                       | Eight bits – abbreviated to "B" (for example, $4B = 4$ bytes)                                                                                                                                                                                                                                                                                                                 |

| LSB                        | Least-Significant Byte.                                                                                                                                                                                                                                                                                                                                                       |

| lsb                        | Least-significant bit.                                                                                                                                                                                                                                                                                                                                                        |

| MSB                        | Most-Significant Byte.                                                                                                                                                                                                                                                                                                                                                        |

| msb                        | Most-significant bit.                                                                                                                                                                                                                                                                                                                                                         |

| DWord                      | Double-Word (32 bits) is the primary register size in these devices.                                                                                                                                                                                                                                                                                                          |

| QWord                      | Quad-Word (64 bits).                                                                                                                                                                                                                                                                                                                                                          |

| Reserved                   | Do not modify <i>Reserved</i> bits and words. Unless specified otherwise, these bits read as 0 and must be written as 0.                                                                                                                                                                                                                                                      |

# Contents

| Chapter 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|           | 1.1         Features         7           1.2         Overview         7         7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | С                           |

| Chapter 2 | Features and Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                           |

|           | 2.1 Flexible and Feature-Rich 8-Lane/8-Port Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

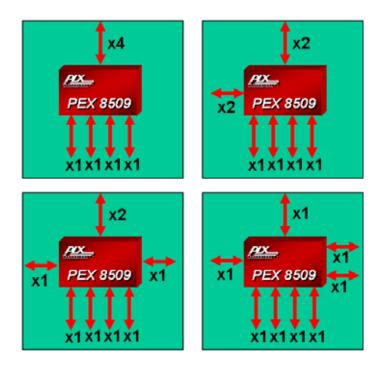

|           | 2.1.1 Highly Flexible Port Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |

|           | 2.1.2 High Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |

|           | 2.1.3 End-to-End Packet Integrity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |

|           | 2.1.4 Configuration Flexibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |

|           | 2.1.5 Interoperability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |

|           | 2.1.6 Low Power with Granular SerDes Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             |

|           | 2.1.7 Flexible Port-Width Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |

|           | 2.1.8 Hot Plug for High Availability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                             |

|           | 2.1.9 Dynamic Lane Reversal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |

|           | 2.1.10 Fully Compliant Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |

|           | 2.2 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             |

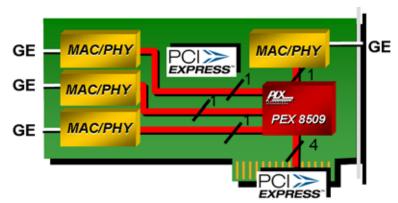

|           | 2.2.1 Adapter Board Aggregation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |

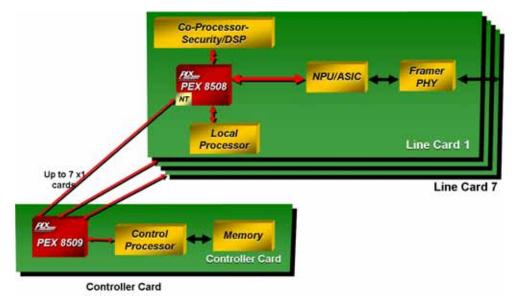

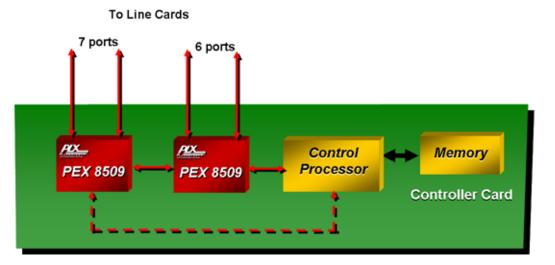

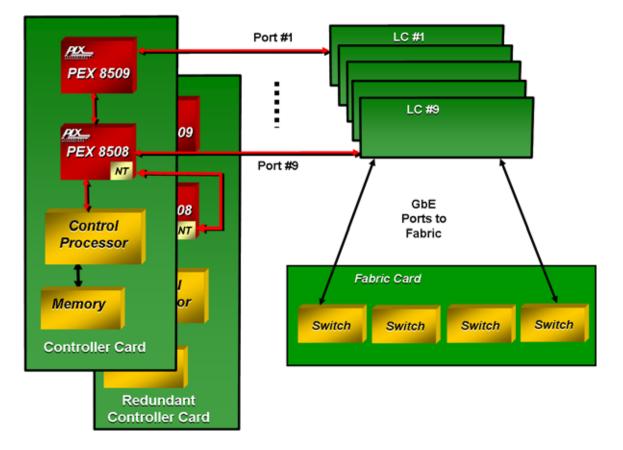

|           | 2.2.2 Control Plane Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             |

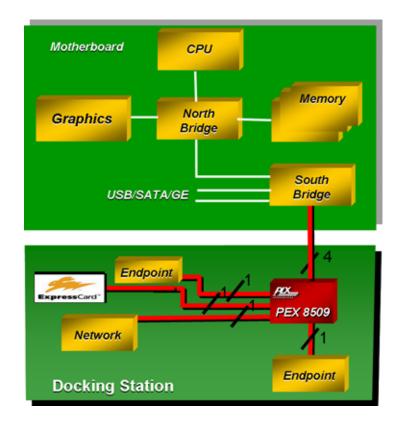

|           | 2.2.3 Docking Station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |

|           | 2.3 Software Usage Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                             |

|           | 2.3.1 System Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |

|           | 2.3.2 Interrupt Sources and Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |

| Chapter 3 | Signal Ball Description 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                           |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ~                           |

|           | 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3                           |

|           | 3.1         Introduction         13           3.2         Abbreviations         13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                           |

|           | 3.2 Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3<br>4                      |

|           | 3.2    Abbreviations    13      3.3    Internal Pull-Up Resistors    14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3<br>4<br>4                 |

|           | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3<br>4<br>5                 |

|           | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3<br>4<br>5<br>6            |

|           | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3<br>4<br>5<br>6<br>0       |

|           | 3.2 Abbreviations       12         3.3 Internal Pull-Up Resistors       14         3.4 Signal Ball Descriptions       14         3.4.1 PCI Express Signals       14         3.4.2 Hot Plug Signals       16         3.4.3 Serial EEPROM Signals       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3<br>4<br>5<br>6<br>1       |

|           | 3.2Abbreviations133.3Internal Pull-Up Resistors143.4Signal Ball Descriptions143.4.1PCI Express Signals143.4.2Hot Plug Signals163.4.3Serial EEPROM Signals203.4.4Strapping Signals213.4.5JTAG Interface Signals22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3<br>4<br>5<br>6<br>1<br>2  |

|           | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       16         3.4.3       Serial EEPROM Signals       20         3.4.4       Strapping Signals       21         3.4.5       JTAG Interface Signals       22                                                                                                                                                                                                                                                                                                                                                                                                                                          | 344560123                   |

|           | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       14         3.4.3       Serial EEPROM Signals       16         3.4.4       Strapping Signals       20         3.4.5       JTAG Interface Signals       22         3.4.6       I <sup>2</sup> C Slave Interface Signals       22                                                                                                                                                                                                                                                                                                                                                                    | 3445601233                  |

|           | 3.2       Abbreviations       12         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       16         3.4.3       Serial EEPROM Signals       16         3.4.4       Strapping Signals       20         3.4.5       JTAG Interface Signals       21         3.4.6       I <sup>2</sup> C Slave Interface Signals       22         3.4.7       Device-Specific Signals       22         3.4.8       No Connect Signals       22                                                                                                                                                                                                                                                               | 34456012335                 |

|           | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       14         3.4.3       Serial EEPROM Signals       16         3.4.4       Strapping Signals       20         3.4.5       JTAG Interface Signals       22         3.4.6       I <sup>2</sup> C Slave Interface Signals       22         3.4.7       Device-Specific Signals       22                                                                                                                                                                                                                                                                                                               | 344560123356                |

|           | 3.2       Abbreviations       12         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       16         3.4.3       Serial EEPROM Signals       20         3.4.4       Strapping Signals       20         3.4.5       JTAG Interface Signals       21         3.4.6       I <sup>2</sup> C Slave Interface Signals       22         3.4.7       Device-Specific Signals       22         3.4.8       No Connect Signals       22         3.4.9       Power and Ground Signals       24                                                                                                                                                                                                         | 3445601233567               |

| Chapter 4 | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       14         3.4.3       Serial EEPROM Signals       16         3.4.4       Strapping Signals       20         3.4.5       JTAG Interface Signals       22         3.4.6       I²C Slave Interface Signals       22         3.4.7       Device-Specific Signals       22         3.4.8       No Connect Signals       23         3.4.9       Power and Ground Signals       26         3.5       Ball Assignments by Location       27                                                                                                                                                              | 34456012335673              |

| Chapter 4 | 3.2Abbreviations133.3Internal Pull-Up Resistors143.4Signal Ball Descriptions143.4.1PCI Express Signals143.4.2Hot Plug Signals163.4.3Serial EEPROM Signals203.4.4Strapping Signals213.4.5JTAG Interface Signals223.4.6I²C Slave Interface Signals223.4.7Device-Specific Signals223.4.8No Connect Signals223.4.9Power and Ground Signals223.5Ball Assignments by Location223.6Physical Layout33                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34456012335673 5            |

| Chapter 4 | 3.2Abbreviations133.3Internal Pull-Up Resistors143.4Signal Ball Descriptions143.4.1PCI Express Signals143.4.2Hot Plug Signals163.4.3Serial EEPROM Signals263.4.4Strapping Signals273.4.5JTAG Interface Signals223.4.6I²C Slave Interface Signals223.4.7Device-Specific Signals223.4.8No Connect Signals223.4.9Power and Ground Signals263.5Ball Assignments by Location273.6Physical Layout33Functional Overview                                                                                                                                                                                                                                                                                                                                                                                                                         | 34456012335673 55           |

| Chapter 4 | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       16         3.4.3       Serial EEPROM Signals       26         3.4.4       Strapping Signals       27         3.4.5       JTAG Interface Signals       27         3.4.6       I <sup>2</sup> C Slave Interface Signals       27         3.4.7       Device-Specific Signals       27         3.4.8       No Connect Signals       26         3.4.9       Power and Ground Signals       26         3.5       Ball Assignments by Location       27         3.6       Physical Layout       33         Functional Overview       34       34                                                        | 34456012335673 <b>5</b> 56  |

| Chapter 4 | 3.2       Abbreviations       13         3.3       Internal Pull-Up Resistors       14         3.4       Signal Ball Descriptions       14         3.4.1       PCI Express Signals       14         3.4.2       Hot Plug Signals       14         3.4.3       Serial EEPROM Signals       16         3.4.4       Strapping Signals       26         3.4.5       JTAG Interface Signals       27         3.4.6       I <sup>2</sup> C Slave Interface Signals       22         3.4.6       I <sup>2</sup> C Slave Interface Signals       22         3.4.8       No Connect Signals       22         3.4.9       Power and Ground Signals       26         3.5       Ball Assignments by Location       22         3.6       Physical Layout       33         Functional Overview         4.1       Ingress and Egress Functions       36 | 34456012335673 <b>5</b> 566 |

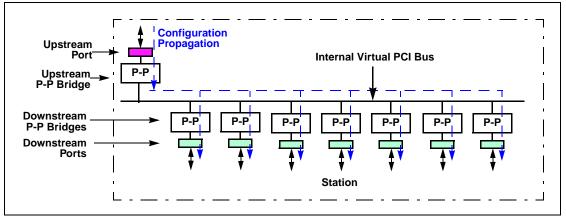

|           | 4.2 PCI-Compatible Software Model                                                               | 39  |

|-----------|-------------------------------------------------------------------------------------------------|-----|

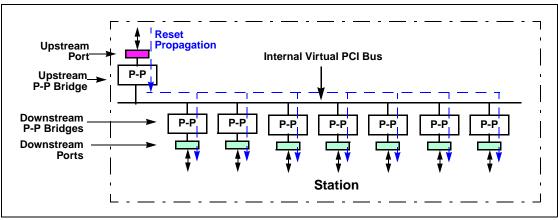

|           | 4.2.1 System Reset                                                                              |     |

|           | 4.2.2 Interrupts                                                                                |     |

|           | 4.2.2.1 Interrupt Sources or Events                                                             |     |

|           | 4.2.2.2 INTx Switch Mapping                                                                     |     |

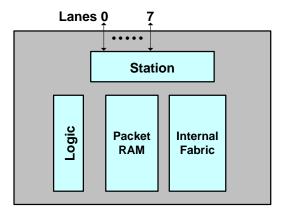

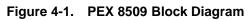

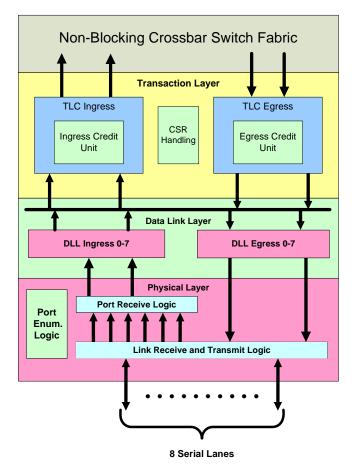

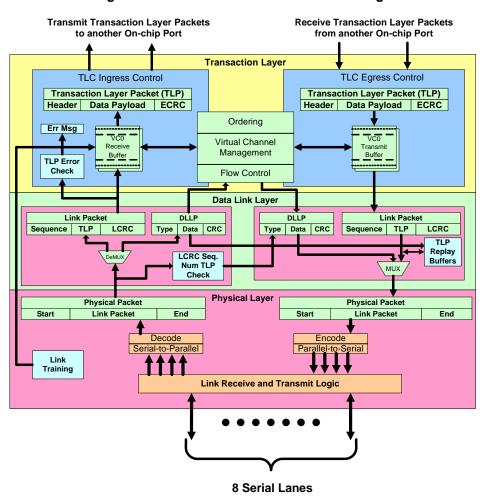

|           | 4.3 PCI Express Station Functional Description                                                  |     |

|           | 4.3.1 Functional Blocks                                                                         |     |

|           | 4.3.1.1       Physical Layer         4.3.1.2       Data Link Layer                              |     |

|           | 4.3.1.2 Data Link Layer                                                                         |     |

|           | 4.3.1.4 Non-Blocking Crossbar Switch Architecture                                               |     |

|           | 4.3.2 Cut-Thru Mode                                                                             |     |

|           |                                                                                                 | ••• |

| Chapter 5 | Reset and Initialization                                                                        | .45 |

|           | 5.1 Reset Overview                                                                              | 45  |

|           | 5.1.1 Cold Reset                                                                                | 45  |

|           | 5.1.2 Warm Reset                                                                                |     |

|           | 5.1.3 Hot Reset                                                                                 |     |

|           | 5.1.3.1 Hot Reset Propagation                                                                   |     |

|           | 5.1.3.2 Hot Reset Disable                                                                       |     |

|           | 5.1.4 Secondary Bus Reset                                                                       |     |

|           | 5.2 Initialization Procedure                                                                    |     |

|           | 5.2.1 Default Port Configuration                                                                |     |

|           | 5.2.2 Default Register Initialization                                                           |     |

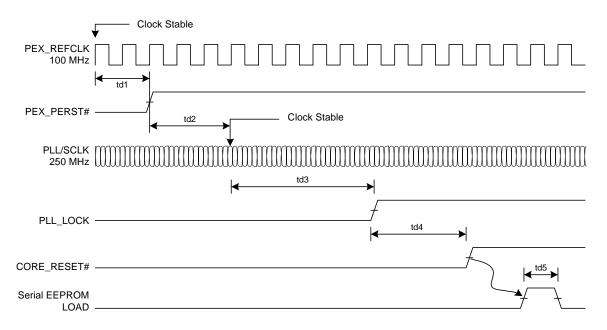

|           | 5.2.3       Device-Specific Registers         5.2.4       Reset and Clock Initialization Timing |     |

|           | 5.2.4 Reset and Clock Initialization Timing                                                     |     |

|           | 5.2.4.2 $I^2C$ Load Time                                                                        |     |

|           |                                                                                                 | 01  |

| Chapter 6 | Serial EEPROM Controller                                                                        | .53 |

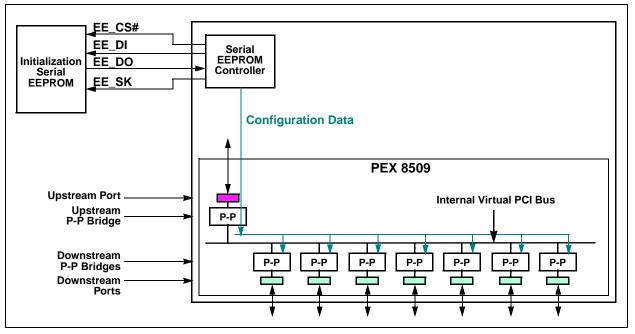

|           | 6.1 Overview                                                                                    | 53  |

|           | 6.2 Serial EEPROM Data Format                                                                   | 55  |

|           | 6.3 Serial EEPROM Initialization                                                                |     |

|           | 6.4 PCI Express Configuration, Control, and Status Registers                                    |     |

|           | 6.5 Serial EEPROM Registers                                                                     |     |

|           | 6.6 Serial EEPROM Random Write/Read Access                                                      |     |

|           | 6.6.1 Writing to Serial EEPROM                                                                  |     |

|           | 6.6.2 Reading from Serial EEPROM                                                                | 59  |

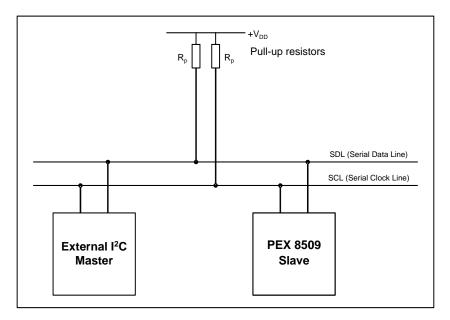

| Chapter 7 | I <sup>2</sup> C Slave Interface Operation                                                      | 61  |

|           | 7.1 Introduction                                                                                |     |

|           | 7.2 I <sup>2</sup> C Support Overview                                                           |     |

|           | 7.3 I <sup>2</sup> C Addressing – Slave Mode Access                                             |     |

|           | 7.4 Command Phase Format                                                                        |     |

|           | 7.5 I <sup>2</sup> C Interface Register                                                         | 64  |

|           | 7.6 I <sup>2</sup> C Register Write Access                                                      | 64  |

|           | 7.6.1 Register Write                                                                            |     |

|           | 7.7 I <sup>2</sup> C Register Read Access                                                       |     |

|           | 7.7.1 Register Read Address Phase and Command Packet                                            |     |

|           | 7.7.2 Register Read Data Packet                                                                 | 71  |

| Chapter 8  | Performance Metrics                                                     | . 73 |

|------------|-------------------------------------------------------------------------|------|

|            | 8.1 Introduction                                                        | . 73 |

|            | 8.2 Throughput                                                          | . 73 |

|            | 8.2.1 Shared Wire                                                       |      |

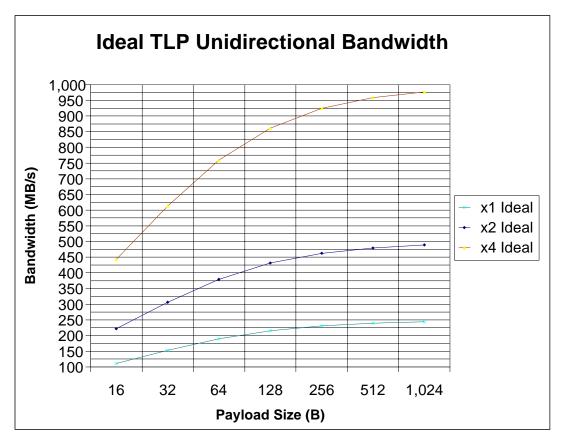

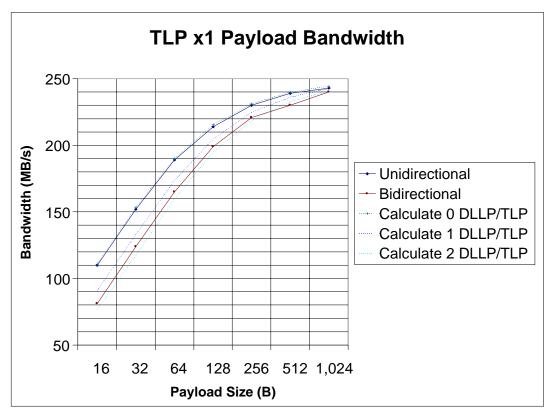

|            | 8.2.2 Unidirectional Throughput                                         |      |

|            | 8.2.3 Ideal PCI Express Throughput                                      |      |

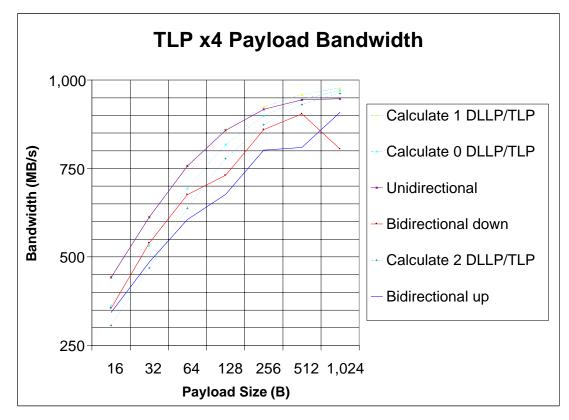

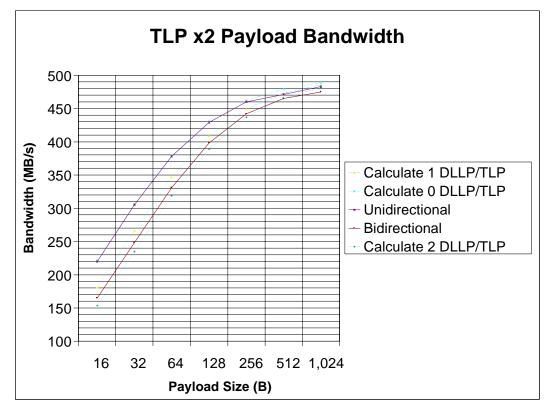

|            | 8.2.4 Bidirectional PCI Express Throughput                              |      |

|            | 8.3 DLLP Policies                                                       |      |

|            | 8.3.1 ACK DLLP Policy                                                   |      |

|            | 8.3.2 UpdateFC DLLP Policy                                              |      |

|            | 8.3.3 Unidirectional DLLP Policies                                      |      |

|            | 8.4 Adjusting Ingress Resources                                         |      |

|            | 8.4.1 Initial Credit Allocation                                         |      |

|            | 8.4.2 Common Credit Pool                                                |      |

|            | 8.4.3 Wait for ACK                                                      |      |

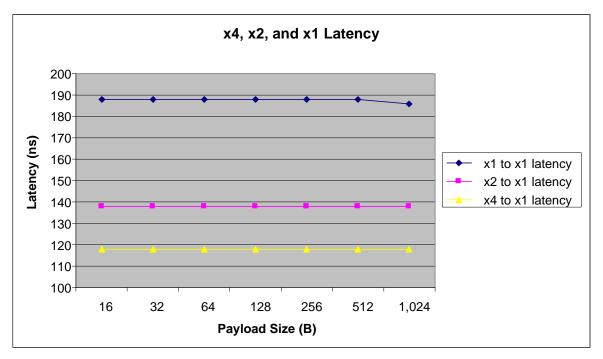

|            | 8.5 Latency                                                             |      |

|            | 8.5.1 Host-Centric Latency                                              |      |

|            | 8.5.2 Peer-to-Peer Latency                                              |      |

|            | 8.5.3 Other Latency Measurements                                        |      |

|            | 8.6 Queuing Options                                                     |      |

|            | 8.6.1 Destination Queue                                                 |      |

|            | 8.6.2 Source Queue                                                      | . 89 |

| Chapter 0  | Device Levere                                                           | 01   |

| Chapter 9  | Device Layers                                                           |      |

|            | 9.1 Data Flow Through                                                   |      |

|            | 9.2 Physical Layer                                                      |      |

|            | 9.2.1 PHY Status and Command Registers                                  |      |

|            | 9.2.2 Hardware Link Interface Configuration         9.3 Data Link Layer |      |

|            | 9.3.1 Data Link Layer Packet                                            |      |

|            | 9.3.1.1 DLLP Ingress                                                    |      |

|            | 9.3.1.2 DLLP Egress                                                     |      |

|            | 9.3.2 Packet Arbiter                                                    |      |

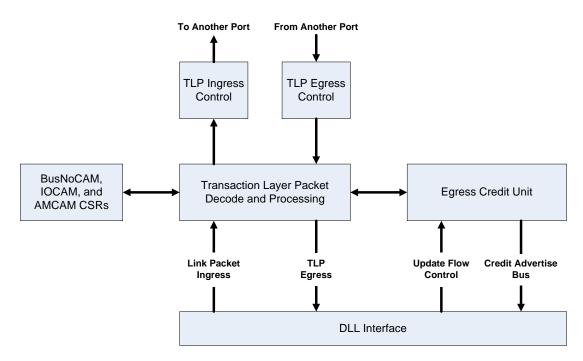

|            | 9.4 Transaction Layer                                                   |      |

|            | 9.4.1 Virtual Channel and Traffic Classes                               |      |

|            | 9.4.2 TL Transmit/Egress Protocol                                       |      |

|            | 9.4.2.1 Headers                                                         |      |

|            | 9.4.2.2 Data Payloads                                                   |      |

|            | 9.4.2.3 End-to-End Cyclic Redundancy Check                              |      |

|            | 9.4.3 TL Receive/Ingress Protocol                                       |      |

|            | 9.4.4 Flow Control Protocol                                             |      |

|            |                                                                         | 100  |

| Chapter 10 | Interrupts                                                              | 101  |

|            | 10.1 Interrupt Support                                                  |      |

|            | 10.1.1 Interrupt Handling                                               |      |

|            | 10.2 INTx Emulation Support                                             |      |

|            | 10.2.1 INTx-Type Interrupt Message Remapping and Collapsing             |      |

|            | 10.3 Message Signaled Interrupt Support                                 |      |

|            | 10.3.1 MSI Operation                                                    |      |

|            | 10.3.2 MSI Capability Registers                                         |      |

|            | 10.4 PEX_INTA# Interrupts                                               |      |

| Chapter 11 | Hot Plug Support         11.1       Hot Plug Purpose and Capability         11.1.1       Hot Plug Controller Capabilities         11.1.2       Hot Plug Port External Signals         11.1.3       Hot Plug Output Signal States for Disabled Hot Plug Slots         11.2       PCI Express Capability Registers for Hot Plug         11.3       Hot Plug Interrupts         11.4       Hot Plug Controller Slot Power-Up/Down Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 105<br>105<br>105<br>105<br>106<br>106                                                                                                                                                                                                                                                      |