## Datasheet

### AS1372 350mA Dual Rail Linear Regulator

### **1** General Description

The AS1372 is a Dual Supply Rail Linear Regulator designed for providing ultra-low voltages.

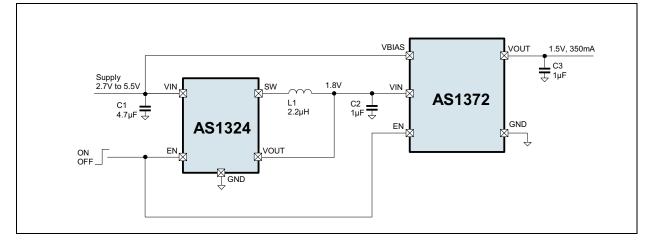

In a typical application the battery is directly connected to VBIAS and VIN is connected to the output of a DC-DC Converter.

The very low quiescent currents together with the excellent transient features and the superior dropout are making the AS1372 an ideal device for applications running on batteries.

The robust design ensures that no under-voltage failure can occur and the device is also equipped with an internal protection against over-temperature and overcurrent.

The device is available in fixed output voltages from 0.5V up to 2.2V in 100mV steps (50mV from 0.5V to 1.1V).

The AS1372 is available in a 5-bumps CS-WLP package and is qualified for -40 $^{\circ}$ C to +85 $^{\circ}$ C operation.

### 2 Key Features

- Input Voltage: 0.7V to 4.5V

- Bias Supply Voltage: 2.5V to 5.5V

- Output Voltage: 0.5V to 2.2V in 100mV steps

- Output Voltage Accuracy: ±1.5%

- Dropout Voltage 135mV @ 350mA load

- Max. Output Current: 350mA

- Load Transient Response: ±15mV (typ.)

- Superior Efficiency

- Low Shutdown Current: 10nA

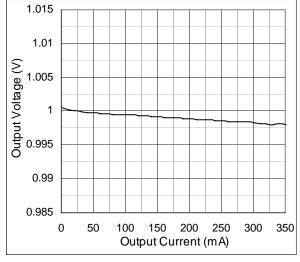

- High PSRR: >80dB @ 10Hz-1kHz, 60db @100kHz

- Noise Voltage: 50µV<sub>RMS</sub> from 10Hz to 1000kHz

- Integrated Overtemperature/Overcurrent Protection

- Chip Enable Input

- Operating Temperature Range: -40°C to +85°C

- 5-bumps CS-WLP Package

### **3** Applications

The devices are ideal for powering cordless and mobile phones, MP3 players, PDAs, hand-held computers, digital cameras, and any other hand-held and/or battery-powered device.

Figure 1. AS1372 - Typical Application Diagram

# **4** Pin Assignments

Figure 2. Pin Assignments (Top View)

### **Pin Descriptions**

Table 1. Pin Descriptions

| Pin Number | Pin Name | Description                                                                                                                 |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------|

| 1          | VOUT     | Regulated Output Voltage. Bypass this pin with a capacitor to GND.                                                          |

| 2          | GND      | Ground.                                                                                                                     |

| 3          | EN       | <b>Enable.</b> Pull this pin to low to disable the device. This pin has an internal $1.6M\Omega$ (typ.) pull-down resistor. |

| 4          | VBIAS    | Bias Supply Voltage. 2.5V to 5.5V, Bypass this pin with a capacitor to GND.                                                 |

| 5          | VIN      | <b>Unregulated Input Voltage</b> . 0.7V to 4.5V, VIN $\leq$ VBIAS, Bypass this pin with a capacitor to GND.                 |

# **5** Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                     | Min  | Max        | Units | Notes                                                                                                                                                                                                                                                                                                           |

|-------------------------------|------|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN, VBIAS and EN to GND      | -0.3 | +6.5       | V     | VIN < VBIAS or equal in operating<br>conditions                                                                                                                                                                                                                                                                 |

| VOUT to GND                   | -0.3 | VIN + 0.3  | V     |                                                                                                                                                                                                                                                                                                                 |

| Output Short-Circuit Duration |      | Indefinite |       |                                                                                                                                                                                                                                                                                                                 |

| ESD                           |      | 2          | kV    | HBM MIL-Std. 883E 3015.7 methods                                                                                                                                                                                                                                                                                |

| Latch-Up                      | -100 | +100       | mA    | JEDEC 78                                                                                                                                                                                                                                                                                                        |

| Operating Temperature Range   | -40  | +85        | °C    |                                                                                                                                                                                                                                                                                                                 |

| Storage Temperature Range     | -65  | +150       | °C    |                                                                                                                                                                                                                                                                                                                 |

| Junction Temperature          |      | +125       | °C    |                                                                                                                                                                                                                                                                                                                 |

| Package Body Temperature      | +260 |            | ٥C    | The reflow peak soldering temperature<br>(body temperature) specified is in<br>accordance with <i>IPC/JEDEC J-STD-</i><br>020D "Moisture/Reflow Sensitivity<br>Classification for Non-Hermetic Solid<br>State Surface Mount Devices".<br>The lead finish for Pb-free leaded<br>packages is matte tin (100% Sn). |

Table 2. Absolute Maximum Ratings

## **6 Electrical Characteristics**

$V_{IN} = V_{OUT} + 0.2V$ ,  $V_{BIAS} = V_{OUT} + 1.5V$  (or 2.5V whichever is larger),  $EN = V_{BIAS}$ ,  $C_{IN} = C_{OUT} = C_{BIAS} = 1\mu$ F,  $T_{AMB} = -40^{\circ}$ C to +85°C, Typical Values are at  $T_{AMB} = +25^{\circ}$ C (unless otherwise specified).

Table 3. Electrical Characteristics

| Symbol                       | Parameter                                            | Conditions                                                                                      | Min  | Тур | Max  | Units             |  |

|------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|-----|------|-------------------|--|

| Vin                          | Input Voltage                                        | $V \text{IN} \leq V \text{BIAS}$                                                                | 0.7  |     | 4.5  | V                 |  |

| VBIAS                        | Bias Supply Voltage                                  |                                                                                                 | 2.5  |     | 5.5  | V                 |  |

| Vout                         | Output Voltage                                       | Available in 50mV or 100mV steps<br>(see Ordering Information on page<br>13)                    | 0.5  |     | 2.2  | v                 |  |

| Vout(nom)                    |                                                      | Ιουτ = 100μΑ                                                                                    | -1.5 |     | +1.5 | %                 |  |

|                              | Output Voltage Accuracy<br>Vout > 1.2V               | IOUT = 100μA to 350mA, VIN =<br>VOUT(NOM)+0.2V to 4.5V, VBIAS =<br>VOUT(NOM)+1.5V to 5.5V       | -2   |     | +2   |                   |  |

| - Vout                       |                                                      | Ιουτ = 100μΑ                                                                                    | -2   |     | +2   |                   |  |

|                              | Output Voltage Accuracy<br>Vou⊤ ≤ 1.2V               | IOUT = 100µA to 350mA, VIN =<br>VOUT(NOM)+0.2V to 4.5V, VBIAS =<br>VOUT(NOM)+1.5V to 5.5V       | -2.5 |     | +2.5 | %                 |  |

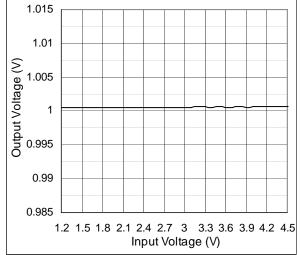

| $\Delta VOUT / \Delta VIN$   | Line Regulation VIN                                  | $V_{IN} = V_{OUT(NOM)} + 0.2V \text{ to } 4.5V,$<br>$V_{BIAS} = 5.5V, \text{ IOUT} = 100 \mu A$ |      | 40  |      | μV/V              |  |

| $\Delta VOUT / \Delta VBIAS$ | Line Regulation VBIAS                                | VBIAS = VOUT(NOM)+1.5V to 5.5V,<br>IOUT = $100\mu A$                                            |      | 100 |      | μV/V              |  |

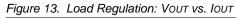

| $\Delta V_{LDR}$             | Load Regulation                                      | IOUT = 1mA to 350mA                                                                             |      | 6   |      | µV/mA             |  |

| Ιουτ                         | Output Current <sup>1</sup>                          |                                                                                                 | 350  |     |      | mA                |  |

| ILIM                         | Current Limit                                        |                                                                                                 |      | 500 |      | mA                |  |

| Vdrop -                      |                                                      | VBIAS = VOUT + 1.5V, IOUT = 350mA                                                               |      | 135 |      | mV                |  |

| VDROF -<br>VIN               | Output Voltage Dropout VIN                           | VBIAS = VOUT + 1.8V, IOUT = 350mA                                                               |      | 115 |      |                   |  |

|                              |                                                      | VBIAS = 5.5V, IOUT = 350mA                                                                      |      | 110 |      |                   |  |

| Vdrop -<br>Vbias             | Output Voltage Dropout VBIAS                         | Iout = 100mA                                                                                    |      | 1.1 | 1.5  | V                 |  |

| E <sub>N</sub>               | Output Voltage Noise                                 | Vout $\leq$ 1.2V, f = 10Hz to 100kHz                                                            |      | 50  |      | μV <sub>RMS</sub> |  |

| PSRR -<br>Vin                |                                                      | f = 100Hz                                                                                       |      | 85  |      | - dB              |  |

|                              | Power-Supply Rejection Ratio                         | f = 1kHz                                                                                        |      | 80  |      |                   |  |

|                              | Sine modulated VIN                                   | f = 10kHz                                                                                       |      | 70  |      |                   |  |

|                              |                                                      | f = 100kHz                                                                                      |      | 60  |      |                   |  |

| PSRR -<br>Vbias              |                                                      | f = 100Hz                                                                                       |      | 75  |      |                   |  |

|                              | Power-Supply Rejection<br>Ratio Sine modulated VBIAS | f = 1kHz                                                                                        |      | 60  |      | dB                |  |

|                              | Ratio one modulated vBIAS                            | f = 10kHz                                                                                       |      | 50  |      |                   |  |

|                              |                                                      | f = 100kHz                                                                                      |      | 50  |      |                   |  |

| IQ_VBIAS                     | Quiescent Current into VBIAS                         |                                                                                                 |      | 40  | 75   |                   |  |

| IQ_VIN                       | Quiescent Current into VIN                           | IOUT = 0mA                                                                                      |      | 6.5 | 10   | - μΑ              |  |

#### Table 3. Electrical Characteristics

| Symbol            | Parameter                          | Conditions                                       | Min | Тур  | Max | Units |  |  |

|-------------------|------------------------------------|--------------------------------------------------|-----|------|-----|-------|--|--|

| Ishdn -<br>Vbias  | Shutdown Current into VBIAS        |                                                  |     | 10   |     | nA    |  |  |

| Ishdn -<br>Vin    | Shutdown Current into VIN          | Ven = 0V                                         |     | 10   |     |       |  |  |

| Logic Leve        | els                                |                                                  |     |      |     |       |  |  |

| Vін               | Enchle Input Threehold             |                                                  | 1   |      |     | V     |  |  |

| VIL               | Enable Input Threshold             |                                                  |     |      | 0.4 | V     |  |  |

| I <sub>EN</sub>   | Enable Input Bias Current          | EN = GND                                         |     | 0.01 |     | nA    |  |  |

| Thermal P         | Thermal Protection                 |                                                  |     |      |     |       |  |  |

| T <sub>SHDN</sub> | Thermal Shutdown<br>Temperature    |                                                  |     | 150  |     | ٥C    |  |  |

| $\Delta T_{SHDN}$ | Thermal Shutdown Hysteresis        |                                                  |     | 25   |     | ٥C    |  |  |

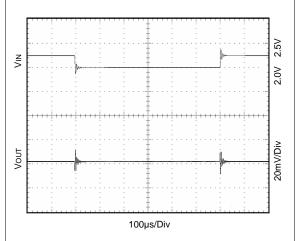

| Transient         | Characteristics                    |                                                  |     |      |     |       |  |  |

| Δνουτ             | Dynamic Load Transient<br>Response | Pulsed ILOAD from 0mA to 300mA in 10µs rise time |     | 15   |     | mV    |  |  |

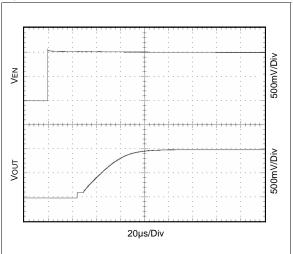

| t <sub>ON</sub>   | Exit Delay from Shutdown           | Vout $\leq$ 1.2V, setting to 95%                 |     | 70   |     | μs    |  |  |

| Соит              | Quitaut Consoltar                  | Load Capacitor Range                             | 1   |      | 10  | μF    |  |  |

|                   | Output Capacitor                   | Maximum ESR Load                                 | 1   |      | 500 | mΩ    |  |  |

1. guaranteed by design

**Note:** All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

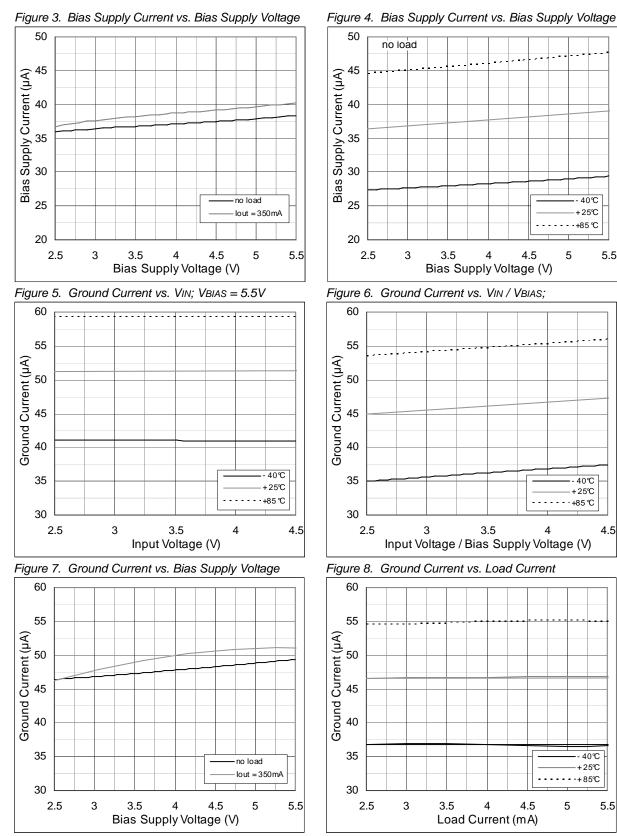

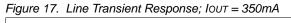

# 7 Typical Operating Characteristics

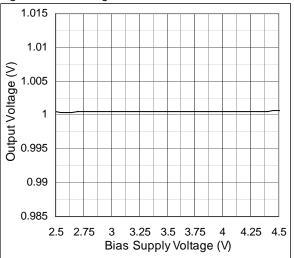

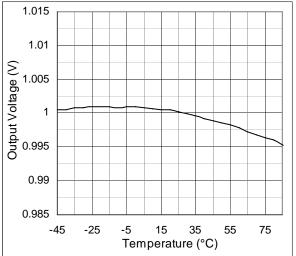

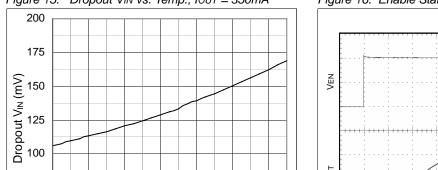

$V_{IN} = 1.2V$ ,  $V_{BIAS} = 2.5V$ ,  $V_{OUT} = 1.0V$ ,  $EN = V_{BIAS}$ ,  $C_{IN} = C_{OUT} = C_{BIAS} = 1\mu$ F,  $T_{AMB} = -40^{\circ}$ C to  $+85^{\circ}$ C, Typical Values are at  $T_{AMB} = +25^{\circ}$ C (unless otherwise specified).

www.austriamicrosystems.com/LDOs/AS1372

Figure 12. Line Regulation: VOUT vs. VBIAS

Figure 14. Output Voltage vs. Temperature; IOUT = 1mA

75

50

-45

-25

35

55

75

Figure 15. Dropout VIN vs. Temp.; IOUT = 350mA

Figure 16. Enable Start-up

15

Temperature (°C)

-5

Figure 18. Load Transient Response; VIN = 2.0V

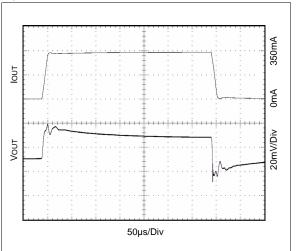

# 8 Detailed Description

The AS1372 is a low-dropout, low-quiescent-current linear regulator intended for LDO regulator applications where output current load requirements range from no load to 350mA. All devices come with fixed output voltage from 0.5V to 2.2V. (see Ordering Information on page 13).

Shutdown current for the whole regulator is typically 10nA. The device features integrated short-circuit and over current protection. Under-Voltage lockout prevents erratic operation when the input voltage is slowly decaying (e.g. in a battery powered application). Thermal Protection shuts down the device when die temperature reaches 150°C. This is a useful protection when the device is under sustained short circuit conditions.

As illustrated in Figure 19, the devices comprise voltage reference, error amplifier, N-channel MOSFET pass transistor, internal voltage divider, current limiter, thermal sensor and shutdown logic.

The bandgap reference is connected to the inverting input of the error amplifier. The error amplifier compares this reference with the feedback voltage and amplifies the difference. If the feedback voltage is lower than the reference voltage, the N-channel MOSFET gate is pulled higher, allowing more current to pass to the output, and increases the output voltage. If the feedback voltage is too high, the pass-transistor gate is pulled down, allowing less current to pass to the output. The output voltage feeds back through an internal resistor voltage divider connected to pin OUT.

Figure 19. AS1372 - Block Diagram

### **Output Voltages**

Standard products are factory-set with output voltages from 0.5V to 2.2V. A two-digit suffix of the part number identifies the nominal output (see Ordering Information on page 13). Non-standard devices are available.

For more information contact: http://www.austriamicrosystems.com/contact

# **9** Application Information

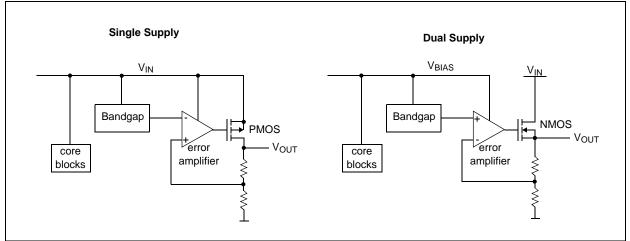

#### Advantages of dual supply architecture vs. traditional single supply approach.

If compared to the traditional single supply approach, the dual rail architecture ensures improved performances in a LDO at the expense of an additional supply voltage and a dedicated pin.

Anyhow, it is worth to note that the additional supply voltage comes for free in all those applications where the LDO is supplied by the output of a DCDC step-down converter: Vin pin is coupled to the step-down output and Vbias is shorted to the DCDC converter supply.

The former is based on a PMOS output transistor connected in a common source configuration: the supply voltage at its source is shared with all the circuit. On the other side, the dual supply approach is based on a NMOS transistor in common drain configuration having its source coincident with the regulated output of the LDO: the supply voltage at the drain is not shared with the remaining blocks of the circuit and its value can be chosen independently.

The second solution allows improved efficiency and dropout at low output reference voltage and faster transient time response.

#### Improved efficiency

At heavy current load the power consumption is almost entirely located in the output transistor. This means that keeping drain to source voltage, that is the difference between input and output voltage of the LDO, as small as possible is the key factor for a good efficiency. It holds, approximately: *Efficiency* = (Vout / Vin)x100 [%]

While this achievement is little challenging in case the output voltage is large enough, traditional implementations based on a PMOS device face a serious bottleneck at low output voltage. In fact the supply voltage cannot be made consequently small because of dynamic range limitations in the core of the LDO circuitry. In many commercial cases the supply voltage cannot be made smaller than 2 or 2,5V which gives only 25% or 20% efficiency for a 500mV reference output.

On the contrary, the possibility to have a dedicated supply voltage for the output transistor offers the possibility to set the drain to source voltage of the output transistor independently from the dynamic range limitations inside the core of the circuit. Thus, even at very small output voltage, the drain to source voltage can be made quite small and guarantee optimal efficiency performance. For instance, by setting Vin at 800mV makes more than 60% efficiency for an output voltage as small as 500mV still ensuring excellent analog performances in the LDO.

#### Improved dropout

Dropout mainly refers to the resistivity of the output transistor when its gate is driven to ground and the feedback regulation loop is open. Moreover when the output transistor is in dropout input and output voltages are nearly coincident. In this way, in a traditional approach, the gate to source voltage that determines the resistivity of the output PMOS in dropout is nearly equal to the output voltage. This means that a smaller output voltage brings worse dropout performances. In the dual supply approach, on the contrary, in dropout conditions the gate of the output transistor is pushed to Vbias voltage and only Vin drops nearly coincident to Vout. As Vbias can be chosen independently from Vin, even at small output voltages a large overdrive at the output transistor can be ensured and an extremely reduced dropout value comes out.

#### Faster response

In a traditional approach, the output of the LDO is coincident with the drain of the output PMOS transistor. In this way, if the load current suddenly changes, any variation at the output voltage is not able to vary the output current of the LDO until it is amplified to the gate of the output PMOS by the error amplifier. A delay comes, unavoidably. On the contrary, in the dual supply approach it is the source of the output transistor to be coincident with the output voltage. In this way a change in the output voltage immediately modulates the current from the LDO and a better regulation in fast load transient is achieved.

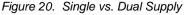

# **10 Package Drawings and Markings**

The device is available in a 5-bumps CS-WLP package.

#### Figure 21. 5-bumps CS-WLP Package

# **11 Ordering Information**

The device is available as the standard products listed in Table 4.

Table 4. Ordering Information

| Ordering Code  | Marking | Output | Description                      | <b>Delivery Form</b> | Package        |

|----------------|---------|--------|----------------------------------|----------------------|----------------|

| AS1372-BWLT-07 | *)      | 0.7V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-10 | ASSN    | 1.0V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-12 | ASSQ    | 1.2V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-13 | ASSO    | 1.3V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-14 | *)      | 1.4V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-15 | ASSR    | 1.5V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-16 | *)      | 1.6V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-18 | ASSS    | 1.8V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-20 | *)      | 2.0V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-24 | *)      | 2.4V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-28 | *)      | 2.8V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-30 | *)      | 3.0V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

| AS1372-BWLT-33 | *)      | 3.3V   | 350mA Dual Rail Linear Regulator | Tape and Reel        | 5-bumps CS-WLP |

\*) on request

Non-standard devices from 0.5V to 1.1V are available in 50mV steps and from 1.1V to 2.2V in 100mV steps. For more information and inquiries contact http://www.austriamicrosystems.com/contact

Note: All products are RoHS compliant and Pb-free.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

For further information and requests, please contact us mailto:sales@austriamicrosystems.com or find your local distributor at http://www.austriamicrosystems.com/distributor

### Copyrights

Copyright © 1997-2010, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

Headquarters

austriamicrosystems AG Tobelbaderstrasse 30 A-8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit: http://www.austriamicrosystems.com/contact