## austriamicrosystems AG

is now

# ams AG

The technical content of this austriamicrosystems datasheet is still valid.

#### **Contact information:**

Headquarters: ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten, Austria Tel: +43 (0) 3136 500 0 e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

## Datasheet

## aleap analog

## AS1334 650mA, Ultra low Ripple Step Down DC/DC Converter

## 1 General Description

The AS1334 is a step-down DC-DC converter designed to power portable applications from a single Li-Ion battery. The device also achieves high-performance in mobile phones and other applications requiring low dropout voltage.

The AS1334 operates from an input voltage range of 2.7 to 5.5V while providing output voltages of 1.2, 1.5, 1.8, 2.5, 3.0 and 3.3V.

Fixed-frequency PWM operation minimizes RF interference. Shutdown function turns the device off and reduces battery consumption to  $0.01\mu A$  (typ).

The AS1334 is available in a TDFN(3x3) 8-pin package. A high switching frequency (2 MHz) allows use of tiny surface-mount components. Only three small external surface-mount components, an inductor and two ceramic capacitors are required.

## 2 Key Features

- Output Voltage Ripple: 2mV

- PWM Switching Frequency: 2MHz

- Single Lithium-Ion Cell Operation

- Output Voltage Range: 1.2V to 3.4V (available in 100mV steps, see Ordering Information on page 17)

- Fixed Output Voltages:

1.2V, 1.5V, 1.8V, 2.5V, 3.0V, 3.3V

- Maximum Load Capability of 650mA

- 97% High Efficiency, 94% Average Efficiency

- Current Overload Protection

- Thermal Overload Protection

- Power-OK

- Soft Start

- Low Dropout Voltage (140 mΩ Typ PFET)

- TDFN(3x3) 8-pin

### 3 Applications

The AS1334 is an ideal solution to supply noise sensitive applications as cellular phones, hand-held radios, RF PC cards, battery powered RF devices, RFID chipsets, A/D Converter, Sensors and OpAmps.

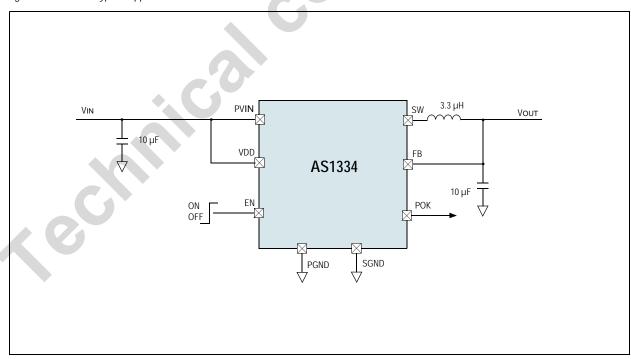

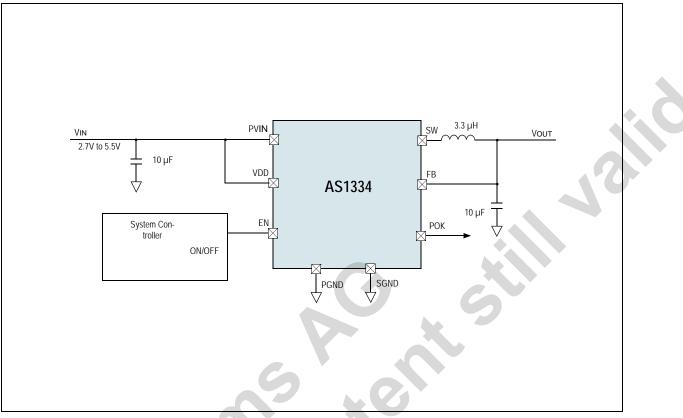

Figure 1. AS1334 - Typical Application Circuit

@analogbench Online Design Tool

## 4 Pin Assignments

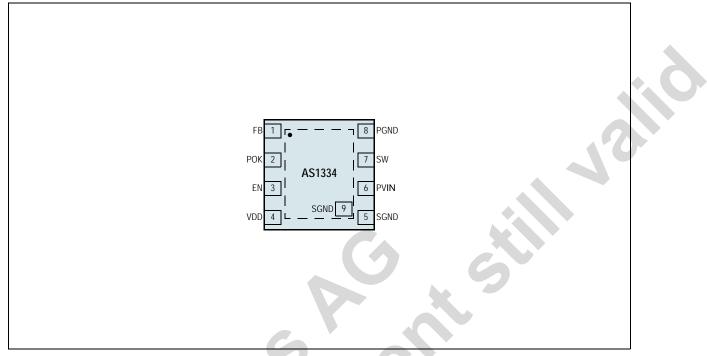

Figure 2. Pin Configuration

#### 4.1 Pin Descriptions

5

Table 1. Pin Descriptions

| Pin Number | Pin Name | Description                                                                                    |

|------------|----------|------------------------------------------------------------------------------------------------|

| 1          | FB       | Feedback Pin. Connect to the output at the output filter capacitor.                            |

|            |          | Power-OK.                                                                                      |

| 2          | POK      | 0 = VOUT < 90% of VOUTNOM.                                                                     |

|            |          | 1 = VOUT > 90% of VOUTNOM.                                                                     |

| 3          | EN       | Enable Input. Set this digital input high for normal operation. For shutdown, set low.         |

| 4          | VDD      | +2.7V to +5.5V Power Supply Voltage. Analog Supply Input.                                      |

| 5, 9       | SGND     | Analog and Control Ground. Connect these pins with low resistance to PGND.                     |

| 6          | PVIN     | +2.7V to +5.5V Power Supply Voltage. Input to the internal PFET switch.                        |

|            |          | Switch Pin. Switch node connection to the internal PFET switch and NFET synchronous rectifier. |

| 7          | SW       | Connect to an inductor with a saturation current rating that exceeds the maximum switch peak   |

|            |          | current limit specification of the AS1334.                                                     |

| 8          | PGND     | Power Ground. Connect this pin with low resistance to SGND.                                    |

## 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

|                                                                                                                                        | Min        | Max          | Units | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ectrical Parameters                                                                                                                    |            |              |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD, PVIN to SGND                                                                                                                      | -0.3       | +7.0         | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PGND to SGND                                                                                                                           | -0.3       | +0.3         | V     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| POK, EN, FB                                                                                                                            | SGND - 0.3 | VDD + 0.3    | V     | 7.01/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SW                                                                                                                                     | PGND - 0.3 | PVIN + 0.3   | V     | - 7.0V max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PVIN to VDD                                                                                                                            | -0.3       | +0.3         | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input Voltage Range                                                                                                                    | 2.7        | 5.5          | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Recommended Load Current                                                                                                               |            | 650          | mA    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Ambient Temperature (T <sub>A</sub> ) Range                                                                                            | -40        | +85          | °C    | In applications where high power dissipation and/<br>or poor package thermal resistance is present,<br>the maximum ambient temperature may have to<br>be derated.<br>Maximum ambient temperature (T <sub>A-MAX</sub> ) is<br>dependent on the maximum operating junction<br>temperature (T <sub>J-MAX-OP</sub> = 125°C), the maximum<br>power dissipation<br>of the device in the application (P <sub>D-MAX</sub> ), and the<br>junction-to ambient thermal resistance of the             |

|                                                                                                                                        |            |              |       | part/package in the application ( $\theta_{JA}$ ), as given by<br>the following<br>equation: T <sub>A-MAX</sub> = T <sub>J-MAX-OP</sub> – ( $\theta_{JA} \times P_{D-MAX}$ ).                                                                                                                                                                                                                                                                                                             |

| ů                                                                                                                                      |            |              |       | part/package in the application ( $\theta_{JA}$ ), as given by<br>the following<br>equation: $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .                                                                                                                                                                                                                                                                                                                                |

| Human Body Model                                                                                                                       |            | 2            | kV    | part/package in the application $(\theta_{JA})$ , as given by the following                                                                                                                                                                                                                                                                                                                                                                                                               |

| emperature Ranges and Storage Condition                                                                                                | ons        | 5            |       | part/package in the application ( $\theta_{JA}$ ), as given by<br>the following<br>equation: $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .                                                                                                                                                                                                                                                                                                                                |

| Human Body Model<br>emperature Ranges and Storage Condition<br>Junction Temperature (T <sub>J-MAX</sub> )                              |            | +150         | ٥C    | part/package in the application ( $\theta_{JA}$ ), as given by<br>the following<br>equation: $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .                                                                                                                                                                                                                                                                                                                                |

| Human Body Model<br>emperature Ranges and Storage Condition                                                                            | ons<br>-55 | 5            |       | part/package in the application (θ <sub>JA</sub> ), as given by<br>the following<br>equation: T <sub>A-MAX</sub> = T <sub>J-MAX-OP</sub> – (θ <sub>JA</sub> × P <sub>D-MAX</sub> ).<br>Norm: MIL 883 E method 3015                                                                                                                                                                                                                                                                        |

| Human Body Model<br>emperature Ranges and Storage Condition<br>Junction Temperature (T <sub>J-MAX</sub> )<br>Storage Temperature Range |            | +150<br>+150 | 0°C   | part/package in the application (θ <sub>JA</sub> ), as given by the following     equation: T <sub>A-MAX</sub> = T <sub>J-MAX-OP</sub> – (θ <sub>JA</sub> × P <sub>D-MAX</sub> ).     Norm: MIL 883 E method 3015     The reflow peak soldering temperature (body temperature) specified is in accordance with <i>IPC, JEDEC J-STD-020"Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".</i> The lead finish for Pb-free leaded packages is |

#### Table 2. Absolute Maximum Ratings

## 6 Electrical Characteristics

$TA = T_J = -40^{\circ}C$  to  $+85^{\circ}C$ ; PVIN = VDD = EN = 3.6V, unless otherwise noted. Typical values are at  $TA=25^{\circ}C$ .

Table 3. Electrical Characteristics

| Symbol                    | Parameter                       | Conditions                            | Min   | Тур  | Max   | Units |   |

|---------------------------|---------------------------------|---------------------------------------|-------|------|-------|-------|---|

| Та                        | Operating Temperature Range     |                                       | -40   |      | +85   | °C    |   |

|                           |                                 |                                       | 1.176 | 1.2  | 1.224 | V     |   |

|                           | Output Voltage                  |                                       | 1.47  | 1.5  | 1.53  | V     |   |

| Vout                      |                                 | PVIN = 3.6V                           | 1.764 | 1.8  | 1.836 | V     |   |

| VOUT                      | Oulput voltage                  | PVIN = 5.0V                           | 2.45  | 2.5  | 2.55  | V     |   |

|                           |                                 |                                       | 2.94  | 3.0  | 3.06  | V     |   |

|                           |                                 |                                       | 3.234 | 3.3  | 3.366 | V     |   |

| I <sub>SHDN</sub>         | Shutdown supply current         | $EN = SW = 0V^{1}$                    |       | 0.01 | 2     | μA    | - |

| ΙQ                        | DC bias current into VDD        | FB = 0V, No Switching <sup>2</sup>    |       | 1    | 1.4   | mA    |   |

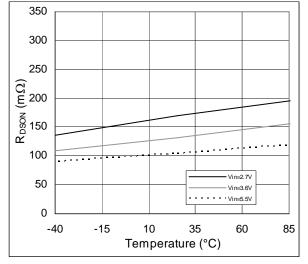

|                           |                                 | I <sub>SW</sub> = 200mA; TA = +25°C   |       | 140  | 200   | -     |   |

| R <sub>DSON</sub> (P)     | Pin-Pin Resistance for PFET     | I <sub>SW</sub> = 200mA               | 7     |      | 230   | mΩ    |   |

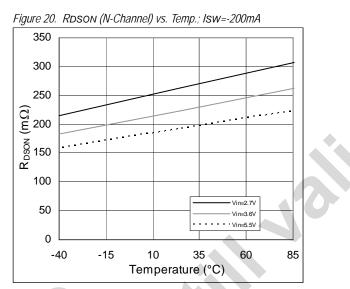

| D                         | Pin-Pin Resistance for NFET     | I <sub>SW</sub> = -200mA; TA = +25°C  |       | 300  |       |       |   |

| R <sub>DSON(N)</sub>      | PIII-PIII RESISTANCE IOI INFET  | I <sub>SW</sub> = -200mA              |       |      | 485   | mΩ    |   |

| I <sub>LIM,PFET</sub>     | Switch peak current limit       | 6                                     | 935   | 1100 | 1200  | mA    |   |

| POK Output                |                                 |                                       | •     |      |       |       |   |

| Vol                       | POK Output Low Voltage          | POK sinking 0.1mA                     |       | 0.05 | 0.2   | V     |   |

|                           | POK Output High Leakage Current | POK = 3.6V                            |       |      | 500   | nA    |   |

|                           | POK Threshold                   | Falling edge, referenced to VOUT(NOM) | 87    | 90   | 93    | %     |   |

| Enable Input              |                                 |                                       |       |      |       |       |   |

| V <sub>IH,EN</sub>        | Logic high input threshold      |                                       | 1.2   |      |       | V     |   |

| $V_{\text{IL},\text{EN}}$ | Logic low input threshold       |                                       |       |      | 0.5   | V     |   |

| I <sub>PIN,ENABLE</sub>   | Pin pull down current           |                                       |       | 5    | 10    | μA    |   |

| Oscillator                |                                 |                                       | 1     |      | •     |       |   |

| Fosc                      | Internal oscillator frequency   |                                       | 1.8   | 2    | 2.2   | MHz   | 1 |

1. Shutdown current includes leakage current of PFET.

x ec

2.  $I_Q$  specified here is when the part is operating at 100% duty cycle.

#### 6.1 System Characteristics

$T_A = 25^{\circ}C$ ; PVIN = VDD = EN = 3.6V, unless otherwise noted. The following parameters are verified by characterisation and are not production tested.

Table 4. System Characteristics

| Symbol      | Parameter                                               | Conditions                                                                                                             | Min | Тур | Мах | Units |

|-------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| T_ON        | Turn on time (from Enable low to high transition)       | EN = Low to High, VIN = 4.2V, C <sub>OUT</sub> = 10µF, $I_{OUT} \leq 1mA$                                              |     | 210 | 350 | μs    |

| η           | Efficiency (L = $3.3\mu$ H, DCR $\leq 100$ m $\Omega$ ) | Vin = 3.6V, I <sub>OUT</sub> = 400mA                                                                                   |     | 96  |     | %     |

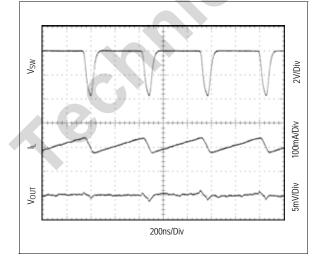

| Vout_ripple | Ripple voltage, PWM mode <sup>1</sup>                   | VIN = 4.2V, I <sub>OUT</sub> = 10mA to 400mA                                                                           |     | 5   |     | mVp-p |

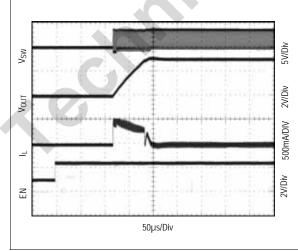

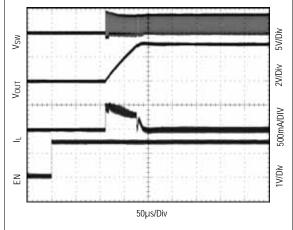

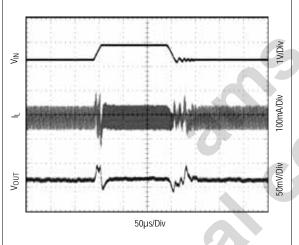

| Line_tr     | Line transient response                                 | VIN = 600mV perturbance, over VIN range 3.4V to 5.5V; $T_{RISE} = T_{FALL} = 10\mu s$ , VOUT = 3.0V, $I_{OUT} = 100mA$ |     | 50  |     | mVpk  |

| Load_tr     | Load transient response                                 | VIN = 4.2V, VOUT = 3.0V, transients up to 100mA, T <sub>RISE</sub> = T <sub>FALL</sub> = 10 $\mu$ s                    |     | 50  |     | mVpk  |

Ripple voltage should measured at C<sub>OUT</sub> electrode on good layout PC board and under condition using suggested inductors and capacitors.

Note: All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Centil

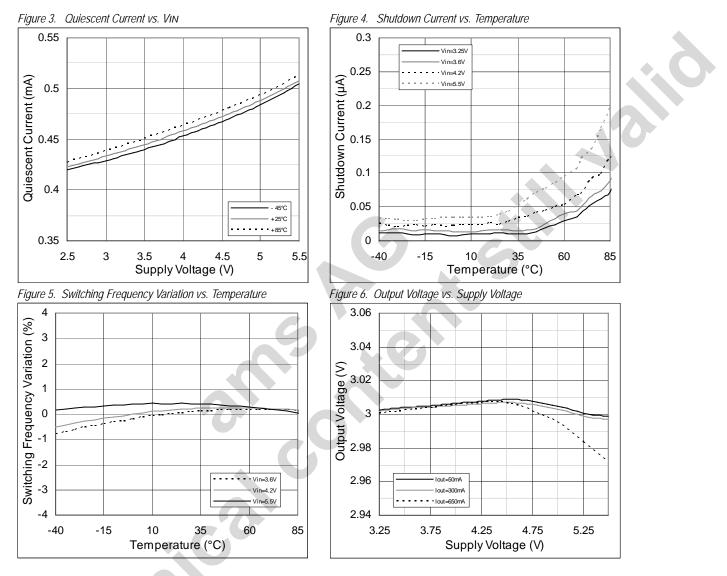

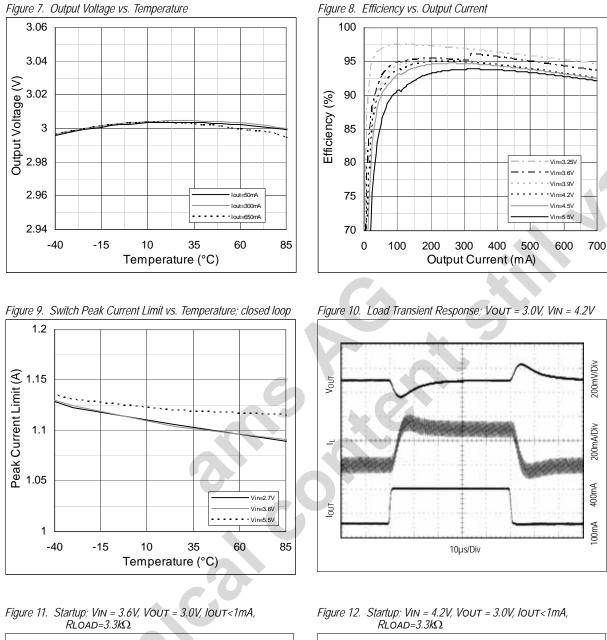

## 7 Typical Operating Characteristics

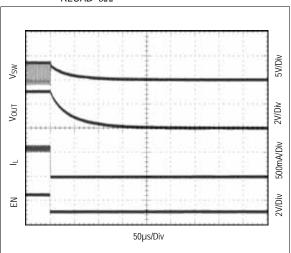

Circuit in Figure 23 on page 11, PVIN = VDD = EN = 3.6V,  $L = 3.3\mu H (LPS4018-332ML_)$ ,  $CIN = COUT = 10\mu F (GRM21BR61C106KA01)$  unless otherwise noted.

Leck

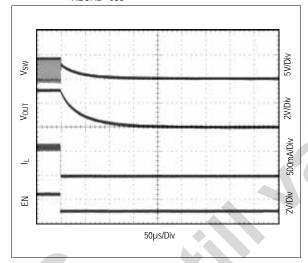

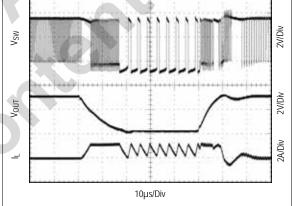

Figure 13. Shutdown Response; VIN=3.6V, VOUT=3.0V, RLOAD=5 $\Omega$

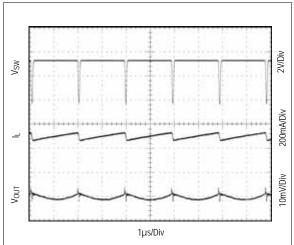

Figure 17. Output Voltage Ripple; VOUT = 3.0V, IOUT = 200mA

Figure 14. Shutdown Response; VIN=4.2V, VOUT=3.0V, RLOAD=5 $\Omega$

Figure 18. Vout Ripple in Skip Mode; VIN=3.31V, Vout=3.0V,  $R{\rm LOAD}{=}5\Omega$

#### Figure 19. RDSON (P-Channel) vs. Temp.; ISW=200mA

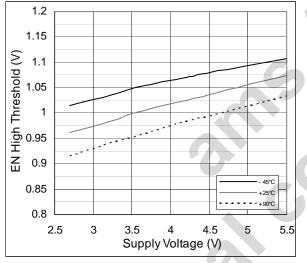

Figure 21. EN High Threshold vs. VIN

recht

## 8 Detailed Description

The AS1334 is a simple, step-down DC-DC converter optimized for powering portable applications that require low dropout voltages such as mobile phones, portable communicators, and similar battery powered RFID devices. Besides being packed with numerous features like current overload protection, thermal overload shutdown and soft start, AS1334 displays the following characteristics:

- Its operation is based on current-mode buck architecture with synchronous rectification for high efficiency.

- Allows the application to operate at maximum efficiency over a wide range of power levels from a single Li-Ion battery cell.

- Provides for a maximum load capability of 650mA in PWM mode, wherein the maximum load range may vary depending on input voltage, output voltage and the selected inductor.

- Is ranked at an efficiency of around 96% for a 400mA load with a 3.6V input voltage.

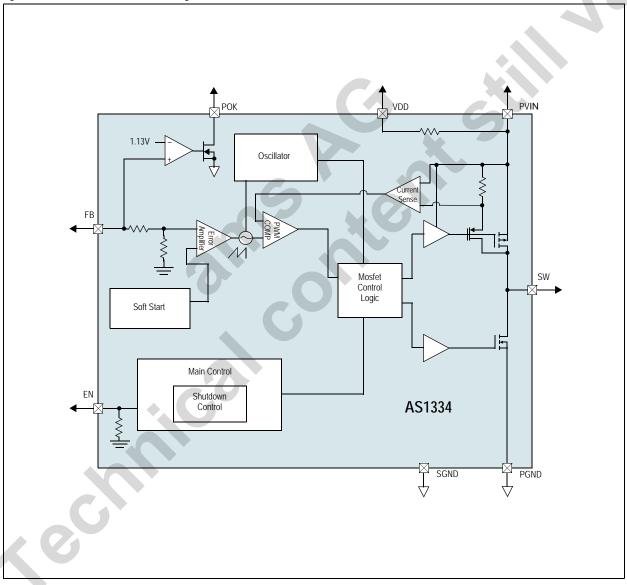

#### Figure 22. AS1334 - Functional Block Diagram

The size of the external components is reduced by using a high switching frequency (2MHz). Figure 1 on page 1 demonstrates that only three external power components are required for implementation. Also, the system controller should set EN low during power-up and other low supply voltage conditions. See Shutdown Mode on page 12.

#### 8.1 Operating the AS1334

AS1334's control block turns on the internal PFET (P-channel MOSFET) switch during the first part of each switching cycle, thus allowing current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of around (VIN - VOUT) / L, by storing energy in a magnetic field.

During the second part of each cycle, the controller turns the PFET switch off, blocking current flow from the input, and then turns the NFET (Nchannel MOSFET) synchronous rectifier on. As a result, the inductor's magnetic field collapses, generating a voltage that forces current from ground through the synchronous rectifier to the output filter capacitor and load.

While the stored energy is transferred back into the circuit and depleted, the inductor current ramps down with a slope around Vout / L. The output filter capacitor stores charge when the inductor current is high, and releases it when low, smoothing the voltage across the load. The output voltage is regulated by modulating the PFET switch on time to control the average current sent to the load. The effect is identical to sending a duty-cycle modulated rectangular wave formed by the switch and synchronous rectifier at SW to a low-pass filter formed by the inductor and output filter capacitor.

The output voltage is equal to the average voltage at the SW pin.

While in operation, the output voltage is regulated by switching at a constant frequency and then modulating the energy per cycle to control power to the load. Energy per cycle is set by modulating the PFET switch on-time pulse width to control the peak inductor current. This is done by comparing the signal from the current-sense amplifier with a slope compensated error signal from the voltage-feedback error amplifier. At the beginning of each cycle, the clock turns on the PFET switch, causing the inductor current to ramp up. When the current sense signal ramps past the error amplifier signal, the PWM comparator turns off the PFET switch and turns on the NFET synchronous rectifier, ending the first part of the cycle.

If an increase in load pulls the output down, the error amplifier output increases, which allows the inductor current to ramp higher before the comparator turns off the PFET. This increases the average current sent to the output and adjusts for the increase in the load. Before appearing at the PWM comparator, a slope compensation ramp from the oscillator is subtracted from the error signal for stability of the current feedback loop. The minimum on time of PFET in PWM mode is 50ns (typ).

#### 8.2 Internal Synchronous Rectifier

To reduce the rectifier forward voltage drop and the associated power loss, the AS1334 uses an internal NFET as a synchronous rectifier. The big advantage of a synchronous rectification is the higher efficiency in a condition where the output voltage is low compared to the voltage drop across an ordinary rectifier diode. During the inductor current down slope in the second part of each cycle the synchronous rectifier is turned on. Before the next cycle the synchronous rectifier is turned off.

There is no need for an external diode because the NFET is conducting through its intrinsic body diode during the transient intervals before it turns on.

#### 8.3 Power-OK

The POK output indicates if the output voltage is within 90% of the nominal voltage level. As long as the output voltage is within regulation the open-drain POK output sinks current.

#### 8.4 Shutdown Mode

If EN is set to high (>1.2V) the AS1334 is in normal operation mode. During power-up and when the power supply is less than 2.7V minimum operating voltage, the chip should be turned off by setting EN low. In shutdown mode the following blocks of the AS1334 are turned off, PFET switch, NFET synchronous rectifier, reference voltage source, control and bias circuitry. The AS1334 is designed for compact portable applications, such as mobile phones where the system controller controls operation mode for maximizing battery life and requirements for small package size outweigh the additional size required for inclusion of UVLO (Under Voltage Lock-Out) circuitry.

Note: Setting the EN digital pin low (<0.5V) places the AS1334 in a 0.01µA (typ) shutdown mode.

#### 8.5 Thermal Overload Protection

To prevent the AS1334 from short-term misuse and overload conditions the chip includes a thermal overload protection. To block the normal operation mode the device is turning the PFET and the NFET off in PWM mode as soon as the junction temperature exceeds 150°C. To resume normal operation the temperature has to drop below 140°C.

Note: Continuing operation in thermal overload conditions may damage the device and is considered bad practice.

#### 8.6 Current Limiting For Protection

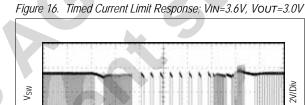

If in the PWM mode the cycle-by-cycle current limit of 1200mA (max.) is reached the current limit feature takes place and protects the device and the external components. A timed current limiting mode is working when a load pulls the output voltage down to approximately 0.375V. In this timed current limit mode the inductor current is forced to ramp down to a safe value. This is achieved by turning off the internal PFET switch and delaying the start of the next cycle for 3.5us. The synchronous rectifier is also turned off in the timed current limit mode.

The advantage of the timed current limit mode is to prevent the device from the loss of the current control.

< echilic

## 9 Application Information

#### 9.1 Inductor Selection

For the external inductor, a 3.3µH inductor is recommended. Minimum inductor size is dependent on the desired efficiency and output current. Inductors with low core losses and small DCR at 2MHz are recommended.

| Part Number    | L     | DCR           | Current Rating | Dimensions (L/W/T) | Manufacturer      |

|----------------|-------|---------------|----------------|--------------------|-------------------|

| LPS4018-222ML_ | 2.2µH | $0.070\Omega$ | 2.9A           | 3.9x3.9x1.7mm      | Coilcraft         |

| LPS4018-332ML_ | 3.3µH | $0.080\Omega$ | 2.4A           | 3.9x3.9x1.7mm      | www.coilcraft.com |

| LPS4018-472ML_ | 4.7µH | 0.125Ω        | 1.9A           | 3.9x3.9x1.7mm      |                   |

Table 5. Recommended Inductor

#### 9.2 Capacitor Selection

A 10µF capacitor is recommended for CIN as well as a 10µF for COUT. Small-sized X5R or X7R ceramic capacitors are recommended as they retain capacitance over wide ranges of voltages and temperatures.

#### 9.2.1 Input and Output Capacitor Selection

Low ESR input capacitors reduce input switching noise and reduce the peak current drawn from the battery. Also low ESR capacitors should be used to minimize VOUT ripple. Multi-layer ceramic capacitors are recommended since they have extremely low ESR and are available in small footprints.

For input decoupling the ceramic capacitor should be located as close to the device as practical. A 4.7µF input capacitor is sufficient for most applications. Larger values may be used without limitations.

A 2.2µF to 10µF output ceramic capacitor is sufficient for most applications. Larger values up to 22µF may be used to obtain extremely low output voltage ripple and improve transient response.

| Part Number       | C     | TC Code | Rated Voltage | Dimensions (L/W/T) | Manufacturer   |

|-------------------|-------|---------|---------------|--------------------|----------------|

| GRM188R60J475KE19 | 4.7µF | X5R     | 6.3V          | 0603               | Murata         |

| GRM219R60J475KE19 | 4.7µF | X5R     | 6.3V          | 0805               | www.murata.com |

| GRM21BR61C475KA88 | 4.7µF | X5R     | 16V           | 0805               |                |

| GRM31CR71E475KA88 | 4.7µF | X7R     | 25V           | 1206               |                |

| GRM188R60J106ME47 | 10µF  | X5R     | 6.3V          | 0603               |                |

| GRM21BR60J106KE19 | 10µF  | X5R     | 6.3V          | 0805               |                |

| GRM21BR61A106KE19 | 10µF  | X5R     | 10V           | 0805               |                |

| GRM32DR71C106KA01 | 10µF  | X7R     | 16V           | 1210               |                |

| GRM21BR60J226ME39 | 22µF  | X5R     | 6.3V          | 0805               |                |

| GRM32ER71A226KE20 | 22µF  | X7R     | 10V           | 1210               |                |

#### Table 6. Recommended Input and Output Capacitor

#### 9.3 EN Pin Control

Drive the EN pin using the system controller to turn the AS1334 ON and OFF. Use a comparator, Schmidt trigger or logic gate to drive the EN pin. Set EN high (>1.2V) for normal operation and low (<0.5V) for a 0.01µA (typ) shutdown mode. Set EN low to turn off the AS1334 during power-up and under voltage conditions when the power supply is less than the 2.7V minimum operating voltage. The part is out of regulation when the input voltage is less than 2.7V.

#### 9.4 Layout Considerations

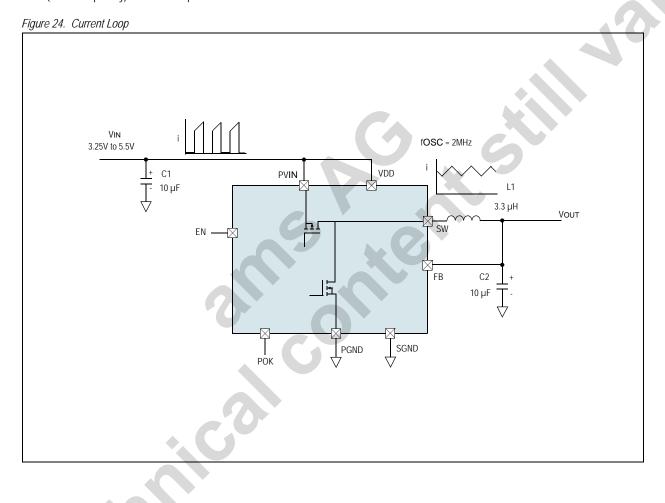

The AS1334 converts higher input voltage to lower output voltage with high efficiency. This is achieved with an inductor based switching topology. During the first half of the switching cycle, the internal PMOS switch turns on, the input voltage is applied to the inductor, and the current flows from PVDD line to the output capacitor (C2) through the inductor. During the second half cycle, the PMOS turns off and the internal NMOS turns on. The inductor current continues to flow via the inductor from the device PGND line to the output capacitor (C2). Referring to Figure 24, the AS1334 has two major current loops where pulse and ripple current flow. The loop shown in the left hand side is most important, because pulse current shown in Figure 24 flows in this path. The right hand side is next. The current waveform in this path is triangular, as shown in Figure 24. Pulse current has many high-frequency components due to fast di/dt. Triangular ripple current also has wide high-frequency components. Board layout and circuit pattern design of these two loops are the key factors for reducing noise radiation and stable operation. Other lines, such as from battery to C1(+) and C2(+) to load, are almost DC current, so it is not necessary to take so much care. Only pattern width (current capability) and DCR drop considerations are needed.

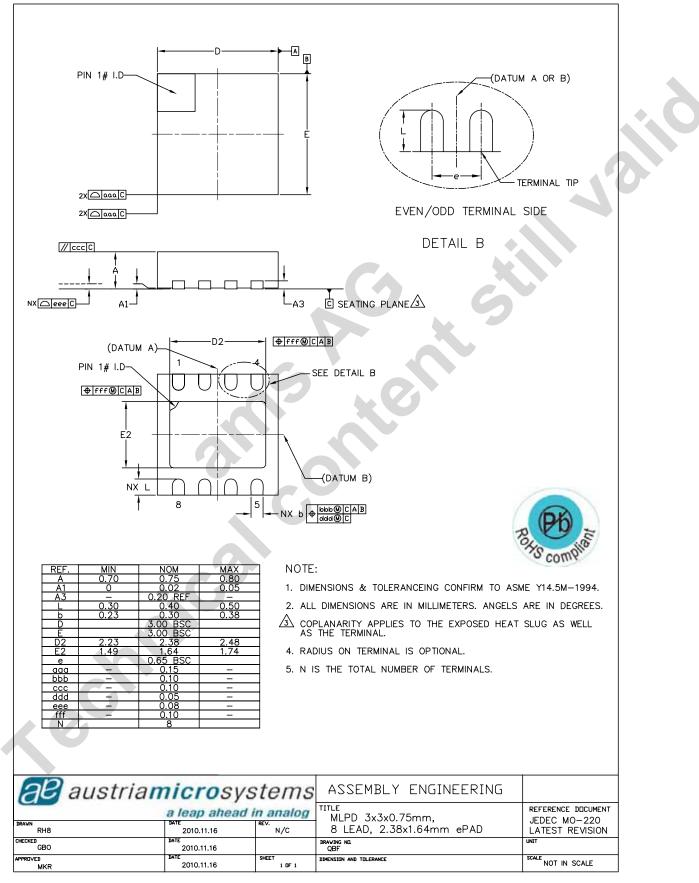

## 10 Package Drawings and Markings

Figure 25. TDFN(3x3) 8-pin Marking

Table 7. Packaging Code YYWWQZZ

| YY              | WW                 | Q                | ZZ                              |

|-----------------|--------------------|------------------|---------------------------------|

| year identifier | manufacturing week | plant identifier | free choice / traceability code |

|                 |                    |                  |                                 |

#### Figure 26. TDFN(3x3) 8-pin Package

## **11 Ordering Information**

The device is available as the standard products shown in Table 8.

Table 8. Ordering Information

| Ordering Code               | Marking | Output | Description                                          | Delivery Form | Package         |

|-----------------------------|---------|--------|------------------------------------------------------|---------------|-----------------|

| AS1334-BTDT-12              | ASR2    | 1.2V   | 650mA, Ultra low Ripple Step Down DC/DC<br>Converter | Tape and Reel | TDFN(3x3) 8-pin |

| AS1334-BTDT-15              | ASR3    | 1.5V   | 650mA, Ultra low Ripple Step Down DC/DC<br>Converter | Tape and Reel | TDFN(3x3) 8-pin |

| AS1334-BTDT-18              | ASR4    | 1.8V   | 650mA, Ultra low Ripple Step Down DC/DC<br>Converter | Tape and Reel | TDFN(3x3) 8-pin |

| AS1334-BTDT-25              | ASR5    | 2.5V   | 650mA, Ultra low Ripple Step Down DC/DC<br>Converter | Tape and Reel | TDFN(3x3) 8-pin |

| AS1334-BTDT-30              | ASQY    | 3.0V   | 650mA, Ultra low Ripple Step Down DC/DC<br>Converter | Tape and Reel | TDFN(3x3) 8-pin |

| AS1334-BTDT-33              | ASR6    | 3.3V   | 650mA, Ultra low Ripple Step Down DC/DC<br>Converter | Tape and Reel | TDFN(3x3) 8-pin |

| AS1334-BTDT-xx <sup>1</sup> | хххх    | хххх   | 650mA, Ultra low Ripple Step Down DC/DC<br>Converter | Tape and Reel | TDFN(3x3) 8-pin |

1. Non-standard devices are available between 1.2V and 3.4V in 100mV steps. For more information and inquiries contact http://www.aus-triamicrosystems.com/contact

#### **Note:** All products are RoHS compliant.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

Technical Support is found at http://www.austriamicrosystems.com/Technical-Support

For further information and requests, please contact us mailto:sales@austriamicrosystems.com or find your local distributor at http://www.austriamicrosystems.com/distributor

Design the AS1334 online at http://www.austriamicrosystems.com/analogbench analogbench is a powerful design and simulation support tool that operates in on-line and off-line mode to evaluate performance and generate application-specific bill-of-materials for austriamicrosystems' power management devices.

> *Banalogbench* Online Design Tool

#### Copyrights

Copyright © 1997-2010, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

#### Headquarters

austriamicrosystems AG Tobelbaderstrasse 30 A-8141 Unterpremstaetten, Austria Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit: http://www.austriamicrosystems.com/contact