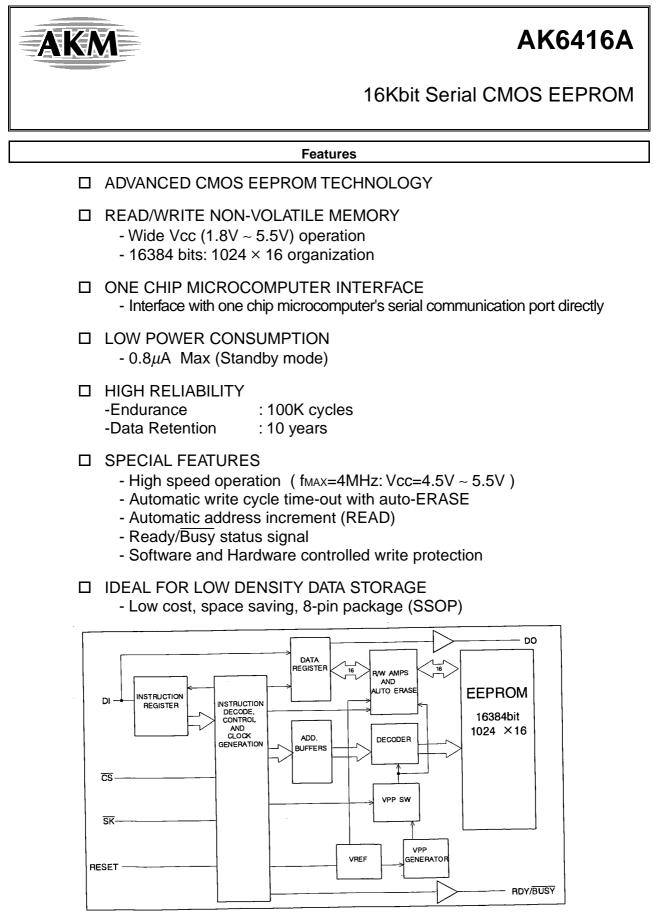

Block diagram

### **General Description**

The AK6416A is a 16384bit, serial, read/write, non-volatile memory device fabricated using an advanced CMOS EEPROM technology. The AK6416A has 16384bits of memory organized into 1024 registers of 16 bits each. The AK6416A can operate full function under wide operating voltage range from 1.8V to 5.5V. The charge up circuit is integrated for high voltage generation that is used for write operation.

The AK6416A can connect to the serial communication port of popular one chip microcomputer directly (3 line negative clock synchronous interface). At write operation, AK6416A takes in the write data from data input pin (DI) to a register synchronously with rising edge of input pulse of serial clock pin ( $\overline{SK}$ ). And at read operation, AK6416A takes out the read data from a register to data output pin (DO) synchronously with falling edge of  $\overline{SK}$ .

The AK6416A has 4 instructions such as READ, WRITE, WREN (write enable) and WRDS (write disable). Each instruction is organized by op-code block (8bits), address block (8bits) and data (8bits  $\times$  2). When input level of  $\overline{SK}$  pin is high level and input level of chip select ( $\overline{CS}$ ) pin is changed from high level to low level, AK6416A can receive the instructions.

Special features of the AK6416A include : automatic write time-out with auto-ERASE, Ready/Busy status signal output and ultra-low standby power mode when deselected ( $\overline{CS}$ =high).

• Software and Hardware controlled write protection

The AK6416A has 2 (hardware and software) write protection functions.

After power on or after execution of WRDS (write disable) instruction, execution of WRITE instruction will be disabled. This write protection condition continues until WREN instruction is executed or Vcc is removed from the part.

Execution of READ instruction is independent of both WREN and WRDS instructions.

Reset pin should be low level when WRITE instruction is executed. When the Reset pin is high level, the WRITE instruction is not executed.

#### • Ready/Busy status signal

During the automatic write time-out period ( $\overline{\text{BUSY}}$  status), the AK6416A can't accept the other instructions. The AK6416A has 2 functions to know the  $\overline{\text{Busy}}$  status from exterior.

The RDY/ $\overline{\text{BUSY}}$  pin indicates the  $\overline{\text{Busy}}$  status regardless of the  $\overline{\text{CS}}$  pin status. The RDY/ $\overline{\text{BUSY}}$  pin outputs the low level regardless of the  $\overline{\text{CS}}$  pin status during  $\overline{\text{Busy}}$  status. Except the above status, this pin outputs high level.

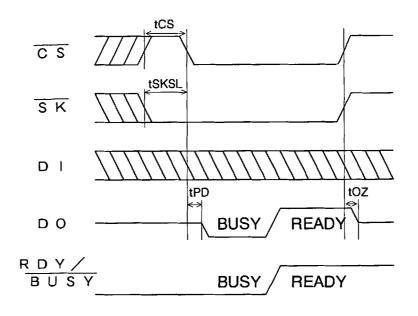

Also the DO pin indicates the Busy status. When input level of  $\overline{SK}$  pin is low level and input level of  $\overline{CS}$  pin is changed from high level to low level, the AK6416A is in the status output mode and the DO pin indicates the Ready/Busy status. The Ready/Busy status outputs on DO pin until  $\overline{CS}$  pin is changed from low level to high level, or first bit ("1") of op-code of next instruction is given to the part. Except when the device is in the status output mode or outputs data, the DO pin is in the high impedance state.

#### Type of Products

| Model    | Memory size | Temp.Range | Vcc       | Package           |

|----------|-------------|------------|-----------|-------------------|

| AK6416AM | 16Kbits     | -40°C~85°C | 1.8V~5.5V | 8pin Plastic SSOP |

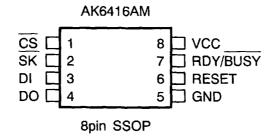

# Pin arrangement

Input pin Output pin

#### Pin Function

| Pin No. | Pin name | I/O      | Note   |

|---------|----------|----------|--------|

| 1       | CS       | I        | l : Ir |

| 2       | SK       | I        | 0:0    |

| 3       | DI       | I        | 0.0    |

| 4       | DO       | 0        |        |

| 5       | GND      |          |        |

| 6       | RESET    | <u> </u> |        |

| 7       | RDY/BUSY | 0        |        |

| 8       | Vcc      |          |        |

|         |          |          |        |

#### ASAHI KASEI

## Pin Description

# CS (Chip Select)

When  $\overline{SK}$  is high level and  $\overline{CS}$  is changed from high level to low level, AK6416A can receive the instructions.  $\overline{CS}$  should be kept low level while receiving op-code, address and data and while outputting data. If  $\overline{CS}$  is changed to high level during the above period, AK6416A stops the instruction execution. When  $\overline{SK}$  is low and  $\overline{CS}$  is changed from high level to low level, AK6416A will be in status output mode. The  $\overline{CS}$  need not be low level during the automatic write time-out period (BUSY status).

# **SK** (Serial Clock)

The  $\overline{SK}$  clock pin is the synchronous clock input for input/output data. At write operation, AK6416A takes in the write data from data input pin (DI) synchronously with rising edge of input pulse of serial clock pin ( $\overline{SK}$ ). And at read operation, AK6416A takes out the read data to data output pin (DO) synchronously with falling edge of  $\overline{SK}$ . The  $\overline{SK}$  clock is not needed during the automatic write time-out period ( $\overline{BUSY}$  status), the status output period and when the device isn't selected ( $\overline{CS}$  = high level).

#### DI (Data Input)

The op-code, address and write data is input to the DI pin.

#### **DO** (Data Output)

The DO pin outputs the read data and status signal and will be high impedance except for this timing.

#### RDY/BUSY (Ready/Busy status)

This pin outputs the internal programming status. When the AK6416A is in the automatic write time-out period, this pin outputs the low level ( $\overline{BUSY}$  status), and outputs the high level except for this timing.

#### **RESET** (Reset)

The AK6416A stops executing the write instruction when the RESET pin is high level. The RESET pin should be low level while the write instruction input period and the automatic write time-out period. If the RESET pin is high level while the automatic write time-out period, the AK6416A stops execution of internal programming and the device returns to ready status. In this case the word data of the specified address will be incomplete. When inputting the new instruction after RESET, the  $\overline{CS}$  pin should be set to high level. The read, write enable and write disable instructions are not affected by RESET pin status.

Vcc (Power Supply)

GND (Ground)

## **Functional Description**

The AK6416A has 4 instructions such as READ, WRITE, WREN (write enable) and WRDS (write disable). Each instruction is organized by op-code block (8bits), address block (8bits) and data (8bits  $\times$  2). When input level of  $\overline{SK}$  pin is high level and input level of chip select ( $\overline{CS}$ ) pin is changed from high level to low level, AK6416A can receive the instructions.

When the instructions are executed consecutively, the  $\overline{CS}$  pin should be brought to high level for a minimum of 250ns(Tcs) between consecutive instruction cycle.

#### Instruction Set For 6416A

| Instruction | Op-Code           | Address                 | Data    |

|-------------|-------------------|-------------------------|---------|

| WRITE       | 1 0 1 0 0 1 A9 A8 | A7 A6 A5 A4 A3 A2 A1 A0 | D15 -D0 |

| READ        | 1 0 1 0 1 0 A9 A8 | A7 A6 A5 A4 A3 A2 A1 A0 | D15 -D0 |

| WREN        | 10100011          | * * * * * * * * *       |         |

| WRDS        | 1010000           | * * * * * * * * *       |         |

| (WRAL)      | 10101111          | * * * * * * * * *       | D15 -D0 |

×:don't care

(Note) The WRAL instruction is used for factory function test only. User can't use this instruction .

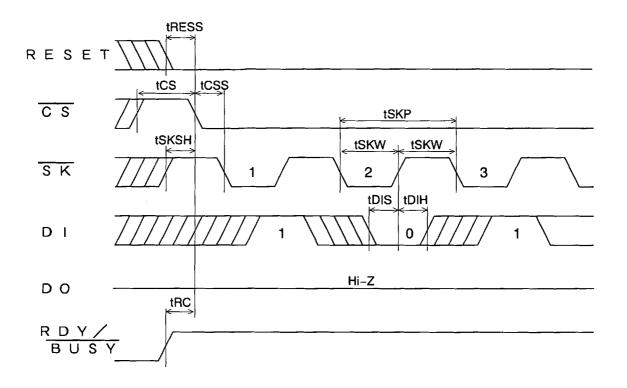

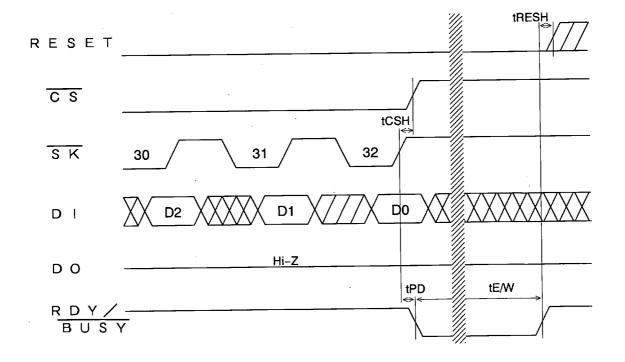

#### Write

The write instruction is followed by 16 bits of data to be written into the specified address. After the 32nd rising edge of SK to read D0 in, the AK6416A will be put into the automatic write time-out period. During the automatic write time-out period (Busy status) and while entering write instruction, the RESET pin should be low level. If the RESET pin is set to high level during the automatic write time-out period, the AK6416A stops execution of internal programming and the device returns to ready status. In this case the word data of the specified address will be incomplete. When inputting the new instruction after RESET, the  $\overline{CS}$  pin should be set to high level. When inputting the new instruction after RESET, the  $\overline{CS}$  pin should be set to high level. When the RESET pin is kept at high level, the write is not executed. This becomes write protection function. The  $\overline{CS}$  pin need not be high level during automatic write time-out period (BUSY status).

| RESET        |             |

|--------------|-------------|

| CS           | 7////////_/ |

| SK           |             |

| DI           |             |

| DO           | Hi-Z        |

| RDY/<br>BUSY |             |

WRITE

### [AK6416A]

## ASAHI KASEI

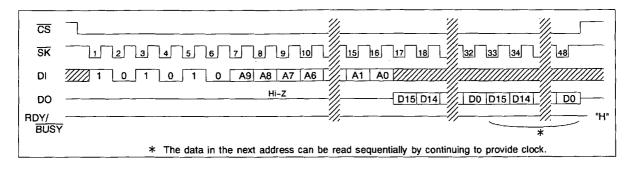

### Read

The read instruction is the only instruction which outputs serial data on the DO pin. When the 17th falling edge of  $\overline{SK}$  is received, the DO pin will come out of high impedance state and shift out the data from D15 first in descending order which is located at the address specified in the instruction.

The data in the next address can be read sequentially by continuing to provide clock. The address automatically cycles to the next higher address after the 16bit data shifted out. When the highest address is reached (\$3FF), the address counter rolls over to address \$000 allowing the read cycle to be continued indefinitely.

## WREN / WRDS (Write Enable and Write Disable)

When Vcc is applied to the part, it powers up in the programming disable (WRDS) state. Programming must be preceded by a programming enable (WREN) instruction. Programming remains enabled until a programming disable (WRDS) instruction is executed or Vcc is removed from the part. The programming disable instruction is provided to protect against accidental data disturb. Execution of a read instruction is not affected by both WREN and WRDS instructions.

| <del>CS</del> | 7                                                                                                                                                                                                                                             | / |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| ŠК            |                                                                                                                                                                                                                                               |   |

| DI            | 1 0 0 X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X |   |

| DO            | WRDS=00 Hi-z                                                                                                                                                                                                                                  | / |

|               | ※ SK pulses exceeding 17 are ignored.                                                                                                                                                                                                         |   |

WREN/WRDS

# Absolute Maximum Ratings

| Parameter                                    | Symbol | Min  | Max     | Unit |

|----------------------------------------------|--------|------|---------|------|

| Power Supply                                 | VCC    | -0.6 | +7.0    | V    |

| All Input Voltages<br>with Respect to Ground | VIO    | -0.6 | VCC+0.6 | V    |

| Ambient storage temperature                  | Tst    | -65  | +150    | °C   |

Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum conditions for extended periods may affect device reliability.

**Recommended Operating Condition**

| Parameter                     | Symbol | Min | Max | Unit |

|-------------------------------|--------|-----|-----|------|

| Power Supply                  | VCC    | 1.8 | 5.5 | V    |

| Ambient Operating Temperature | Та     | -40 | +85 | °C   |

# [AK6416A]

## **Electrical Characteristics**

# (1) D.C. ELECTRICAL CHARACTERISTICS

(  $1.8V \le Vcc \le 5.5V$ ,  $-40^{\circ}C \le Ta \le 85^{\circ}C$ , unless otherwise specified )

| Parameter                                | Symbol | Condition                     | Min.             | Max.             | Unit |

|------------------------------------------|--------|-------------------------------|------------------|------------------|------|

| Current Dissipation                      | ICC1   | VCC=5.5V, tSKP=250ns, *1      |                  | 5.5              | mA   |

| (WRITE)                                  | ICC2   | VCC=2.5V, tSKP=500ns, *1      |                  | 3.5              | mA   |

| · · · · ·                                | ICC3   | VCC=1.8V, tSKP=1.0us, * 1     |                  | 2.5              | mA   |

| Current Dissipation                      | ICC4   | VCC=5.5V, tSKP=250ns, *1      |                  | 1.5              | mA   |

| (READ,WREN,<br>WRDS)                     | ICC5   | VCC=2.5V, tSKP=500ns, *1      |                  | 0.3              | mA   |

| ,                                        | ICC6   | VCC=1.8V, tSKP=1.0us, *1      |                  | 0.2              | mA   |

| Current Dissipation<br>(Standby)         | ICCSB  | VCC=5.5V *2                   |                  | 0.8              | uA   |

| Input High Voltage1<br>CS, SK, RESET pin | VIH1   | 1.8V≤VCC≤5.5V                 | 0.8 ×VCC         | VCC+0.5          | V    |

| Input High Voltage2                      | VIH2   | 2.5V≤VCC≤5.5V                 | $0.7 \times VCC$ | VCC+0.5          | V    |

| DI pin                                   | VIH3   | 1.8V≤VCC<2.5V                 | $0.8 \times VCC$ | VCC+0.5          | V    |

| Input Low Voltage1<br>CS, SK, RESET pin  | VIL1   | 1.8V≤VCC≤5.5V                 | 0                | 0.2 × VCC        | V    |

| Input Low Voltage2                       | VIL2   | 2.5V≤VCC≤5.5V                 | 0                | $0.3 \times VCC$ | V    |

| DI pin                                   | VIL3   | 1.8V≤VCC<2.5V                 | 0                | $0.2 \times VCC$ | V    |

| Output High Voltage                      | VOH1   | 2.5V≤VCC≤5.5V<br>IOH=-50μA    | VCC-0.3          |                  | V    |

|                                          | VOH2   | 1.8V≤VCC<2.5V<br>IOH=-50μA    | VCC-0.3          |                  | V    |

| Output Low Voltage                       | VOL1   | 2.5V≤VCC≤5.5V<br>IOL=1.0mA    |                  | 0.4              | V    |

|                                          | VOL2   | 1.8V≤VCC<2.5V<br>IOL=0.1mA    |                  | 0.4              | V    |

| Input Leakage                            | ILI    | VCC=5.5V,VIN=5.5V             |                  | ±1.0             | uA   |

| Output Leakage                           | ILO    | VCC=5.5V<br>VOUT=5.5V, CS=VCC |                  | ±1.0             | uA   |

\*1: VIN=VIH/VIL, DO=RDY/BUSY=Open

\*2: CS=Vcc, SK/DI/RESET=Vcc/GND,DO=RDY/BUSY=Open

# (2) A.C. ELECTRICAL CHARACTERISTICS

(  $1.8V{\leq}Vcc{\leq}5.5V$ ,  ${-}40^{\circ}C{\leq}Ta{\leq}85^{\circ}C$ , unless otherwise specified )

| Parameter                                | Symbol   | Condition         | Min. | Max. | Unit |

|------------------------------------------|----------|-------------------|------|------|------|

| SK Cycle Time                            | tSKP1    | 4.5V≤VCC≤5.5V     | 250  |      | ns   |

|                                          | tSKP2    | 2.5V≤VCC<4.5V     | 500  |      | ns   |

|                                          | tSKP3    | 1.8V≤VCC<2.5V     | 1.0  |      | us   |

| SK Pulse Width                           | tSKW1    | 4.5V≤VCC≤5.5V     | 125  |      | ns   |

|                                          | tSKW2    | 2.5V≤VCC<4.5V     | 250  |      | ns   |

|                                          | tSKW2    | 1.8V≤VCC<2.5V     | 500  |      | ns   |

| CS Setup Time                            | tCSS1    | 4.5V≤VCC≤5.5V     | 50   |      | ns   |

|                                          | tCSS2    | 1.8V≤VCC<4.5V     | 100  |      | ns   |

| CS Hold Time                             | tCSH1    | 4.5V≤VCC≤5.5V     | 50   |      | ns   |

|                                          | tCSH2    | 1.8V≤VCC<4.5V     | 100  |      | ns   |

| SK Setup Time                            | tSKSH/L1 | 4.5V≤VCC≤5.5V     | 50   |      | ns   |

|                                          | tSKSH/L2 | 1.8V≤VCC<4.5V     | 100  |      | ns   |

| RESET Setup Time                         | tRESS    |                   | 0    |      | ns   |

| RESET Hold Time                          | tRESH    |                   | 0    |      | ns   |

| Data Setup Time                          | tDIS1    | 4.5V≤VCC≤5.5V     | 50   |      | ns   |

|                                          | tDIS2    | 2.5V≤VCC<4.5V     | 100  |      | ns   |

|                                          | tDIS3    | 1.8V≤VCC<2.5V     | 200  |      | ns   |

| Data Hold Time                           | tDIH1    | 4.5V≤VCC≤5.5V     | 50   |      | ns   |

|                                          | tDIH2    | 2.5V≤VCC<4.5V     | 100  |      | ns   |

|                                          | tDIH3    | 1.8V≤VCC<2.5V     | 200  |      | ns   |

| DO pin                                   | tPD1     | 4.5V≤VCC≤5.5V, *3 |      | 75   | ns   |

| Output delay                             | tPD2     | 2.5V≤VCC<4.5V, *3 |      | 150  | ns   |

|                                          | tPD3     | 1.8V≤VCC<2.5V, *3 |      | 300  | ns   |

| RDY/ <del>BUSY</del> pin<br>Output delay | tPD      | CL=100pF          |      | 1    | us   |

| Selftimed Programming                    | tE/W1    | 2.5V≤VCC≤5.5V     |      | 7    | ms   |

| Time                                     | tE/W2    | 1.8V≤VCC<2.5V     |      | 10   | ms   |

| Write Recovery Time                      | tRC      |                   | 100  |      | ns   |

| Min $\overline{CS}$ High Time            | tCS      |                   | 250  |      | ns   |

| DO High-Z Time                           | tOZ      |                   |      | 500  | ns   |

\*3:CL=100pF

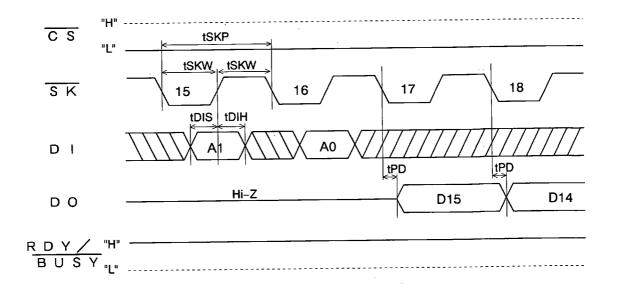

# Synchronous Data Timing

Instruction Input

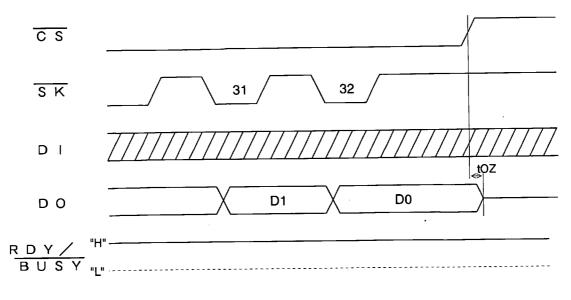

Data Output (READ)

Data Output (READ)

Ready / BUSY Signal Output(RDY/BUSY pin)

Ready / BUSY Signal Output (DO pin)