# Am79C432A ISM PhoX<sup>™</sup> Controller for Digital Cordless Telephones

**Technical Manual**

1997

#### © 1997 Advanced Micro Devices, Inc. All rights reserved.

# Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products, except as provided in AMD's Terms and Conditions of Sale for such products.

#### Trademarks

PhoX, AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# TABLE OF CONTENTS

#

| Chapter 1 | OVE        | RVIEW      |                    |                                                |       |

|-----------|------------|------------|--------------------|------------------------------------------------|-------|

|           | 1.1        | General    | Description        |                                                | . 1-9 |

|           | 1.2        | Distinctiv | /e Characte        | ristics                                        | 1-11  |

|           | 1.3        | Pin List.  |                    |                                                | 1-15  |

|           | 1.4        | Logic Sy   | mbol               |                                                | 1-17  |

|           | 1.5        |            |                    |                                                |       |

|           |            | 1.5.1      |                    | Pins                                           |       |

|           |            | 1.5.2      |                    |                                                |       |

|           |            | 1.5.3      |                    | oller and Address Decoder Pins.                |       |

|           |            | 1.5.4      |                    | rt Pins.                                       |       |

|           |            | 1.5.5      |                    | er and Serial Port Pins.                       |       |

|           | 4.0        | 1.5.6      |                    | et, and Power Supply Pins                      |       |

|           | 1.6        |            |                    | ultiplexing                                    |       |

|           | 1.7<br>1.8 |            |                    | η                                              |       |

|           | 1.0        | Glossaly   | or renns.          |                                                | 1-20  |

| Chapter 2 | FUN        | CTIONAL    | DESCRIP            | TION                                           |       |

|           | 2.1        | Global F   | unctions           |                                                | . 2-1 |

|           |            | 2.1.1      | Reset and          | Basic Mode Establishment                       | . 2-1 |

|           |            | 2.1.2      |                    | nagement and Shutdown Mode                     |       |

|           | 2.2        | •          |                    | ck Functions                                   |       |

|           |            | 2.2.1      |                    | Microcontroller                                |       |

|           |            |            | 2.2.1.1            | Memory                                         |       |

|           |            |            | 2.2.1.2            |                                                |       |

|           |            |            | 2.2.1.3            | Reset                                          |       |

|           |            |            | 2.2.1.4<br>2.2.1.5 | EA                                             |       |

|           |            |            | 2.2.1.5            | SFR Map Additions                              |       |

|           |            |            | 2.2.1.0            | PSEN Modifications                             |       |

|           |            |            | 2.2.1.8            | Interrupt Modifications                        |       |

|           |            |            | 2.2.1.9            | T0 and T1                                      |       |

|           |            | 2.2.2      |                    | ontroller                                      |       |

|           |            | 2.2.3      |                    | ecoder and Latch                               |       |

|           |            | 2.2.4      |                    | n-Chip RAM (Data RAM)                          |       |

|           |            | 2.2.5      | •                  | vel Detection                                  |       |

|           |            | 2.2.6      |                    | Timer (WDT) and Software Reset                 |       |

|           |            | 2.2.7      | Key Scann          | er                                             | . 2-8 |

|           |            | 2.2.8      | Serial Port        |                                                | . 2-9 |

|           |            | 2.2.9      |                    | rt                                             |       |

|           | 2.3        |            | •                  | cific Functions                                |       |

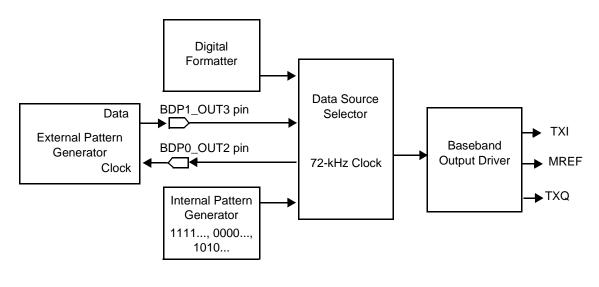

|           |            | 2.3.1      | -                  | matter                                         |       |

|           |            |            | 2.3.1.1            | Block Diagram                                  |       |

|           |            |            | 2.3.1.2            | Device Selection: CFP/CPP                      |       |

|           |            |            | 2.3.1.3            | Multiplex Selection and Formatter Clear        |       |

|           |            |            | 2.3.1.4            | Starting and Stopping Transmission             |       |

|           |            |            | 2.3.1.5            | Timing Recovery                                |       |

|           |            |            | 2.3.1.6            | SYN Channel Operation and Link Synchronization |       |

|           |            |            | 2.3.1.7            | D Channel Operation                            |       |

|           |            |            | 2.3.1.8            | B Channel Operation                            | 2-21  |

Chapter 3

|     |                                                                                                                                                                               | 2.3.1.9                                                                                                                                                                                                           | Setting Modem Delay                            | . 2-22                                                                                                                                                         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                               | 2.3.1.10                                                                                                                                                                                                          | Radio Interface                                | . 2-25                                                                                                                                                         |

|     |                                                                                                                                                                               | 2.3.1.11                                                                                                                                                                                                          | FDD Mode                                       |                                                                                                                                                                |

|     | 2.3.2                                                                                                                                                                         |                                                                                                                                                                                                                   |                                                |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.3.2.1                                                                                                                                                                                                           | MODE1                                          |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.3.2.2                                                                                                                                                                                                           | MODE2                                          |                                                                                                                                                                |

|     | 2.3.3                                                                                                                                                                         |                                                                                                                                                                                                                   | Output Driver                                  |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.3.3.1                                                                                                                                                                                                           | I-Q Mode                                       |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.3.3.2                                                                                                                                                                                                           | NRZ Mode                                       | -                                                                                                                                                              |

|     | 2.3.4                                                                                                                                                                         |                                                                                                                                                                                                                   |                                                |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.3.4.1                                                                                                                                                                                                           | Handling the Link                              |                                                                                                                                                                |

| 0.4 | A                                                                                                                                                                             | 2.3.4.2                                                                                                                                                                                                           |                                                |                                                                                                                                                                |

| 2.4 |                                                                                                                                                                               |                                                                                                                                                                                                                   |                                                |                                                                                                                                                                |

|     | 2.4.1<br>2.4.2                                                                                                                                                                |                                                                                                                                                                                                                   | tiplexer                                       |                                                                                                                                                                |

|     | 2.4.2                                                                                                                                                                         | 2.4.2.1                                                                                                                                                                                                           |                                                |                                                                                                                                                                |

|     | 2.4.3                                                                                                                                                                         |                                                                                                                                                                                                                   | Hands-Free Support                             |                                                                                                                                                                |

|     | 2.4.3                                                                                                                                                                         |                                                                                                                                                                                                                   | ing Notes                                      |                                                                                                                                                                |

|     | 2.4.4                                                                                                                                                                         | 0                                                                                                                                                                                                                 | I Multiplexer and B Channel Port.              |                                                                                                                                                                |

|     | 2.4.5                                                                                                                                                                         |                                                                                                                                                                                                                   |                                                |                                                                                                                                                                |

|     | 2.4.7                                                                                                                                                                         | •                                                                                                                                                                                                                 | GI                                             |                                                                                                                                                                |

| 2.5 |                                                                                                                                                                               | •                                                                                                                                                                                                                 | ort                                            |                                                                                                                                                                |

| 2.0 | 2.5.1                                                                                                                                                                         |                                                                                                                                                                                                                   | Mode                                           |                                                                                                                                                                |

|     | 2.5.2                                                                                                                                                                         |                                                                                                                                                                                                                   | est Facilities                                 |                                                                                                                                                                |

|     | 2.0.2                                                                                                                                                                         | 2.5.2.1                                                                                                                                                                                                           | Modulator Test Mode                            |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.5.2.2                                                                                                                                                                                                           | Transmitter Digital Output                     |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.5.2.3                                                                                                                                                                                                           | B Channel Injection/Monitoring                 |                                                                                                                                                                |

|     |                                                                                                                                                                               | 2.5.2.4                                                                                                                                                                                                           | D Channel and SYN Channel Injection/Monitoring |                                                                                                                                                                |

|     | 2.5.3                                                                                                                                                                         | B Channe                                                                                                                                                                                                          | I Loopbacks                                    |                                                                                                                                                                |

|     |                                                                                                                                                                               |                                                                                                                                                                                                                   |                                                |                                                                                                                                                                |

| REG |                                                                                                                                                                               | SUMMARY                                                                                                                                                                                                           |                                                |                                                                                                                                                                |

| 3.1 |                                                                                                                                                                               |                                                                                                                                                                                                                   | ndex                                           |                                                                                                                                                                |

| 3.2 |                                                                                                                                                                               | •                                                                                                                                                                                                                 | Bits                                           |                                                                                                                                                                |

| 3.3 |                                                                                                                                                                               |                                                                                                                                                                                                                   |                                                | 3-4                                                                                                                                                            |

|     | 3.3.1                                                                                                                                                                         |                                                                                                                                                                                                                   |                                                |                                                                                                                                                                |

| 3.4 | Dorollal                                                                                                                                                                      |                                                                                                                                                                                                                   |                                                |                                                                                                                                                                |

|     |                                                                                                                                                                               | Port                                                                                                                                                                                                              |                                                | 3-5                                                                                                                                                            |

|     | 3.4.1                                                                                                                                                                         | Port<br>P1SRC0 .                                                                                                                                                                                                  |                                                | 3-5<br>3-5                                                                                                                                                     |

|     | 3.4.1<br>3.4.2                                                                                                                                                                | Port                                                                                                                                                                                                              |                                                | 3-5<br>3-5<br>3-5                                                                                                                                              |

|     | 3.4.1<br>3.4.2<br>3.4.3                                                                                                                                                       | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .                                                                                                                                                                          |                                                | 3-5<br>3-5<br>3-5<br>3-6                                                                                                                                       |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                                                                                              | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .                                                                                                                                                              |                                                | 3-5<br>3-5<br>3-5<br>3-6<br>3-6                                                                                                                                |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                                                                                                                                     | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG                                                                                                                                                    |                                                | 3-5<br>3-5<br>3-5<br>3-6<br>3-6<br>3-7                                                                                                                         |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6                                                                                                                            | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG<br>GPOCTRO                                                                                                                                         | )                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7                                                                                                                  |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7                                                                                                                   | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG<br>GPOCTR0<br>GPOCTR1                                                                                                                              | )                                              | 3-5<br>3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8                                                                                                    |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8                                                                                                          | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG .<br>GPOCTR0<br>GPOCTR1<br>XISTAT0 .                                                                                                               | )                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9                                                                                                    |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9                                                                                                 | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG<br>GPOCTR0<br>GPOCTR1<br>XISTAT0 .<br>XISTAT1 .                                                                                                    | ).<br>                                         | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10                                                                                     |

| 2 5 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10                                                                                       | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG .<br>GPOCTR0<br>GPOCTR1<br>XISTAT0 .<br>XISTAT1 .<br>XISTAT2 .                                                                                     | )                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>3-10                                                                                    |

| 3.5 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca                                                                            | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG<br>GPOCTR0<br>GPOCTR1<br>XISTAT0 .<br>XISTAT1 .<br>XISTAT2 .                                                                                       | )                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>3-10<br>3-11                                                                            |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1                                                 | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG<br>GPOCTR0<br>GPOCTR1<br>XISTAT0 .<br>XISTAT1 .<br>XISTAT2 .<br>Anner                                                                              | )                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-11                                                                            |

| 3.6 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX                                        | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG .<br>GPOCTR0<br>GPOCTR1<br>XISTAT0 .<br>XISTAT1 .<br>XISTAT2 .<br>anner<br>KPSTAT                                                                  | ).<br>                                         | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>3-10<br>3-11<br>3-11<br>3-12                                                                   |

|     | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX<br>Serial P                                              | Port                                                                                                                                                                                                              | D                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-11<br>3-11<br>3-12<br>3-13                                                           |

| 3.6 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX<br>Serial P<br>3.7.1                                     | Port                                                                                                                                                                                                              | D                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9<br>. 3-10<br>. 3-11<br>. 3-11<br>. 3-11<br>. 3-13<br>. 3-13                                        |

| 3.6 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX<br>Serial P<br>3.7.1<br>3.7.2                            | Port                                                                                                                                                                                                              | D                                              | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-7<br>3-10<br>. 3-10<br>. 3-11<br>. 3-11<br>. 3-12<br>. 3-13<br>. 3-13<br>. 3-13                             |

| 3.6 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX<br>Serial P<br>3.7.1<br>3.7.2<br>3.7.3                   | Port                                                                                                                                                                                                              |                                                | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-7<br>3-10<br>. 3-10<br>. 3-11<br>. 3-11<br>. 3-11<br>. 3-13<br>. 3-13<br>. 3-14                             |

| 3.6 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX<br>Serial P<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4          | Port                                                                                                                                                                                                              |                                                | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>.3-10<br>.3-11<br>.3-11<br>.3-11<br>.3-13<br>.3-13<br>.3-13<br>.3-14<br>3-15            |

| 3.6 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX<br>Serial P<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4<br>3.7.5 | Port                                                                                                                                                                                                              |                                                | 3-5<br>3-5<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9<br>3-10<br>.3-10<br>.3-11<br>.3-11<br>.3-11<br>.3-13<br>.3-13<br>.3-13<br>.3-13<br>.3-14<br>.3-15<br>3-15 |

| 3.6 | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>3.4.10<br>Key Sca<br>3.5.1<br>BDMUX<br>Serial P<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4          | Port<br>P1SRC0 .<br>P1SRC1 .<br>P1SRC2 .<br>P1MASK .<br>P1TRIG<br>GPOCTR0<br>GPOCTR1<br>XISTAT0 .<br>XISTAT1 .<br>XISTAT2 .<br>XISTAT2 .<br>XISTAT2 .<br>SIOMODE<br>SIOTB<br>SIORB<br>SIOTBL<br>SIOTBL<br>SIOMASK |                                                | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-8<br>3-9<br>. 3-10<br>. 3-11<br>. 3-11<br>. 3-11<br>. 3-13<br>. 3-13<br>. 3-14<br>. 3-15<br>. 3-16          |

|       | 3.7.8     | SPTMG                                   | . 3-17 |

|-------|-----------|-----------------------------------------|--------|

| 3.8   | Audio M   | ux                                      | . 3-18 |

|       | 3.8.1     | AO2MUX                                  | 3-18   |

|       | 3.8.2     | AO3MUX                                  |        |

|       | 3.8.3     | ADMUX                                   |        |

|       | 3.8.4     | Al2CTR                                  |        |

|       |           |                                         |        |

|       | 3.8.5     | STCR                                    |        |

|       | 3.8.6     | A23ATTN                                 |        |

| 3.9   |           | ree Operations                          |        |

|       | 3.9.1     | RXLEVEL                                 |        |

|       | 3.9.2     | TXLEVEL                                 |        |

| 3.10  | Tone Rir  | nger                                    | . 3-25 |

|       | 3.10.1    | TRAMP                                   | . 3-25 |

|       | 3.10.2    | TRFR                                    | . 3-25 |

| 3.11  | Modulate  | or                                      | . 3-28 |

|       | 3.11.1    | MODTST                                  |        |

| 3 12  | Battery [ | Detect                                  |        |

| 0.12  | 3.12.1    | BATLEV                                  |        |

| 3 13  |           | D, (i = 0,                              |        |

| 5.15  | 3.13.1    | RSSICFG                                 |        |

|       |           |                                         |        |

| 0.4.4 | 3.13.2    | RSSISTAT                                |        |

| 3.14  |           |                                         |        |

|       | 3.14.1    | T1FR1–3, T2FR1–3 (Dual-Tone Frequency)  |        |

|       | 3.14.2    | T1AR, T2AR (Dual-Tone Amplitude)        |        |

|       | 3.14.3    | TTAR, RTAR (Dual-Tone Path Attenuation) |        |

| 3.15  | Codec .   |                                         | . 3-36 |

|       | 3.15.1    | TXATTN                                  | . 3-36 |

|       | 3.15.2    | RXATTN                                  | 3-36   |

|       | 3.15.3    | DSPCTR                                  | . 3-37 |

| 3.16  | Noise Su  | uppression                              | . 3-38 |

|       | 3.16.1    | NSCTR                                   |        |

|       | 3.16.2    | NSTHR                                   |        |

|       | 3.16.3    | MUTE                                    |        |

|       | 3.16.4    | JITCTR                                  |        |

| 2 1 7 |           | ormatter                                |        |

| 3.17  | •         |                                         |        |

|       | 3.17.1    | RXBUF0–5                                |        |

|       | 3.17.2    | TXBUF0–5                                |        |

|       | 3.17.3    |                                         |        |

|       | 3.17.4    | RXTMGR                                  |        |

|       | 3.17.5    | TXMUX                                   | . 3-44 |

|       | 3.17.6    | RXMUX                                   | . 3-45 |

|       | 3.17.7    | TXDISAB                                 | . 3-46 |

|       | 3.17.8    | SYNCDC                                  | . 3-46 |

|       | 3.17.9    | RDATAC                                  | . 3-47 |

|       | 3.17.10   | TPOWER                                  | . 3-47 |

|       | 3.17.11   | BVALID                                  |        |

|       | 3.17.12   | SYNCTR                                  |        |

|       | 3.17.13   | DMONIT                                  |        |

|       | 3.17.14   | DTXCTR                                  |        |

|       | 3.17.14   | TDELAY                                  |        |

|       |           |                                         |        |

|       | 3.17.16   |                                         |        |

|       | 3.17.17   | RFINV                                   |        |

|       | 3.17.18   | RXFALL                                  |        |

|       | 3.17.19   | PLLCTRL                                 |        |

|       | 3.17.20   | MODTMG                                  |        |

|       | 3.17.21   | MODDLY                                  | . 3-57 |

|       | 3.17.22   | DCHSTAT                                 | . 3-58 |

|       | 3.17.23   | CMSSRC                                  | . 3-60 |

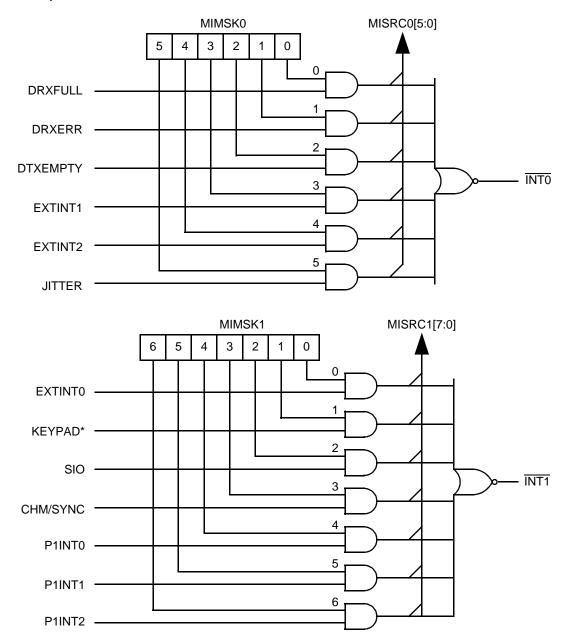

|           | 3.17.24       CMSMASK       3-61         3.18       Interrupt Controller.       3-62         3.18.1       MISRC0       3-62         3.18.2       MISRC1       3-63         3.18.3       MIMSK0       3-65         3.18.4       MIMSK1       3-65         3.19       Clock Generator (Power Management)       3-66         3.19.1       UCCCTR.       3-66         3.19.2       UCCCP.       3-67         3.19.3       MECTR0.       3-68         3.19.4       MECTR1.       3-69         3.20       Watchdog Timer.       3-70                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -         | 3.20.1 WDTKEY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

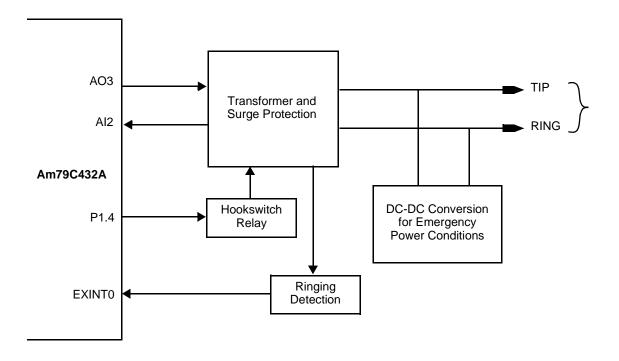

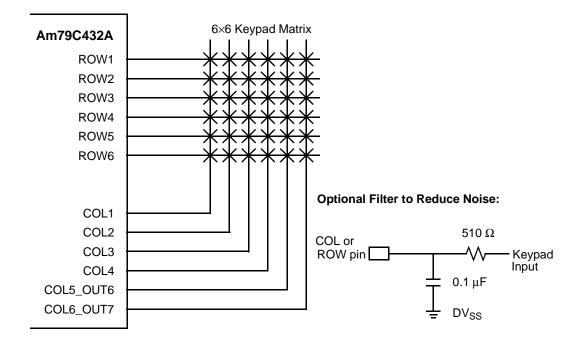

| Chapter 4 | HARDWARE APPLICATIONS4.1ROM and RAM Interface4-14.2EEPROM Interface4-24.3Handset and Loudspeaker Interface4-24.4PSTN Interface4-34.5Key Scanner Interface4-34.6Battery4-4                                                                                                                                                                                                                                                                                                                                                                                                              |

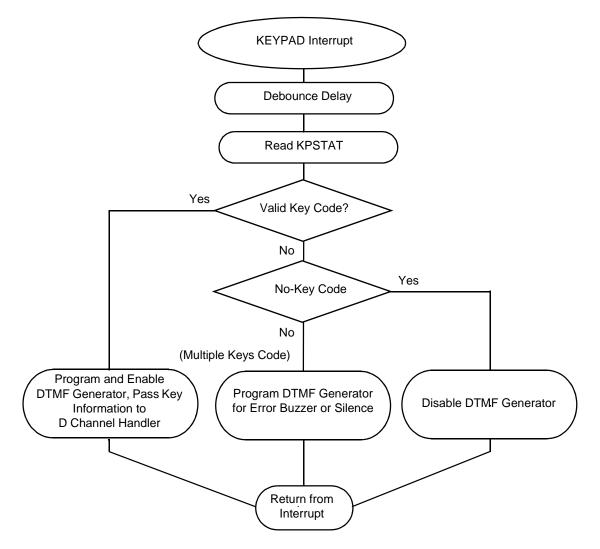

| Chapter 5 | SOFTWARE APPLICATIONS5.1Shutdown Mode.5-15.2Key Scanner Operation5-25.3Digital Formatter Programming Hints.5-35.3.1SYNCD Register5-35.3.2Transmitting MUX2 or MUX35-35.4T0 and T1 Timer/Counters.5-35.5P1 Interrupts5-35.6Serial Port Service.5-4                                                                                                                                                                                                                                                                                                                                      |

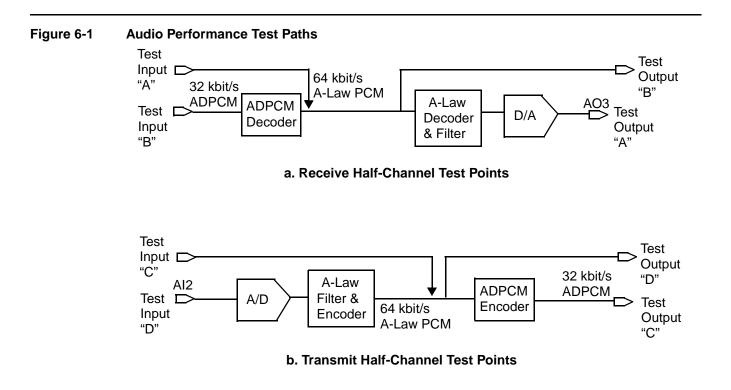

| Chapter 6 | ELECTRICAL CHARACTERISTICS6.1Absolute Maximum Ratings6-16.2Operating Range6-16.3Digital I/O DC Characteristics6-26.4Audio Characteristics6-36.4.1Audio Pin Characteristics6-36.4.2dBm0 Reference-Level and Digital Full Scale6-36.4.3Audio Performance6-46.5RSSI Characteristics6-66.6I/Q Modulator Characteristics6-76.7NRZ Output Characteristics6-86.8Reset6-86.9Microcontroller and Address Decoder Switching Characteristics6-126.10Digital Formatter Switching Characteristics6-146.12Serial Port and A-Law PCM Port Switching Characteristics6-156.13Battery-Level Detector6-15 |

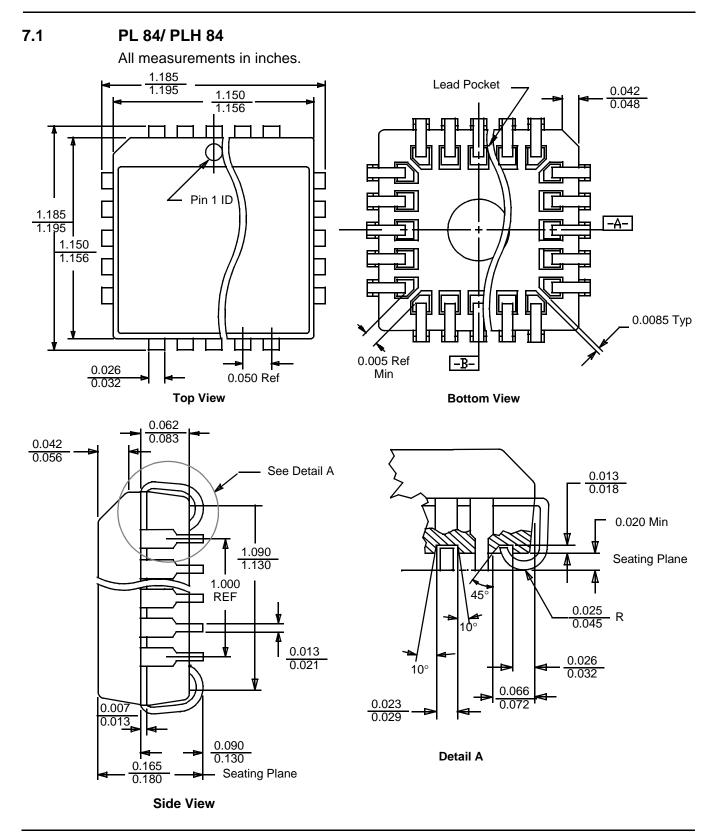

| Chapter 7 | PACKAGE DIMENSIONS           7.1         PL 84/PLH 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# LIST OF FIGURES

| Figure 1-1<br>Figure 1-2<br>Figure 1-3 | System Architecture       Block Diagram       Connection Diagram | 1-13 |

|----------------------------------------|------------------------------------------------------------------|------|

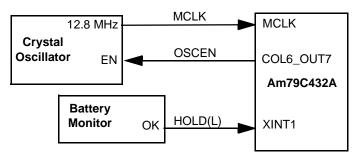

| Figure 2-1                             | OSCEN and HOLD Application                                       | 2.2  |

| Figure 2-1                             |                                                                  |      |

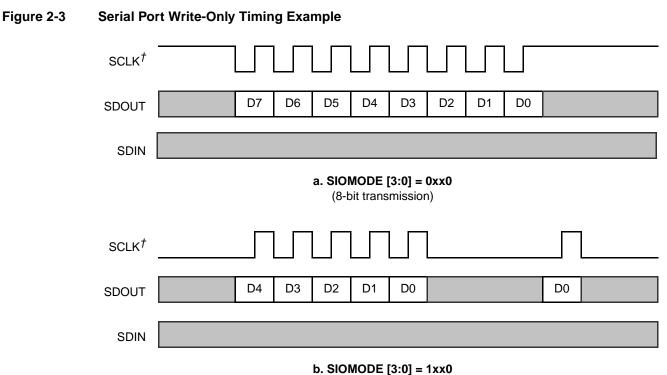

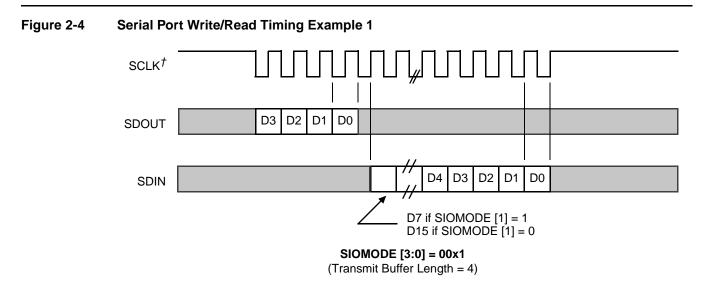

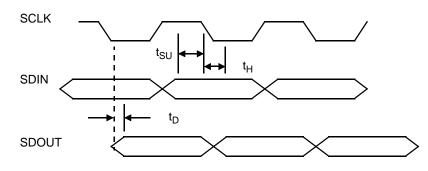

| Figure 2-2                             | Serial Port Write-Only Timing Example.                           | 2-10 |

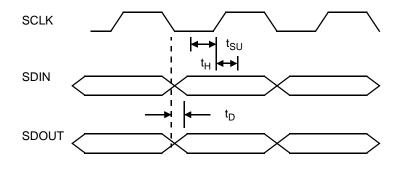

| Figure 2-3                             | Serial Port Write/Read Timing Example 1                          |      |

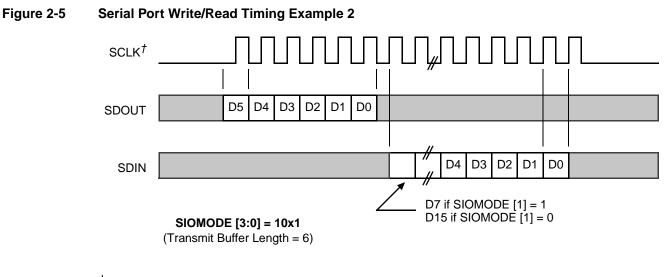

| Figure 2-4                             | Serial Port Write/Read Timing Example 2                          |      |

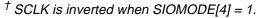

| Figure 2-6                             | Serial Port Write/Read Timing Example 3                          |      |

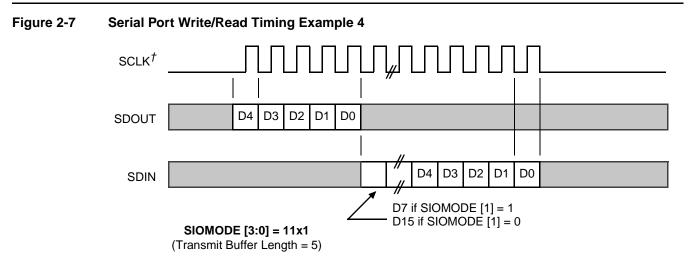

| Figure 2-7                             | Serial Port Write/Read Timing Example 4.                         |      |

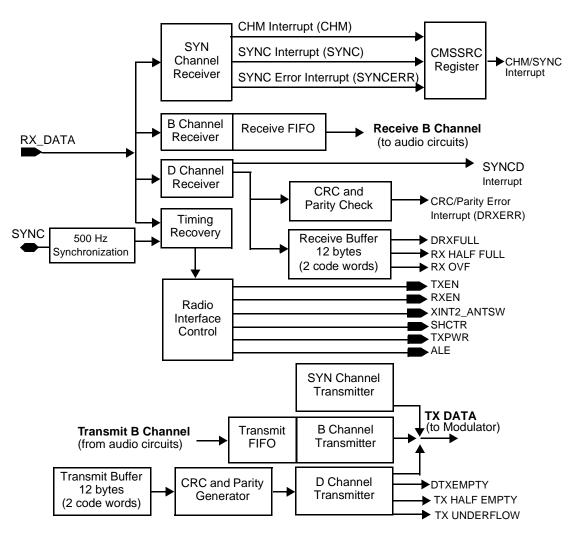

| Figure 2-8                             | Digital Formatter Block Diagram                                  |      |

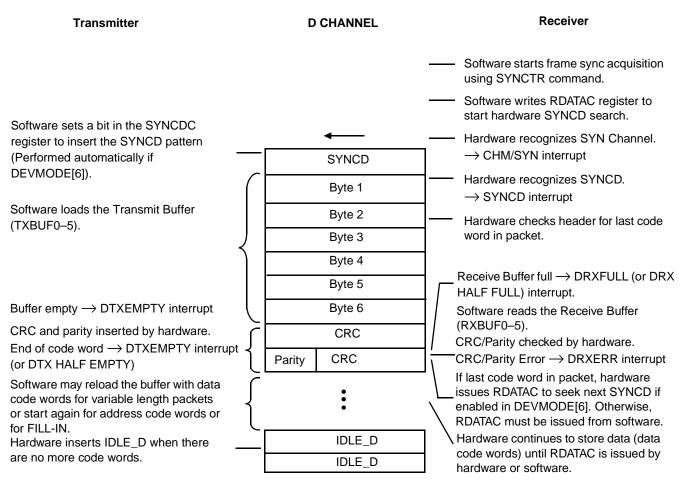

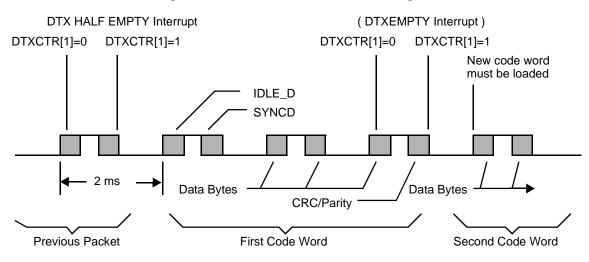

| Figure 2-9                             | Operation of the D Channel.                                      |      |

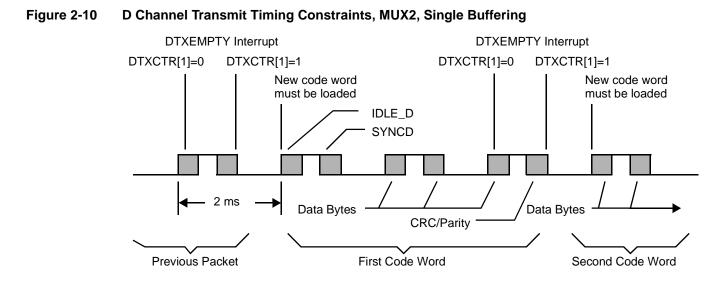

| Figure 2-10                            | D Channel Transmit Timing Constraints, MUX2, Single Buffering    |      |

| Figure 2-11                            | D Channel Transmit Timing Constraints, MUX2, Double Buffering.   |      |

| Figure 2-12                            | Frame Timing of MUX1.x and MUX2                                  |      |

| Figure 2-13                            | Correct Timing Relationship between SHCTRL and RX_DATA for       |      |

| rigare 2 re                            | MUX1.x or MUX2                                                   | 2-23 |

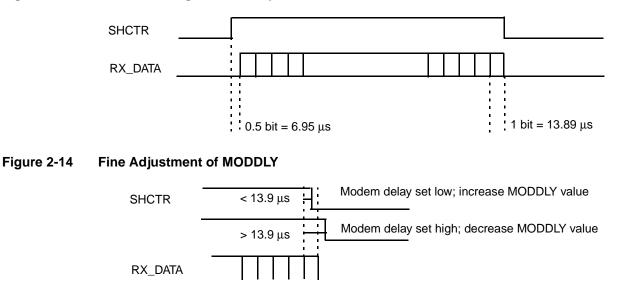

| Figure 2-14                            | Fine Adjustment of MODDLY                                        |      |

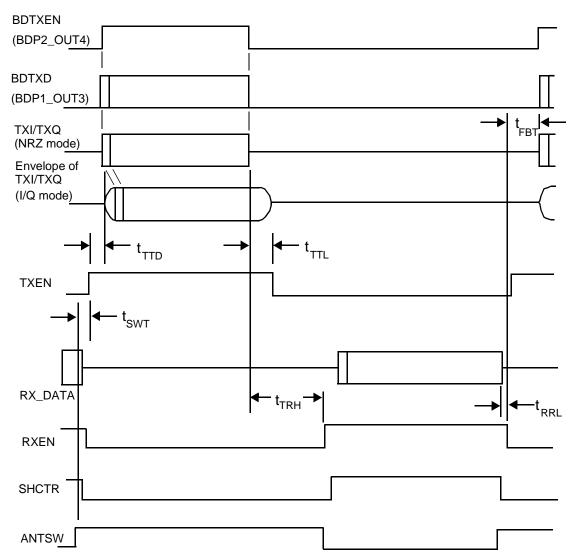

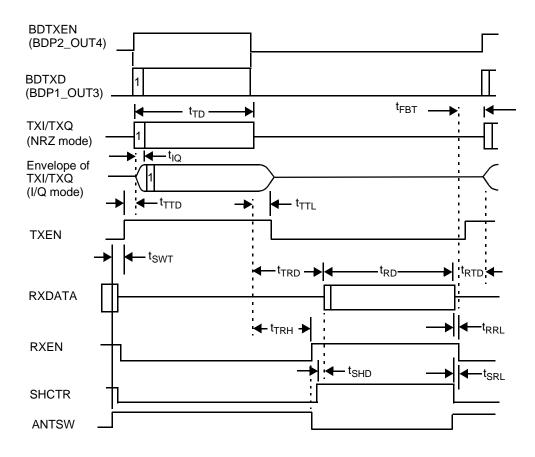

| Figure 2-15                            | Programmable Timing of RF Interface Controls                     |      |

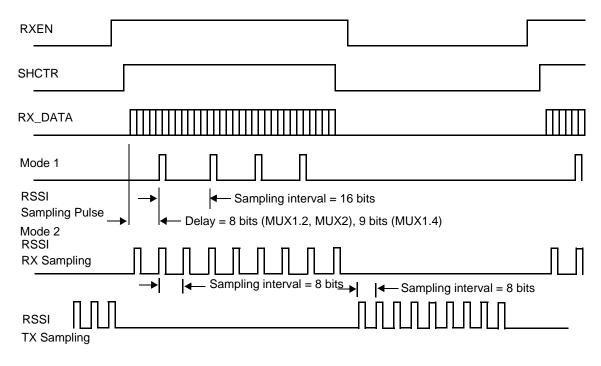

| Figure 2-16                            | RSSI Timing in Synchronous Mode                                  |      |

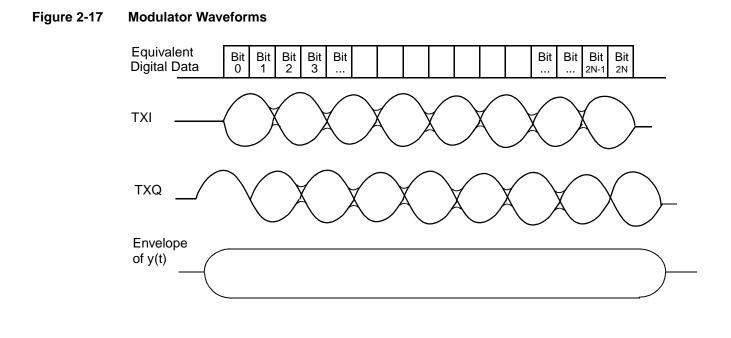

| Figure 2-17                            | Modulator Waveforms                                              |      |

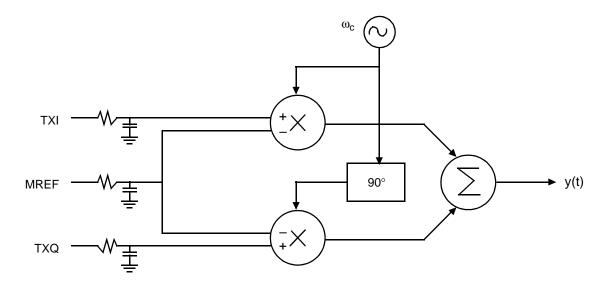

| Figure 2-18                            | Modulator I/Q Mixer Block Diagram                                |      |

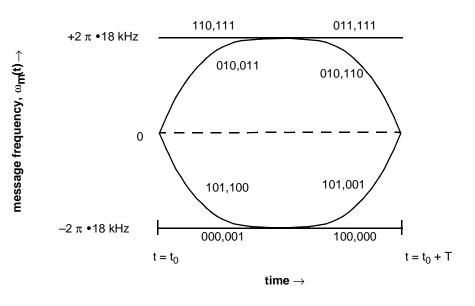

| Figure 2-19                            | Modulator Eye Diagram for Three-Term Data Sequences              |      |

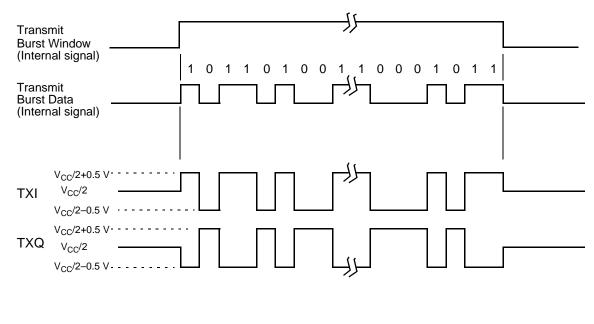

| Figure 2-20                            | NRZ-Format Output.                                               |      |

| Figure 2-21                            | Noise Suppression Muting Sequence                                |      |

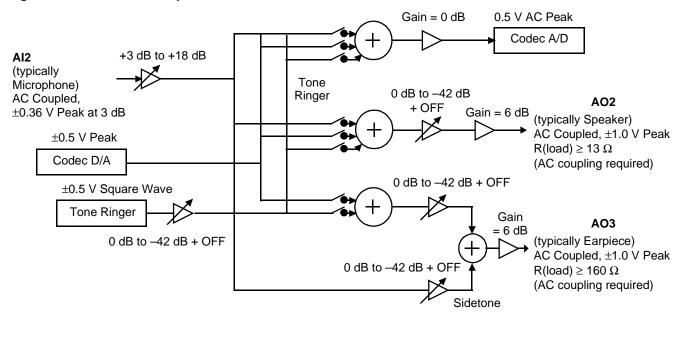

| Figure 2-22                            | Audio Multiplexer.                                               |      |

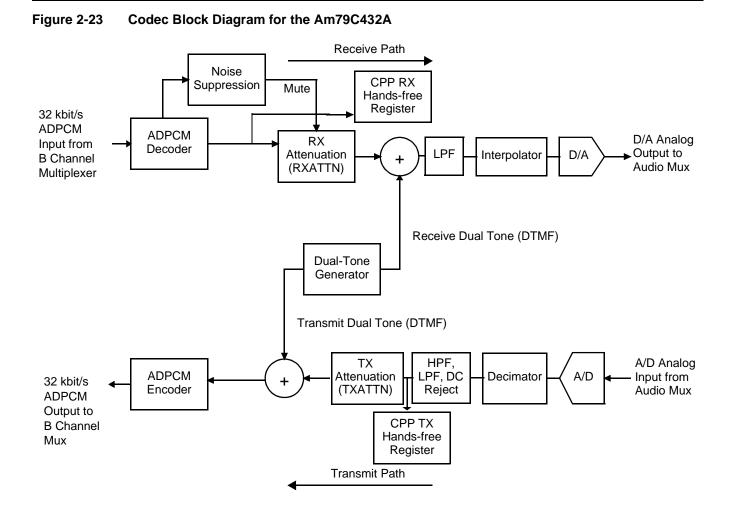

| Figure 2-23                            | Codec Block Diagram for the Am79C432A                            |      |

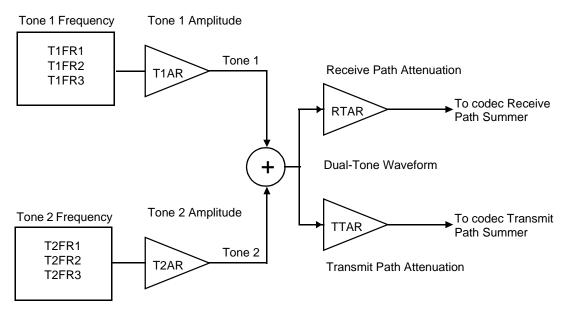

| Figure 2-24                            | Dual-Tone Generator Block Diagram                                |      |

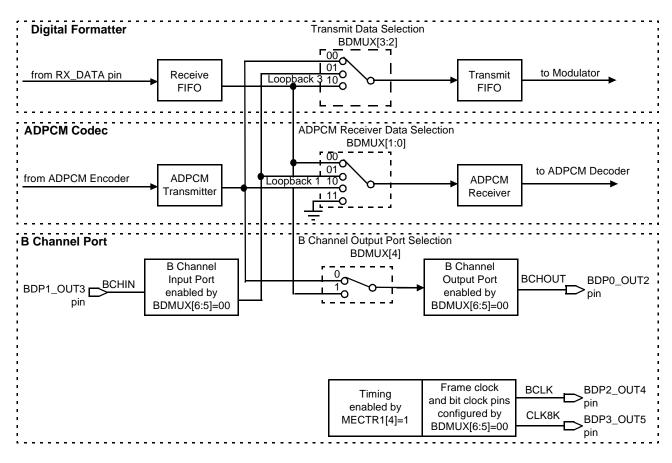

| Figure 2-25                            | B Channel Multiplexer Diagram.                                   |      |

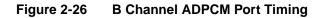

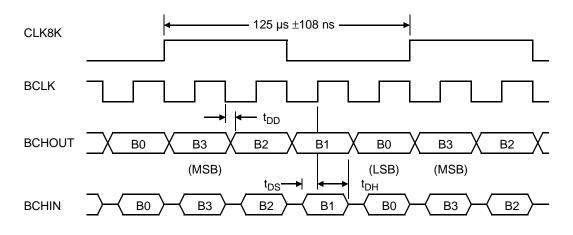

| Figure 2-26                            | B Channel ADPCM Port Timing                                      |      |

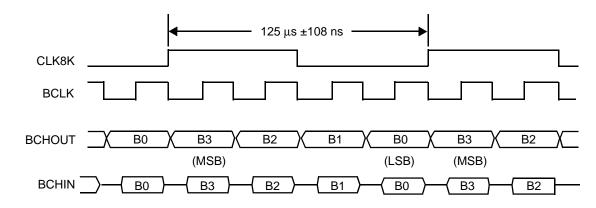

| Figure 2-27                            | Driving the Am79C432A with an 8051-Family In-Circuit Emulator    |      |

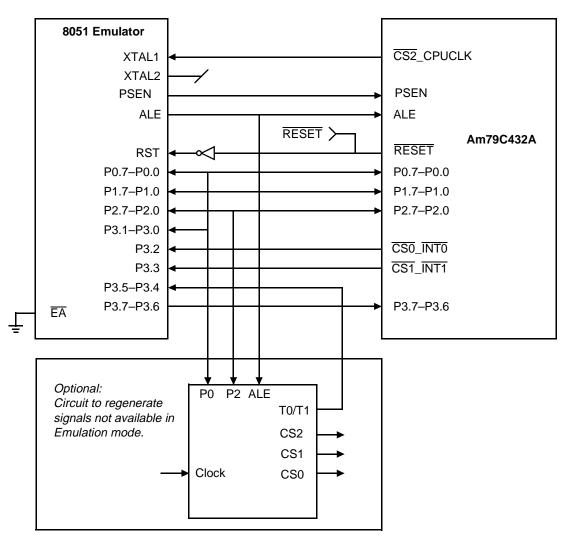

| Figure 2-28                            | Data Source Selection for Modulator Test Mode                    |      |

| Figure 2-29                            | Eliminating the RF Front-End During Software Development         | 2-44 |

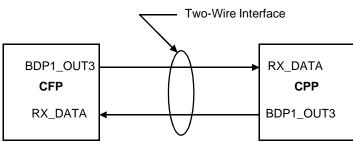

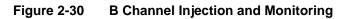

| Figure 2-30                            | B Channel Injection and Monitoring                               | 2-45 |

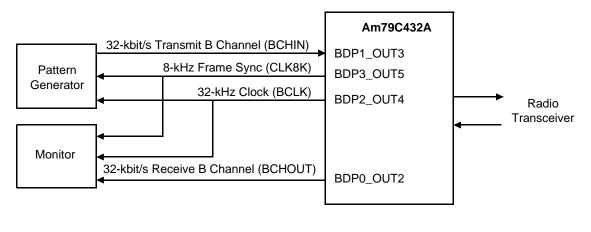

| Figure 2-31                            | D/SYN Channel Injection and Monitoring                           | 2-46 |

| Figure 2-32                            | B Channel Loopbacks                                              | 2-46 |

| Figure 3-1                             | DTMF Frequency Short-Form Reference                              | 3-33 |

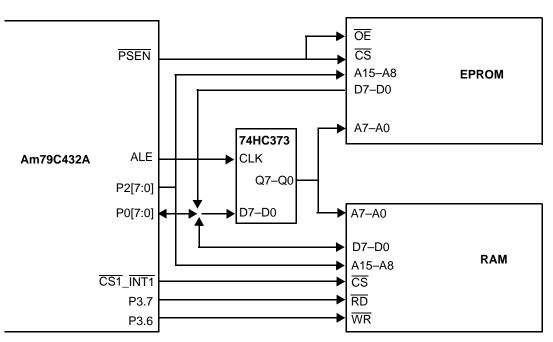

| Figure 4-1                             | Interface to Program ROM and External Data RAM                   | 4-1  |

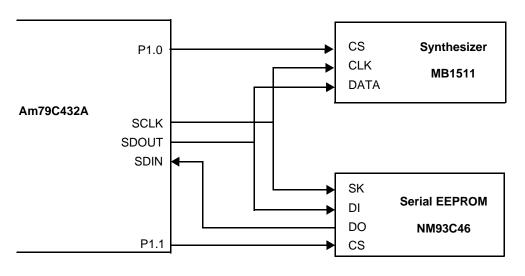

| Figure 4-2                             | Interface to a Synthesizer and Serial Access EEPROM              |      |

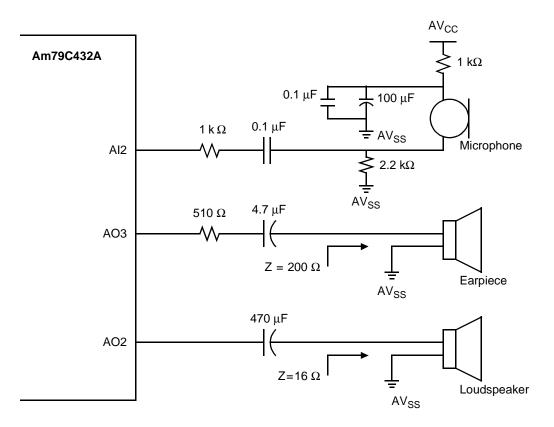

| Figure 4-3                             | Interface to Handset and Loudspeaker                             |      |

| Figure 4-4                             | Interface to Public Switched Telephone Network                   |      |

| Figure 4-5                             | Interface to a 6 x 6 Keypad Matrix.                              |      |

| -                                      |                                                                  |      |

| Figure 5-1                             | Example Key Scanner Flow Diagram                                 |      |

| Figure 6-1                             | Audio Performance Test Paths                                     | 6-4  |

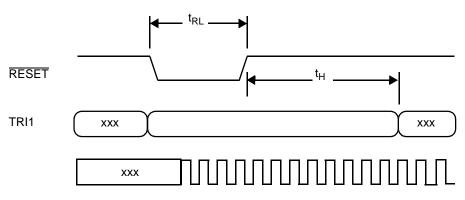

| Figure 6-2                             | Reset Timing                                                     |      |

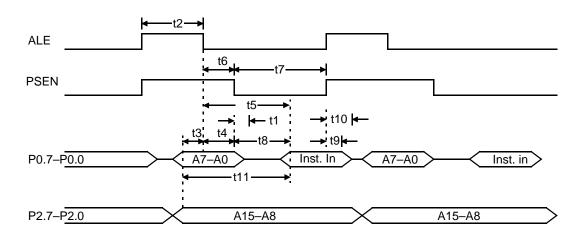

| Figure 6-3                             | Microcontroller External Program Memory Read Cycle               |      |

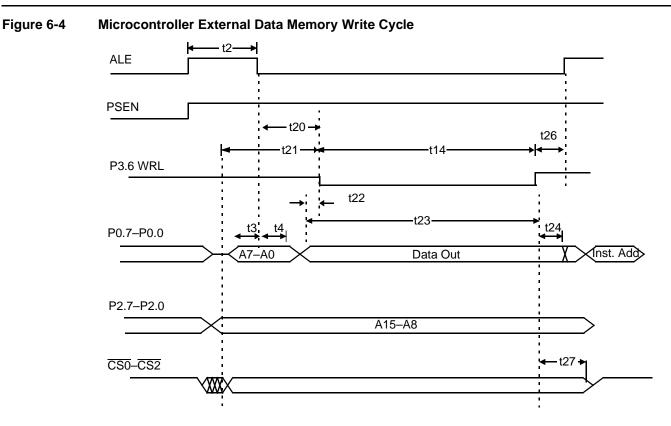

| Figure 6-4                             | Microcontroller External Data Memory Write Cycle.                |      |

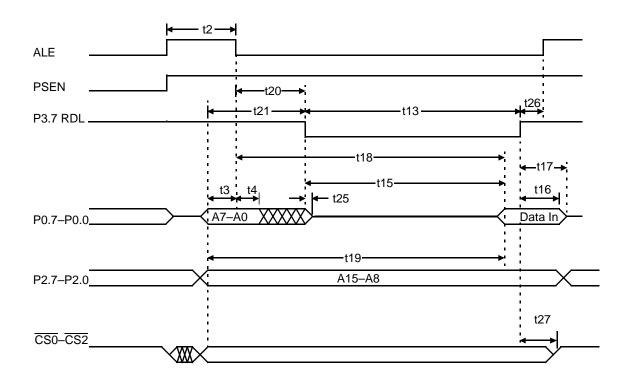

| Figure 6-5                             | Microcontroller External Data Memory Read Cycle                  |      |

| Figure 6-6                             | RF Interface Control Signal Timing                               |      |

| Figure 6-7                             | B Channel ADPCM Port Timing                                      |      |

| Figure 6-8                             | Serial Port Timing (SIOMODE[2] = 0)                              |      |

| Figure 6-9                             | Serial Port Timing (SIOMODE[2] = 1)                              | 6-15 |

## LIST OF TABLES

| Table 2-1  | Establishing the Basic Operating Mode2-1                                |

|------------|-------------------------------------------------------------------------|

| Table 2-2  | Program Memory Map                                                      |

| Table 2-3  | Data Memory Map                                                         |

| Table 2-4  | SFR Additions                                                           |

| Table 2-5  | 8032 INTO Interrupt Sources                                             |

| Table 2-6  | 8032 INT1 Interrupt Sources                                             |

| Table 2-7  | Radio Interface Signals2-26                                             |

| Table 3-1  | External Data Space Address Map                                         |

| Table 3-2  | CS2_CPUCLK Pin Function                                                 |

| Table 3-3  | Pin Select Multifunction Pin Configuration                              |

| Table 3-4  | Al2 Gain Codes                                                          |

| Table 3-5  | Sidetone Gain Codes                                                     |

| Table 3-6  | Tone Ringer Frequency Codes, Ordered by Frequency                       |

| Table 3-7  | Tone Ringer Frequency Codes, Ordered by Code                            |

| Table 3-8  | Battery-Level Comparison Threshold Codes                                |

| Table 3-9  | RSSI Codes                                                              |

| Table 3-10 | Attenuation Codes                                                       |

| Table 3-11 | Jitter Event Threshold Codes                                            |

| Table 3-12 | Jitter Phase Threshold Codes                                            |

| Table 3-13 | 8051 CPUCLK Speed Codes                                                 |

| Table 6-1  | Digital Pin DC Characteristics                                          |

| Table 6-2  | Audio Analog Pin Characteristics6-3                                     |

| Table 6-3  | Transmit and Receive Half-Channel Transmission Characteristics6-5       |

| Table 6-4  | Audio Path Performance Specifications6-6                                |

| Table 6-5  | RSSI Characteristics                                                    |

| Table 6-6  | I/Q Modulator Characteristics (Applies to TXI, TXQ, and MREF pins)6-7   |

| Table 6-7  | NRZ Output Characteristics6-8                                           |

| Table 6-8  | Reset Timing6-8                                                         |

| Table 6-9  | Am79C432A Microcontroller (80C32T2) and Address Decoder                 |

|            | Switching Characteristics                                               |

| Table 6-10 | Am79C432A Emulation Mode Address Decoder Switching Characteristics 6-10 |

| Table 6-11 | RF Interface Control Signal Timing6-13                                  |

| Table 6-12 | B Channel ADPCM Port Timing6-14                                         |

| Table 6-13 | Serial Port and A-Law PCM Switching Characteristics                     |

**CHAPTER**

# OVERVIEW

#

### 1.1 GENERAL DESCRIPTION

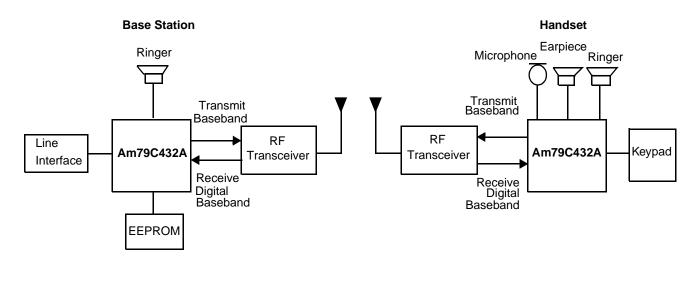

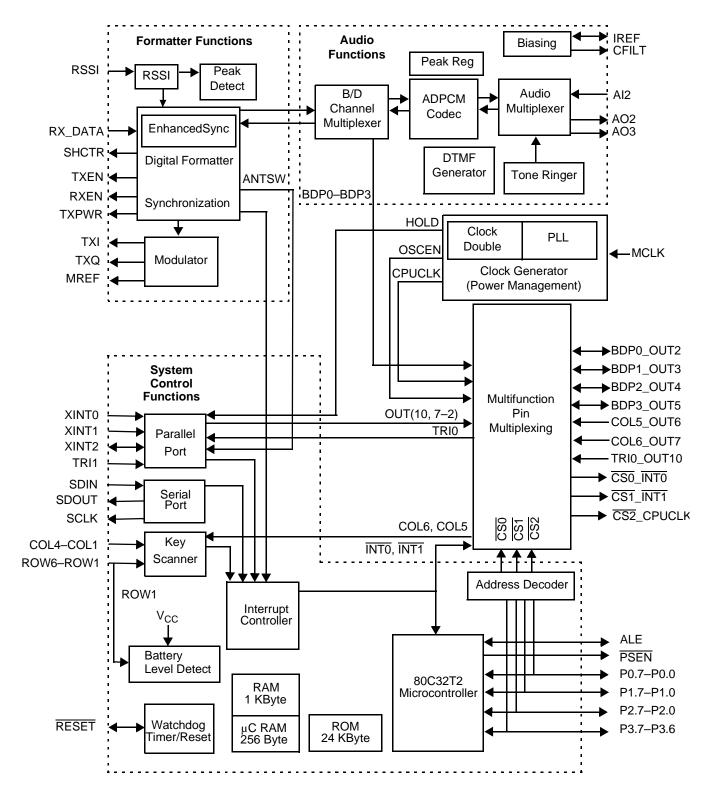

The Am79C432A PhoX<sup>™</sup> Controller is a highly integrated, low-voltage implementation of the baseband functions needed by digital cordless telephones on a single chip, including audio processing, protocol control, data formatting, and peripheral functions.

The PhoX chip implements a 32 kbit/s voice channel and a 1-, 2-, or 16 kbit/s control channel between the handset and the base station. Under the control of the on-chip 8051-class microcontroller, the Formatter performs all of the protocol requirements as well as baseband transmission and reception.

Baseband transmit data is available unfiltered as a Non-Return to Zero (NRZ) pseudo-digital signal, which is passed to the external RF transceiver for filtering and transmission. Data can also be filtered on-chip to provide analog Gaussian minimum-shift key (GMSK) output for external RF transceivers that require this format.

The voice channel is a 32 kbit/s ADPCM (Adaptive Differential Pulse Code Modulation) stream. The PhoX controller converts analog voice input at the microphone interface into ADPCM format and converts ADPCM received data into analog output at the earpiece or loudspeaker output. The device also provides digitally generated DTMF and ringing tones.

The Am79C432A incorporates many peripheral functions necessary for digital cordless telephones. For example, it has a 36-key keypad scanner, a serial port for interfacing to EEPROMs or serial LCDs, and a host of multifunction ports.

The brain of the PhoX chip is the 80C32T2, an 8051-class 8-bit microcontroller, which, with appropriate software, controls the audio path and services the various on-chip peripherals. The on-chip 1.25 Kbyte static RAM is used for variable storage. For software development, the chip interfaces directly to standard 8051 in-circuit emulators in Emulation mode.

The Am79C432A is designed for power management in a battery-operated environment. It has a low power dissipation while operating over a 2.7 to 3.6 V supply. The chip also includes a very low power Shutdown mode. For battery support, there is a battery-level measurement facility.

# AMDA

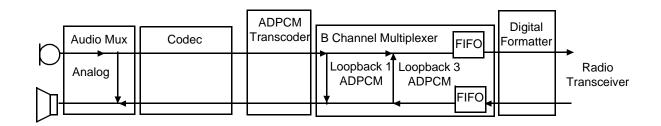

#### Figure 1-1 System Architecture

#### License

The Am79C432A PhoX device is covered by patents owned or controlled by the Common Air Interface Founders Group. AMD's license to such patents extends to use of the Am79C432A PhoX device. For information concerning additional applications, interested parties should contact:

Secretariat, Common Air Interface Founders Group Lingdales Glendyke Road Liverpool L186JR, United Kingdom

Tel: +44-151-724-5591 Fax: +44-151-724-6938

### 1.2 DISTINCTIVE CHARACTERISTICS

- Performs protocol, data formatting, audio processing, and peripheral functions for digital cordless telephones

- May be used in the base station or the handset

- Power and battery management features to extend battery life:

- Full CMOS design and low voltage operation

- Battery monitor to protect the cordless operation

- On-chip 8051-class microcontroller controls all functions

- Special Digital Formatter features:

- Link controller which performs all data transmission and reception

- Baseband I/Q GMSK modulator

- Receive signal strength indicator for channel scanning

- Fade detection and management

- Improved timing and symbol recovery

- Special audio features:

- ADPCM codec compliant with CCITT G.721

- DTMF generator

- Flexible audio multiplexing and gain control

- Includes 16  $\Omega$  speaker driver and a microphone interface

- Ringing tone generator

- Other on-chip peripheral functions include:

- 1.25 KByte static RAM (includes 256 bytes internal data space)

- 24 KByte mask-programmable ROM

- Serial port for EEPROM, LCD or synthesizer control

- 36-key scanner for dialing and special function keys

- Up to 10 general-purpose output ports

- Watchdog timer

- Clock Double mode for the microcontroller

- Other features:

- Peak-detect hardware to allow the implementation of a handsfree near full-duplex speakerphone capabilities

- Enhanced RSSI with peak detect hardware

- Antenna diversity control

- Built-in power management features:

- 2.7 V to 3.6 V low-power operation

- Low active power consumption, 24 mW

- Super low power Shutdown mode, 108  $\mu$ W

- Battery-level detection

- Test and development features:

- In-circuit 8051 emulator support for code development

- Numerous test paths and loopbacks for bit error rate, continuity, and performance testing

- Continuous transmit RF spectral measurement and modulator bypass features

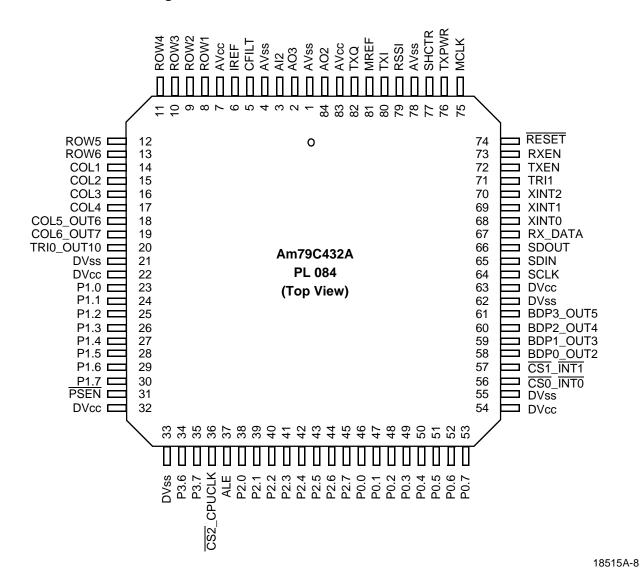

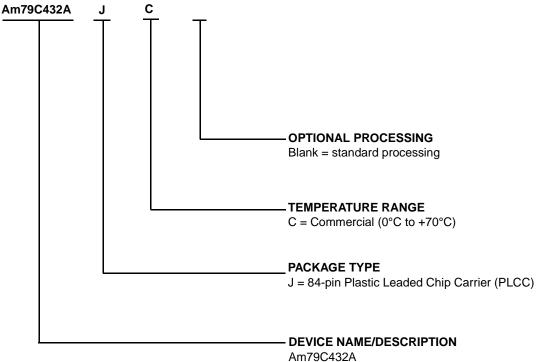

- 84-pin PLCC package

#### Figure 1-2 Block Diagram

#### Figure 1-3 Connection Diagram

#### Note:

Pin 1 marked for orientation purposes only.

**PIN LIST**

| Pin      | Pin Name Pad Type |                        | Shutdown/<br>Idle State<br>Conditions<br>(Default<br>Functions) <i>†</i> | Default<br>Function or<br>80C32T2 Port<br>Special<br>Function <del>/</del> | Alternate<br>Multifunction<br>Pins <i>†</i> |

|----------|-------------------|------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------|

| 1        | AV <sub>SS</sub>  | ANALOG OUTPUT          |                                                                          |                                                                            |                                             |

| 2        | AO3               | ANALOG OUTPUT          | Z                                                                        |                                                                            |                                             |

| 3        | AI2               | ANALOG INPUT           | Z                                                                        |                                                                            |                                             |

| 4        | AV <sub>SS</sub>  | ANALOG POWER           |                                                                          |                                                                            |                                             |

| 5        | CFILT             | ANALOG OUTPUT          | R (reference)                                                            |                                                                            |                                             |

| 6        | IREF              | ANALOG OUTPUT          | Z                                                                        |                                                                            |                                             |

| 7        | AV <sub>CC</sub>  | ANALOG POWER           |                                                                          |                                                                            |                                             |

| 8        | ROW1              | ROWCOL                 | 0R                                                                       | ROW1                                                                       | BATLEVEL (Z)                                |

| 9        | ROW2              | ROWCOL                 | 0R                                                                       |                                                                            |                                             |

| 10       | ROW3              | ROWCOL                 | 0R                                                                       |                                                                            |                                             |

| 11       | ROW4              | ROWCOL                 | 0R                                                                       |                                                                            |                                             |

| 12       | ROW5              | ROWCOL                 | 0R                                                                       |                                                                            |                                             |

| 13       | ROW6              | ROWCOL                 | 1R                                                                       |                                                                            |                                             |

| 14       | COL1              | ROWCOL                 | 1R                                                                       |                                                                            |                                             |

| 15       | COL2              | ROWCOL                 | 1R                                                                       |                                                                            |                                             |

| 16       | COL3              | ROWCOL                 | 1R                                                                       |                                                                            |                                             |

| 17       | COL4              | ROWCOL                 | 1R                                                                       |                                                                            |                                             |

| 18       | COL5_OUT6         | ROWCOL                 | 1R                                                                       | COL5 (1R)                                                                  | OUT6 (Q)                                    |

| 19       | COL6_OUT7         | ROWCOL                 | 1R                                                                       | COL6 (1R)                                                                  | OUT7 (Q),<br>OSCEN (Q)                      |

| 20       | TRI0_OUT10        | TRI-INPUT              | Z                                                                        | TRI0 (Z)                                                                   | OUT10 (Q)                                   |

| 21       | DV <sub>SS</sub>  | POWER                  |                                                                          |                                                                            |                                             |

| 22       | DV <sub>CC</sub>  | POWER                  |                                                                          |                                                                            |                                             |

| 23       | P1.0              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 24       | P1.1              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 25       | P1.2              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 26       | P1.3              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 27       | P1.4              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 28       | P1.5              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 29       | P1.6              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 30       | P1.7              | TSIO (pu)              | SFR (0, 1R)                                                              |                                                                            |                                             |

| 31       | PSEN              | TSIO (pu)              | 1R                                                                       |                                                                            |                                             |

| 32       | DV <sub>CC</sub>  | POWER                  |                                                                          |                                                                            |                                             |

| 33       | DV <sub>SS</sub>  | POWER                  |                                                                          |                                                                            |                                             |

| 34       | P3.6              | TSIO (pu)              | 1R                                                                       | WR                                                                         |                                             |

| 35       | P3.7              | TSIO (pu)              | 1R                                                                       | RD                                                                         |                                             |

| 36       | CS2_CPUCLK        | OUTPUT                 | Q                                                                        | CS2                                                                        | CPUCLK                                      |

| 37       | ALE               | TSIO                   |                                                                          | A [0]                                                                      |                                             |

| 38       | P2.0              | TSIO (pu)              | SFR (0, 1R)                                                              | A[8]                                                                       |                                             |

| 39<br>40 | P2.1<br>P2.2      | TSIO (pu)<br>TSIO (pu) | SFR (0, 1R)<br>SFR (0, 1R)                                               | A[9]<br>A[10]                                                              |                                             |

| 40       | P2.2<br>P2.3      | TSIO (pu)              | SFR (0, 1R)<br>SFR (0, 1R)                                               | A[10]<br>A[11]                                                             |                                             |

| 41       | P2.4              | TSIO (pu)              | SFR (0, 1R)<br>SFR (0, 1R)                                               | A[11]<br>A[12]                                                             |                                             |

| 43       | P2.5              | TSIO (pu)              | SFR (0, 1R)                                                              | A[13]                                                                      |                                             |

| 44       | P2.6              | TSIO (pu)              | SFR (0, 1R)                                                              | A[14]                                                                      |                                             |

| 45       | P2.7              | TSIO (pu)              | SFR (0, 1R)                                                              | A[15]                                                                      |                                             |

# AMD

| Pin  | Pin Name             | Pad Type       | Shutdown/<br>Idle State<br>Conditions<br>(Default<br>Functions) <i>†</i> | Default<br>Function or<br>80C32T2 Port<br>Special<br>Function <i>†</i> | Alternate<br>Multifunction<br>Pins <i>†</i> |

|------|----------------------|----------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------|

| 46   | P0.0                 | TSIO (keeper)  | QZ                                                                       | A/D[0]                                                                 |                                             |

| 47   | P0.1                 | TSIO (keeper)  | QZ                                                                       | A/D[1]                                                                 |                                             |

| 48   | P0.2                 | TSIO (keeper)  | QZ                                                                       | A/D[2]                                                                 |                                             |

| 49   | P0.3                 | TSIO (keeper)  | QZ                                                                       | A/D[3]                                                                 |                                             |